Содержание

- 2. Цели и задачи Освоение основных принципов проектирования логических вентилей: Схемотехника КМДП логических вентилей Проектирование КМДП вентилей

- 3. КМДП вентили ТТЛ – транзисторно-транзисторная логика. КМДП – комплементарный металл–диэлектрик–полупроводник. Преимущества КМДП: Высокая степень интеграции (плотность)

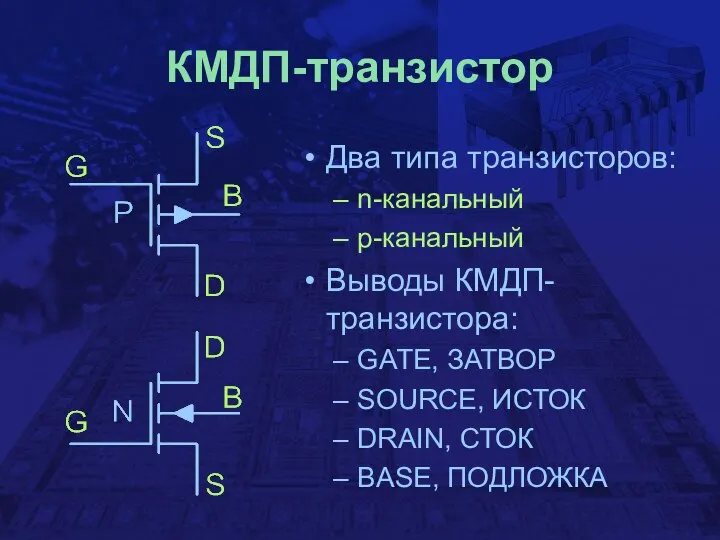

- 4. КМДП-транзистор Два типа транзисторов: n-канальный p-канальный Выводы КМДП-транзистора: GATE, ЗАТВОР SOURCE, ИСТОК DRAIN, СТОК BASE, ПОДЛОЖКА

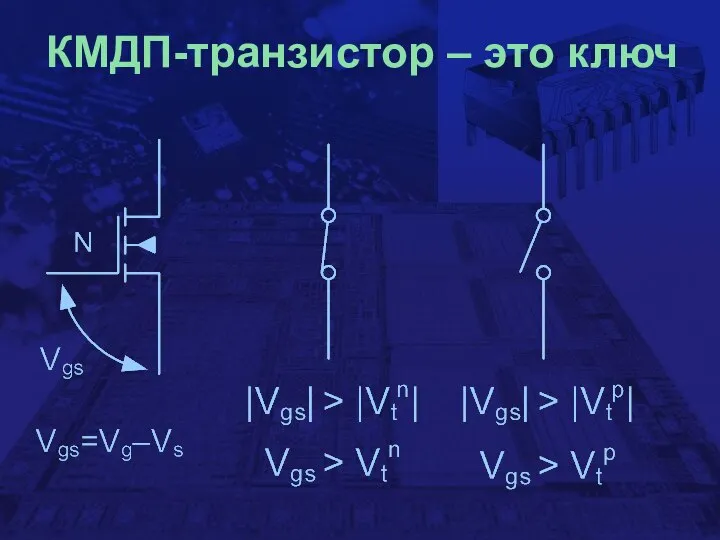

- 5. КМДП-транзистор – это ключ

- 6. КМДП-транзистор – это ключ

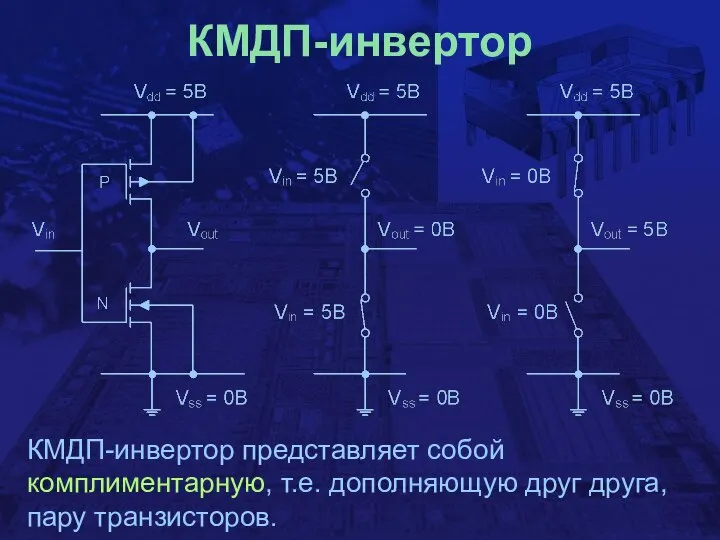

- 7. КМДП-инвертор КМДП-инвертор представляет собой комплиментарную, т.е. дополняющую друг друга, пару транзисторов.

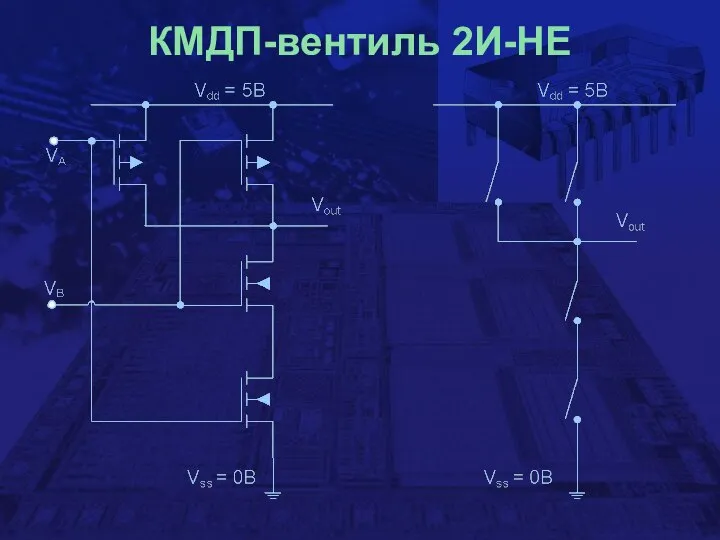

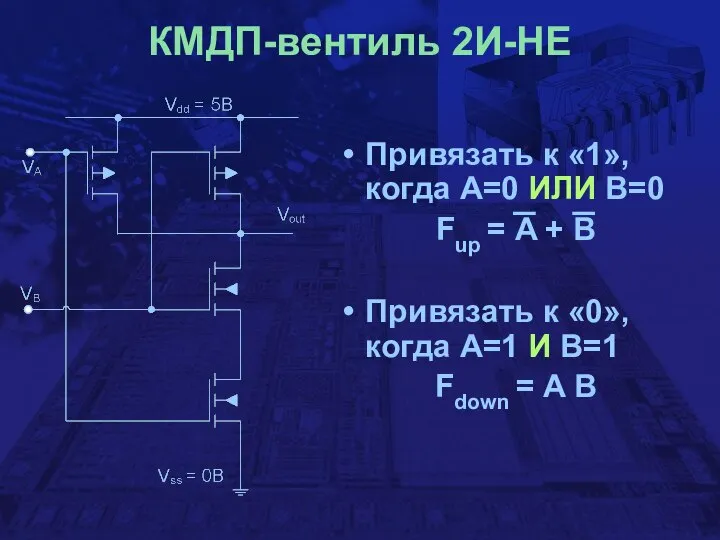

- 8. КМДП-вентиль 2И-НЕ

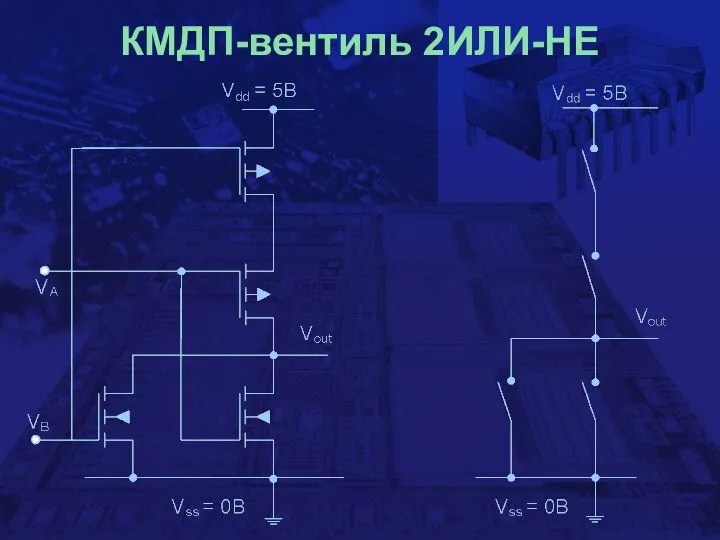

- 9. КМДП-вентиль 2ИЛИ-НЕ

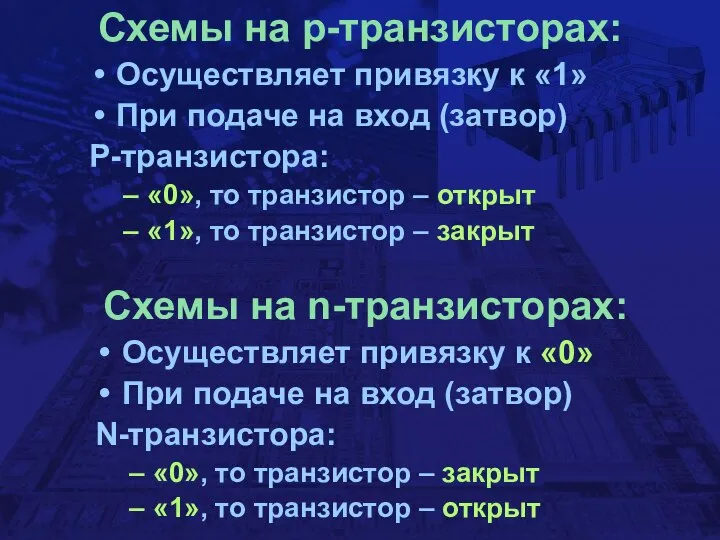

- 10. Схемы на p-транзисторах: Осуществляет привязку к «1» При подаче на вход (затвор) P-транзистора: «0», то транзистор

- 11. КМДП-вентиль 2И-НЕ Привязать к «1», когда А=0 ИЛИ B=0 Fup = A + B Привязать к

- 12. КМДП-вентиль 2ИЛИ-НЕ Привязать к «1», когда А=0 И B=0 Fup= A B Привязать к «0», когда

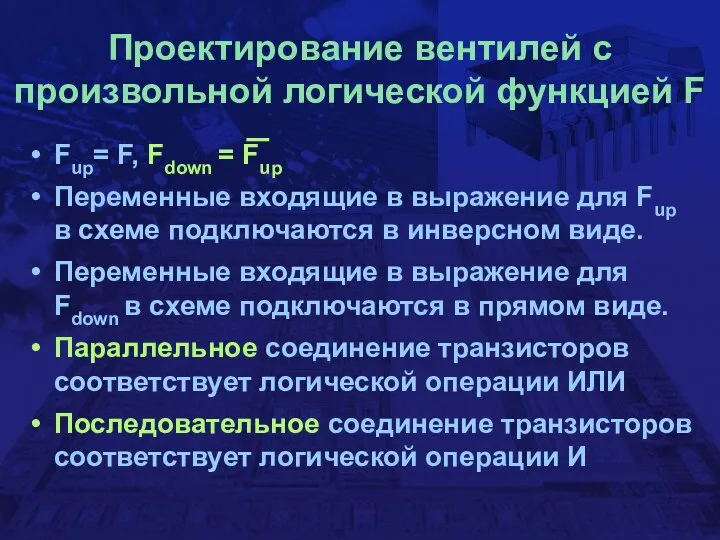

- 13. Проектирование вентилей с произвольной логической функцией F Fup= F, Fdown = Fup Переменные входящие в выражение

- 15. Скачать презентацию

Влияние вредных примесей на свойства стали

Влияние вредных примесей на свойства стали jQuery UI

jQuery UI Новогодняя презентация: Новый год, Рождество, Старый Новый год

Новогодняя презентация: Новый год, Рождество, Старый Новый год Презентация "Регулирование предпринимательской деятельности" - скачать презентации по Экономике

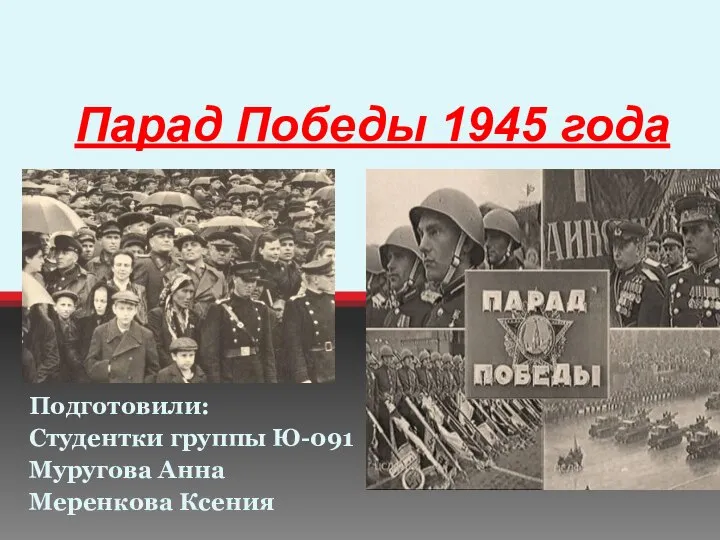

Презентация "Регулирование предпринимательской деятельности" - скачать презентации по Экономике Презентация Парад Победы 1945 года

Презентация Парад Победы 1945 года телестудия LEONARUS

телестудия LEONARUS  Выполнено Наумовым Михаилом

Выполнено Наумовым Михаилом  Праздник Троица

Праздник Троица Приглашаем к сотрудничеству. Рекламные возможности ВК «Алтай»

Приглашаем к сотрудничеству. Рекламные возможности ВК «Алтай» Философия как явление культуры

Философия как явление культуры  Методические основы анализа и проектирования ПО

Методические основы анализа и проектирования ПО Офисно-логистический комплекс «Передовой»

Офисно-логистический комплекс «Передовой» Мусульманская правовая система_

Мусульманская правовая система_ Особливості спеціальності оператор комп’ютерного набору

Особливості спеціальності оператор комп’ютерного набору Математик 4б анги Багш Б. Болортуяа

Математик 4б анги Багш Б. Болортуяа Презентация Экспертиза растительного масла

Презентация Экспертиза растительного масла Многомерные массивы. (Тема 7)

Многомерные массивы. (Тема 7) Сделки в гражданском праве

Сделки в гражданском праве  Фотопрезентация. Работа с крупой. Младший дошкольный возраст. Подготовил: Воспитатель

Фотопрезентация. Работа с крупой. Младший дошкольный возраст. Подготовил: Воспитатель  Презентация на тему "Патогенді микроорганизм" - скачать презентации по Медицине

Презентация на тему "Патогенді микроорганизм" - скачать презентации по Медицине Понятие и источники уголовного права

Понятие и источники уголовного права Навыки оценки санитарно-гигиенических требований к получению, транспортировке, хранению очищенной воды и воды для инъекций

Навыки оценки санитарно-гигиенических требований к получению, транспортировке, хранению очищенной воды и воды для инъекций Аппендицит

Аппендицит Язык программирования Pascal. Основные структуры языка

Язык программирования Pascal. Основные структуры языка Цыпленок - презентация для начальной школы

Цыпленок - презентация для начальной школы Современная философия качества

Современная философия качества  Теория железобетона. Проектирование ж/б конструкций. Инженерные сооружения

Теория железобетона. Проектирование ж/б конструкций. Инженерные сооружения Международные стандарты и руководства в области КСО

Международные стандарты и руководства в области КСО