Содержание

- 2. Суть блочно-иерархического подхода расчленение представлений об объекте проектирования, включая модели, постановка проектных задач, проектной документации и

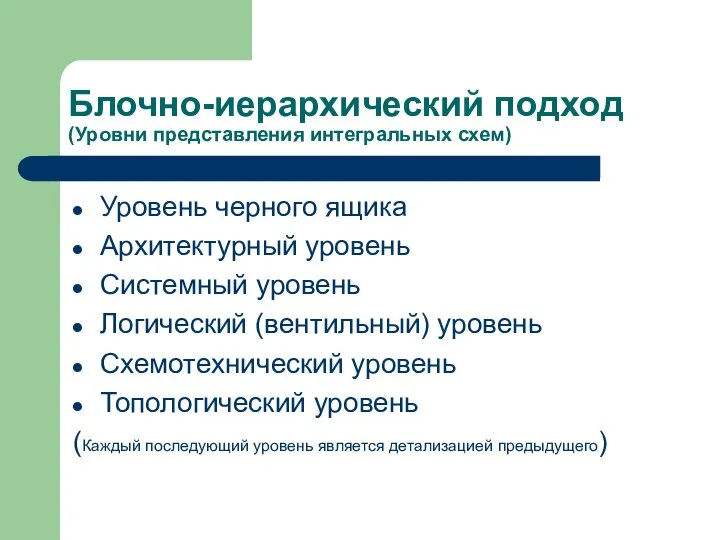

- 3. Блочно-иерархический подход (Уровни представления интегральных схем) Уровень черного ящика Архитектурный уровень Системный уровень Логический (вентильный) уровень

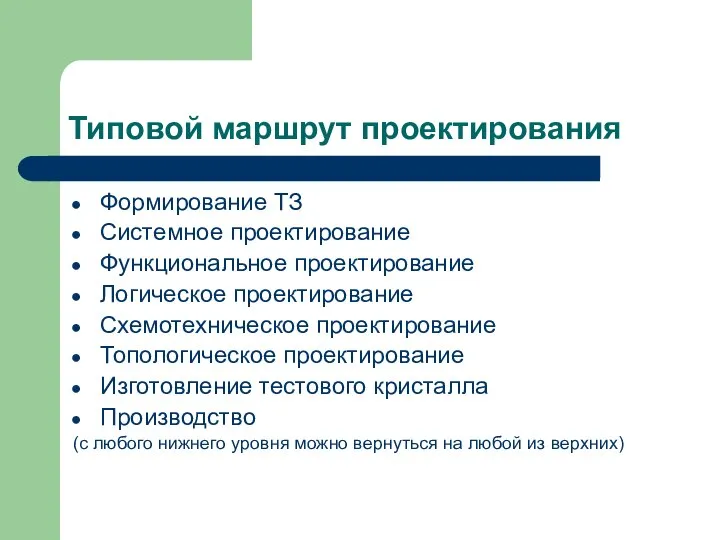

- 4. Типовой маршрут проектирования Формирование ТЗ Системное проектирование Функциональное проектирование Логическое проектирование Схемотехническое проектирование Топологическое проектирование Изготовление

- 5. Формирование Технического Задания (ТЗ) Техническое задание – это документ на разработку микросхемы, который формируется в тесном

- 6. Состав ТЗ Функциональность ИМС (какую функцию она должна выполнять) Параметры работы ИМС (напряжение питания, тактовая частота,

- 7. Системное проектирование определяется архитектура будущей ИМС (какие блоки будут входить в ее состав, как они будут

- 8. Верификация описания схемы Верификация – проверка правильности функционирования схемы на данном уровне представления. На каждом этапе

- 9. Технология повторного использования разработок Некоторые блоки в разных ИМС имеют одинаковую функциональность и структуру возможно повторное

- 10. Функциональное проектирование Производится детализация поведенческого описания, до уровня регистровых передач (RTL - Register Transfer Level) Т.е.

- 11. Логическое проектирование На основе описания на RTL уровне разрабатывается описание на вентильном уровне Трансляция описания на

- 12. Библиотека элементов (БЭ) это база данных логических вентилей. Каждая запись в такой базе данных содержит информацию

- 13. БЭ (библиотека элементов) это набор кирпичиков, которые проектировщик с помощью САПР использует для создания ИМС. Создание

- 14. Схемотехническое проектирование На данном этапе согласно полученной логической схеме и БЭ синтезируется электрическая схема. Для цифровых

- 15. Топологическое проектирование Этап проектирования топологи требует гораздо больших экономических и временных затрат, чем любые другие этапы.

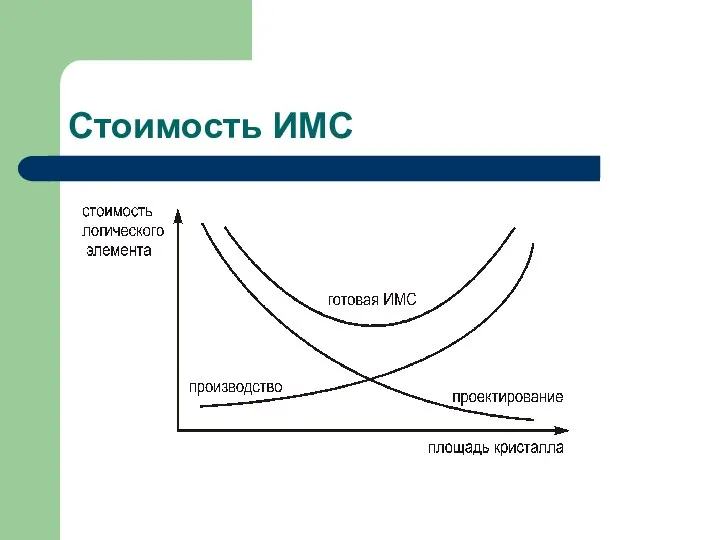

- 16. Стоимость ИМС

- 17. Маршрут топологического проектирования Разработка общего плана топологии Разработка топологии Верификация топологии Экспертная проверка Изготовление фотошаблонов

- 18. Разработка общего плана топологии Спланировать разводку шин питания, земли и глобальных сигналов Определить расположение контактных площадок

- 19. Разработка топологии Топология – дерево со стволом (кристалл в целом), ветками (блоки), малыми ветками (субблоки), листьями

- 20. Верификация (проверка топологии) Визуальный контроль топологии Design Rules Check (DRC) или проверка на соответствие правилам проектирования

- 21. Экспертная проверка Проведение проверки правильности выполнения топологии независимым экспертом, напрямую не вовлеченным в данный проект Проводится

- 23. Скачать презентацию

Устойчивость откосов и склонов

Устойчивость откосов и склонов Урок, как основная форма работы по физическому воспитанию в начальной школе

Урок, как основная форма работы по физическому воспитанию в начальной школе Central Nervous System

Central Nervous System Достопримечательности Китая

Достопримечательности Китая Орталыќ пост пульт-манипуляторыныњ телебасќару арнасыныњ таратушы ќ±рылѓыларымен байланысы

Орталыќ пост пульт-манипуляторыныњ телебасќару арнасыныњ таратушы ќ±рылѓыларымен байланысы Московский лабиринт

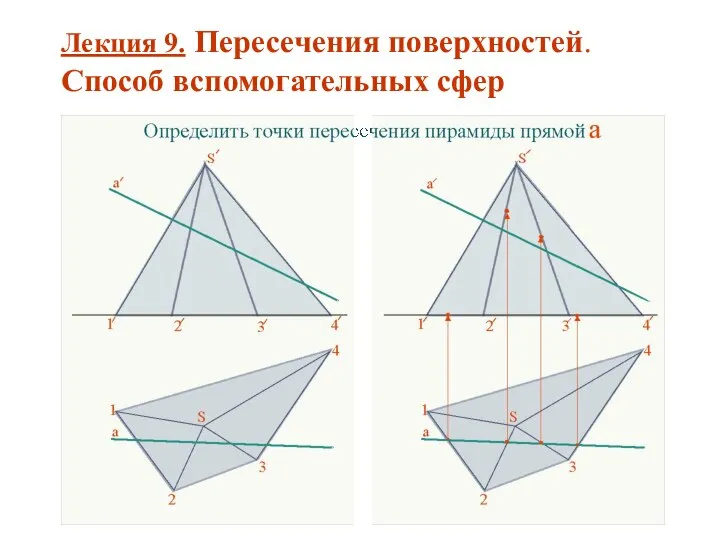

Московский лабиринт Пересечения поверхностей. Способ вспомогательных сфер. (Лекция 9)

Пересечения поверхностей. Способ вспомогательных сфер. (Лекция 9) Национальная денежно-кредитная политика страны Подготовила: Омельченко Марина, гр.Т-091

Национальная денежно-кредитная политика страны Подготовила: Омельченко Марина, гр.Т-091 Современный этап развития ядерной энергетики.Реакторы на тепловых и быстрых нейтронах

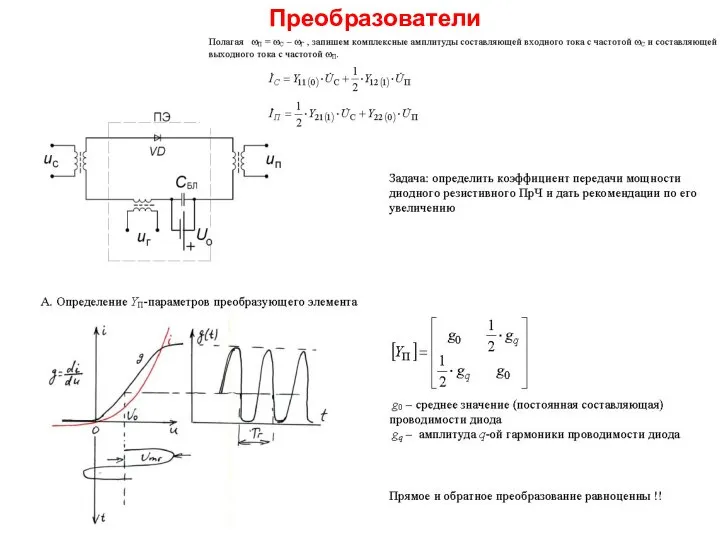

Современный этап развития ядерной энергетики.Реакторы на тепловых и быстрых нейтронах Преобразователи частоты

Преобразователи частоты Достопримечательности Великобритании

Достопримечательности Великобритании Организация, вооружение и боевая техника общевойсковых подразделений Вооружённых Сил Российской Федерации. Общая тактика

Организация, вооружение и боевая техника общевойсковых подразделений Вооружённых Сил Российской Федерации. Общая тактика Preposition maskulinum, femininum, neutrum

Preposition maskulinum, femininum, neutrum Моделирование движения математического маятника в среде с нелинейным сопротивлением на языке программирования Pascal

Моделирование движения математического маятника в среде с нелинейным сопротивлением на языке программирования Pascal Архитектура Древней Руси 11-13 вв.

Архитектура Древней Руси 11-13 вв. Ионные транспортеры и их роль в клетке

Ионные транспортеры и их роль в клетке Дифференциальная диагностика неонатальных желтух Выполнила: Мельчукова Владлена. Гр.51ф 1бр. Преподаватель: Соколова Л. И.

Дифференциальная диагностика неонатальных желтух Выполнила: Мельчукова Владлена. Гр.51ф 1бр. Преподаватель: Соколова Л. И. Опросник описания поведения Томаса

Опросник описания поведения Томаса Коммутационные поля

Коммутационные поля Атраценпроизводные и другие производные антрацена

Атраценпроизводные и другие производные антрацена реанимация 10.09.2018-16.09. 2018

реанимация 10.09.2018-16.09. 2018 Любка Ганна Степанівна - презентация для начальной школы

Любка Ганна Степанівна - презентация для начальной школы Аквааэробика

Аквааэробика ПрезентацияДидактическая игра овощи - презентация для начальной школы

ПрезентацияДидактическая игра овощи - презентация для начальной школы Прості механізми в побуті

Прості механізми в побуті Типы словосочетаний - презентация для начальной школы_

Типы словосочетаний - презентация для начальной школы_ Презентация Налоговая льгота: понятие и классификация

Презентация Налоговая льгота: понятие и классификация Презентация на тему "Инновационные медицинские образовательные программы" - скачать презентации по Медицине

Презентация на тему "Инновационные медицинские образовательные программы" - скачать презентации по Медицине