Содержание

- 2. Программная модель современных процессоров х86 Современные представители семейства х86 являются 32-битными процессорами; в новых моделях появилось

- 3. Расширения х86-64 и ЕМ64Т в первую очередь предназначены для радикального увеличения объема адресуемой памяти: 64-битные регистры

- 4. Режимы работы процессоров 32-битные процессоры могут работать в одном из следующих режимов: ♦ Режим реальной адресации

- 5. ♦ Режим виртуального процессора 8086 (Virtual 8086 Mode, V86) является особым состоянием задачи защищенного режима, в

- 6. ♦ В режиме системного управления (System Management Mode, SMM) процессор выходит в иное, изолированное от остальных

- 7. ♦ режим совместимости (compatibility mode) позволяет 64-битным ОС работать с 32- и 16-битными приложениями. Для приложений

- 8. Пространство памяти (memory space) предназначено для хранения кодов инструкций и данных. Память может логически организовываться в

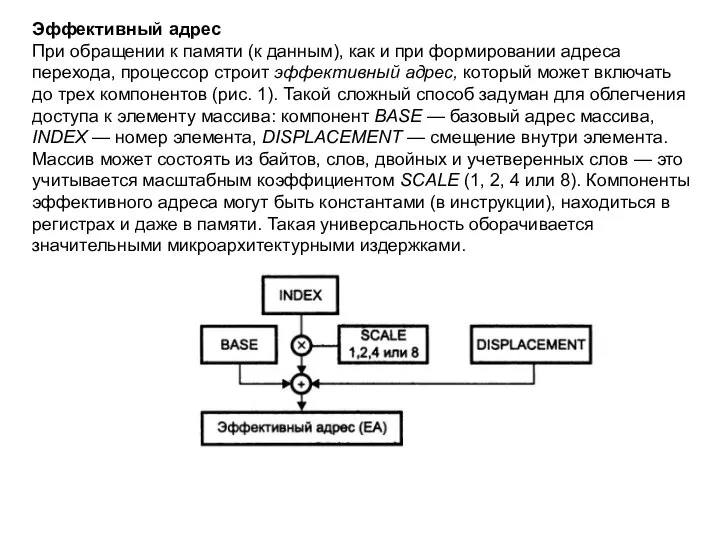

- 9. Эффективный адрес При обращении к памяти (к данным), как и при формировании адреса перехода, процессор строит

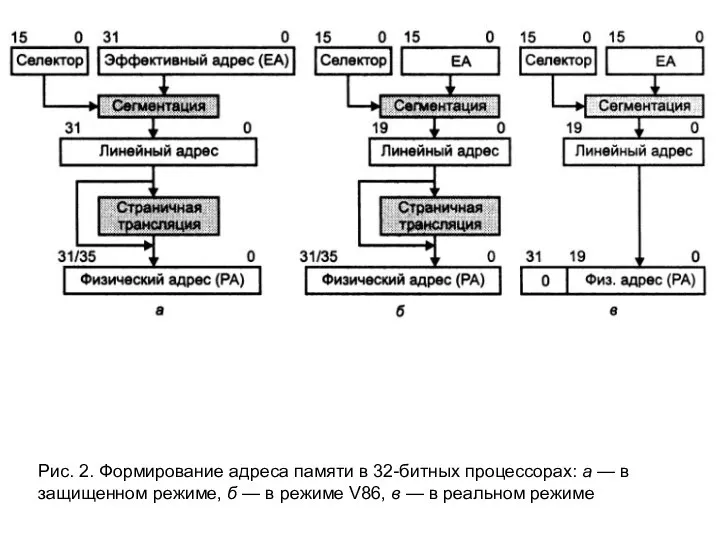

- 10. Преобразование адресов Применительно к памяти различают три адресных пространства: логическое, линейное и физическое. По сочетанию сегментации

- 11. Рис. 2. Формирование адреса памяти в 32-битных процессорах: а — в защищенном режиме, б — в

- 12. Преобразование логического адреса в физический для 32-битных процессоров иллюстрирует рис. 2. Блок сегментации транслирует логическое адресное

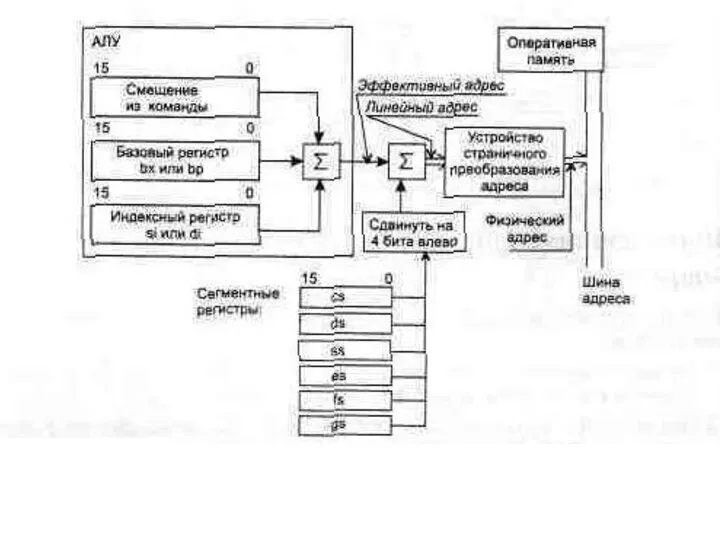

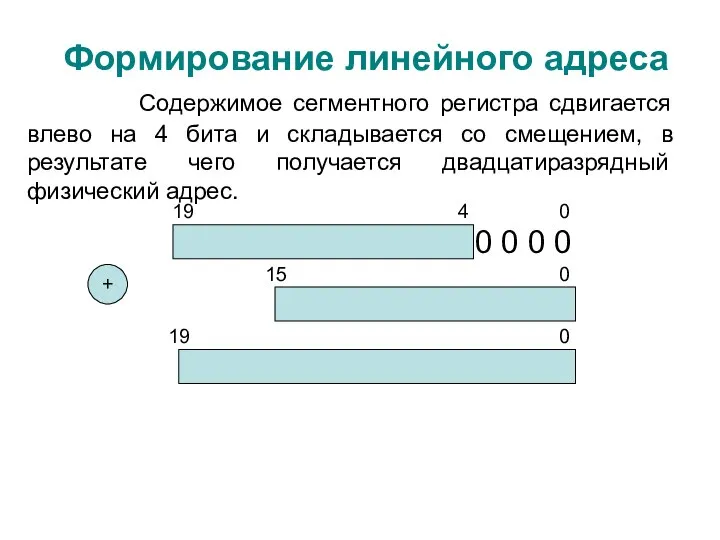

- 14. Формирование линейного адреса Содержимое сегментного регистра сдвигается влево на 4 бита и складывается со смещением, в

- 15. В реальном режиме микропроцессор работает как 8086 с возможностью использования 32-битных расширений. В отличие от 8086

- 16. Данный механизм образования физического адреса позволяет сделать программное обеспечение перемещаемым, то есть не зависящим от конкретных

- 17. Защищенный режим лишен недостатков реального режима, в нем можно адресоваться к участку памяти размером 4 Гб

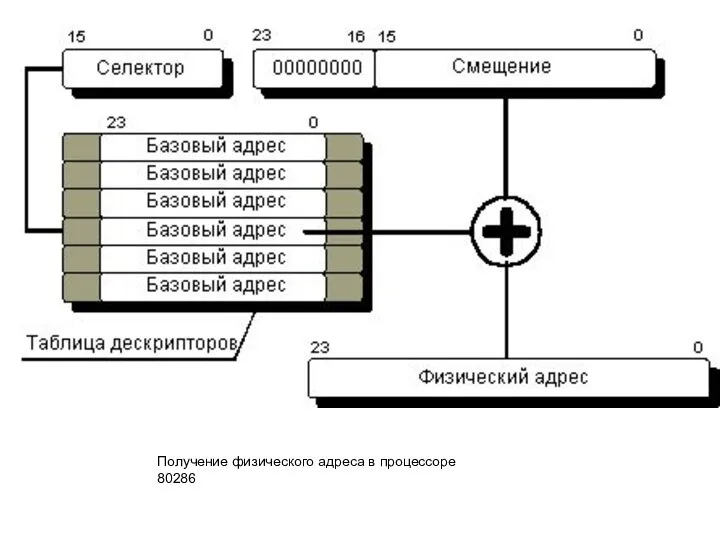

- 18. РАБОТА С АДРЕСАМИ В защищенном режиме, как и в реальном, логический адрес состоит из двух компонент.

- 19. Получение физического адреса в процессоре 80286

- 20. Согласно этой схеме адресации памяти, селектор содержит номер ячейки таблицы дескрипторов, но не компоненту физического адреса.

- 21. Преобразование адресов в защищённом режиме Процессор i80386 и выше использует трёхступенчатую схему преобразования адреса. Программы используют

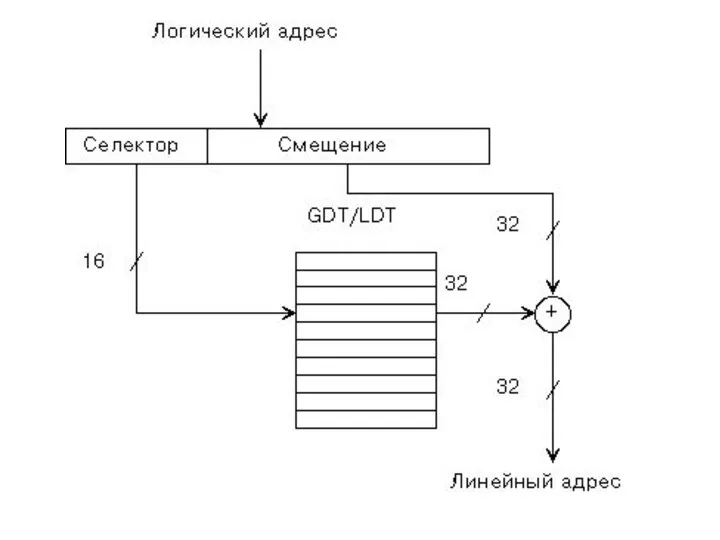

- 23. Значение из поля индекса селектора используется в качестве индекса в таблице LDT или GDT для выборки

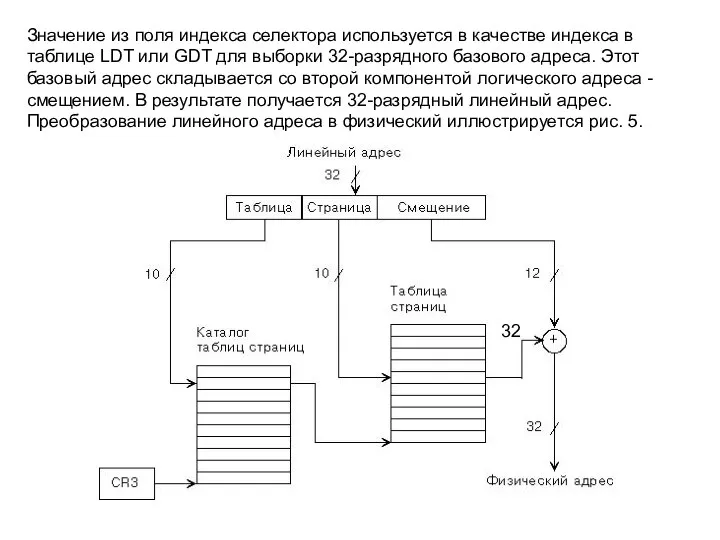

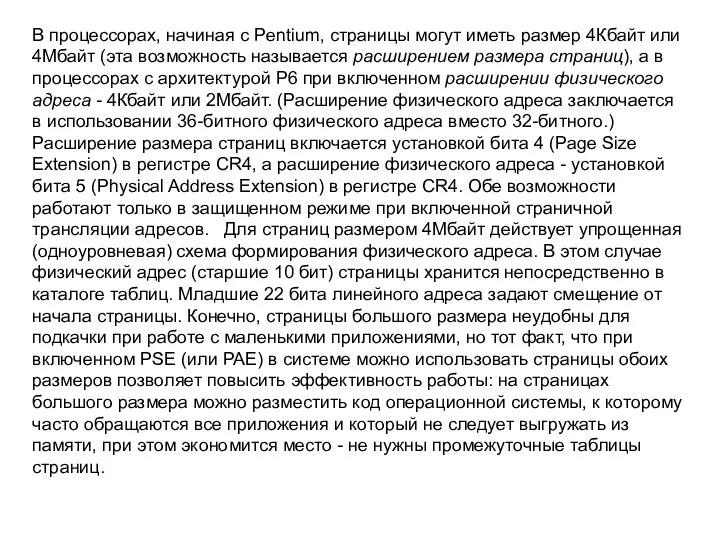

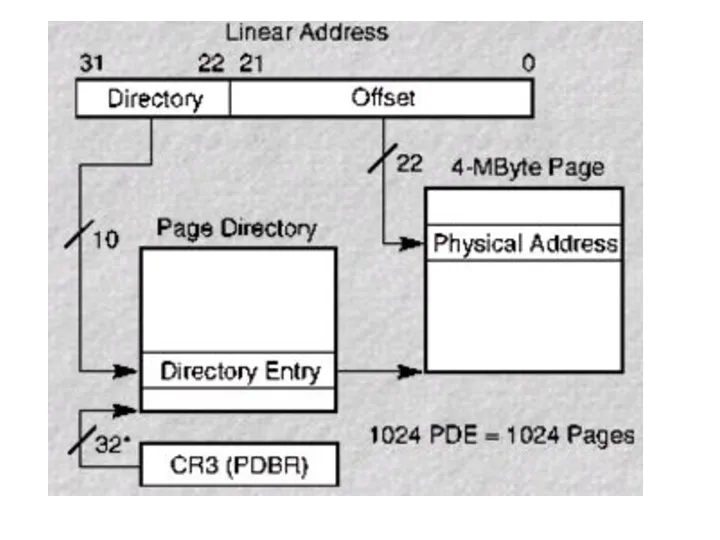

- 24. Процесс вычисления адреса страницы часто называют трансляцией страниц. Старшие 10 бит линейного адреса используются как индекс

- 25. Дескриптор таблицы страниц. Для представления старших 20 битов физического адреса таблицы страниц в дескрипторе используются биты

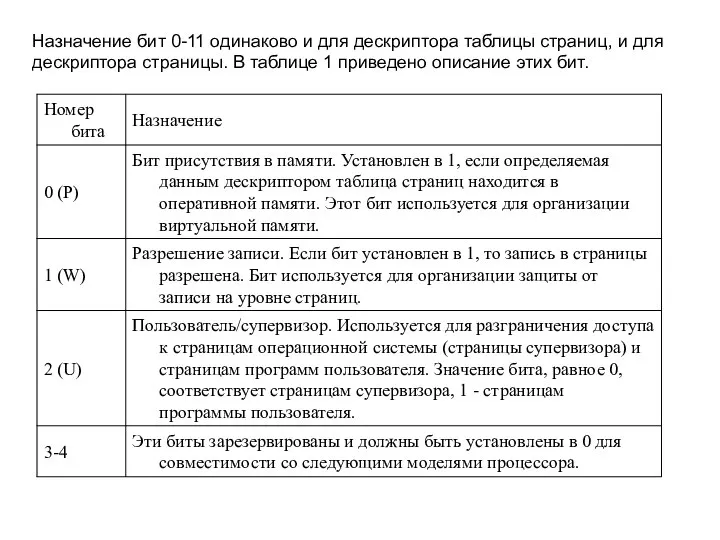

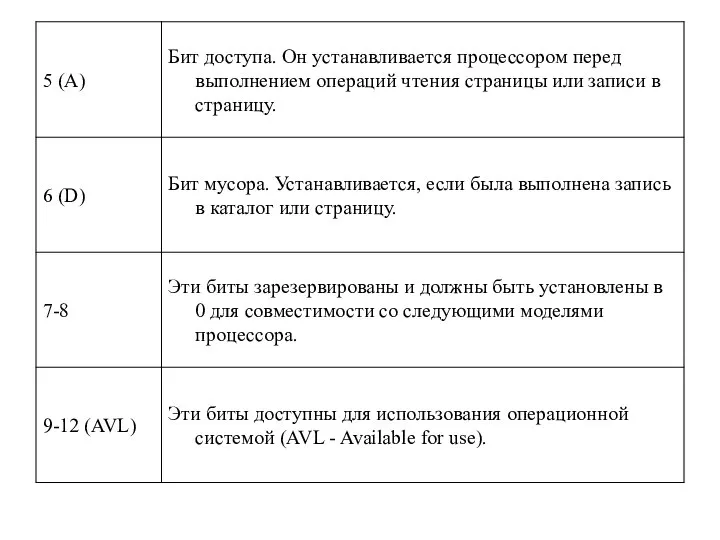

- 26. Назначение бит 0-11 одинаково и для дескриптора таблицы страниц, и для дескриптора страницы. В таблице 1

- 28. Для использования механизма трансляции страниц операционная система должна установить в 1 старший бит системного регистра CR0.

- 29. Каков объем виртуального адресного пространства? Для индекса дескриптора отведено 13 бит. Отсюда следует, что в дескрипторной

- 30. В процессорах, начиная с Pentium, страницы могут иметь размер 4Кбайт или 4Мбайт (эта возможность называется расширением

- 34. Скачать презентацию

Программная модель современных процессоров х86

Современные представители семейства х86 являются 32-битными процессорами;

Программная модель современных процессоров х86

Современные представители семейства х86 являются 32-битными процессорами;

Разрядность адреса определяет, сколько битов (16, 32 или 64) используется в регистрах, формирующих адрес данных или инструкций, расположенных в памяти. Разрядность данных определяет, сколько битов используется в инструкциях, оперирующих словами. Каждому режиму работы процессоров соответствуют своя разрядность, применяемая по умолчанию. При необходимости для каждой исполняемой инструкции разрядность адреса или/и операнда может изменяться с помощью специальных префиксов (байтов перед кодом инструкции).

32-битные регистры процессоров позволяют непосредственно адресовать до 4 Гбайт памяти. Встроенный блок управления памятью поддерживает механизмы сегментации и страничной трансляции адресов.

Расширения х86-64 и ЕМ64Т в первую очередь предназначены для радикального увеличения

Расширения х86-64 и ЕМ64Т в первую очередь предназначены для радикального увеличения

Процессоры предоставляют четырехуровневую систему привилегий для защиты памяти, ввода-вывода и прерываний, а также механизм переключения задач для многозадачных ОС.

Процессоры могут работать в различных режимах, определяющих возможности адресации памяти и защиты.

Режим работы процессора задается операционной системой с учетом режима работы приложений (задач). У процессоров с 64-битным расширением появляются новые режимы, среди которых есть и режимы, обеспечивающие совместимость с 32-разрядными операционными системами и приложениями. Новые режимы используются только в 64-битных ОС, а полностью их преимущества доступны только 64-битным приложениям.

Режимы работы процессоров

32-битные процессоры могут работать в одном из следующих режимов:

♦

Режимы работы процессоров

32-битные процессоры могут работать в одном из следующих режимов:

♦

♦ Защищенный режим виртуальной адресации (protected virtual address mode), или просто защищенный режим (protected mode). В этом режиме у процессора включаются механизмы сегментации и страничной трансляции. Механизм сегментации позволяет поддерживать виртуальную память объемом до 64 Тбайт. На практике используется только страничная трансляция, благодаря которой каждой задаче предоставляется до 4 Гбайт виртуального адресного пространства. По умолчанию и адреса, и операнды имеют разрядность 32 бита. В защищенном режиме процессор может выполнять дополнительные инструкции, недоступные в реальном режиме; ряд инструкций, связанных с передачей управления, обработкой прерываний, и некоторые другие выполняются иначе, чем в реальном режиме.

Есть возможность организации 16-разрядного защищенного режима в стиле процессора 80286, но этот режим не представляет интереса.

♦ Режим виртуального процессора 8086 (Virtual 8086 Mode, V86) является особым

♦ Режим виртуального процессора 8086 (Virtual 8086 Mode, V86) является особым

♦ «Нереальный» режим (unreal mode, он же big real mode) — это «неофициальный» режим, который поддерживают все 32-битные процессоры. Он позволяет адресоваться к 4-гигабайтному пространству памяти. В этом режиме инструкции исполняются так же, как и в реальном режиме, но с помощью дополнительных сегментных регистров FS и GS программы получают непосредственный доступ к данным во всей физической памяти.

♦ В режиме системного управления (System Management Mode, SMM) процессор выходит

♦ В режиме системного управления (System Management Mode, SMM) процессор выходит

Для процессоров х86-64 вышеперечисленные режимы объединены понятием legacy mode; кроме того, появился новый режим long mode с двумя подрежимами:

♦ 64-битный режим (64-bit mode) — это режим полной поддержки 64-битной виртуальной адресации и 64-битных расширений регистров. В этом режиме используется только плоская модель памяти (общий сегмент для кода, данных и стека). По умолчанию разрядность адреса составляет 64 бита, а операндов (для большинства инструкций) — 32 бита, однако префиксом (REX) можно заказать 64-битные операнды. Имеется новый способ адресации данных — относительно указателя инструкций. Режим предназначен для использования 64-битными ОС при запуске 64-битных приложений — он включается операционной системой для сегмента кода конкретной задачи;

♦ режим совместимости (compatibility mode) позволяет 64-битным ОС работать с 32-

♦ режим совместимости (compatibility mode) позволяет 64-битным ОС работать с 32-

32-битные ОС используют процессоры х86-64 только в режиме legacy mode (как обычный процессор IA-32).

Пространство памяти (memory space) предназначено для хранения кодов инструкций и данных.

Пространство памяти (memory space) предназначено для хранения кодов инструкций и данных.

Эффективный адрес

При обращении к памяти (к данным), как и при формировании

Эффективный адрес

При обращении к памяти (к данным), как и при формировании

Преобразование адресов

Применительно к памяти различают три адресных пространства: логическое, линейное и

Преобразование адресов

Применительно к памяти различают три адресных пространства: логическое, линейное и

♦ В сегментной модели памяти приложение использует несколько сегментов памяти (для кода, данных, стека) и может переключать используемые сегменты. В этой модели приложение оперирует логическими адресами.

♦ В плоской модели памяти приложению для всех целей выделяется единственный сегмент. В этой модели приложение оперирует линейными адресами. Плоская модель гораздо проще и удобнее в обращении и используется в современных ОС.

Логический адрес состоит из селектора сегмента Seg и эффективного адреса, называемого также смещением (offset). Логический адрес обозначается в форме Seg:Offset. Селектор сегмента хранится в старших 14 битах сегментного регистра (CS, DS, ES, SS, FS или GS), участвующего в адресации конкретного элемента памяти. По значению селектора из специальных таблиц дескрипторов сегментов, хранящихся в памяти, извлекается начальный адрес сегмента. Поскольку каждая задача может иметь до 16К селекторов (214), а смещение, ограниченное размером сегмента, - достигать 4 Гбайт, логическое адресное пространство для каждой задачи может равняться 64 Тбайт. Операционная система может ограничить число доступных сегментов и их конкретные размеры.

Рис. 2. Формирование адреса памяти в 32-битных процессорах: а — в

Рис. 2. Формирование адреса памяти в 32-битных процессорах: а — в

Преобразование логического адреса в физический для 32-битных процессоров иллюстрирует рис. 2.

Преобразование логического адреса в физический для 32-битных процессоров иллюстрирует рис. 2.

В реальном режиме селектор любого сегмента равен адресу его начала, деленому на 16. Чтобы получить адрес в памяти, 16-битное смещение складывают с этим селектором, сдвинутым предварительно влево на 4 разряда. Таким образом, оказывается, что максимальный доступный адрес в реальном режиме 220-1 = 1 048 575.

Формирование линейного адреса

Содержимое сегментного регистра сдвигается влево на 4 бита

Формирование линейного адреса

Содержимое сегментного регистра сдвигается влево на 4 бита

+

19

0

15

0

0

19

0 0 0 0

4

В реальном режиме микропроцессор работает как 8086 с возможностью использования 32-битных

В реальном режиме микропроцессор работает как 8086 с возможностью использования 32-битных

В отличие от 8086 микропроцессоры 286+ в определенных ситуациях генерируют исключения, например, при превышении предела сегмента, который для всех сегментов в реальном режиме - 0FFFFh.

Имеется две фиксированные области в памяти, которые резервируются в режиме реальной адресации:

область инициализации системы

область таблицы прерываний

Ячейки от 00000h до 003FFH резервируются для векторов прерываний. Каждое из 256 возможных прерываний имеет зарезервированный 4-байтовый адрес перехода.

Ячейки от FFFFFFF0H до FFFFFFFFH резервируются для инициализации системы.

Данный механизм образования физического адреса позволяет сделать программное обеспечение перемещаемым, то

Данный механизм образования физического адреса позволяет сделать программное обеспечение перемещаемым, то

Недостатки такой организации памяти:

сегменты бесконтрольно размещаются с любого адреса, кратного 16 (так как содержимое сегментного регистра аппаратно смещается на 4 разряда). Как следствие, программа может обращаться по любым адресам, в том числе и реально не существующим;

сегменты имеют максимальный размер 64 Кбайт;

сегменты могут перекрываться с другими сегментами.

Защищенный режим лишен недостатков реального режима, в нем можно адресоваться к

Защищенный режим лишен недостатков реального режима, в нем можно адресоваться к

В защищенном режиме базовый адрес загружается из дескриптора, хранящегося в таблице, по селектору, загруженному в используемый сегментный регистр.

РАБОТА С АДРЕСАМИ

В защищенном режиме, как и в реальном, логический адрес

РАБОТА С АДРЕСАМИ

В защищенном режиме, как и в реальном, логический адрес

Получение физического адреса в процессоре 80286

Получение физического адреса в процессоре 80286

Согласно этой схеме адресации памяти, селектор содержит номер ячейки таблицы дескрипторов,

Согласно этой схеме адресации памяти, селектор содержит номер ячейки таблицы дескрипторов,

Таким образом, несмотря на то, что компоненты адреса остались, как и в реальном режиме, 16-разрядными, новая схема адресации защищенного режима процессора 80286 позволяет адресовать до 16 Мбайт памяти, так как в результате преобразования получается 24-разрядный физический адрес.

Кроме индекса, используемого для выбора ячейки дескрипторной таблицы при формировании физического адреса, селектор содержит еще два поля

Поле TI (Table Indicator )

бит 2: индикатор таблицы 0/1 — использовать GDT/LDT

Поле RPL

биты 1 – 0: уровень привилегий запроса (RPL)— это число от 0 до 3, указывающее уровень защиты сегмента, для доступа к которому используется данный селектор.

Преобразование адресов в защищённом режиме

Процессор i80386 и выше использует трёхступенчатую

Преобразование адресов в защищённом режиме

Процессор i80386 и выше использует трёхступенчатую

Уровень логического адреса - это первая ступень в схеме преобразования адресов.

Вторая ступень - получение из логического адреса 32-разрядного линейного адреса. Линейный адрес берётся из глобальной или локальной таблицы дескрипторов (GDT или LDT) в зависимости от соответствующего бита селектора (бит 2). Механизм получения линейного адреса напоминает механизм получения 24-разрядного физического адреса в процессоре i80286. Однако линейный адрес не отображается непосредственно на адресную шину памяти, то есть он не является физическим адресом.

Для получения из линейного адреса физического адреса используется третья ступень - механизм страничной адресации. С помощью этого механизма 20 старших бит линейного адреса используются для выбора блока памяти размером 4 килобайта. Такой блок называется страницей физической памяти. Оставшиеся 12 бит линейного адреса представляют собой смещение внутри страницы. Процесс преобразования логического адреса в линейный иллюстрируется рис. 4.

Значение из поля индекса селектора используется в качестве индекса в таблице

Значение из поля индекса селектора используется в качестве индекса в таблице

Преобразование линейного адреса в физический иллюстрируется рис. 5.

32

Процесс вычисления адреса страницы часто называют трансляцией страниц. Старшие 10 бит

Процесс вычисления адреса страницы часто называют трансляцией страниц. Старшие 10 бит

Каталог таблиц страниц содержит дескрипторы таблиц страниц, определяющие физический адрес таблиц страниц. В каталоге таблиц страниц всего может быть 1024 дескриптора. Самих же каталогов может быть сколько угодно, но в каждый момент времени используется только один - тот, на который указывает регистр CR3.

Следующие 10 бит линейного адреса предназначены для индексации таблицы страниц, выбранной с помощью старших 10 бит адреса. Таблица страниц содержит 1024 дескриптора, определяющих физические адреса страниц памяти. Размер одной страницы составляет 4 килобайта, т.е. 4096 байт.

Младшие 12 бит линейного адреса указывают смещение к адресуемому байту внутри страницы.

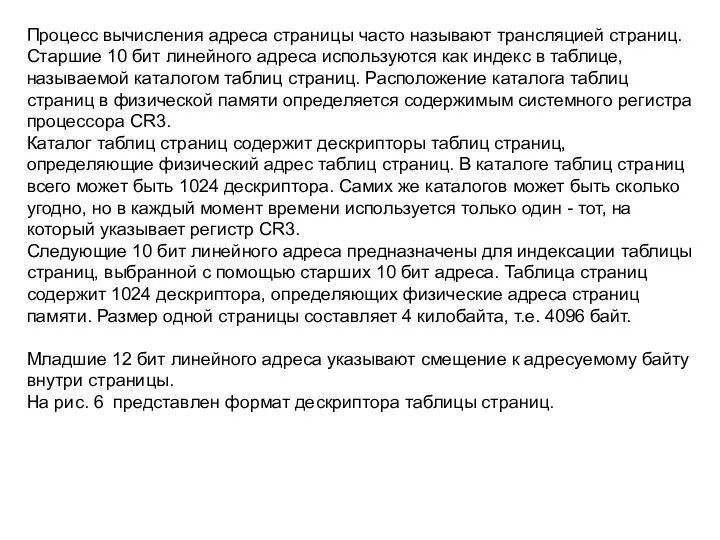

На рис. 6 представлен формат дескриптора таблицы страниц.

Дескриптор таблицы страниц.

Для представления старших 20 битов физического адреса таблицы

Дескриптор таблицы страниц.

Для представления старших 20 битов физического адреса таблицы

Формат дескриптора страницы представлен на рис.7.

Дескриптор страницы.

Назначение бит 0-11 одинаково и для дескриптора таблицы страниц, и для

Назначение бит 0-11 одинаково и для дескриптора таблицы страниц, и для

Для использования механизма трансляции страниц операционная система должна установить в 1

Для использования механизма трансляции страниц операционная система должна установить в 1

Включенный блок страничной трансляции адресов осуществляет трансляцию линейного адреса в физический страницами размером 4 Кбайт (для последних поколений процессоров также возможны страницы размером 2 или 4 Мбайт). Блок трансляции может включаться только в защищенном режиме.

Каков объем виртуального адресного пространства? Для индекса дескриптора отведено 13 бит.

Каков объем виртуального адресного пространства? Для индекса дескриптора отведено 13 бит.

В процессорах, начиная с Pentium, страницы могут иметь размер 4Кбайт или

В процессорах, начиная с Pentium, страницы могут иметь размер 4Кбайт или

Контур.бонус. Программа лояльности для клиентов

Контур.бонус. Программа лояльности для клиентов Теория языка

Теория языка Таблица умножения и деления на 8 Технологический приём анимированная сорбонка

Таблица умножения и деления на 8 Технологический приём анимированная сорбонка Политический процесс

Политический процесс Принципы выделения частей речи в истории языкознания

Принципы выделения частей речи в истории языкознания  Алексей Семёнович Губкин (1816 – 1883)

Алексей Семёнович Губкин (1816 – 1883) Классификация механических муфт

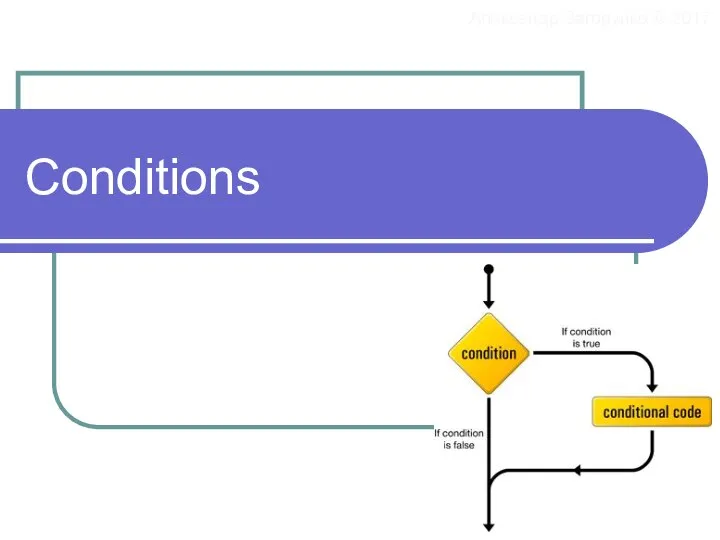

Классификация механических муфт Операци сравнения. Логические операторы

Операци сравнения. Логические операторы Творческий характер культуры

Творческий характер культуры Идеальный гардероб

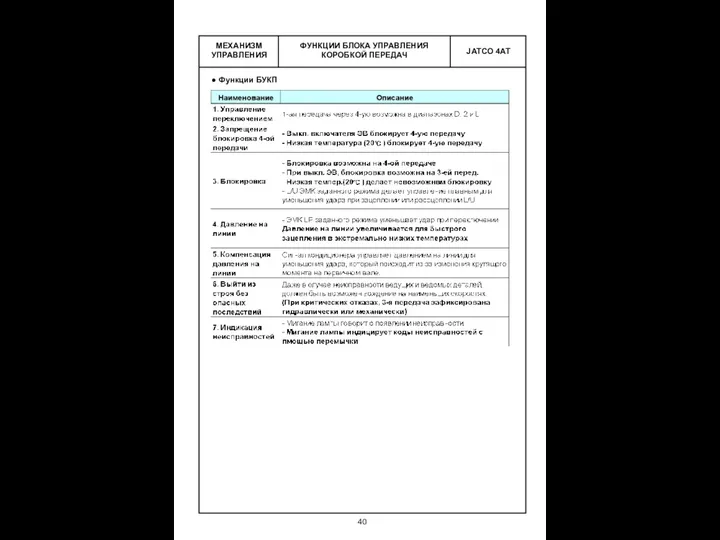

Идеальный гардероб Механизм управления функции блока управления коробкой передач

Механизм управления функции блока управления коробкой передач Золотой век театра и музыки. (Окружающий мир, 4 класс)

Золотой век театра и музыки. (Окружающий мир, 4 класс) Древняя Индия

Древняя Индия Использование динамически выделяемой памяти (Delphi / Pascal, глава 6)

Использование динамически выделяемой памяти (Delphi / Pascal, глава 6) Направления развития экологической маркировки в Республике Беларусь

Направления развития экологической маркировки в Республике Беларусь  Анализ использования материальных ресурсов

Анализ использования материальных ресурсов  Суперкомпьютеры

Суперкомпьютеры Написание заявки на грант. Работа над ошибками

Написание заявки на грант. Работа над ошибками Художественный образ

Художественный образ ПРИЗНАКИ ДЕЛИМОСТИ НА 9 И НА 3 Урок математики в 6 классе учитель Дмитриева О.Е.

ПРИЗНАКИ ДЕЛИМОСТИ НА 9 И НА 3 Урок математики в 6 классе учитель Дмитриева О.Е. Деление двухзначного числа на однозначное - презентация для начальной школы_

Деление двухзначного числа на однозначное - презентация для начальной школы_ Гражданско-правовая статистика

Гражданско-правовая статистика Воды мирового океана - презентация для начальной школы_

Воды мирового океана - презентация для начальной школы_ Презентация "Бог огня Гефест" - скачать презентации по МХК

Презентация "Бог огня Гефест" - скачать презентации по МХК Новый год 2014

Новый год 2014 Национальная и региональная экономическая безопасность

Национальная и региональная экономическая безопасность ЭИС учета и мониторинга выполнения заказов

ЭИС учета и мониторинга выполнения заказов  Тест. Интеллектуальные средства измерений

Тест. Интеллектуальные средства измерений