Содержание

- 2. Современные микропроцессоры 1 Что у нас на орбите? 2 Взлет характеристик 3 Из чего это делается?

- 3. История ЭВМ

- 4. История ЭВМ

- 5. История ЭВМ Первым этапом затронувшим период с 40-х по конец 50-х годов, было создание процессоров с

- 6. История ЭВМ Вторым этапом, с середины 50-х до середины 60-х, стало внедрение транзисторов. Транзисторы монтировались уже

- 7. История ЭВМ Третьим этапом, наступившим в середине 60-х годов, стало использование микросхем. Первоначально использовались микросхемы низкой

- 8. История ЭВМ Затем в микросхемах реализовывались более сложные элементы — элементарные регистры, счётчики, сумматоры, позднее появились

- 9. История ЭВМ Четвёртым этапом, в начале 70-х годов, стало создание, благодаря прорыву в технологии создания БИС

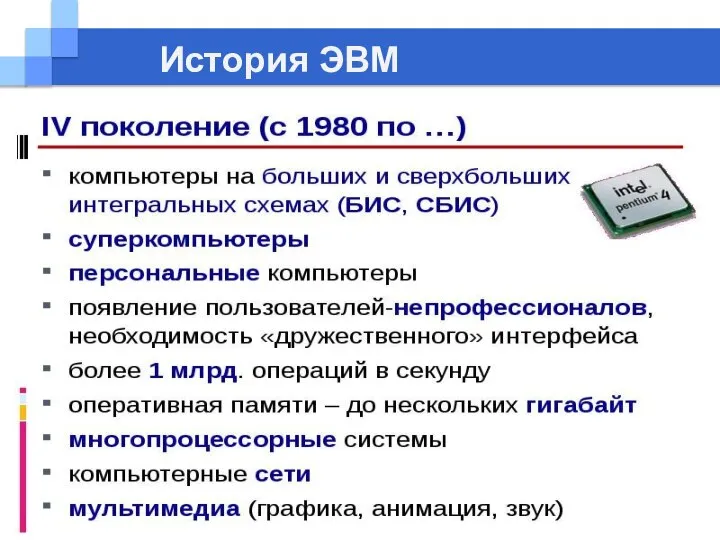

- 10. История ЭВМ

- 11. История ЭВМ

- 12. История ЭВМ

- 13. История архитектур ЭВМ Вернемся к началу… Первая попытка создать программируемый компьютер была предпринята в 1941 году

- 14. История архитектур ЭВМ Компьютер Марк-1 1941 год США Гарвардский университет

- 15. История архитектур ЭВМ Первый компьютер Марк-1 был собран на электромеханических реле.

- 16. История архитектур ЭВМ Чтобы упростить и убыстрить процесс задания программ, Мочли и Экерт стали конструировать новый

- 17. История архитектур ЭВМ Нейман ясно и просто сформулировал общие принципы функционирования компьютеров, т.е. универсальных вычислительных устройств.

- 18. История архитектур ЭВМ В вычислительной машине Дж. Фон Неймана, структура которой представлена на рисунке, ввод-вывод информации

- 19. История архитектур ЭВМ Современные ЭВМ строятся на основе принципа программного управления , предполагающего следующее уточнение понятия

- 20. История архитектур ЭВМ Принфипы фон Неймана: - разнотипные слова информации (данные и команды) различаются по способу

- 21. История архитектур ЭВМ Дальнейшее увеличение производительности вычислительных машин осуществлялось путем совмещения этапов выполнения операций и опережающего

- 22. Современные ЭВМ Современные микропроцессоры представляют весьма сложные устройства. Их работа может существенно отличаться от описанной выше

- 23. Современные ЭВМ В понятие архитектуры микропроцессора входит совокупность некоторых характеристик: 1) структура МП (совокупность компонентов и

- 24. Современные ЭВМ В ходе эволюционного развития архитектур процессоров в состав системы команд вводились и, в силу

- 25. Современные ЭВМ Два типа команд микропроцессора Команды называются скалярными, если входные операнды и результат являются числами

- 26. Современные ЭВМ Примером векторной команды служит команда, при выполнении которой: умножаются два очередных элемента двух массивов,

- 27. Современные ЭВМ Само появление векторных команд обусловлено стремлением ускорить обработку массивов данных за счет исключения затрат

- 28. Современные ЭВМ При сохранении последовательных программ для ускорения обработки применяются суперскалярные процессоры, в которых за счет

- 29. Современные ЭВМ Суперскалярность — архитектура вычислительного ядра, использующая несколько декодеров команд, которые могут нагружать работой множество

- 30. Современные ЭВМ В более поздних системах, таких как Эльбрус-3 и Itanium, используется статпланирование, то есть параллельные

- 31. Современные ЭВМ Стремление использовать присущий большинству программ естественный параллелизм вычисления целочисленных адресных выражений и собственно обработки

- 32. Современные ЭВМ Особенно, конечно, такая возможность ускорения вычислений проявляется при работе с данными 3-D графики и

- 33. Современные ЭВМ В первом приближении, микропроцессор с разнесенной архитектурой, как показано на рисунке, состоит из двух

- 34. Современные ЭВМ Условно эти подпроцессоры называются адресным А-процессором и исполнительным Е-процессором. А- и Е-процессоры имеют собственные

- 35. Современные ЭВМ А-процессор выполняет все адресные вычисления и формирует обращения к памяти по чтению и записи.

- 36. Современные ЭВМ Данные, извлекаемые из памяти, используются либо в А-процессоре, будучи помещенными в FIFO очередь АА,

- 37. Современные ЭВМ При записи данных в память после вычисления адреса А-процессор сразу отправляет адрес в FIFO

- 38. Современные ЭВМ Разнесенная архитектура позволяет достигать при скалярной обработке производительности, характерной для векторных процессоров, за счет

- 39. Классификация архитектур микропроцессоров Два типа архитектур микропроцессоров Анализ кода программ, генерируемого компиляторами языков высокого уровня, показал,

- 40. Классификация архитектур микропроцессоров Два типа архитектур микропроцессоров Другим обстоятельством, фактически приведшим к появлению RISC-процессоров, было развитие

- 41. Классификация архитектур микропроцессоров Два типа архитектур микропроцессоров Каждая такая команда единообразно разбивается на небольшое количество этапов

- 42. Классификация архитектур микропроцессоров Два типа архитектур микропроцессоров После обособления RISC-процессоров в отдельный класс, процессоры с традиционными

- 43. Классификация архитектур микропроцессоров В настоящее время на основе разработок компаний NexGen и AMD, подхваченных компанией Intel,

- 44. Классификация архитектур микропроцессоров Примером такого подхода могут служить микропроцессоры Nx586 (NexGen), K5, Кб (AMD), Pentium (Intel),

- 45. Классификация архитектур микропроцессоров В следующей лекции более подробно будут рассмотрены следующие темы: Разновидности микропроцссоров микроконтроллеры; сигнальные

- 47. Скачать презентацию

Демографическая ситуация в Приволжском федеральном округе От переписи населения 2004 года численность жителей округа сократилась к началу 2011 года на 913,5 тыс. человек, или на 2,9 процента и составила 30241,5 тыс. человек. З

Демографическая ситуация в Приволжском федеральном округе От переписи населения 2004 года численность жителей округа сократилась к началу 2011 года на 913,5 тыс. человек, или на 2,9 процента и составила 30241,5 тыс. человек. З Введение в предмет физики. Кинематика материальной точки

Введение в предмет физики. Кинематика материальной точки Презентация Требования к лицам, поступающим на гражданскую службу в таможенные органы России

Презентация Требования к лицам, поступающим на гражданскую службу в таможенные органы России  Система Национальных Счетов ВВП (Gross Domestic Product) ВНП (Gross National Product) Для расчета ВВП может быть использовано три метода: по расхода

Система Национальных Счетов ВВП (Gross Domestic Product) ВНП (Gross National Product) Для расчета ВВП может быть использовано три метода: по расхода Расширенный поиск в НКРЯ

Расширенный поиск в НКРЯ Выполнили: студентки 3-го курса ФТД группы Т-084 Лоренгель Татьяна Барякинская Екатерина Пикалёва Валерия Шатикова Ирина

Выполнили: студентки 3-го курса ФТД группы Т-084 Лоренгель Татьяна Барякинская Екатерина Пикалёва Валерия Шатикова Ирина  Муниципальное общеобразовательное учреждение «МОУ СОШ № 6 г.Вольска Саратовской области» Иконы Богородицы в истории России Вы

Муниципальное общеобразовательное учреждение «МОУ СОШ № 6 г.Вольска Саратовской области» Иконы Богородицы в истории России Вы мое призвание УЧИТЬ!!! - презентация для начальной школы

мое призвание УЧИТЬ!!! - презентация для начальной школы Тест по МХК. 9 класс. Азбука архитектуры

Тест по МХК. 9 класс. Азбука архитектуры Получение и передача переменного электрического тока. Трансформатор

Получение и передача переменного электрического тока. Трансформатор Ремонт столовых у буфетов ДЦ-1 КХЦ

Ремонт столовых у буфетов ДЦ-1 КХЦ Презентация на тему "Развитие зародыша и плода. Беременность и роды" - скачать презентации по Медицине

Презентация на тему "Развитие зародыша и плода. Беременность и роды" - скачать презентации по Медицине 12 апреля - Международный день космонавтики Сегодня весь мир отмечает знаменательный для человечества день! Ровно 50 лет назад состо

12 апреля - Международный день космонавтики Сегодня весь мир отмечает знаменательный для человечества день! Ровно 50 лет назад состо Важнейшее христианское таинство - крещение

Важнейшее христианское таинство - крещение Будда реальний і Будда із легенд

Будда реальний і Будда із легенд Тема: « Предмет и задачи этнопедагогики»

Тема: « Предмет и задачи этнопедагогики» Нормы таможенного законодательства XIX века. Подготовила: Шмакова Татьяна, ЮФ-104

Нормы таможенного законодательства XIX века. Подготовила: Шмакова Татьяна, ЮФ-104 Классификация организмов. История создания современной классификации

Классификация организмов. История создания современной классификации Крито-микенская культура (III-II тыс. до н. э.)

Крито-микенская культура (III-II тыс. до н. э.) Черхаркашглотская Священная Империя

Черхаркашглотская Священная Империя Информационные технологии в сфере сервиса и туризма

Информационные технологии в сфере сервиса и туризма Механизмы отогенеза

Механизмы отогенеза  Актерское мастерство

Актерское мастерство Процессор. Что такое процессор?

Процессор. Что такое процессор? Программа праздника 8 Марта

Программа праздника 8 Марта Презентация на тему "Черты современного урока с точки зрения повышения познавательной активности учащихся" - скачать презент

Презентация на тему "Черты современного урока с точки зрения повышения познавательной активности учащихся" - скачать презент Инструкция по совершенствованию регионализации перинатальной помощи в Республики

Инструкция по совершенствованию регионализации перинатальной помощи в Республики Российско-сирийские отношения

Российско-сирийские отношения