Содержание

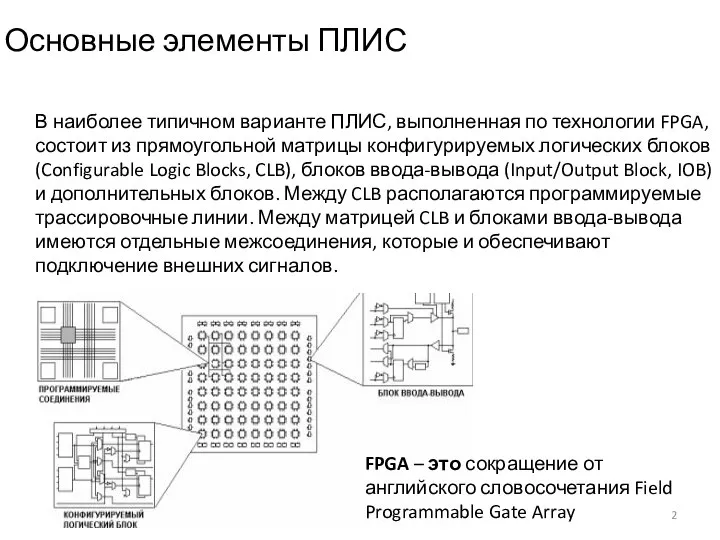

- 2. Основные элементы ПЛИС В наиболее типичном варианте ПЛИС, выполненная по технологии FPGA, состоит из прямоугольной матрицы

- 3. Основные элементы ПЛИС Современные ПЛИС также содержат блоки памяти (BRAM), секции цифровой обработки сигналов (DSP) и

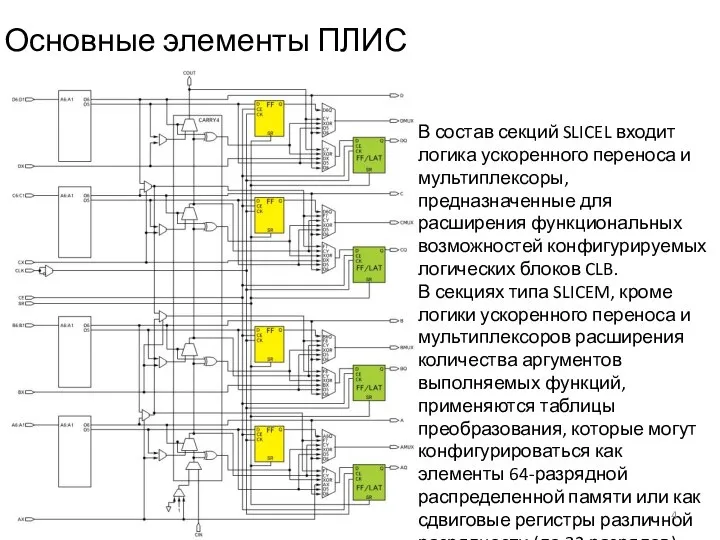

- 4. В состав секций SLICEL входит логика ускоренного переноса и мультиплексоры, предназначенные для расширения функциональных возможностей конфигурируемых

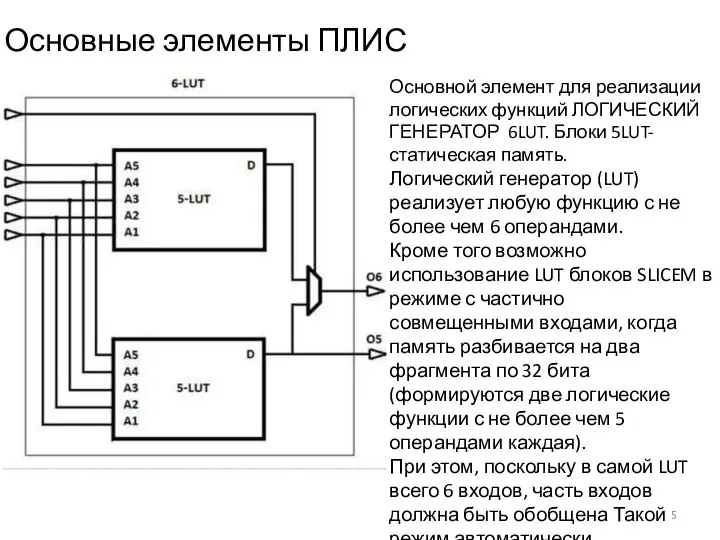

- 5. Основной элемент для реализации логических функций ЛОГИЧЕСКИЙ ГЕНЕРАТОР 6LUT. Блоки 5LUT- статическая память. Логический генератор (LUT)

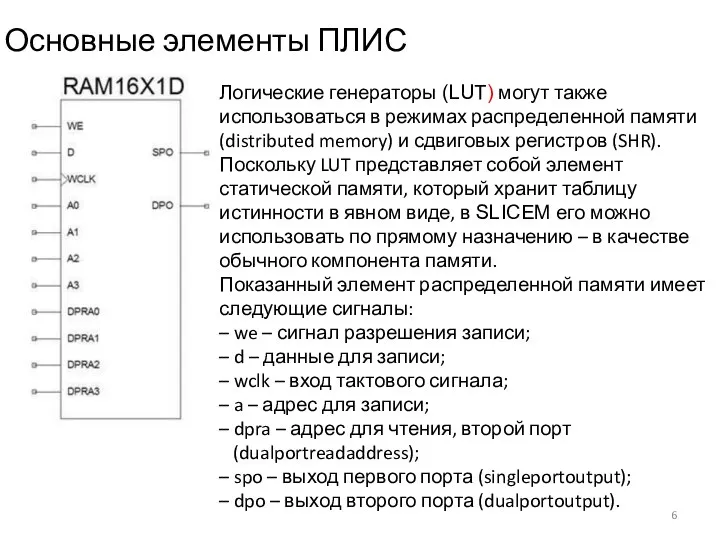

- 6. Логические генераторы (LUT) могут также использоваться в режимах распределенной памяти (distributed memory) и сдвиговых регистров (SHR).

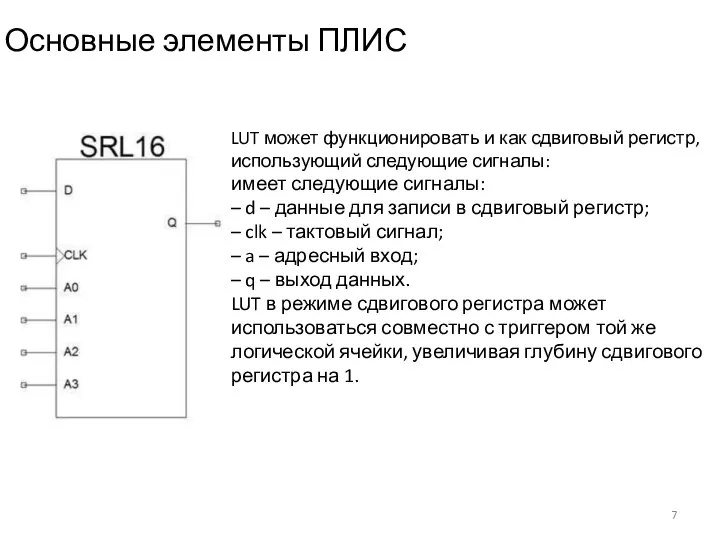

- 7. LUT может функционировать и как сдвиговый регистр, использующий следующие сигналы: имеет следующие сигналы: – d –

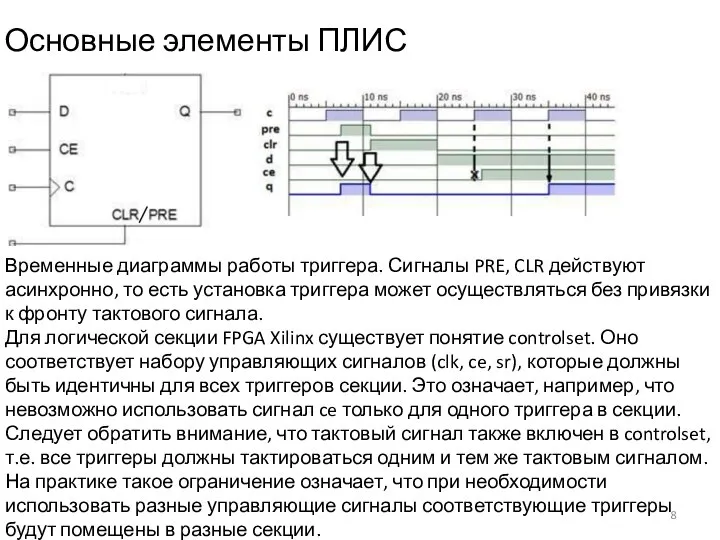

- 8. Временные диаграммы работы триггера. Сигналы PRE, CLR действуют асинхронно, то есть установка триггера может осуществляться без

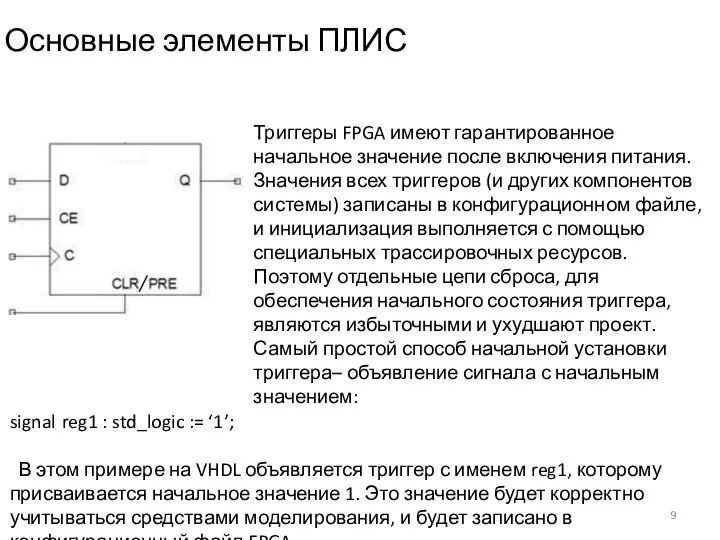

- 9. Триггеры FPGA имеют гарантированное начальное значение после включения питания. Значения всех триггеров (и других компонентов системы)

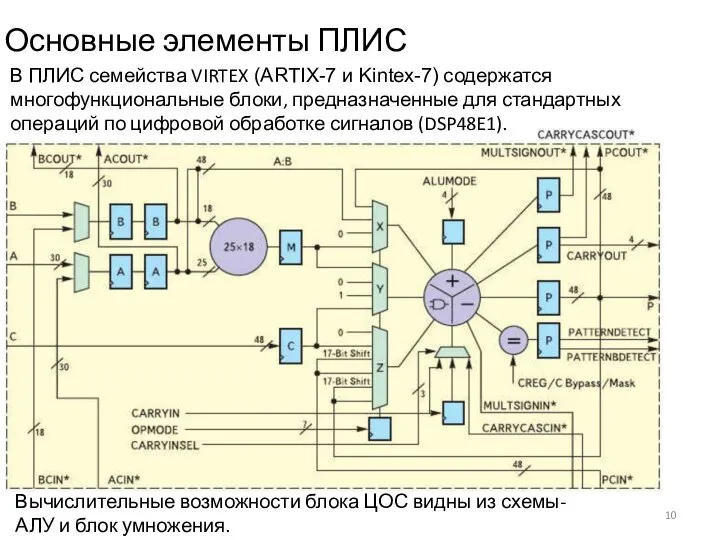

- 10. Основные элементы ПЛИС В ПЛИС семейства VIRTEX (ARTIX-7 и Kintex-7) содержатся многофункциональные блоки, предназначенные для стандартных

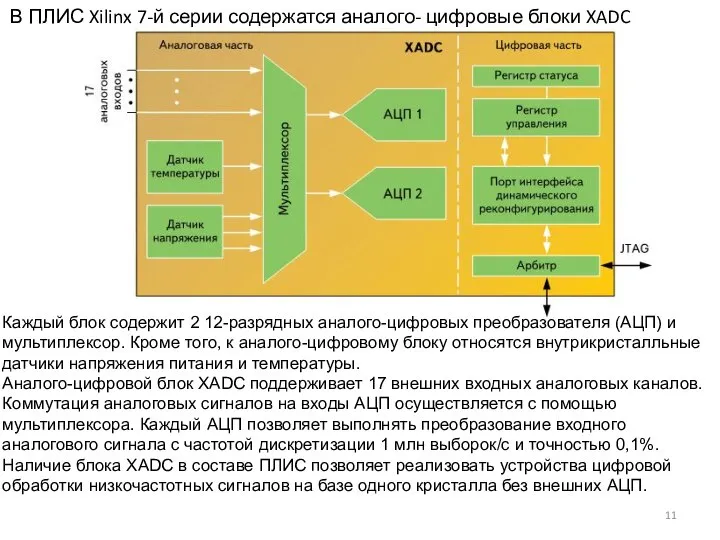

- 11. В ПЛИС Xilinx 7-й серии содержатся аналого- цифровые блоки XADC Каждый блок содержит 2 12-разрядных аналого-цифровых

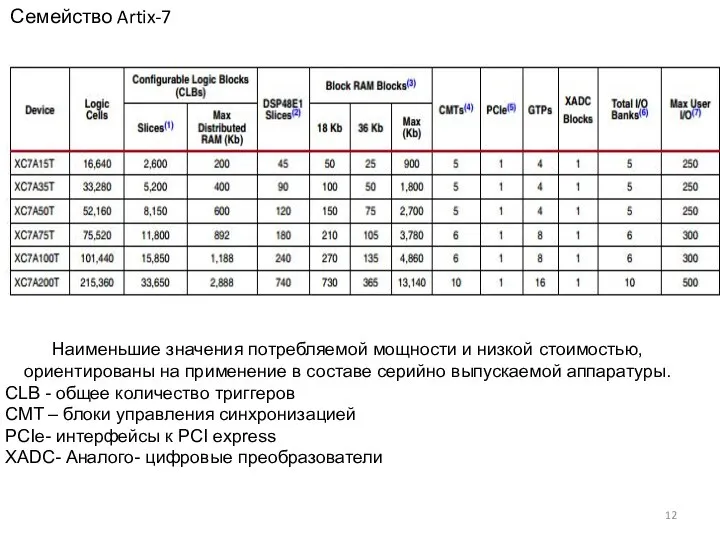

- 12. Семейство Artix-7 Наименьшие значения потребляемой мощности и низкой стоимостью, ориентированы на применение в составе серийно выпускаемой

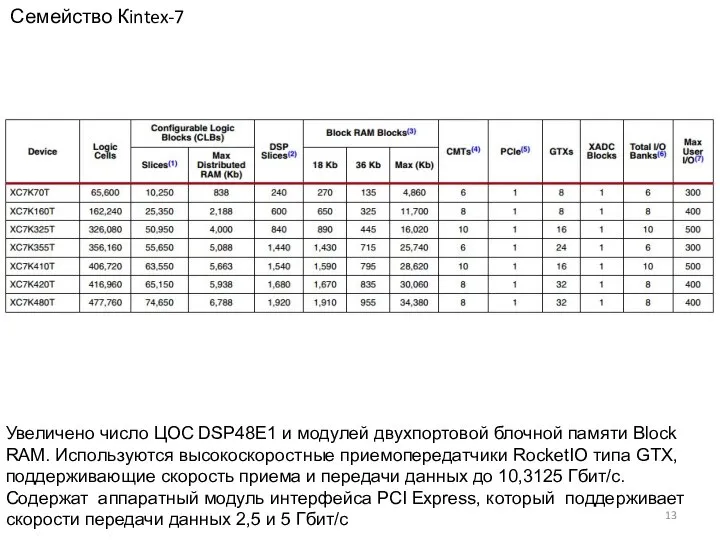

- 13. Семейство Кintex-7 Увеличено число ЦОС DSP48E1 и модулей двухпортовой блочной памяти Block RAM. Используются высокоскоростные приемопередатчики

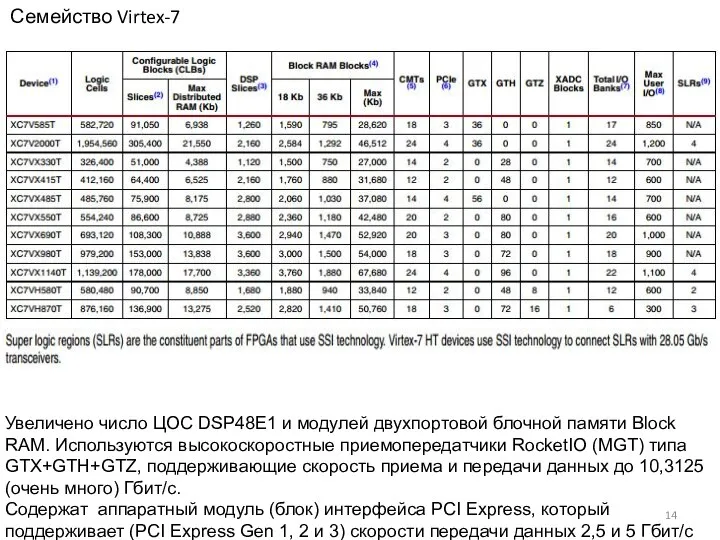

- 14. Семейство Virtex-7 Увеличено число ЦОС DSP48E1 и модулей двухпортовой блочной памяти Block RAM. Используются высокоскоростные приемопередатчики

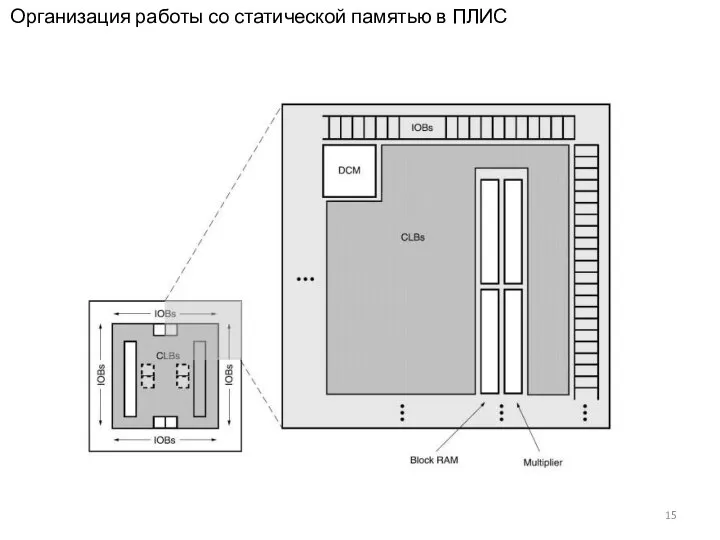

- 15. Организация работы со статической памятью в ПЛИС

- 16. Работа со статической памятью Внутри ПЛИС Xilinx есть специальный аппаратный ресурс – блочная память или BRAM

- 17. Работа со статической памятью Сравнивая блочную и распределенную память, надо сказать следующее: Блочная память – это

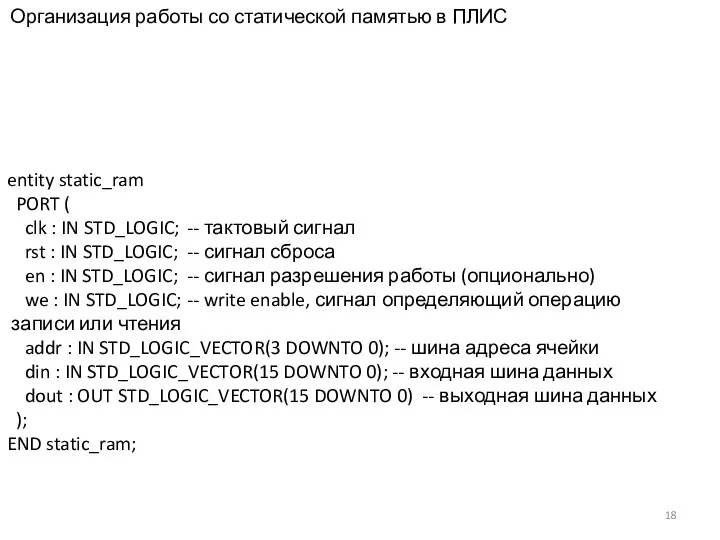

- 18. Организация работы со статической памятью в ПЛИС entity static_ram PORT ( clk : IN STD_LOGIC; --

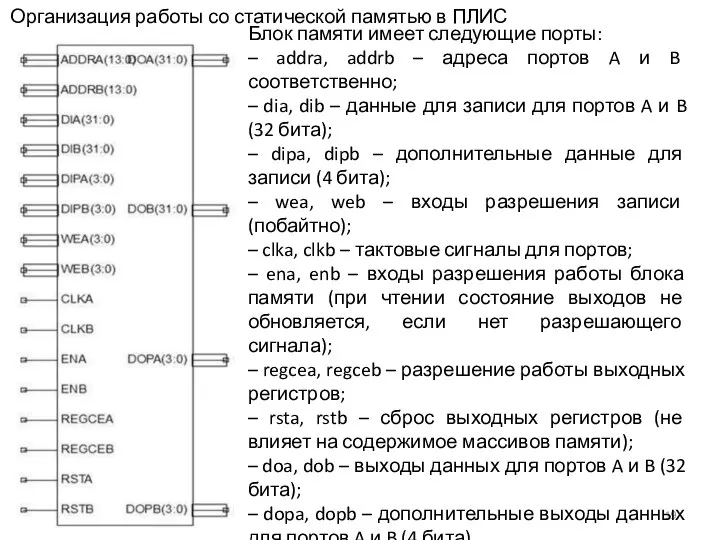

- 19. Организация работы со статической памятью в ПЛИС Блок памяти имеет следующие порты: – addra, addrb –

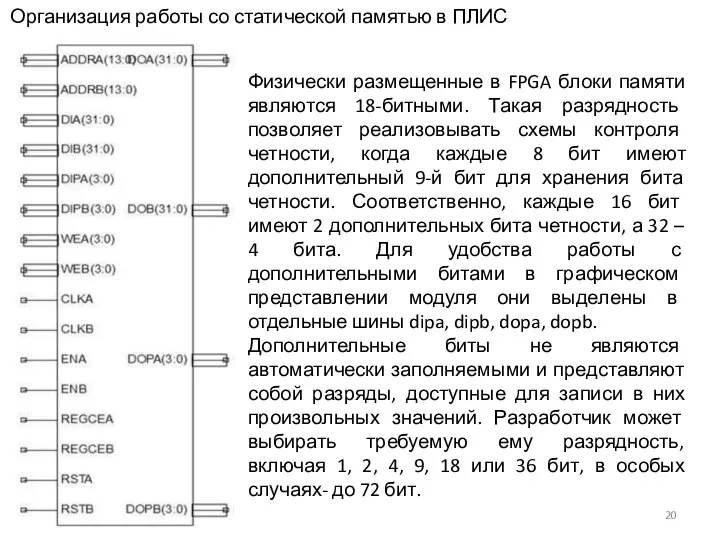

- 20. Организация работы со статической памятью в ПЛИС Физически размещенные в FPGA блоки памяти являются 18-битными. Такая

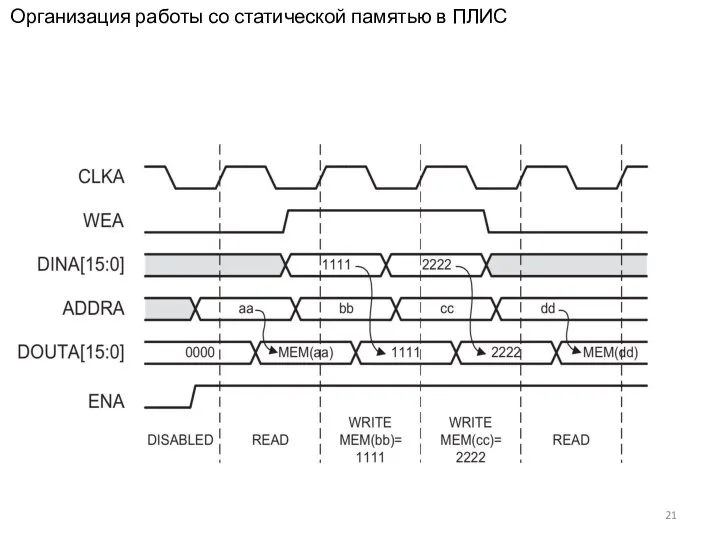

- 21. Организация работы со статической памятью в ПЛИС

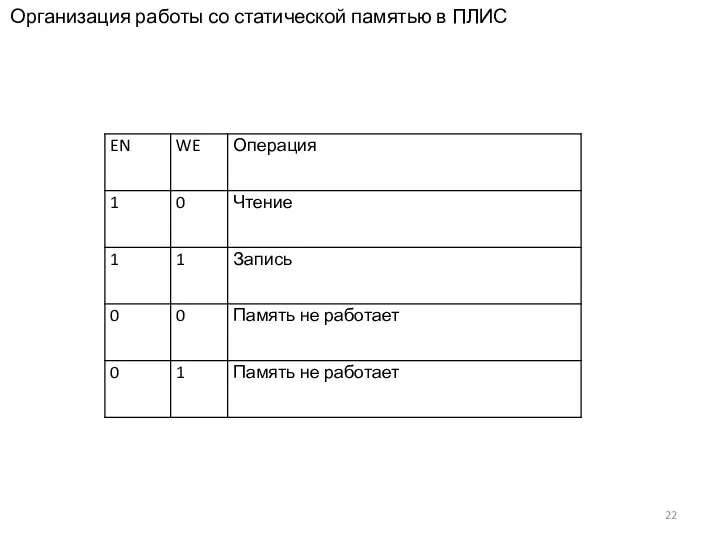

- 22. Организация работы со статической памятью в ПЛИС

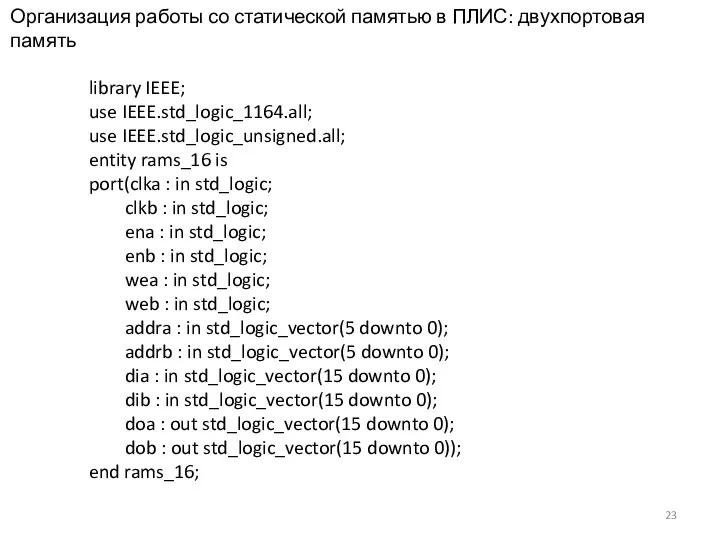

- 23. Организация работы со статической памятью в ПЛИС: двухпортовая память library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity

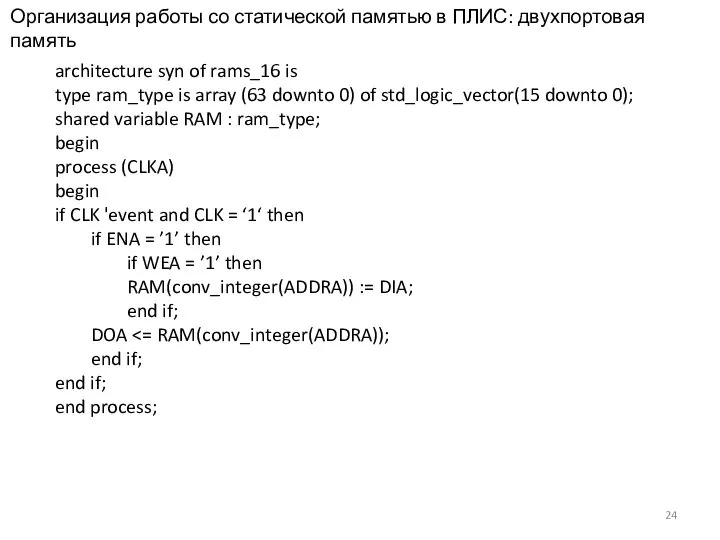

- 24. Организация работы со статической памятью в ПЛИС: двухпортовая память architecture syn of rams_16 is type ram_type

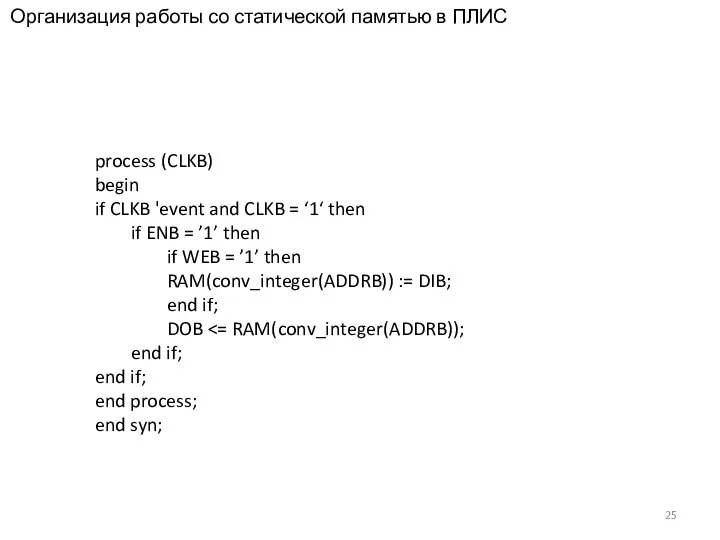

- 25. Организация работы со статической памятью в ПЛИС process (CLKB) begin if CLKB 'event and CLKB =

- 26. Термин: IP cores (IP-ядра, от англ. Intellectual Property — интеллектуальный продукт. В FPGA (ПЛИС) под Hard

- 27. Термин: Приложение CoreGenerator входит в состав САПР фирмы Xilinx и предлагает разработчику графический интерфейс быстрого конфигурирования

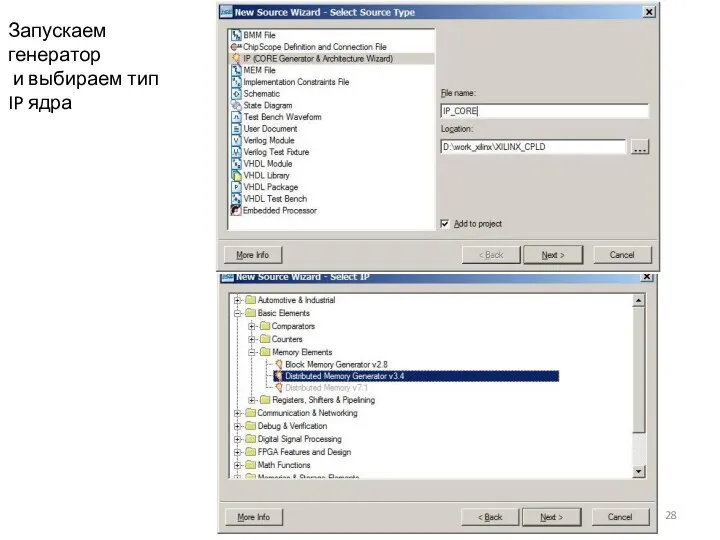

- 28. Запускаем генератор и выбираем тип IP ядра

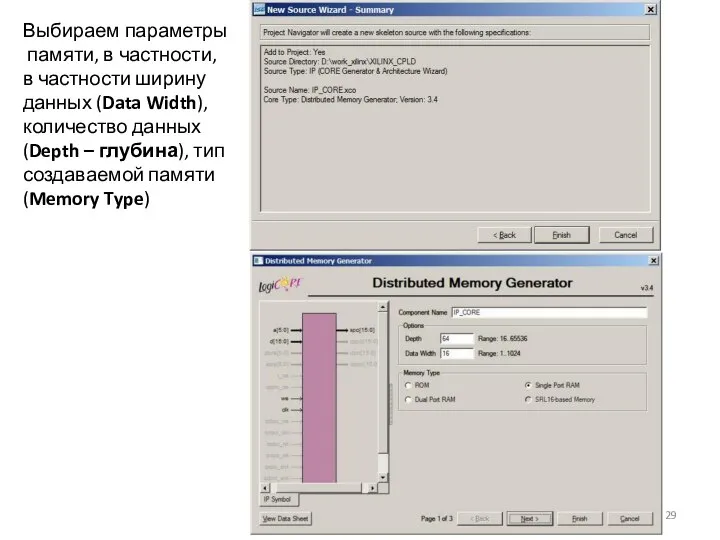

- 29. Выбираем параметры памяти, в частности, в частности ширину данных (Data Width), количество данных (Depth – глубина),

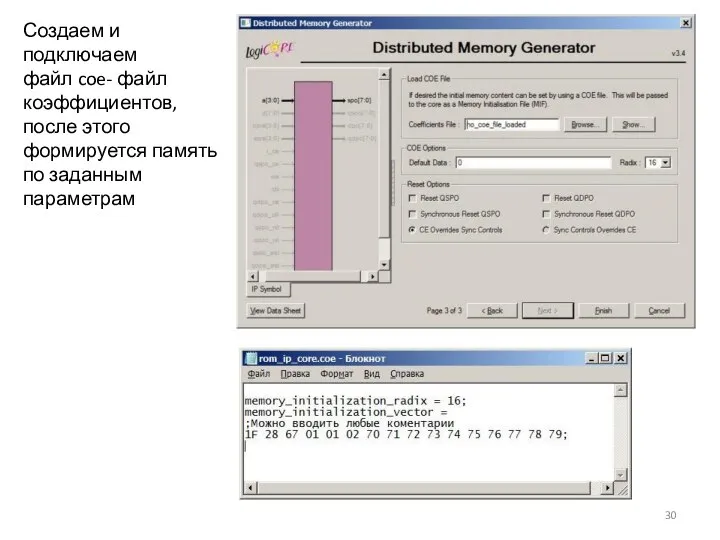

- 30. Создаем и подключаем файл coe- файл коэффициентов, после этого формируется память по заданным параметрам

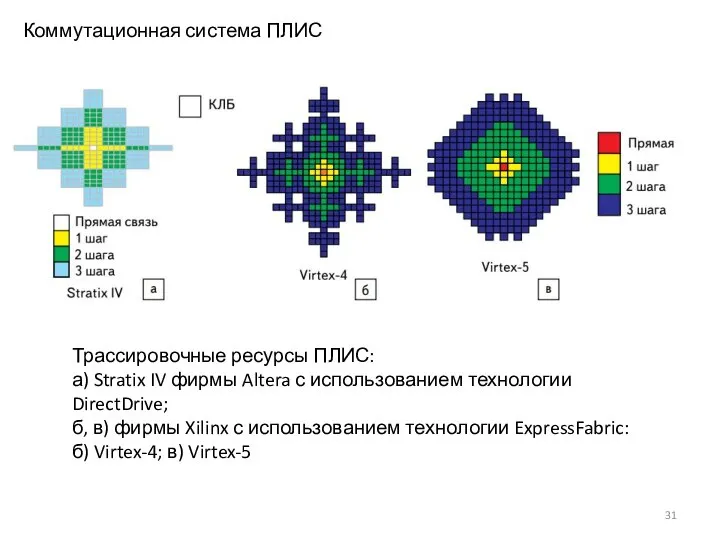

- 31. Коммутационная система ПЛИС Трассировочные ресурсы ПЛИС: а) Stratix IV фирмы Altera с использованием технологии DirectDrive; б,

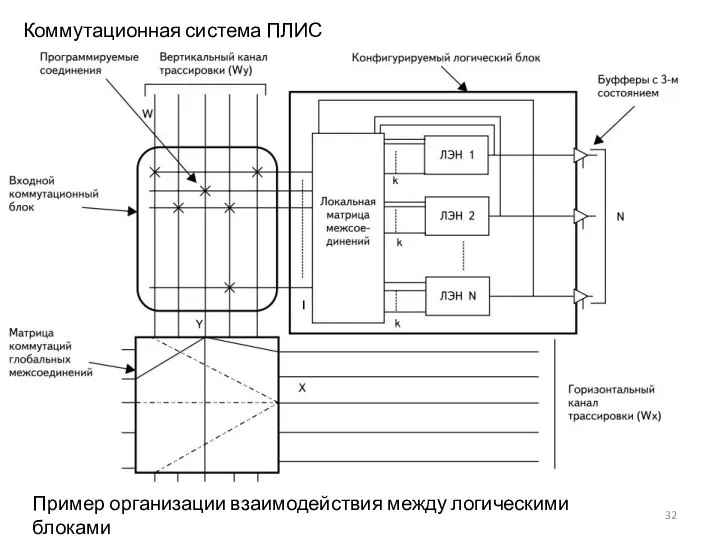

- 32. Коммутационная система ПЛИС Пример организации взаимодействия между логическими блоками

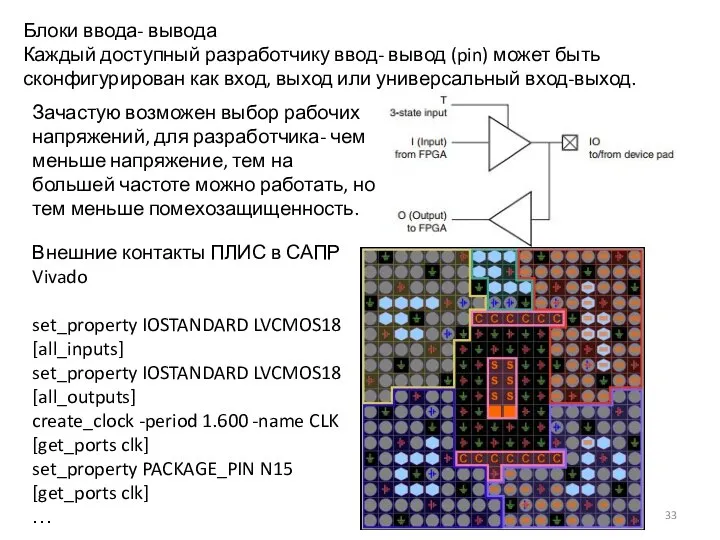

- 33. Блоки ввода- вывода Каждый доступный разработчику ввод- вывод (pin) может быть сконфигурирован как вход, выход или

- 35. Скачать презентацию

Волшебный мир

Волшебный мир Проблемы и инструменты управления проектами Управление человеческими ресурсами в проекте

Проблемы и инструменты управления проектами Управление человеческими ресурсами в проекте  Partizip ii в perfekt

Partizip ii в perfekt Культура – это то, что остается, когда все остальное забыто Автор: Латыпова Карина ученица 9 «А» класса МАОУ «СОШ № 91» г.Перми Руко

Культура – это то, что остается, когда все остальное забыто Автор: Латыпова Карина ученица 9 «А» класса МАОУ «СОШ № 91» г.Перми Руко Основы программирования. Язык программирования С++. Массивы

Основы программирования. Язык программирования С++. Массивы Педагогические Lookи

Педагогические Lookи Геодезическое обеспечение при возведения небоскребов

Геодезическое обеспечение при возведения небоскребов Сотовая связь

Сотовая связь Средства и методы физической культуры для формирования правильной осанки детей младшего школьного возраста

Средства и методы физической культуры для формирования правильной осанки детей младшего школьного возраста Тестовые технологии в курсе Мировой художественной культуры Из опыта работы учителя МХК Туркменского района, с. Малые Ягуры А

Тестовые технологии в курсе Мировой художественной культуры Из опыта работы учителя МХК Туркменского района, с. Малые Ягуры А Проект организации службы технического заказчика в рамках производственно-хозяйственной деятельности ГК «Строй – Плюс»

Проект организации службы технического заказчика в рамках производственно-хозяйственной деятельности ГК «Строй – Плюс» Тесты по ОЦК, кровопотеря

Тесты по ОЦК, кровопотеря Система функций управления Паршутова, Доровских

Система функций управления Паршутова, Доровских  Индивидуальный малоэтажный жилой дом

Индивидуальный малоэтажный жилой дом Секция «Эффективность e-learning – оценка качества» Оценка качества e-learning на основе международных и национальных стандартов

Секция «Эффективность e-learning – оценка качества» Оценка качества e-learning на основе международных и национальных стандартов Знакомство с инструментальными средствами разработки программ на Assembler (на примере WinAsm Studio)

Знакомство с инструментальными средствами разработки программ на Assembler (на примере WinAsm Studio) Основы объектно-ориентированного программирования

Основы объектно-ориентированного программирования Способы преобразования чертежа

Способы преобразования чертежа Контроль и запись переговоров

Контроль и запись переговоров  Станции страховки. Виды и способы организации станций страховки в горах

Станции страховки. Виды и способы организации станций страховки в горах ПОЗНАВАТЕЛЬНАЯ АКТИВНОСТЬ МЛАДШИХ ШКОЛЬНИКОВ Уровни активности: Репродуктивно-подражательная активность Поисково-исполните

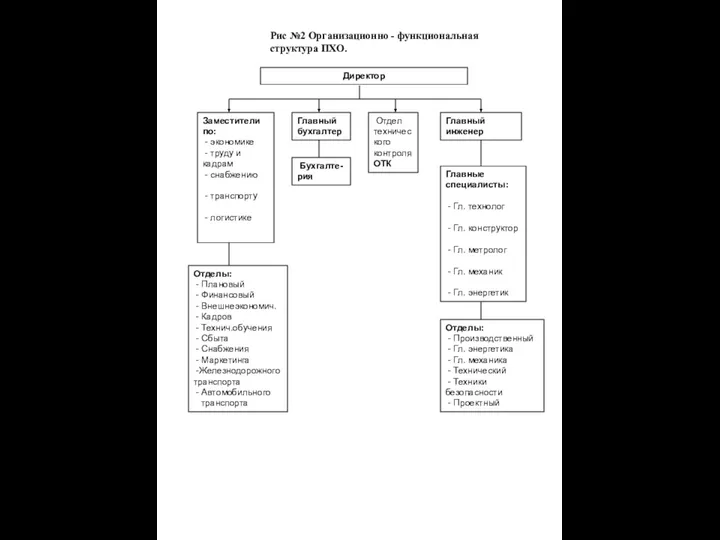

ПОЗНАВАТЕЛЬНАЯ АКТИВНОСТЬ МЛАДШИХ ШКОЛЬНИКОВ Уровни активности: Репродуктивно-подражательная активность Поисково-исполните Структура ПХО

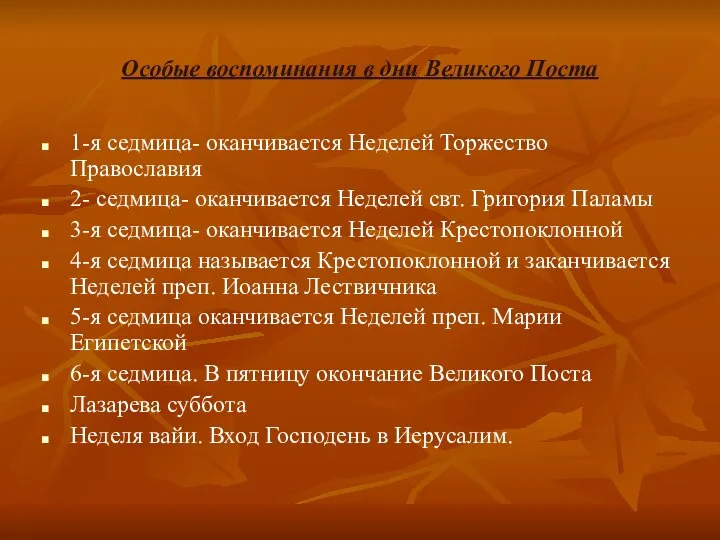

Структура ПХО Особые воспоминания в дни Великого Поста

Особые воспоминания в дни Великого Поста Функции и работа с файлами

Функции и работа с файлами Владивостокский государственный университет экономики и сервиса Институт международного бизнеса и экономики Кафедра «Финанс

Владивостокский государственный университет экономики и сервиса Институт международного бизнеса и экономики Кафедра «Финанс Зарождение концепции самолёта. История науки и техники. Часть 1

Зарождение концепции самолёта. История науки и техники. Часть 1 ООП Перегруженные операции. Объекты-исключения

ООП Перегруженные операции. Объекты-исключения План внедрения подходов ХХI века.

План внедрения подходов ХХI века.