Содержание

- 2. ∙ На базе архитектуры EPIC; ∙ Масштабируемость до 512 процессоров; ∙ Память PC100; ∙ КЭШ 1-го

- 3. Регистры процессора Itanium ∙ 128 64-битных регистров общего назначения GR0-GR127; ∙ 128 82-битных вещественных регистров FR0-FR127;

- 4. Прикладные регистры 1 pr0 pr1 pr2 pr15 pr16 pr63 Предикаты IP 63 0 Указатель команд br0

- 5. Набор системных регистров процессора Itanium

- 6. IPG FET EXP ROT REN WLD REG EXE DET WRB Ядро выполнения 4 однотактовых АЛУ, 2

- 7. Структура процессора Itanium 2 Блоки ПЗ Кэш L3 внутри-кристальный Прогнозирование ветвления Декодирование и управление IA-32 БПА

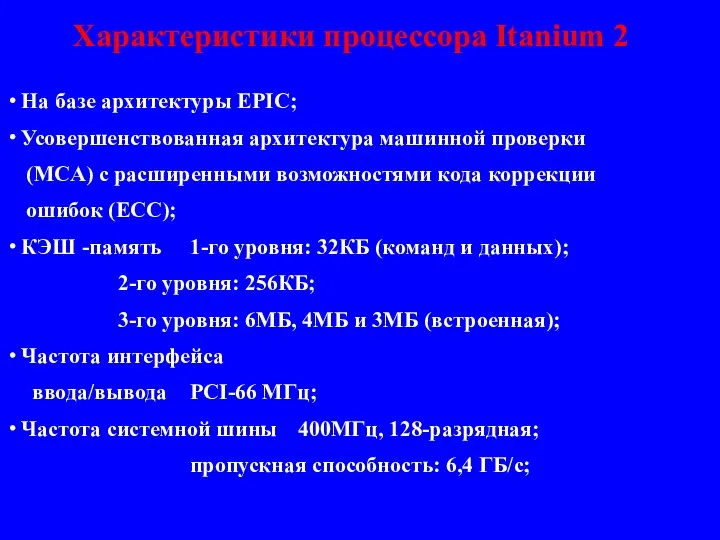

- 8. ∙ На базе архитектуры EPIC; ∙ Усовершенствованная архитектура машинной проверки (MCA) с расширенными возможностями кода коррекции

- 9. Конвейер процессора Itanium 2 Количество ступеней конвейера - 8. Параллельно обрабатывается до 6 команд в течение

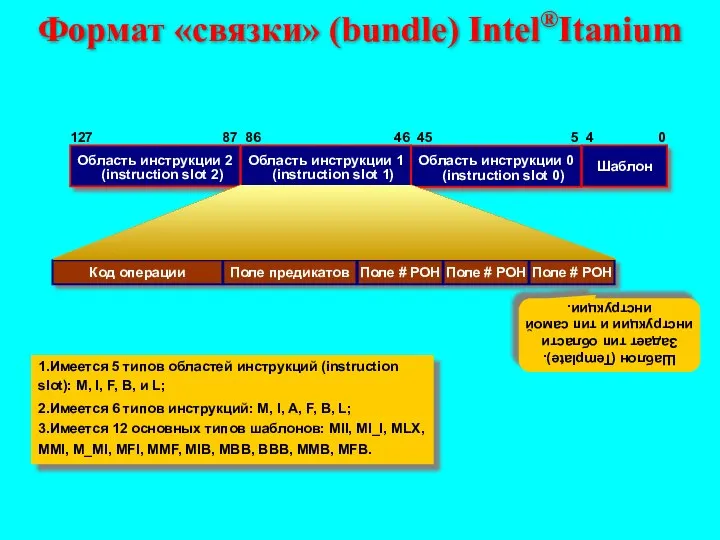

- 10. Формат «связки» (bundle) Intel®Itanium 5 4 46 45 87 86 127 Шаблон (Template). Задает тип области

- 12. Скачать презентацию

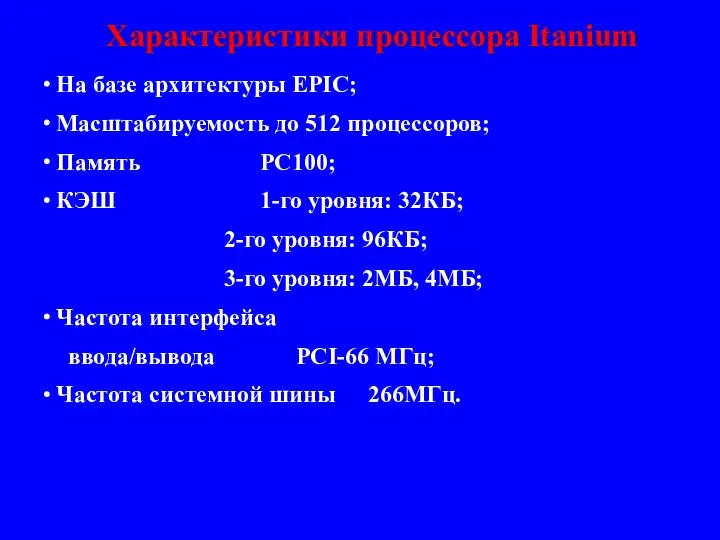

∙ На базе архитектуры EPIC;

∙ Масштабируемость до 512 процессоров;

∙ Память PC100;

∙

∙ На базе архитектуры EPIC;

∙ Масштабируемость до 512 процессоров;

∙ Память PC100;

∙

2-го уровня: 96КБ;

3-го уровня: 2МБ, 4МБ;

∙ Частота интерфейса

ввода/вывода PCI-66 МГц;

∙ Частота системной шины 266МГц.

Характеристики процессора Itanium

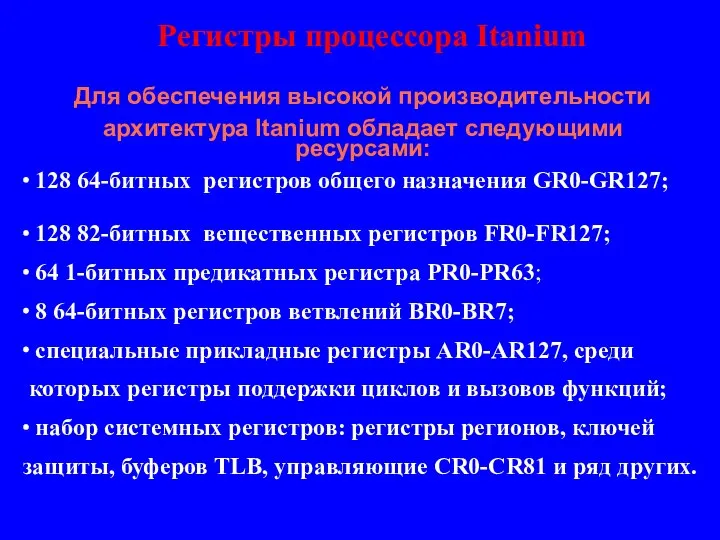

Регистры процессора Itanium

∙ 128 64-битных регистров общего назначения GR0-GR127;

∙ 128

Регистры процессора Itanium

∙ 128 64-битных регистров общего назначения GR0-GR127;

∙ 128

∙ 64 1-битных предикатных регистра PR0-PR63;

∙ 8 64-битных регистров ветвлений BR0-BR7;

∙ специальные прикладные регистры AR0-AR127, среди

которых регистры поддержки циклов и вызовов функций;

∙ набор системных регистров: регистры регионов, ключей

защиты, буферов TLB, управляющие CR0-CR81 и ряд других.

Для обеспечения высокой производительности

архитектура Itanium обладает следующими ресурсами:

Прикладные регистры

1

pr0

pr1

pr2

pr15

pr16

pr63

Предикаты

IP

63 0

Указатель команд

br0

br1

br2

63 0

Регистры ветвлений

br7

CFM

37 0

Маркер текущего фрейма

5 0

Маска пользователя

63

Прикладные регистры

1

pr0

pr1

pr2

pr15

pr16

pr63

Предикаты

IP

63 0

Указатель команд

br0

br1

br2

63 0

Регистры ветвлений

br7

CFM

37 0

Маркер текущего фрейма

5 0

Маска пользователя

63

cpuid0

cpuid1

cpuidn

Идентификаторы процессора

63 0

pmd0

pmd1

pmdm

Регистры данных монитора производительности

RSC

BSP

BSPSTORE

EFLAG

CSD

SSD

CFLG

FSR

FIR

PFS

LC

ar0

ar7

ar16

ar17

ar18

ar19

ar21

ar24

ar25

ar26

ar27

ar28

ar29

ar30

ar32

ar36

ar40

ar44

ar64

ar65

ar66

ar127

EC

ITC

UNAT

RNAT

KR7

KR0

FCR

FDR

CCV

FPSR

Регистры общего назначения

gr0

gr1-3

gr4

63 0

0

gr7

gr8

gr31

gr32

gr127

nats

0

fr0

fr1

fr2-5

fr6-7

fr8

fr31

fr32

fr127

Регистры плавающей точки

0.0

1.0

81 0

gr16

Рег. банк

Набор прикладных регистров процессора Itanium

Не используются при выполнении программ IA–32

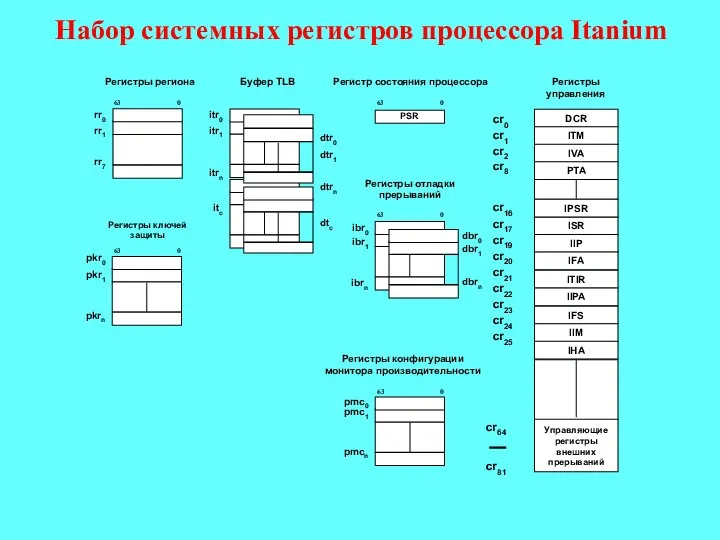

Набор системных регистров процессора Itanium

Набор системных регистров процессора Itanium

IPG

FET

EXP

ROT

REN

WLD

REG

EXE

DET

WRB

Ядро выполнения

4 однотактовых АЛУ, 2 опер. считывания/записи

Загрузка с опережением

Прогнозирование и ветвление

NaT/исключения/

Запись

IPG

FET

EXP

ROT

REN

WLD

REG

EXE

DET

WRB

Ядро выполнения

4 однотактовых АЛУ, 2 опер. считывания/записи

Загрузка с опережением

Прогнозирование и ветвление

NaT/исключения/

Запись

Доставка команд

Распределе-ние 6 команд по 9 портам

Перераспр. регистров

Сохранение содержимого регистров

Входной каскад

Выборка/выборка с

упреждением 6

команд/такт

Предсказание

ветвления

Доставка операндов

Чтение и обход

регистрового файла

Прогнозирова− ние зависимостей

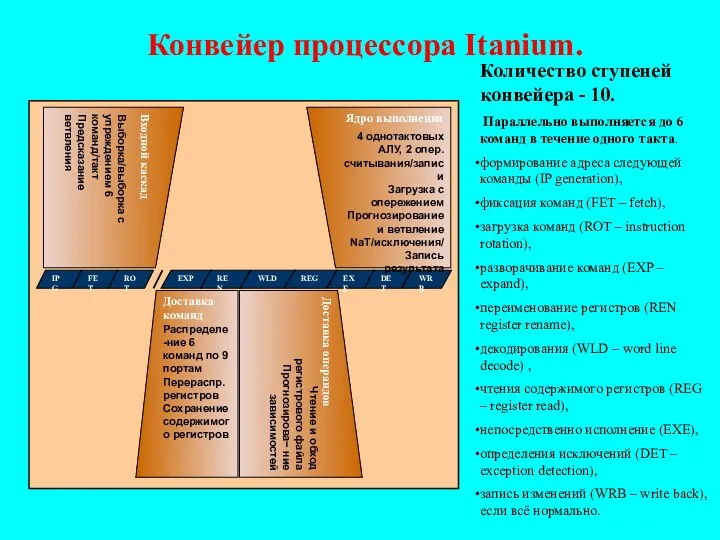

Конвейер процессора Itanium.

Количество ступеней конвейера - 10.

Параллельно выполняется до 6 команд в течение одного такта.

формирование адреса следующей команды (IP generation),

фиксация команд (FET – fetch),

загрузка команд (ROT – instruction rotation),

разворачивание команд (EXP – expand),

переименование регистров (REN register rename),

декодирования (WLD – word line decode) ,

чтения содержимого регистров (REG – register read),

непосредственно исполнение (EXE),

определения исключений (DET – exception detection),

запись изменений (WRB – write back), если всё нормально.

Структура процессора Itanium 2

Блоки ПЗ

Кэш L3 внутри-кристальный

Прогнозирование

ветвления

Декодирование

и

управление IA-32

БПА команд, буфер

Структура процессора Itanium 2

Блоки ПЗ

Кэш L3 внутри-кристальный

Прогнозирование

ветвления

Декодирование

и

управление IA-32

БПА команд, буфер

B

B

B

M

M

I

I

F

F

Стек регистров / вращение регистров

Прогнозирование, обработка исключений

128 целочисленных регистров

128 регистров ПТ

Блоки ветвле-ния

Блоки ветвле-ния

Блоки ветвления

Кэш данных L1

и БПА данных (включая TLB)

ALAT

Функц

блоки ПТ

Контроллер системной шины

Регистры прогнозирования и ветвления

Буфер разделения

8 связок

КЭШ команд L1 и механизм выборки/выборки с упреждением

M

M

Кэш L2

Целочисл. и ММ функц. блоки

Ширина шины 128 бит; 400МГц.

Блоки умножения с накопл.

∙ На базе архитектуры EPIC;

∙ Усовершенствованная архитектура машинной проверки

(MCA) с

∙ На базе архитектуры EPIC;

∙ Усовершенствованная архитектура машинной проверки

(MCA) с

ошибок (ECC);

∙ КЭШ -память 1-го уровня: 32КБ (команд и данных);

2-го уровня: 256КБ;

3-го уровня: 6МБ, 4МБ и 3МБ (встроенная);

∙ Частота интерфейса

ввода/вывода PCI-66 МГц;

∙ Частота системной шины 400МГц, 128-разрядная;

пропускная способность: 6,4 ГБ/с;

Характеристики процессора Itanium 2

Конвейер процессора Itanium 2

Количество ступеней конвейера - 8.

Параллельно обрабатывается до

Конвейер процессора Itanium 2

Количество ступеней конвейера - 8.

Параллельно обрабатывается до

Этапы конвейера

формирование адреса следующей команды (IP generation),

загрузка команд (ROT – instruction rotation),

разворачивание команд (EXP – expand),

переименование регистров (REN register rename),

чтения содержимого регистров (REG – register read),

непосредственно исполнение (EXE),

определения исключений (DET – exception detection),

запись изменений (WRB – writeback), если всё нормально.

По сравнению с Itanium отсутствуют этапы FET и WLD.

Формат «связки» (bundle) Intel®Itanium

5 4

46 45

87 86

127

Шаблон

Формат «связки» (bundle) Intel®Itanium

5 4

46 45

87 86

127

Шаблон

0

1.Имеется 5 типов областей инструкций (instruction slot): M, I, F, B, и L;

2.Имеется 6 типов инструкций: M, I, A, F, B, L;

3.Имеется 12 основных типов шаблонов: MII, MI_I, MLX,

MMI, M_MI, MFI, MMF, MIB, MBB, BBB, MMB, MFB.

3-D принтеры. Принцип действия и области применения

3-D принтеры. Принцип действия и области применения Насоси. Загальна характеристика насосів

Насоси. Загальна характеристика насосів «4П» 4 основные составляющие маркетинга

«4П» 4 основные составляющие маркетинга Класс ПРЕСМЫКАЮЩИЕСЯ REPTILIA

Класс ПРЕСМЫКАЮЩИЕСЯ REPTILIA Программирование на языке C++. Символьные строки

Программирование на языке C++. Символьные строки Физические основы передачи оптического излучения по волоконным световодам

Физические основы передачи оптического излучения по волоконным световодам  Типовые узлы комбинационного типа

Типовые узлы комбинационного типа Гонки балансирующих роботов

Гонки балансирующих роботов Сказка о глупом мышонке - презентация для начальной школы

Сказка о глупом мышонке - презентация для начальной школы Презентация на тему "Звіт директора 2014" - скачать презентации по Педагогике

Презентация на тему "Звіт директора 2014" - скачать презентации по Педагогике Древние образы в народных игрушках

Древние образы в народных игрушках Project Management: Organizational Essential Aspects

Project Management: Organizational Essential Aspects  Талассократические ориентации американской геополитики

Талассократические ориентации американской геополитики ОБЖ 10 КЛАСС

ОБЖ 10 КЛАСС План роботи семінару педагогів-організаторів - презентация для начальной школы

План роботи семінару педагогів-організаторів - презентация для начальной школы Механизмы государственной поддержки на территории Пензенской области

Механизмы государственной поддержки на территории Пензенской области Итоги первого года работы по ФГОС. Методические рекомендации при переходе к работе по новым федеральным стандартам. Е.А.Халиуллин

Итоги первого года работы по ФГОС. Методические рекомендации при переходе к работе по новым федеральным стандартам. Е.А.Халиуллин Школьные годы чудесные. Советы новоиспечённым педагогам

Школьные годы чудесные. Советы новоиспечённым педагогам Бизнес-слой. Метамодель бизнес-слоя

Бизнес-слой. Метамодель бизнес-слоя Российское движение школьников. Военно-патриотическое направление

Российское движение школьников. Военно-патриотическое направление Метод проецирования. Ортогональный чертеж точки, прямой линии и плоскости

Метод проецирования. Ортогональный чертеж точки, прямой линии и плоскости Риэлтор в социальных сетях

Риэлтор в социальных сетях Різдвяні традиції. Кутя

Різдвяні традиції. Кутя Фактический состав ЮРИДИЧЕСКИХ ФАКТОВ Подготовила студентка 2 курса Группы ЮБ03/1303 БРАГИНА АННА

Фактический состав ЮРИДИЧЕСКИХ ФАКТОВ Подготовила студентка 2 курса Группы ЮБ03/1303 БРАГИНА АННА  Модернизация рабочего органа автогрейдера

Модернизация рабочего органа автогрейдера Триггер. D-триггер. Программирование в Lab View и в Multisim

Триггер. D-триггер. Программирование в Lab View и в Multisim Деяние. Главная мысль

Деяние. Главная мысль Лингвострановедческий аспект обучения иностранному языку как средство повышения мотивации к его изучению

Лингвострановедческий аспект обучения иностранному языку как средство повышения мотивации к его изучению