Содержание

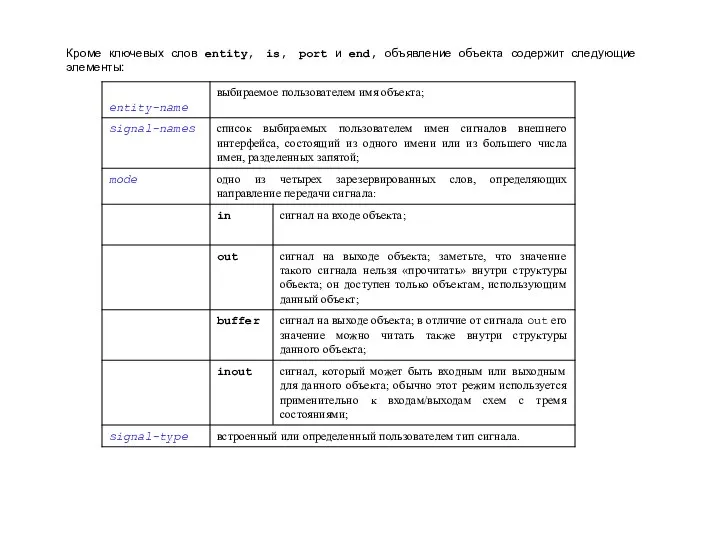

- 4. Кроме ключевых слов entity, is, port и end, объявление объекта содержит следующие элементы:

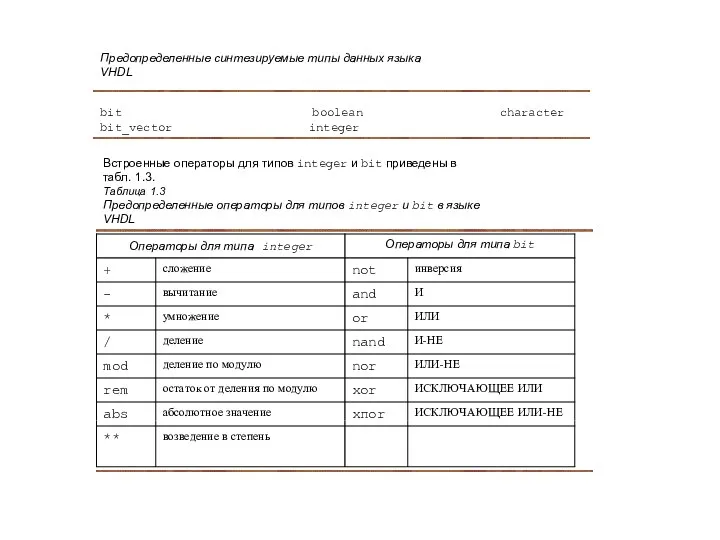

- 5. Предопределенные синтезируемые типы данных языка VHDL bit boolean character bit_vector integer Встроенные операторы для типов integer

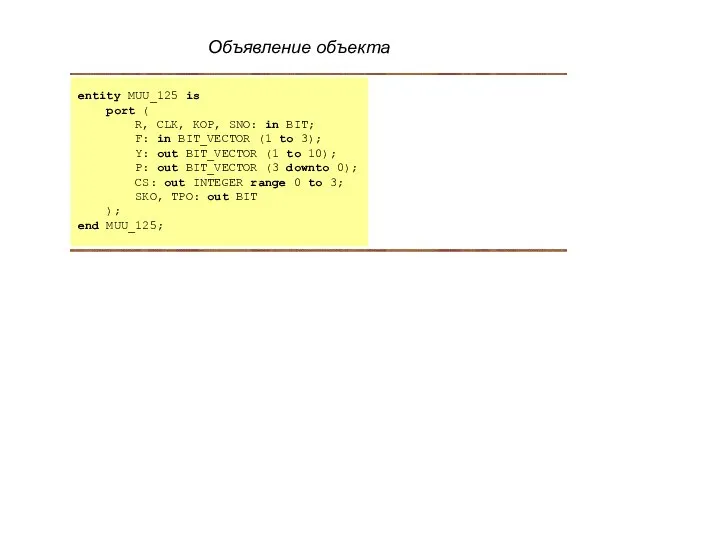

- 6. entity MUU_125 is port ( R, CLK, KOP, SNO: in BIT; F: in BIT_VECTOR (1 to

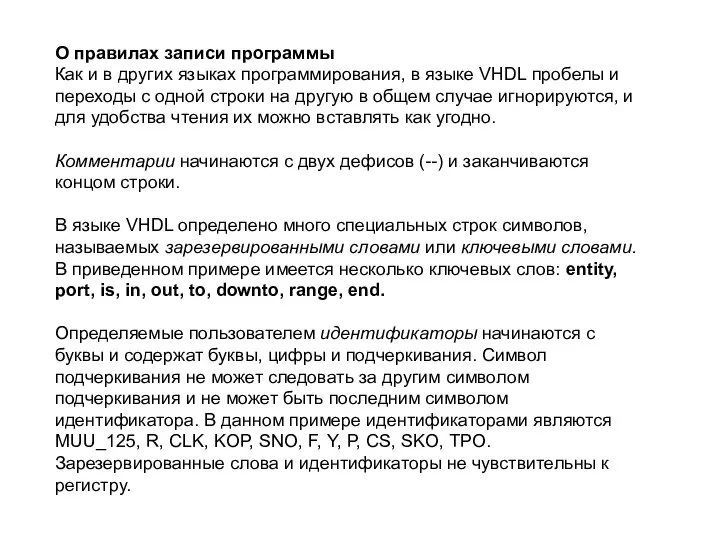

- 7. О правилах записи программы Как и в других языках программирования, в языке VHDL пробелы и переходы

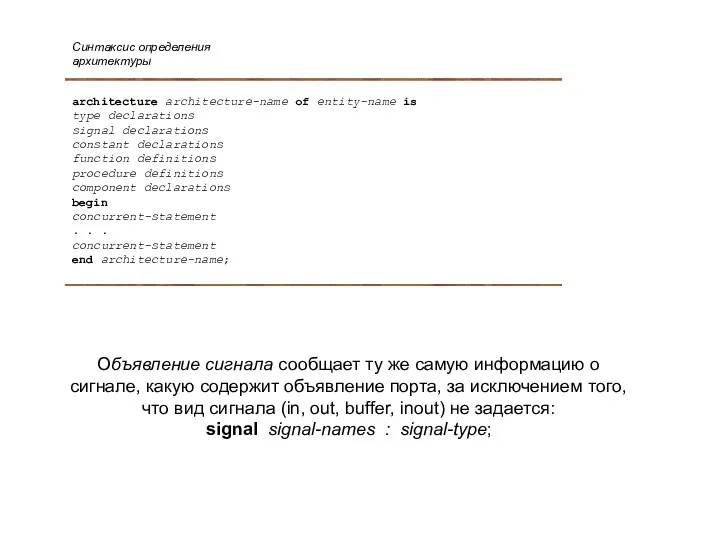

- 8. Синтаксис определения архитектуры architecture architecture-name of entity-name is type declarations signal declarations constant declarations function definitions

- 9. Выделяют следующие стили проектирования и описания схем: структурный, потоковый, поведенческий, смешанный. Элементы потокового проектирования В потоковых

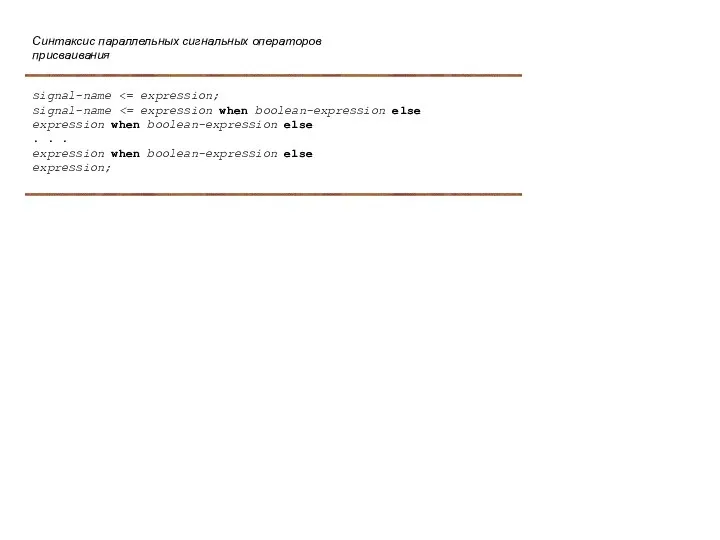

- 10. Синтаксис параллельных сигнальных операторов присваивания signal-name signal-name expression when boolean-expression else . . . expression when

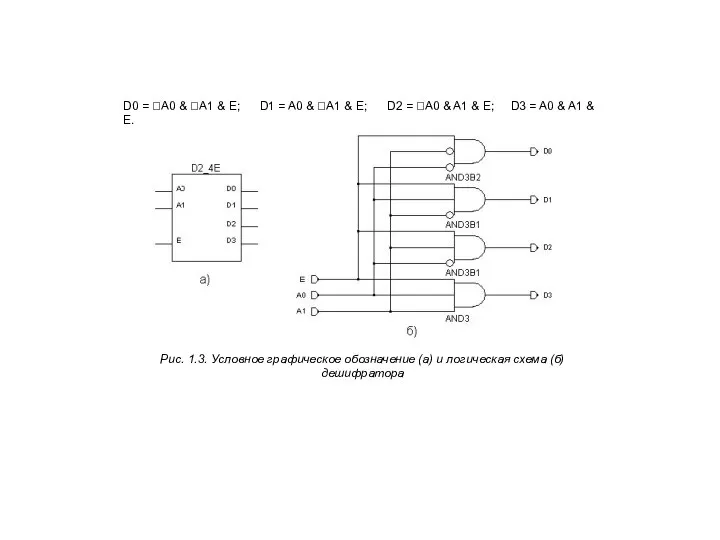

- 11. D0 = A0 & A1 & E; D1 = A0 & A1 & E; D2 =

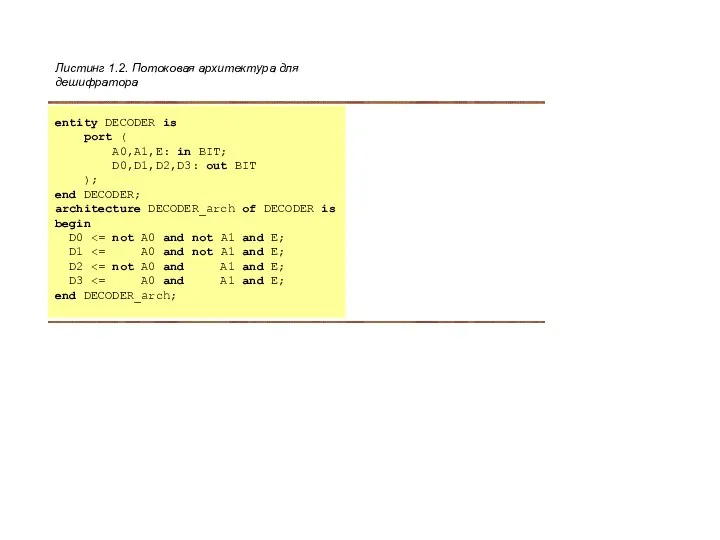

- 12. Листинг 1.2. Потоковая архитектура для дешифратора entity DECODER is port ( A0,A1,E: in BIT; D0,D1,D2,D3: out

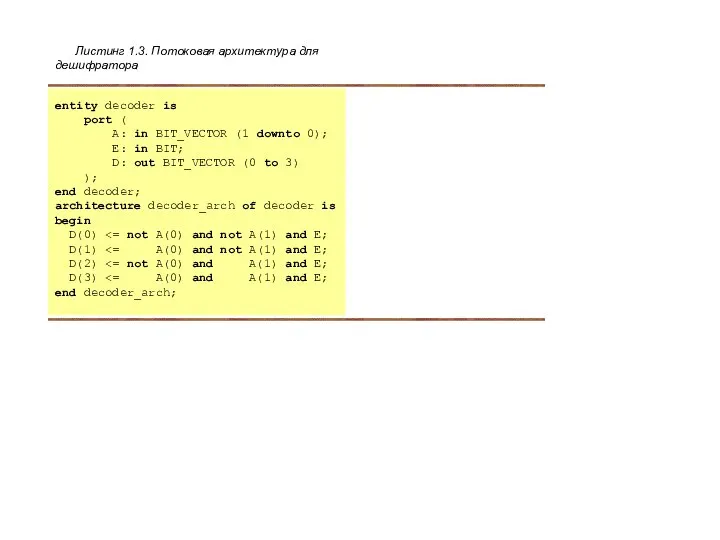

- 13. Листинг 1.3. Потоковая архитектура для дешифратора entity decoder is port ( A: in BIT_VECTOR (1 downto

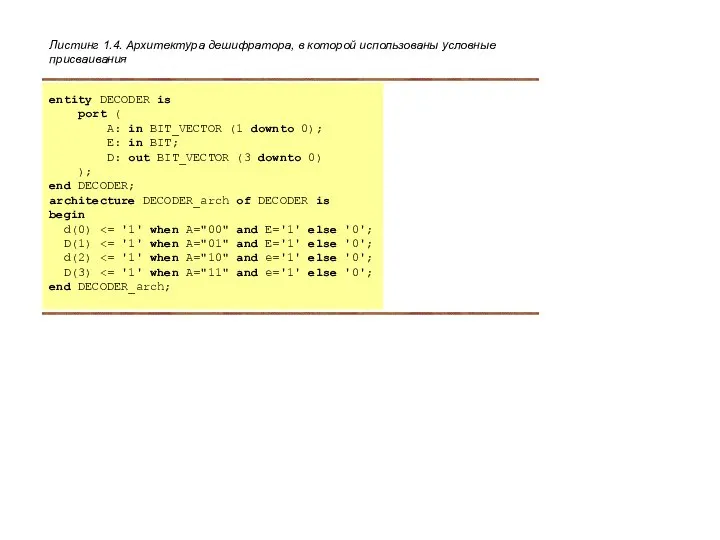

- 14. Листинг 1.4. Архитектура дешифратора, в которой использованы условные присваивания entity DECODER is port ( A: in

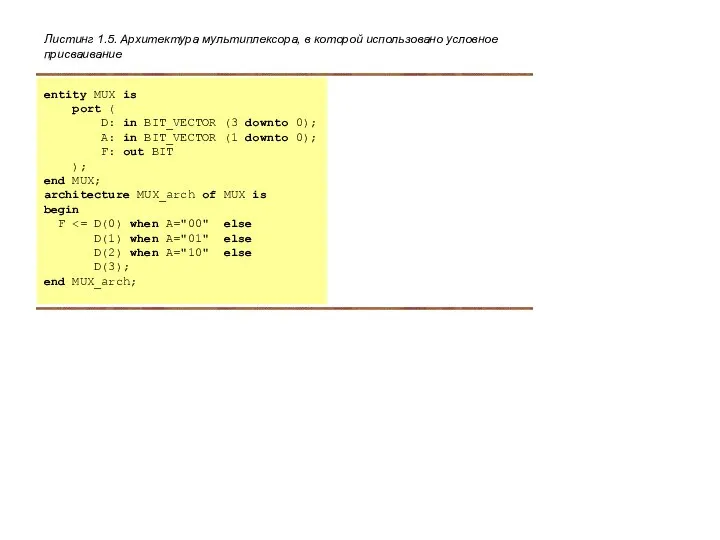

- 15. Листинг 1.5. Архитектура мультиплексора, в которой использовано условное присваивание entity MUX is port ( D: in

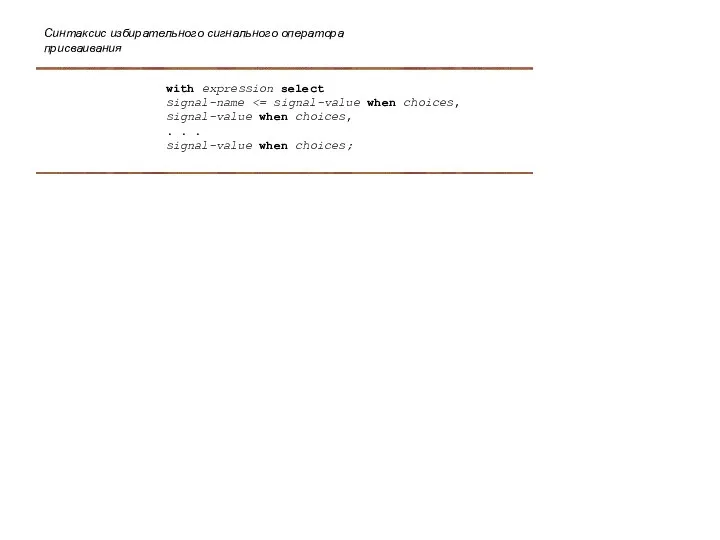

- 16. Синтаксис избирательного сигнального оператора присваивания with expression select signal-name signal-value when choices, . . . signal-value

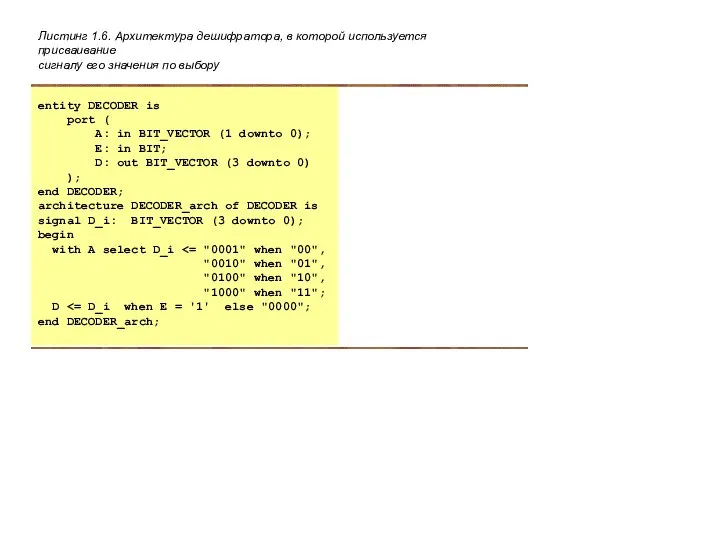

- 17. Листинг 1.6. Архитектура дешифратора, в которой используется присваивание сигналу его значения по выбору entity DECODER is

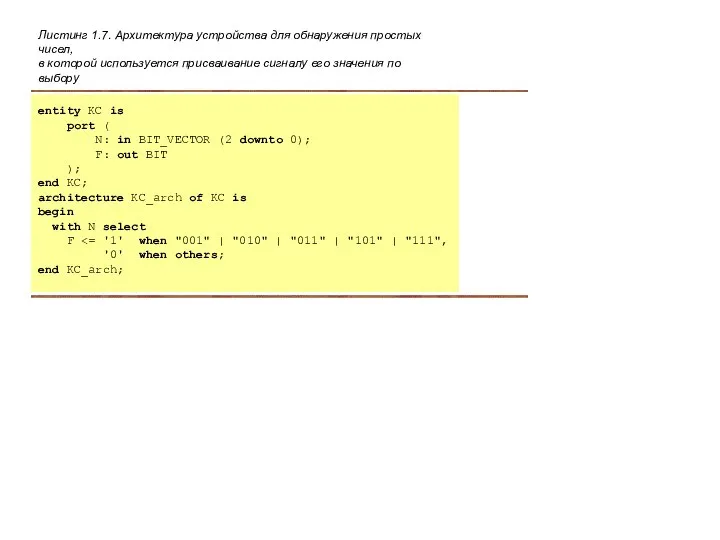

- 18. Листинг 1.7. Архитектура устройства для обнаружения простых чисел, в которой используется присваивание сигналу его значения по

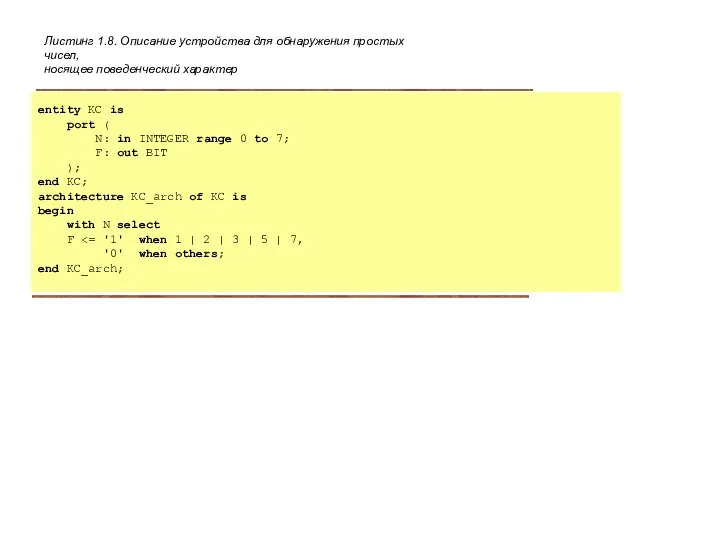

- 19. Листинг 1.8. Описание устройства для обнаружения простых чисел, носящее поведенческий характер entity KC is port (

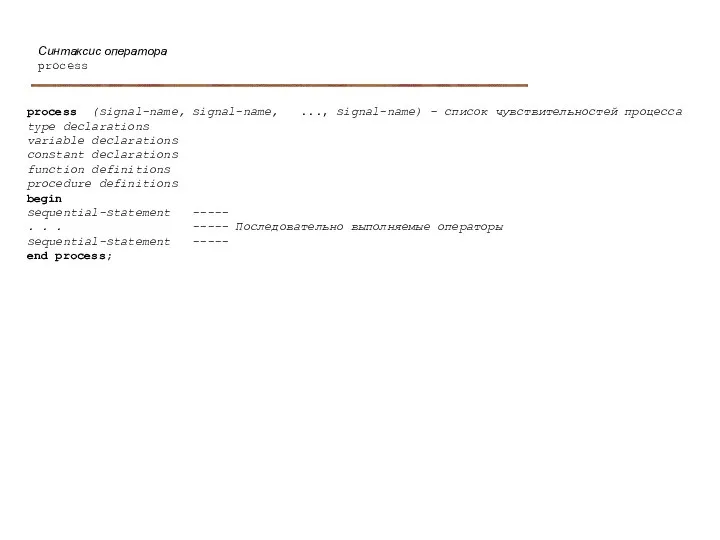

- 20. Синтаксис оператора process process (signal-name, signal-name, ..., signal-name) – список чувствительностей процесса type declarations variable declarations

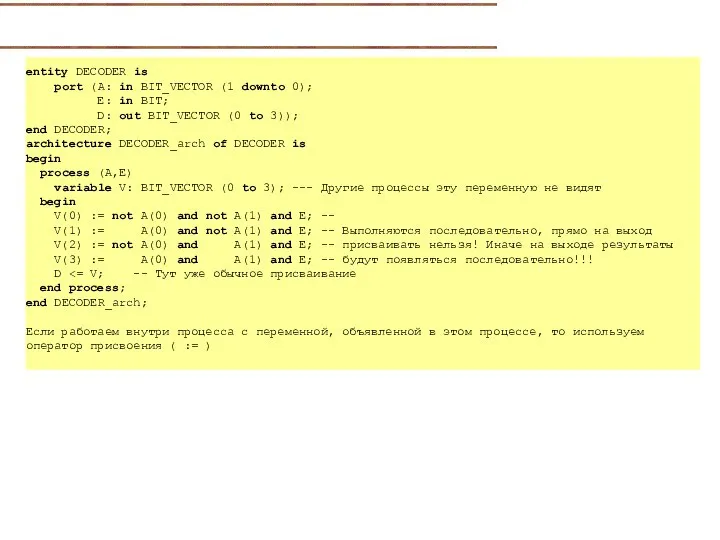

- 21. entity DECODER is port (A: in BIT_VECTOR (1 downto 0); E: in BIT; D: out BIT_VECTOR

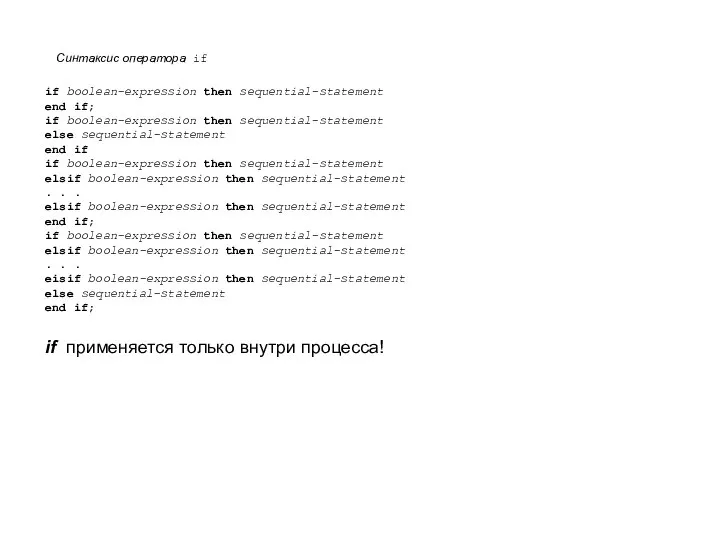

- 22. Синтаксис оператора if if boolean-expression then sequential-statement end if; if boolean-expression then sequential-statement else sequential-statement end

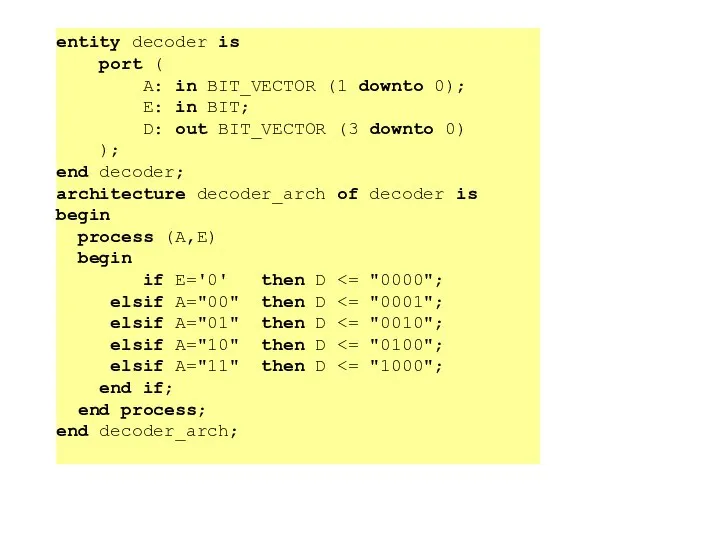

- 23. entity decoder is port ( A: in BIT_VECTOR (1 downto 0); E: in BIT; D: out

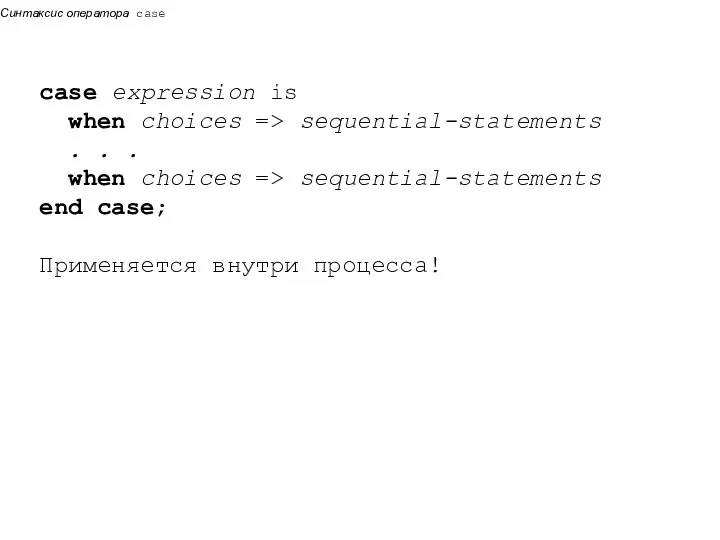

- 24. Синтаксис оператора case case expression is when choices => sequential-statements . . . when choices =>

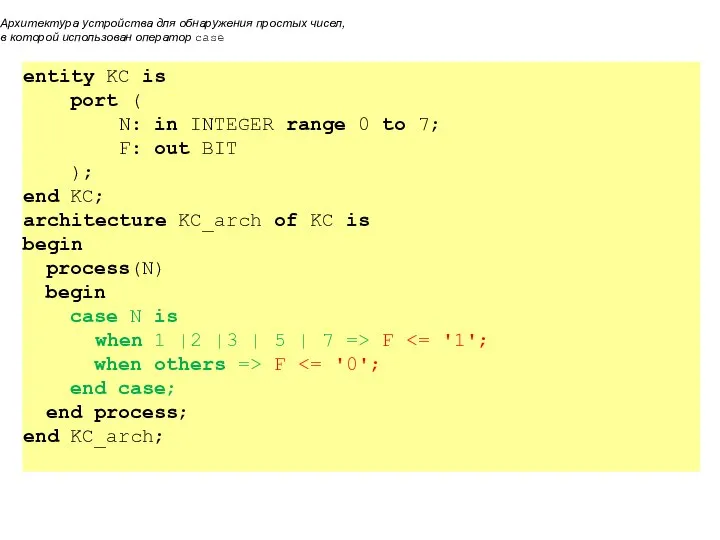

- 25. Архитектура устройства для обнаружения простых чисел, в которой использован оператор case entity KC is port (

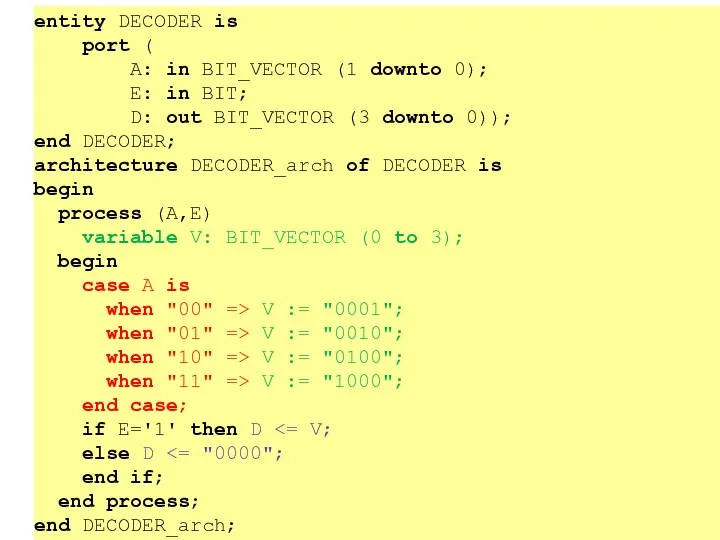

- 26. entity DECODER is port ( A: in BIT_VECTOR (1 downto 0); E: in BIT; D: out

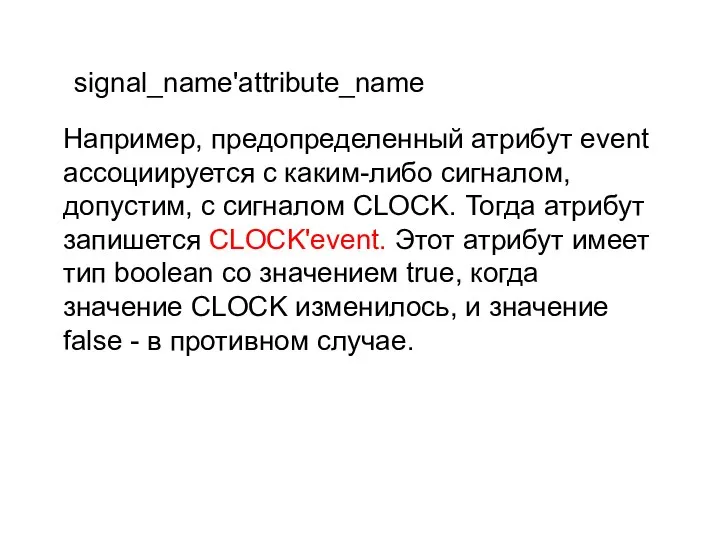

- 27. signal_name'attribute_name Например, предопределенный атрибут event ассоциируется с каким-либо сигналом, допустим, с сигналом CLOCK. Тогда атрибут запишется

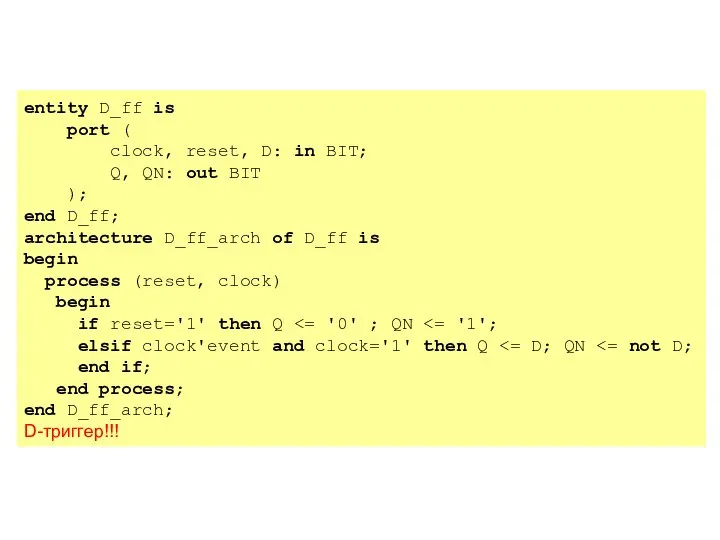

- 28. entity D_ff is port ( clock, reset, D: in BIT; Q, QN: out BIT ); end

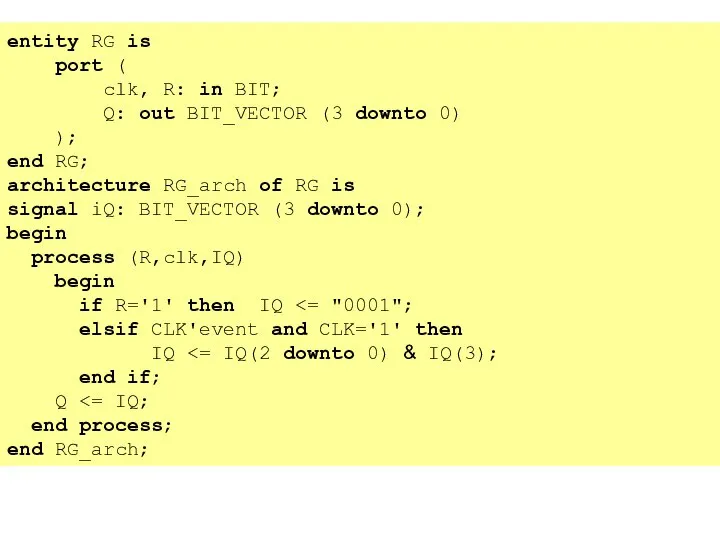

- 29. entity RG is port ( clk, R: in BIT; Q: out BIT_VECTOR (3 downto 0) );

- 31. Скачать презентацию

Родословная Д. И. Менделеева

Родословная Д. И. Менделеева Управление охраной труда на предприятиях

Управление охраной труда на предприятиях Спортивное питание

Спортивное питание 3D-сканер. Устройство. Назначение. Применение. Эксплуатация аккумуляторных установок

3D-сканер. Устройство. Назначение. Применение. Эксплуатация аккумуляторных установок Оформление предметно-пространственной среды спортивных объектов

Оформление предметно-пространственной среды спортивных объектов Презентация исследовательской работы на тему: «Связь творчества Н. А. Некрасова и И. Е. Репина» Учебный предмет: МХК, литература Ав

Презентация исследовательской работы на тему: «Связь творчества Н. А. Некрасова и И. Е. Репина» Учебный предмет: МХК, литература Ав Т Е М А «ПОСТАВКА ТОВАРОВ»

Т Е М А «ПОСТАВКА ТОВАРОВ» Устранение конфликтов планировочного решения

Устранение конфликтов планировочного решения

.ppt

.ppt Презентация Научная революция ХХ века

Презентация Научная революция ХХ века 23 февраля

23 февраля Презентация "Барокко" - скачать презентации по МХК

Презентация "Барокко" - скачать презентации по МХК Extreme sports

Extreme sports Общая система типов CTS

Общая система типов CTS Искусство Эгейского мира

Искусство Эгейского мира Алхимия

Алхимия Сравнение множеств Урок информатики во 2 классе Автор: учитель информатики Дальнезакорской СОШ Богатова Ю.Л

Сравнение множеств Урок информатики во 2 классе Автор: учитель информатики Дальнезакорской СОШ Богатова Ю.Л Системы автоматического контроля и приборы для пассивного контроля. (Лекция 3)

Системы автоматического контроля и приборы для пассивного контроля. (Лекция 3) НАСЛЕДСТВЕННО-ДЕГЕНЕРАТИВНЫЕ ЗАБОЛЕВАНИЯ НЕРВНОЙ СИСТЕМЫ

НАСЛЕДСТВЕННО-ДЕГЕНЕРАТИВНЫЕ ЗАБОЛЕВАНИЯ НЕРВНОЙ СИСТЕМЫ Датчик Тока

Датчик Тока Лидерство. Стили лидерства

Лидерство. Стили лидерства Реляционный алгебра

Реляционный алгебра Почему Лига Наций не смогла сохранить мир после Первой мировой войны

Почему Лига Наций не смогла сохранить мир после Первой мировой войны Uniforme scolaire

Uniforme scolaire Времена года в живописи

Времена года в живописи  Элементы аналогового интерфейса

Элементы аналогового интерфейса ГЕНЕТИКА АНТИГЕНРАСПОЗНАЮЩЕГО РЕЦЕПТОРА Т-КЛЕТОК

ГЕНЕТИКА АНТИГЕНРАСПОЗНАЮЩЕГО РЕЦЕПТОРА Т-КЛЕТОК  Подвижные игры на уроках физической культуры

Подвижные игры на уроках физической культуры