Содержание

- 2. Упрощённая структура микропроцессора

- 3. Структура микропроцессора

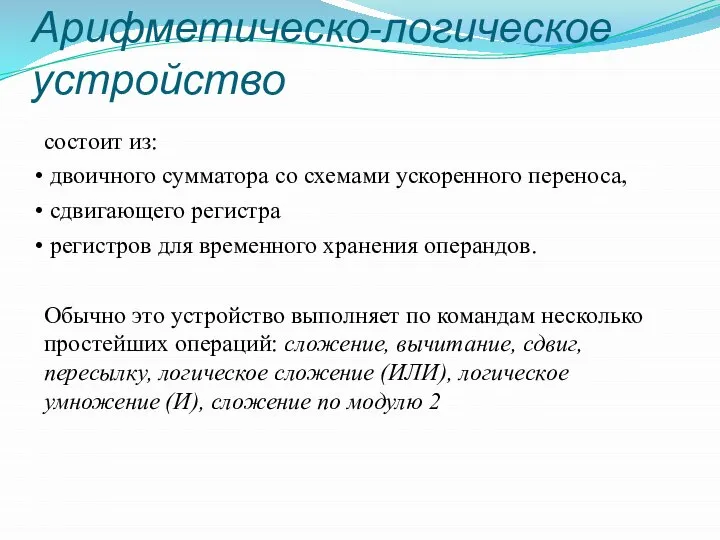

- 4. Арифметическо-логическое устройство состоит из: двоичного сумматора со схемами ускоренного переноса, сдвигающего регистра регистров для временного хранения

- 5. Структурная схема АЛУ

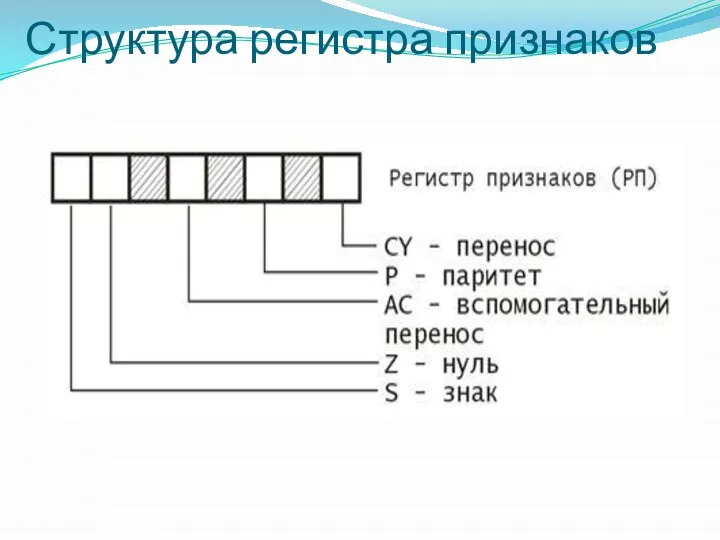

- 6. Структура регистра признаков

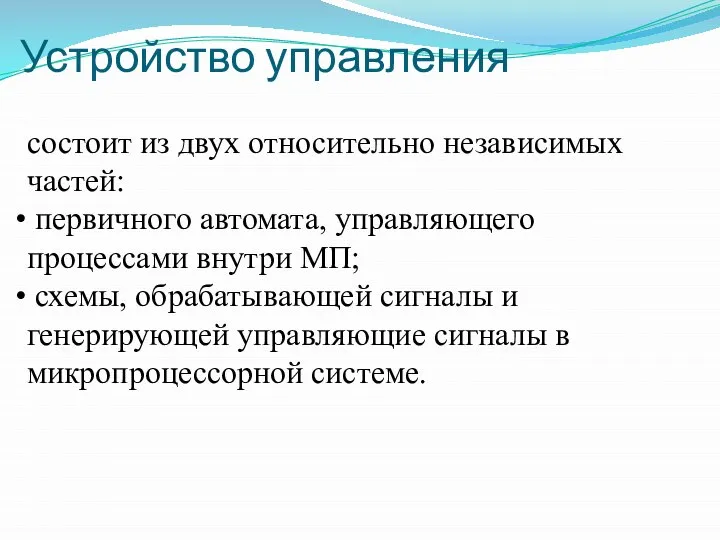

- 7. Устройство управления состоит из двух относительно независимых частей: первичного автомата, управляющего процессами внутри МП; схемы, обрабатывающей

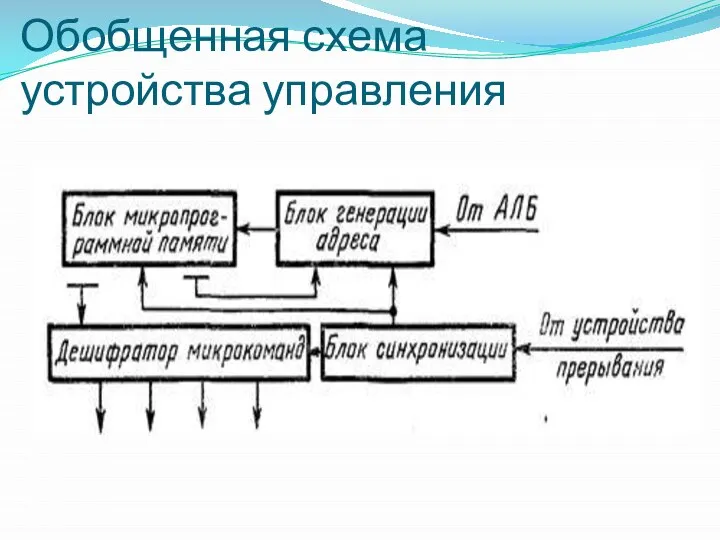

- 8. Обобщенная схема устройства управления

- 9. Блок внутренних регистров БВР расширяет возможности АЛУ, служит внутренней памятью МП и используется для временного хранения

- 10. Специальные регистры Регистр – аккумулятор (“накопитель”), предназначен для временного хранения операнда или промежуточного результата действий производимой

- 11. Регистры общего назначения Их функция – хранение операндов. Могут выполнять также и роль регистров Число может

- 12. Управление и синхронизация МП Машинный такт (Т) — это период синхросигналов. Его длительность может быть установлена

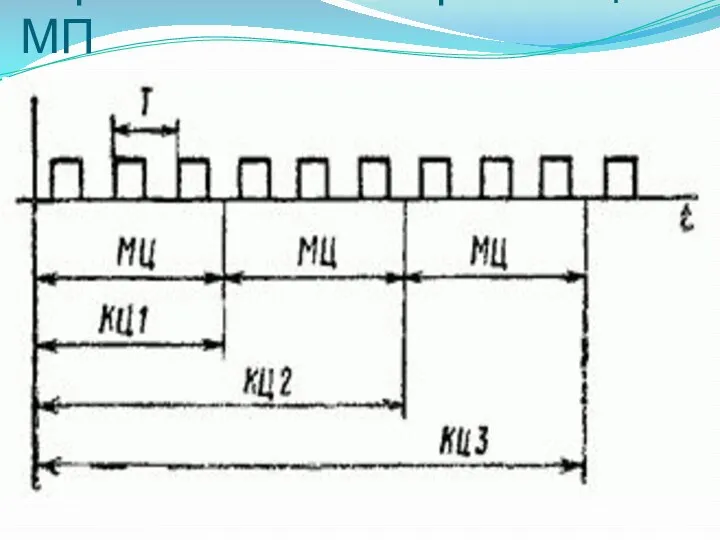

- 13. Управление и синхронизация МП

- 14. Управление и синхронизация МП Элементарную функциональную операцию (или их некоторую комбинацию), выполняемую за один тактовый интервал

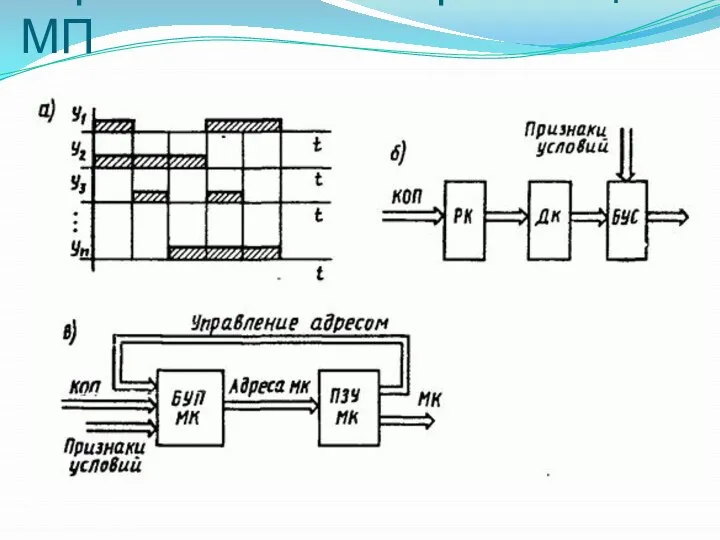

- 15. Управление и синхронизация МП

- 16. Управление и синхронизация МП Схемный, жесткий или аппаратный способ управления используется в однокристальных МП. Он характеризуется

- 18. Скачать презентацию

Обморожения и ожоги

Обморожения и ожоги Самоконтроль при занятиях физической культурой и спортом

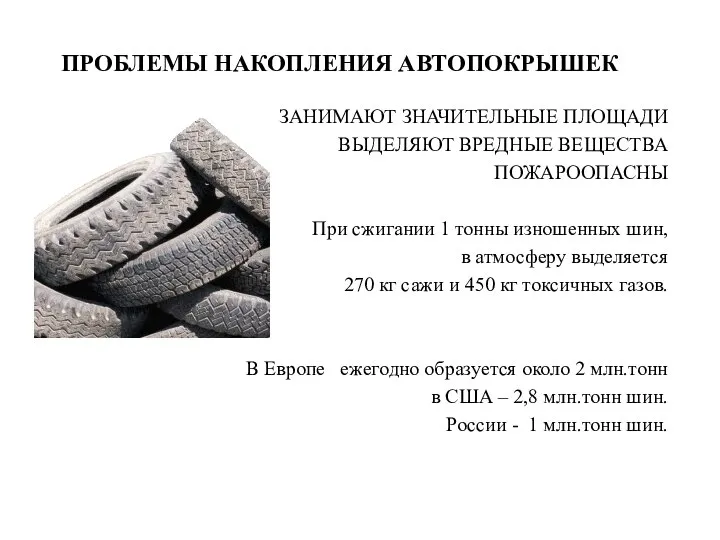

Самоконтроль при занятиях физической культурой и спортом УТИЛИЗАЦИЯ АВТОПОКРЫШЕК

УТИЛИЗАЦИЯ АВТОПОКРЫШЕК Специализированные Учреждения ООН

Специализированные Учреждения ООН Педагогический_состав

Педагогический_состав Механизм газораспределения

Механизм газораспределения Презентація з теорії твору і тексту на тему “Співідношення поняття “твір” і “текст”

Презентація з теорії твору і тексту на тему “Співідношення поняття “твір” і “текст” Культура России в XVII веке

Культура России в XVII веке Спряжение глаголов в Präsens ( настоящем времени)

Спряжение глаголов в Präsens ( настоящем времени) Сжатые и растянутые железобетонные конструкции

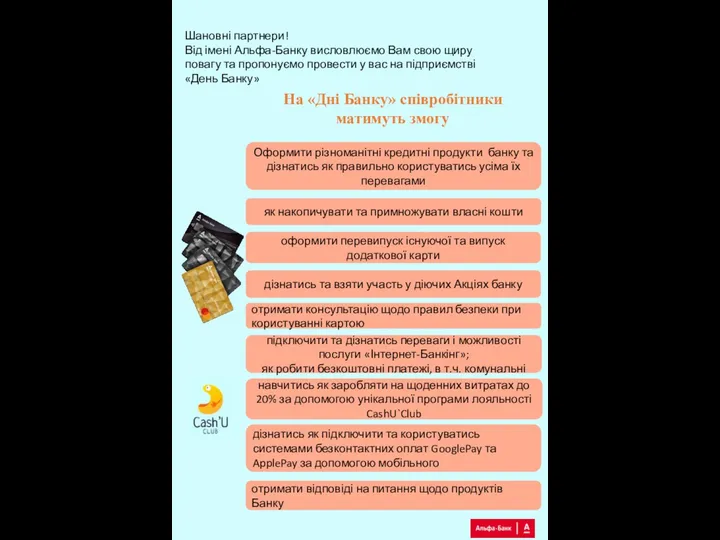

Сжатые и растянутые железобетонные конструкции День банка в Альфа-Банк

День банка в Альфа-Банк Тесты по ОЦК, кровопотеря

Тесты по ОЦК, кровопотеря Модель «сущность-связь». Основные понятия: Сущность, Свойства, Связи.

Модель «сущность-связь». Основные понятия: Сущность, Свойства, Связи. Язык и речь

Язык и речь  Презентация на тему "Правила управления успехом на уроке" - скачать презентации по Педагогике

Презентация на тему "Правила управления успехом на уроке" - скачать презентации по Педагогике Контрольная работа по .NET

Контрольная работа по .NET Мастерская народного творчества "Василиса". Номинация "Прильну ко льну"

Мастерская народного творчества "Василиса". Номинация "Прильну ко льну" Стиль жизни ХХІ века. Tiens Group Corporation

Стиль жизни ХХІ века. Tiens Group Corporation ГОМЕОСТАЗ ЗУБА ПОСЛЕ ПРОРЕЗЫВАНИЯ. РЕЗИСТЕНТНОСТЬ ЭМАЛИ ЗУБА К КАРИОЗНОМУ ПОРАЖЕНИЮ. ВЛИЯНИЕ НА ПРОЦЕССЫ ФОРМИРОВАНИЯ, МИНЕРА

ГОМЕОСТАЗ ЗУБА ПОСЛЕ ПРОРЕЗЫВАНИЯ. РЕЗИСТЕНТНОСТЬ ЭМАЛИ ЗУБА К КАРИОЗНОМУ ПОРАЖЕНИЮ. ВЛИЯНИЕ НА ПРОЦЕССЫ ФОРМИРОВАНИЯ, МИНЕРА Развитие медицины в России в 19 веке

Развитие медицины в России в 19 веке Новая конституция РФ (часть 6)

Новая конституция РФ (часть 6) Презентация по вкусовым товарам. Кофе.

Презентация по вкусовым товарам. Кофе.  Характер

Характер Разработка и принятие Уголовного кодекса 1922 г.

Разработка и принятие Уголовного кодекса 1922 г. Презентация Классификация овощей

Презентация Классификация овощей  Презентация "Строительство из соломы" - скачать презентации по Экономике

Презентация "Строительство из соломы" - скачать презентации по Экономике Презентация по алгебре Типы иррациональных уравнений Примеры решения

Презентация по алгебре Типы иррациональных уравнений Примеры решения  Презентация на тему Формы государства

Презентация на тему Формы государства