- Главная

- Информатика

- ЭВМ и периферия

Содержание

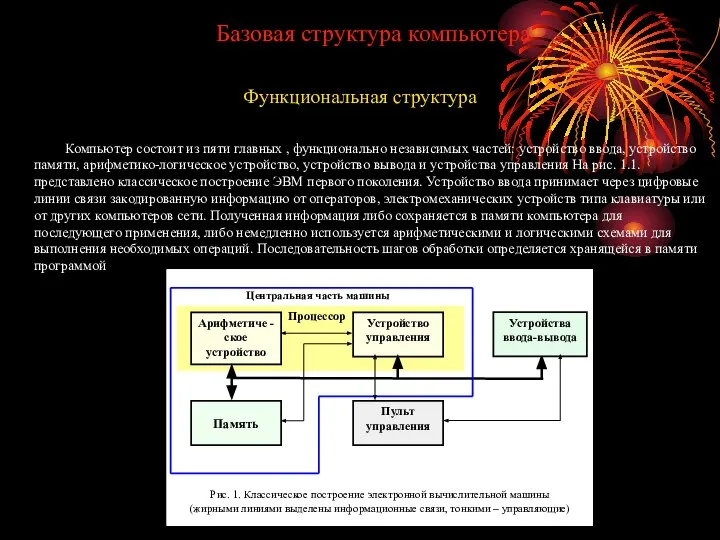

- 2. Базовая структура компьютера Функциональная структура Компьютер состоит из пяти главных , функционально независимых частей: устройство ввода,

- 3. Полученные результаты отправляются обратно во внешний мир, посредством устройства вывода. Все эти действия координируются блоком (устройством)

- 4. Устройство ввода Компьютер принимает кодированную информацию через устройство ввода, задачей которого является чтение данных. Наиболее распространенным

- 5. Во время выполнения программа все время должна находиться в памяти. Команды и данные должны записываться в

- 6. Управление операциями ввода-вывода осуществляется командами программ, в которых идентифицируются соответствующие устройства ввода-вывода и пересылаемые данные. Однако,

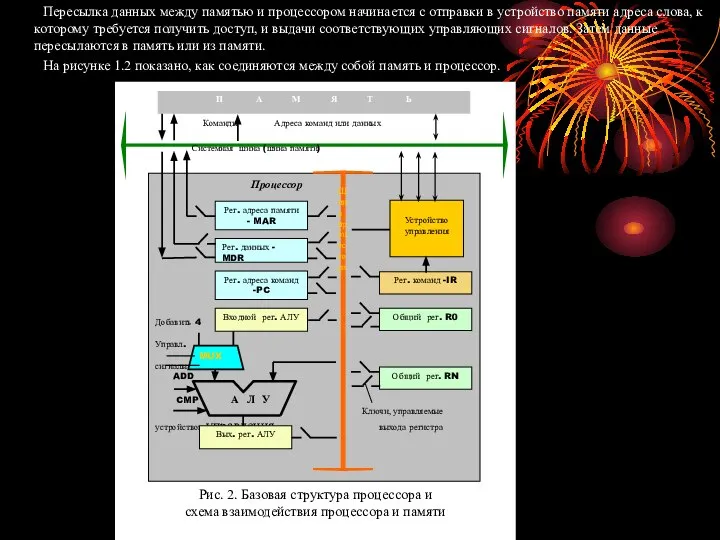

- 7. Пересылка данных между памятью и процессором начинается с отправки в устройство памяти адреса слова, к которому

- 8. Кроме АЛУ и управляющих схем процессор содержит множество регистров, предназначенных для разных целей В регистре команды

- 9. Другими словами, как только завершится выполнение текущей инструкции, можно будет приступить к выборке следующей. Компьютер не

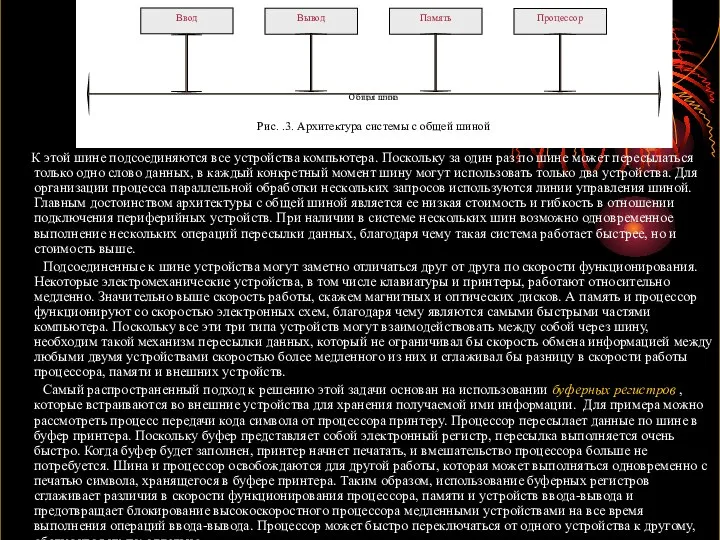

- 10. Для соединения нескольких функциональных устройств компьютера проще всего использовать общую шину (single bus), как показано на

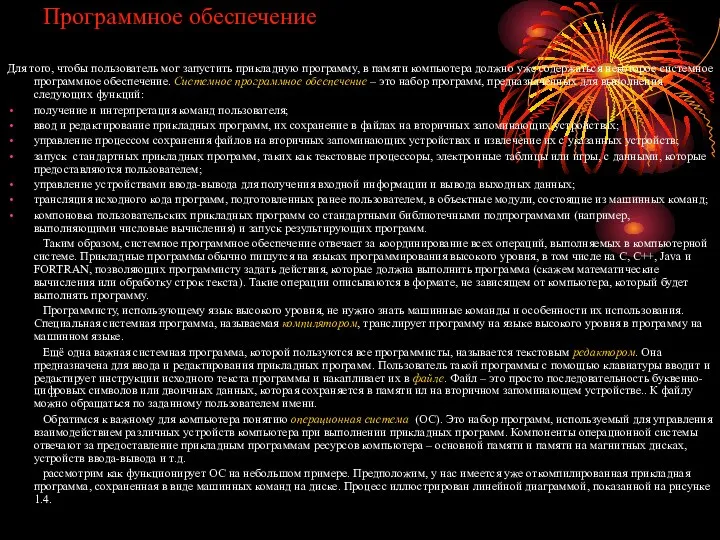

- 11. Программное обеспечение Для того, чтобы пользователь мог запустить прикладную программу, в памяти компьютера должно уже содержаться

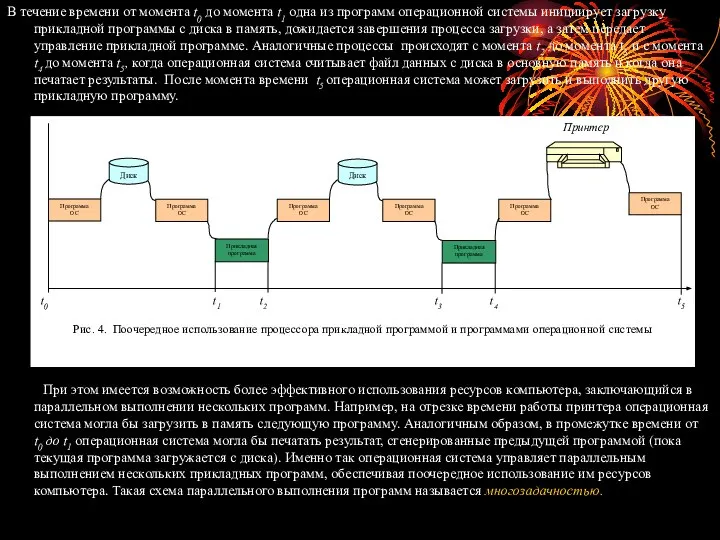

- 12. В течение времени от момента t0 до момента t1 одна из программ операционной системы инициирует загрузку

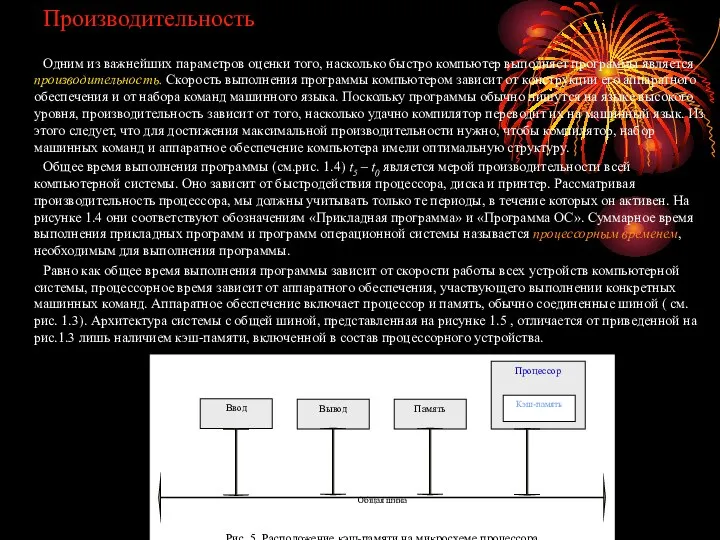

- 13. Производительность Одним из важнейших параметров оценки того, насколько быстро компьютер выполняет программы является производительность. Скорость выполнения

- 14. Какую роль играет кэш-память в производительности компьютера? По мере выполнения программы ее команды по одной выбираются

- 15. Компилятор генерирует соответствующую объектную программу на машинном языке. Допустим, что для полного выполнения такой программы нужно

- 16. Оценка производительности Чтобы оценить производительность компьютера, ее необходимо как-то измерить. Руководствуясь показателем производительности, конструкторы компьютеров обычно

- 17. Символы Компьютеры должны обрабатывать не только числа, но и текстовую информацию, состоящую из символов. Под термином

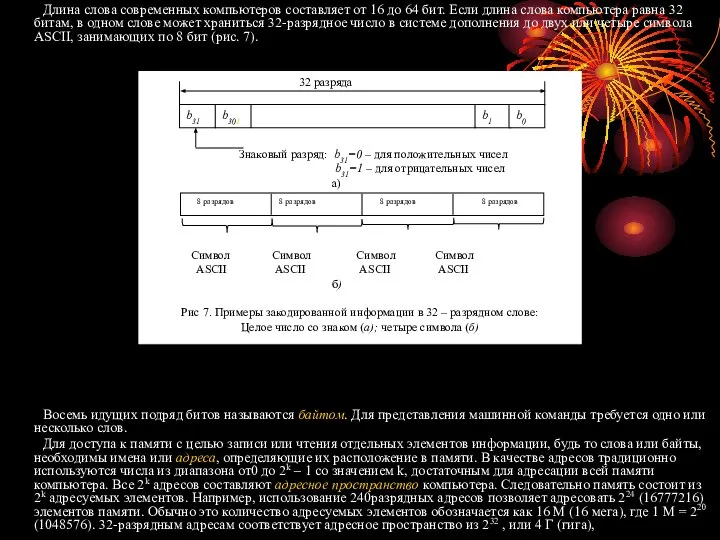

- 18. Длина слова современных компьютеров составляет от 16 до 64 бит. Если длина слова компьютера равна 32

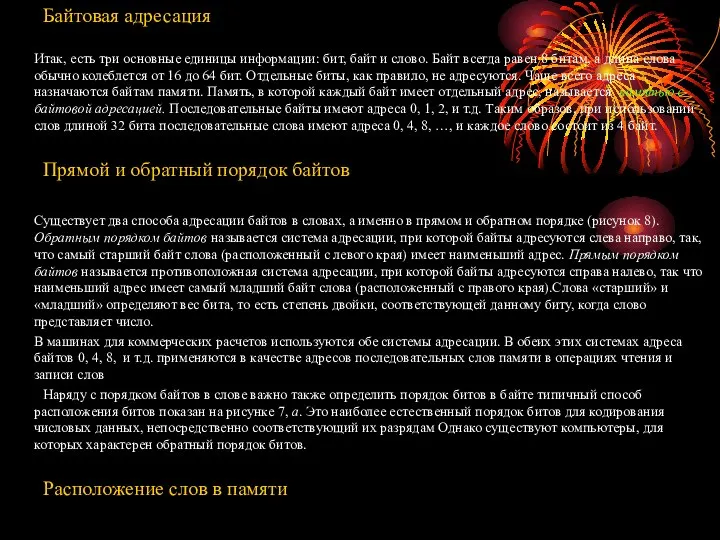

- 19. Байтовая адресация Итак, есть три основные единицы информации: бит, байт и слово. Байт всегда равен 8

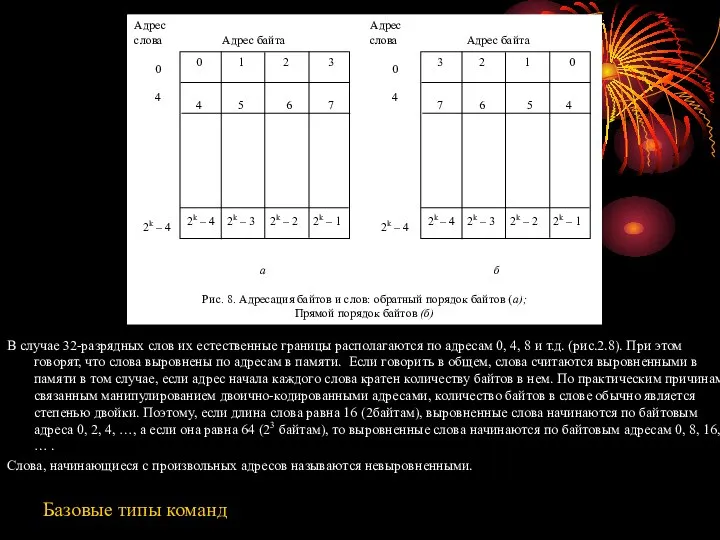

- 20. В случае 32-разрядных слов их естественные границы располагаются по адресам 0, 4, 8 и т.д. (рис.2.8).

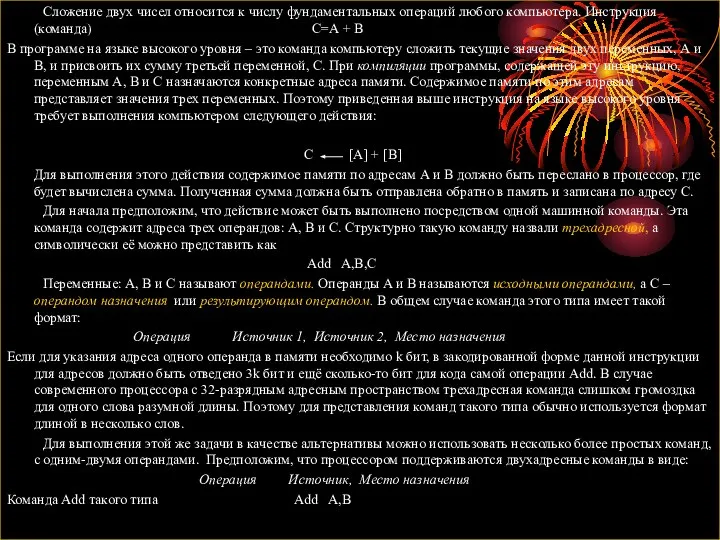

- 21. Сложение двух чисел относится к числу фундаментальных операций любого компьютера. Инструкция (команда) С=А + В В

- 22. Будет выполнять операцию B [A] + [B]. После вычисления суммы результат будет переслан обратно в память

- 23. Следует обратить внимание на то, что в зависимости от типа команды её операнд может служить либо

- 24. Эта команда помещает в приемник копию содержимого источника. Команда Move может использоваться для пересылки данных из

- 25. Чтобы программа начала выполняться адрес ее первой команды (в нашем примере i) должен быть помещен в

- 26. Ветвление На рисунке 10 представлена программ сложения n чисел, адреса которых в памяти символически обозначены как

- 27. Имеет место определение команды условного перехода, при котором переход в нужную часть программы осуществляется только при

- 28. Флаги N и Z указывают, является результат арифметической операции отрицательным или нулевым. Кроме арифметических команд на

- 29. Таблица1. Стандартные режимы адресации

- 30. Реализация переменных и констант Переменные и константы – это простейшие виды данных, используемые в любой компьютерной

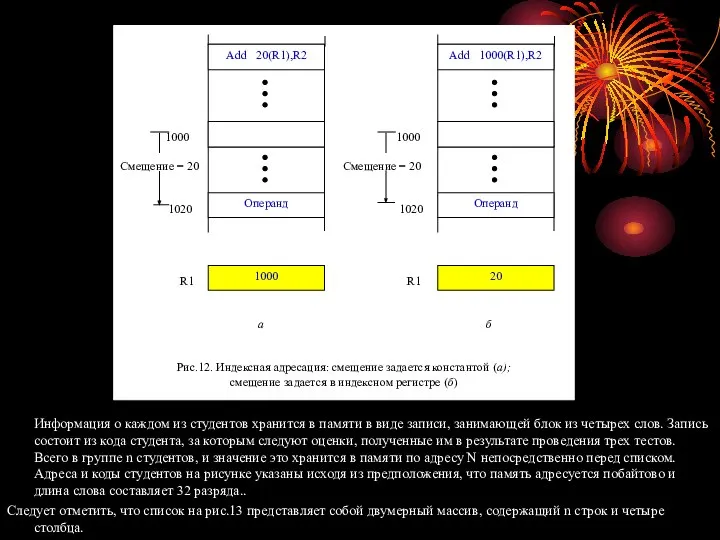

- 31. Косвенная адресация и указатели При эти режимах адресации операнд и его адрес не задаются прямо в

- 32. Для выполнения команды Add, схематически представленной на рисунке 11, а, процессор использует в качестве исполнительного адреса

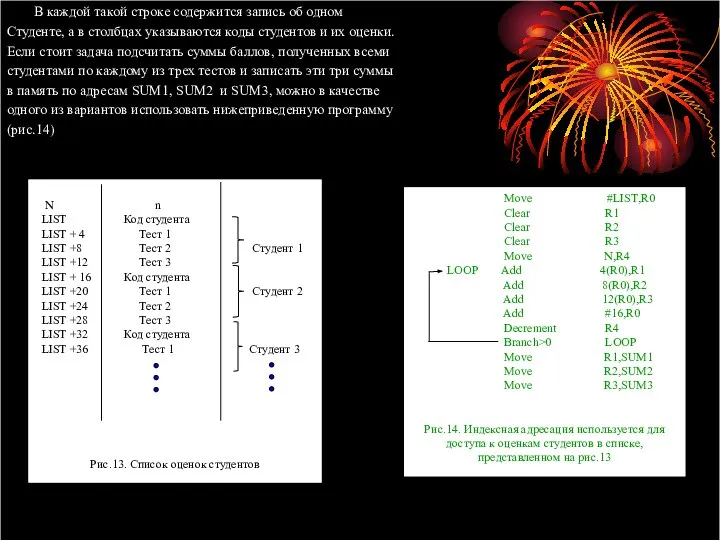

- 33. Индексация и массивы Режим адресации, который будет рассматриваться сейчас считается наиболее полезным для работы с массивами

- 34. Информация о каждом из студентов хранится в памяти в виде записи, занимающей блок из четырех слов.

- 35. В каждой такой строке содержится запись об одном Студенте, а в столбцах указываются коды студентов и

- 36. В теле цикла программы для доступа к записям с каждой из трех оценок очередного студента применяется

- 37. Относительная адресация Запись X(PC) означает, что исполнительный адрес смещен на X байтов относительно адреса, заданного в

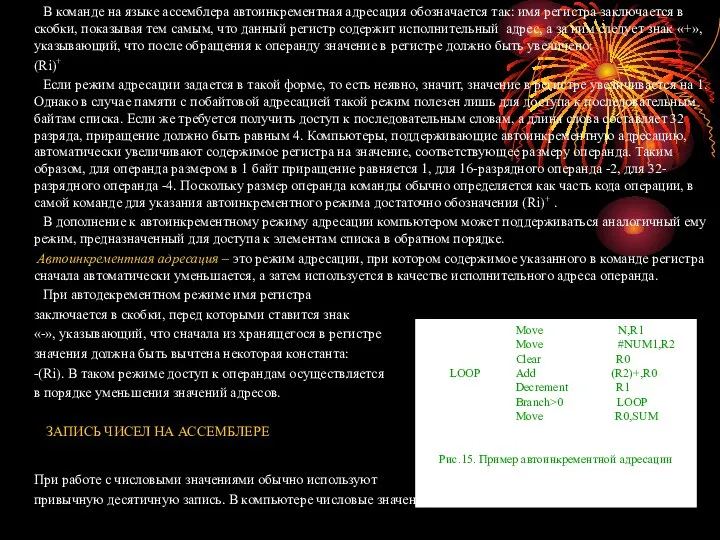

- 38. В команде на языке ассемблера автоинкрементная адресация обозначается так: имя регистра заключается в скобки, показывая тем

- 39. В некоторых случаях удобнее прямо задавать числовые значения различными способами, используя соглашения, определяемые синтаксисом языка. Возьмем

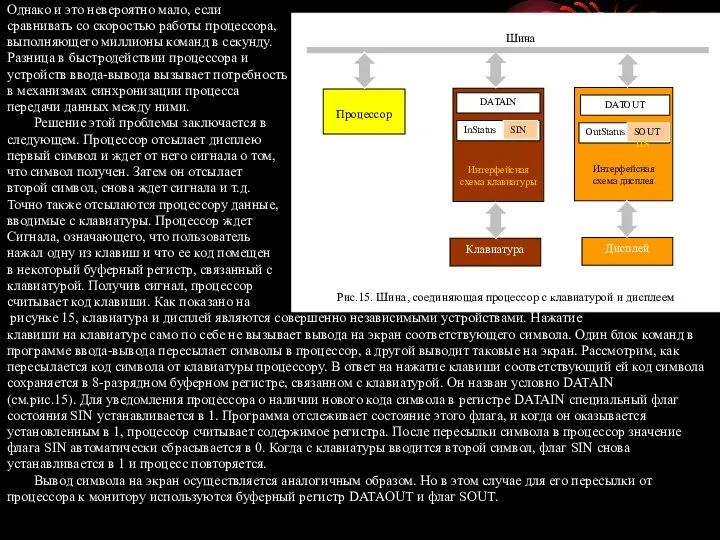

- 40. Однако и это невероятно мало, если сравнивать со скоростью работы процессора, выполняющего миллионы команд в секунду.

- 41. Если значение SOUT равно 1, значит, дисплей готов к приему символа. Процессор под управлением программы отслеживает

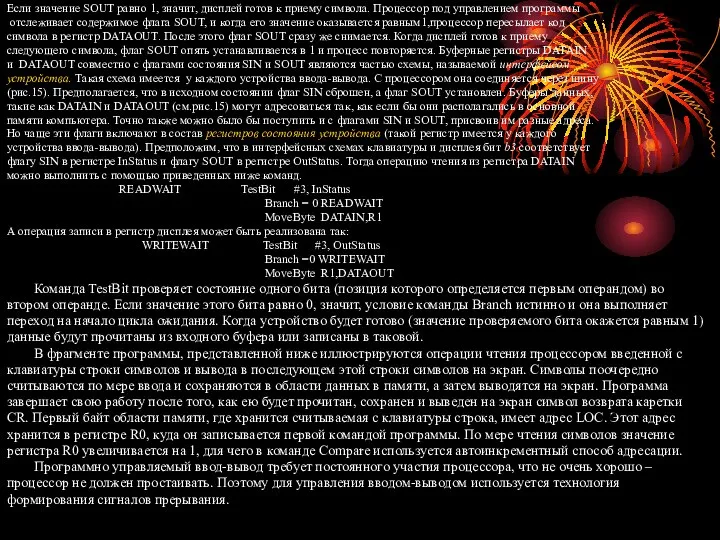

- 42. Программа считывающая строку символов и выводящая ее на экран Move #LOC,R0 Инициализация регистра R0, то есть

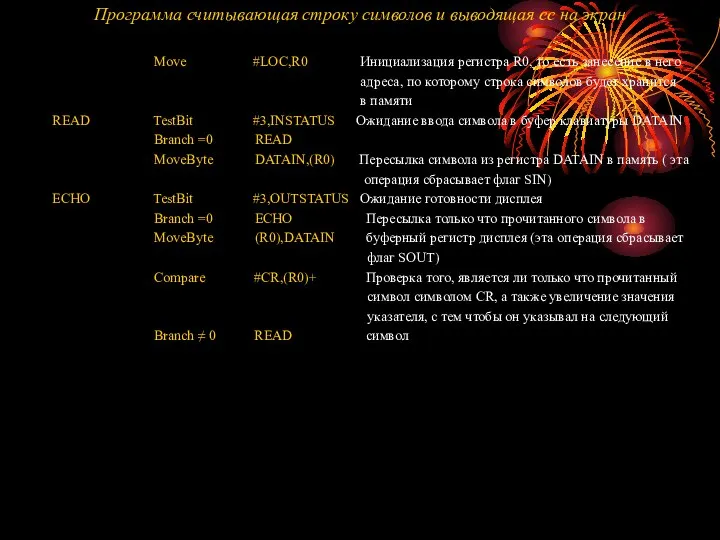

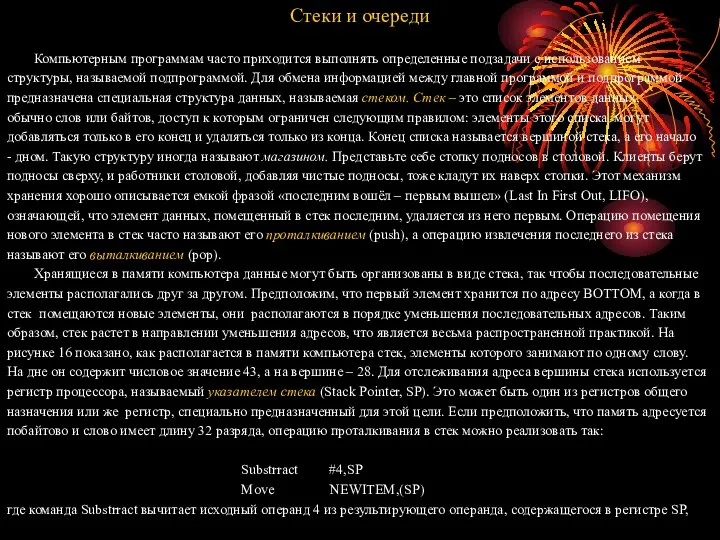

- 43. Стеки и очереди Компьютерным программам часто приходится выполнять определенные подзадачи с использованием структуры, называемой подпрограммой. Для

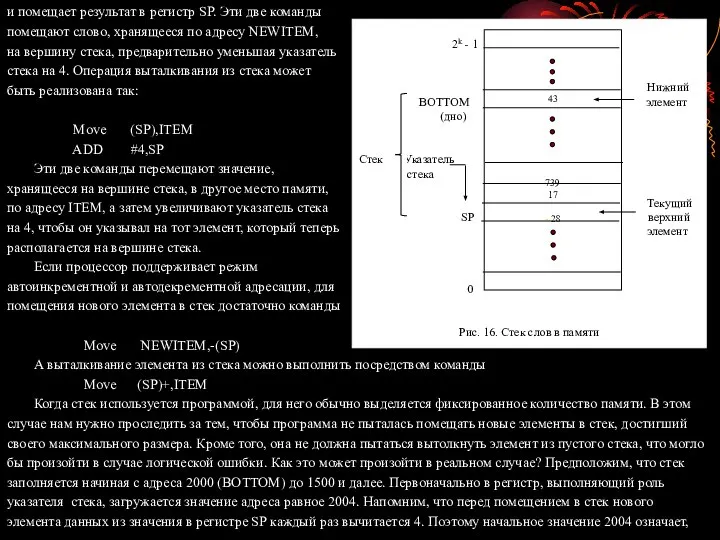

- 44. и помещает результат в регистр SP. Эти две команды помещают слово, хранящееся по адресу NEWITEM, на

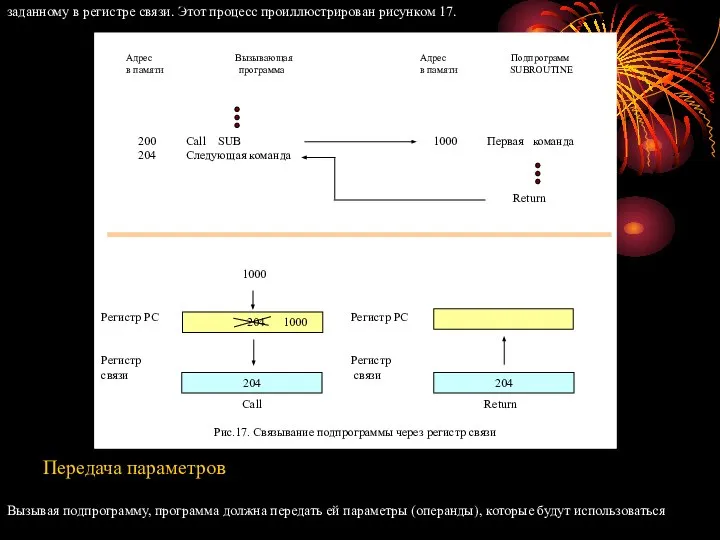

- 45. что первый элемент стека будет иметь адрес 2000. Для предотвращения попыток помещения элемента в полный стек

- 46. Второе различие между стеком и очередью состоит в том, что без дополнительного управления очередь будет постоянно

- 47. заданному в регистре связи. Этот процесс проиллюстрирован рисунком 17. Передача параметров Вызывая подпрограмму, программа должна передать

- 48. в вычислениях, или же их адреса. Закончив свою работу, подпрограмма вернет другие параметры – результаты вычислений.

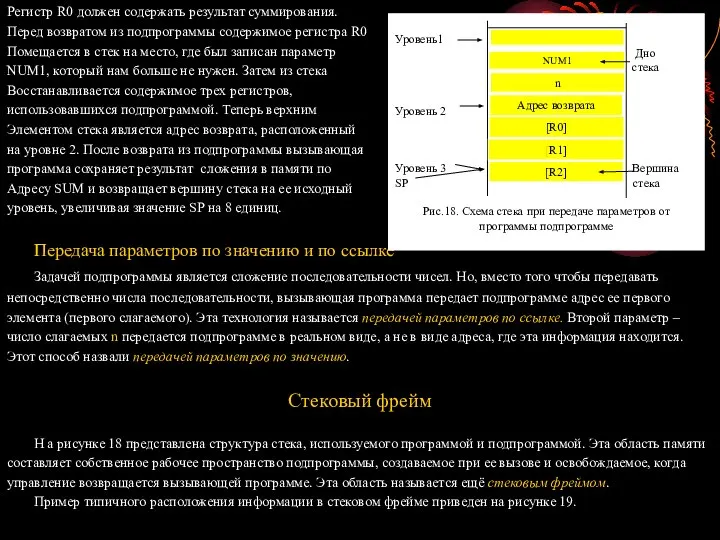

- 49. первого числа, NUM1, передаются подпрограмме через регистры R1 и R2. Вычисленная подпрограммой сумма возвращается вызывающей программе

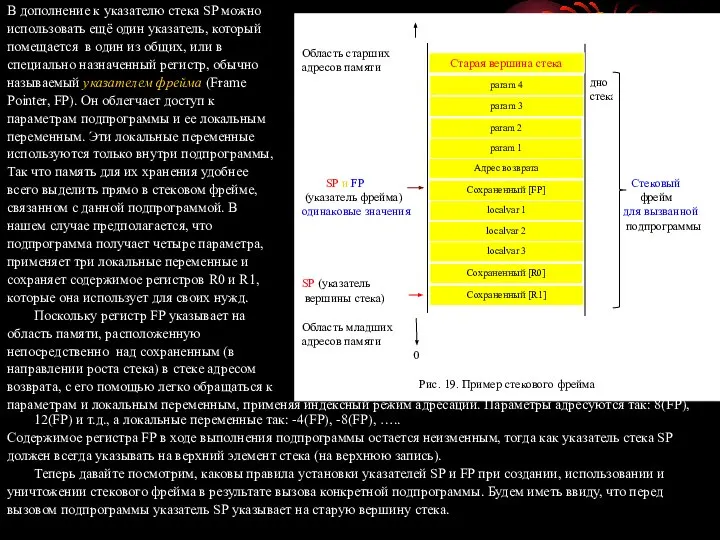

- 50. Пример программы, передающей параметры подпрограмме через стек, вызывающая программа и подпрограмма. (Предполагается, что вершина стека расположена

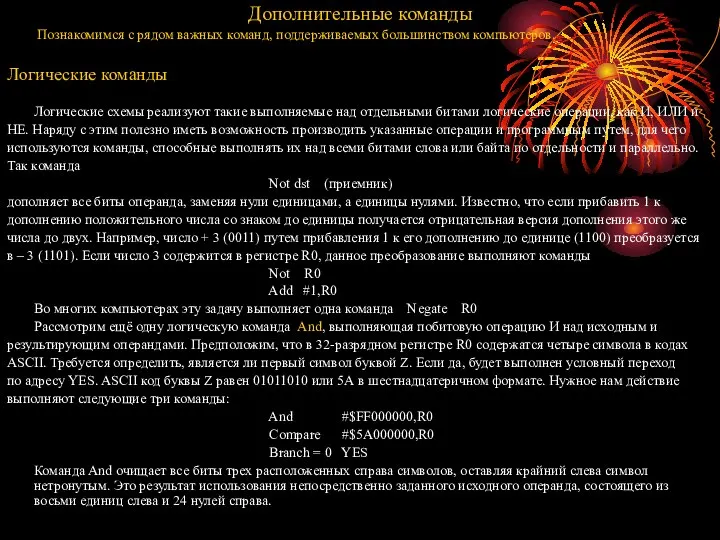

- 51. Регистр R0 должен содержать результат суммирования. Перед возвратом из подпрограммы содержимое регистра R0 Помещается в стек

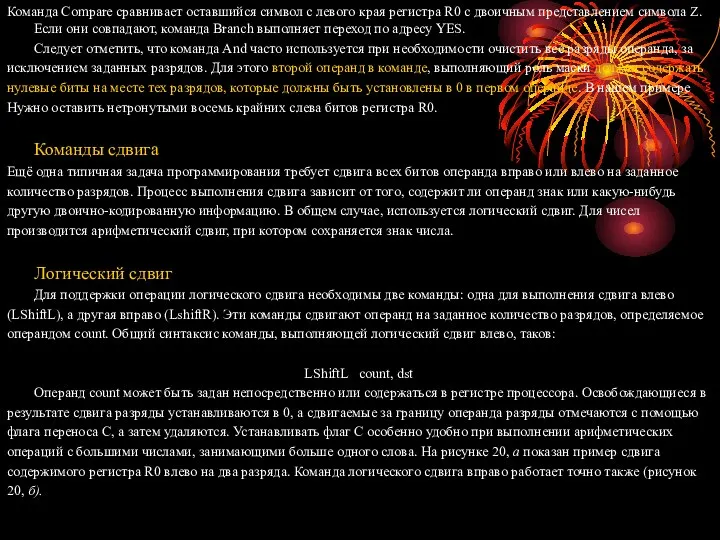

- 52. В дополнение к указателю стека SP можно использовать ещё один указатель, который помещается в один из

- 53. Дополнительные команды Познакомимся с рядом важных команд, поддерживаемых большинством компьютеров. Логические команды Логические схемы реализуют такие

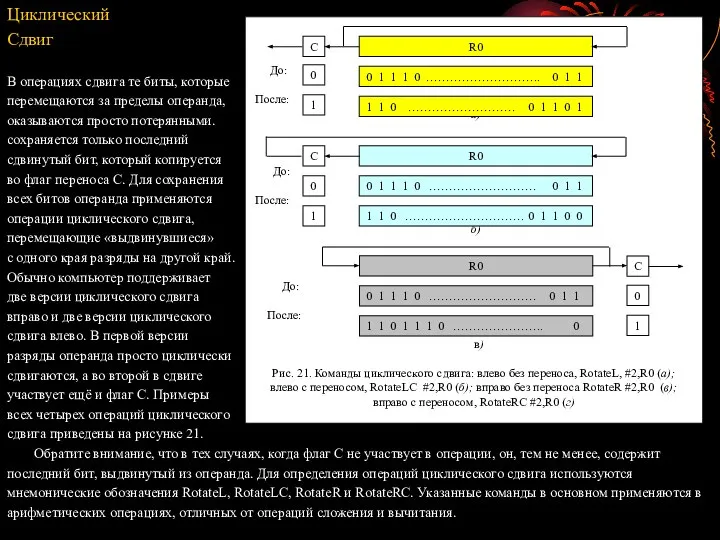

- 54. Команда Compare сравнивает оставшийся символ с левого края регистра R0 с двоичным представлением символа Z. Если

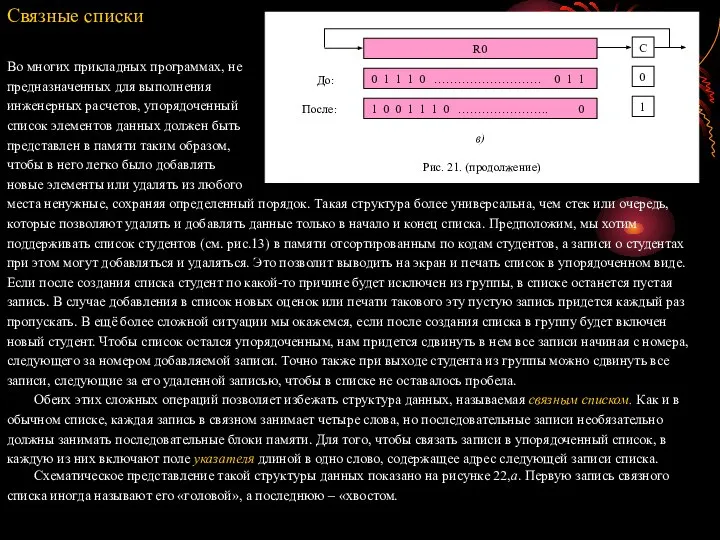

- 55. Арифметический сдвиг Сдвиг числа на один разряд влево эквивалентен его умножению на 2, а сдвиг на

- 56. Циклический Сдвиг В операциях сдвига те биты, которые перемещаются за пределы операнда, оказываются просто потерянными. сохраняется

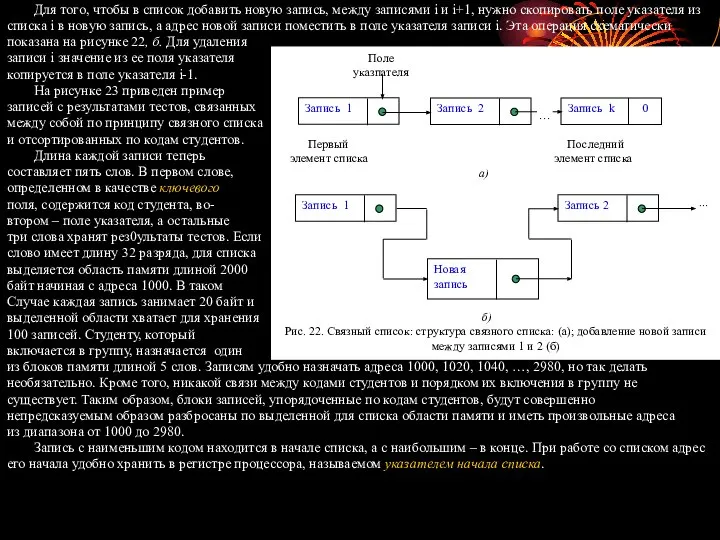

- 57. Связные списки Во многих прикладных программах, не предназначенных для выполнения инженерных расчетов, упорядоченный список элементов данных

- 58. Для того, чтобы в список добавить новую запись, между записями i и i+1, нужно скопировать поле

- 59. В нашем примере это адрес 2320. Адрес 1040 в поле указателя первой записи определяет местоположение второй

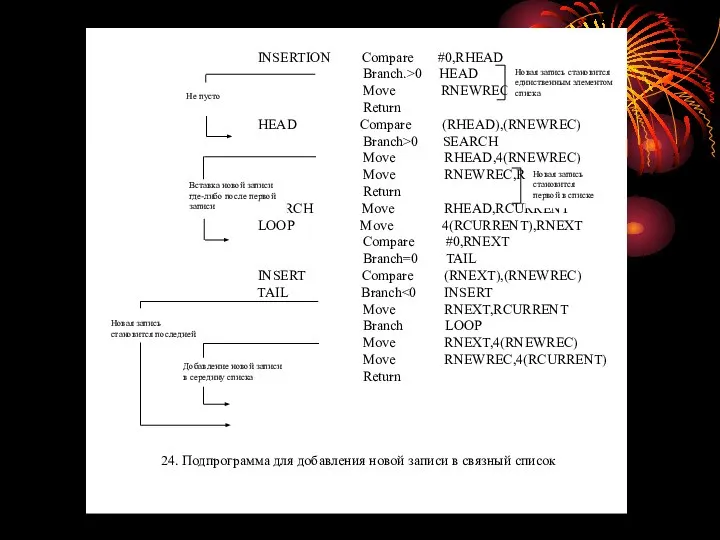

- 61. Теперь новая запись помещена на третье место списка, между второй и третьей записями исходного списка. Выполняющая

- 62. Мы предполагаем, что в регистре RIDNUM содержится код удаляемой записи, а регистры RHEAD, RCURRENT и RNEXT

- 63. Обработка ошибок Подпрограммы добавления и удаления записи, показанные на рисунках 24 и 25, не учитывают, что

- 64. Ввод – вывод Одной из важнейших функций компьютера является поддержка устройств ввода-вывода. Благодаря этому оператор, к

- 65. Шина USB Объединение компьютеров и коммуникационных технологий привело к настоящей информационной революции. Современные компьютерные системы включают

- 66. Шина USB обеспечивает возможность подключения к компьютеру большего количества устройств в любой момент и без необходимости

- 67. Для того, чтобы при оцифровке звука сохранялись те его составляющие, которые меняются с очень большой скоростью,

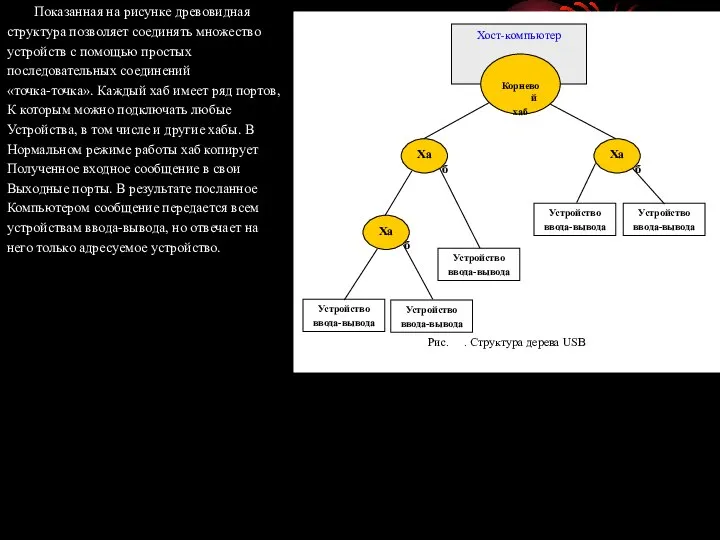

- 68. Поэтому небольшие дополнительные задержки при пересылке данных между диском и компьютером не имеют значения, равно как

- 69. Показанная на рисунке древовидная структура позволяет соединять множество устройств с помощью простых последовательных соединений «точка-точка». Каждый

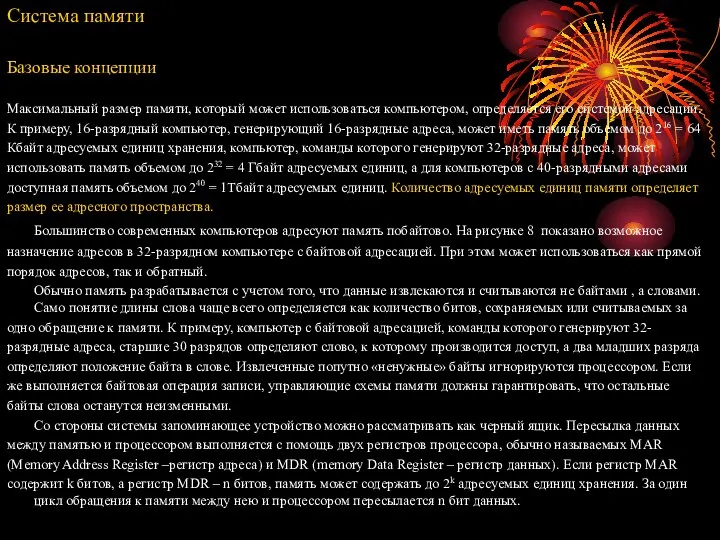

- 72. Система памяти Базовые концепции Максимальный размер памяти, который может использоваться компьютером, определяется его системой адресации. К

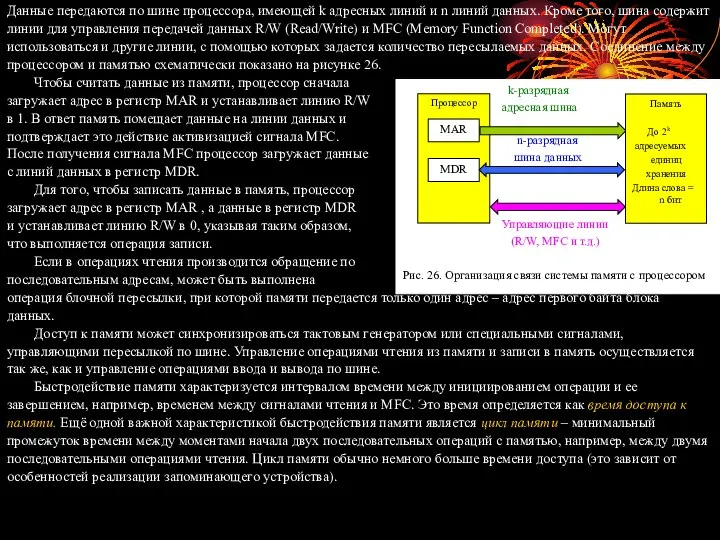

- 73. Данные передаются по шине процессора, имеющей k адресных линий и n линий данных. Кроме того, шина

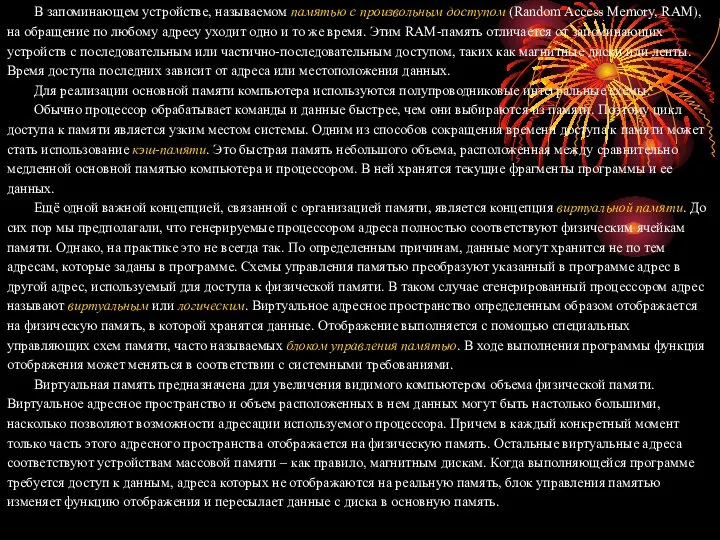

- 74. В запоминающем устройстве, называемом памятью с произвольным доступом (Random Access Memory, RAM), на обращение по любому

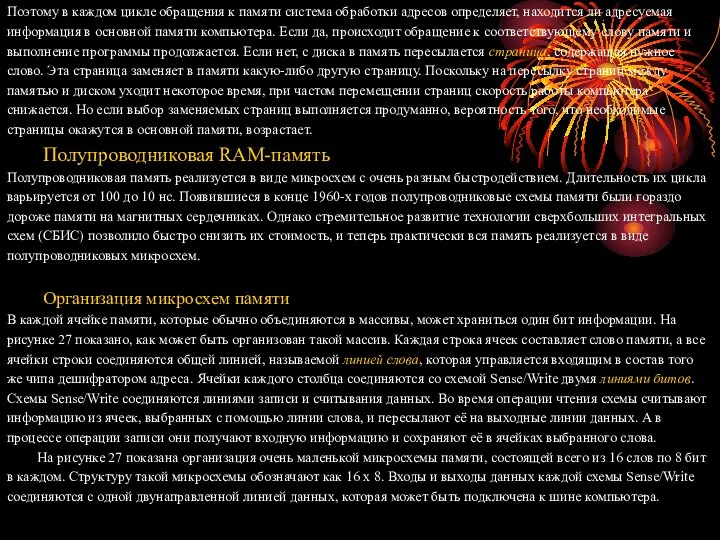

- 75. Поэтому в каждом цикле обращения к памяти система обработки адресов определяет, находится ли адресуемая информация в

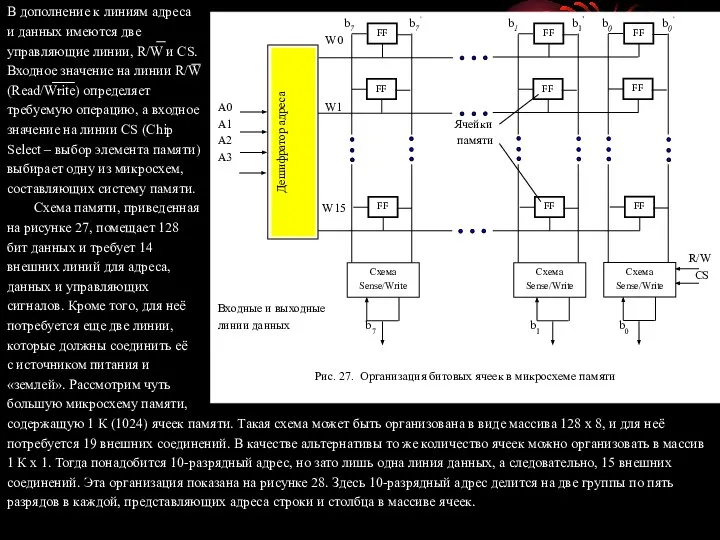

- 76. В дополнение к линиям адреса и данных имеются две управляющие линии, R/W и CS. Входное значение

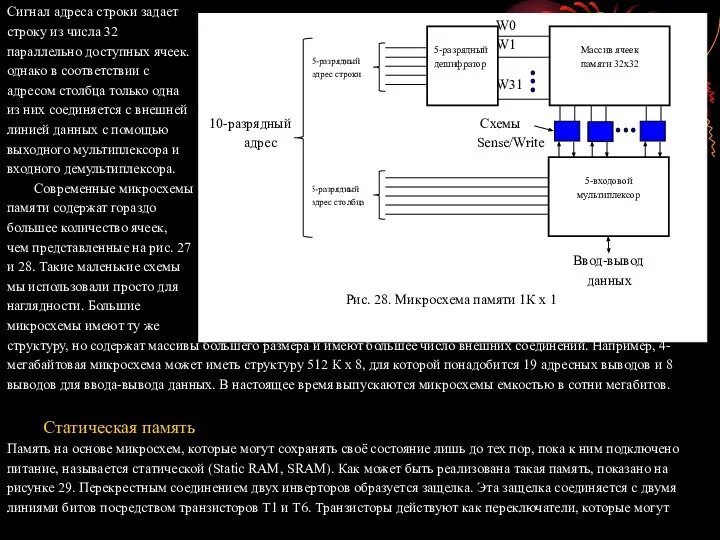

- 77. Сигнал адреса строки задает строку из числа 32 параллельно доступных ячеек. однако в соответствии с адресом

- 78. Операция чтения Для того, чтобы прочитать состояние ячейки SRAM, схемы управления памятью активируют линию слова, в

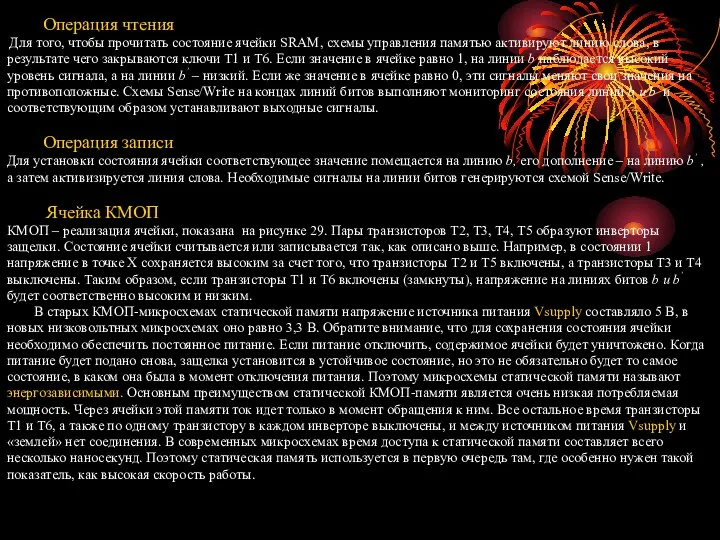

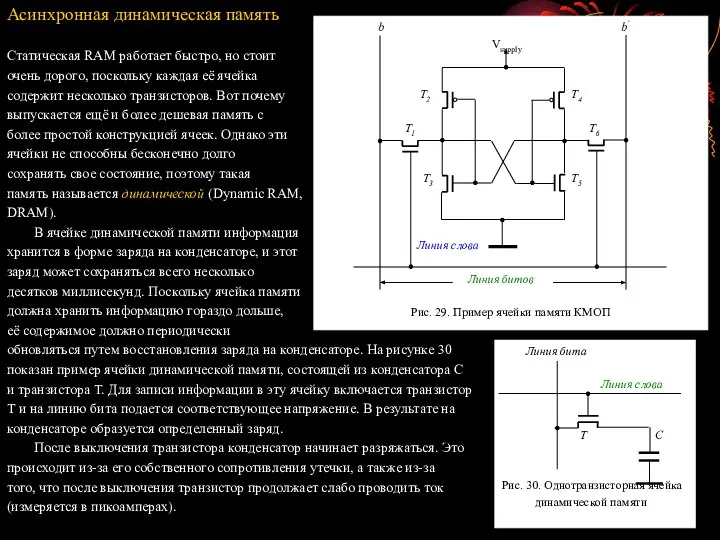

- 79. Асинхронная динамическая память Статическая RAM работает быстро, но стоит очень дорого, поскольку каждая её ячейка содержит

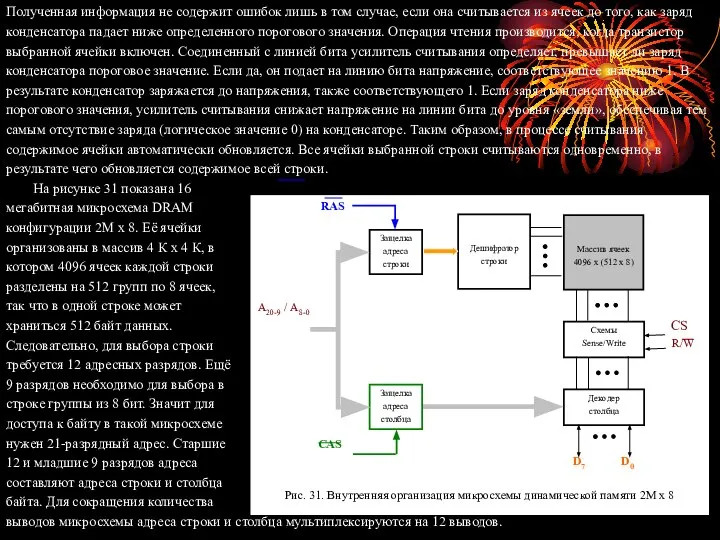

- 80. Полученная информация не содержит ошибок лишь в том случае, если она считывается из ячеек до того,

- 81. В процессе операции чтения или записи сначала на адресные выводы микросхемы подается адрес строки. В ответ

- 82. Быстрый постраничный объем При обращении к микросхеме DRAM, показанной на рисунке 31, считывается содержимое всех 4096

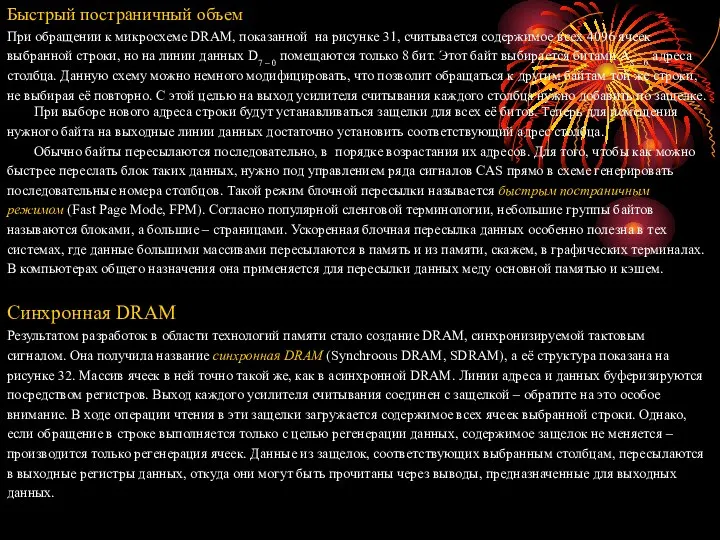

- 83. Память SDRAM может функционировать в нескольких режимах, определяемых управляющей информацией в регистре режима. Например, могут задаваться

- 84. На рисунке 33 приведена временная диаграмма типичной операции пакетного чтения длительностью 4 такта. Первым делом в

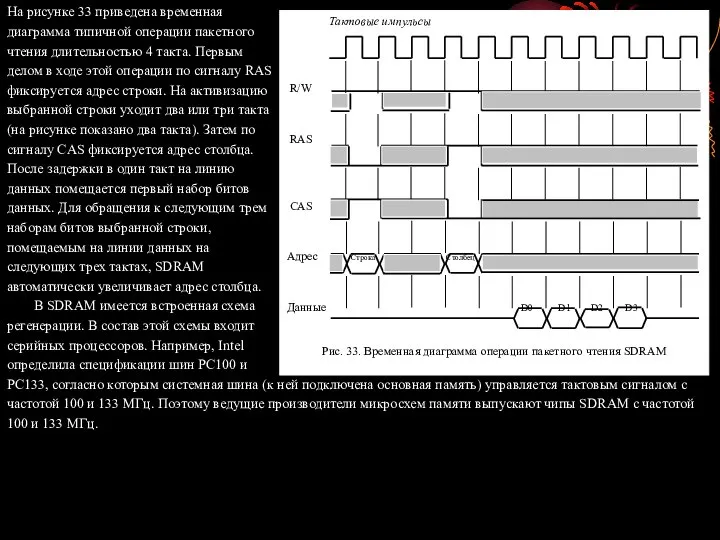

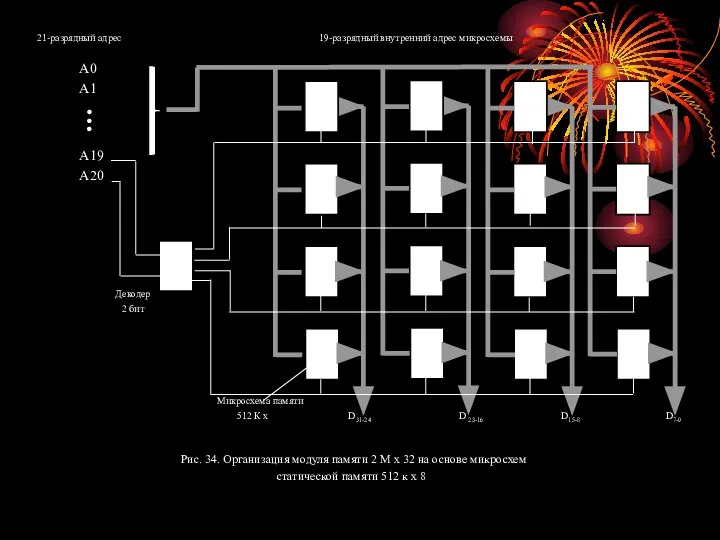

- 85. Структура памяти большого объема Рассмотрим память, которая сконструирована из отдельных микросхем, соединенных в крупные запоминающие устройства.

- 86. модуль памяти с однорядным расположением выводов) и DIMM (dual In Line Memory Module – модуль памяти

- 87. 21-разрядный адрес 19-разрядный внутренний адрес микросхемы A0 A1 A19 A20 Декодер 2 бит Микросхема памяти 512

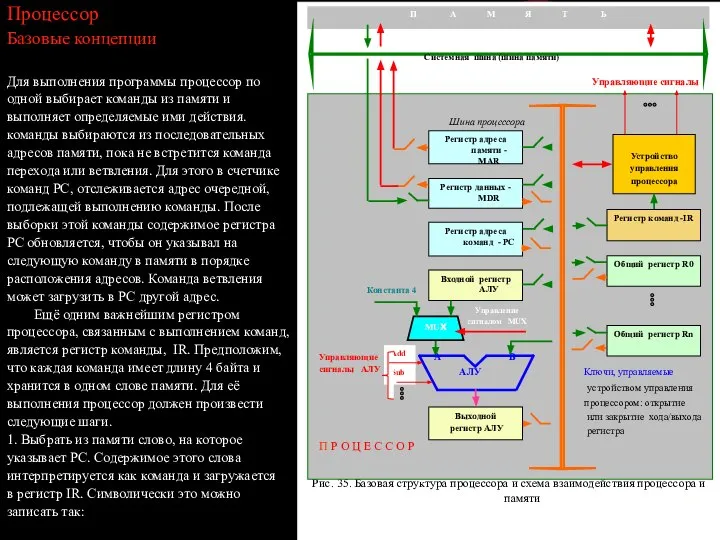

- 88. Процессор Базовые концепции Для выполнения программы процессор по одной выбирает команды из памяти и выполняет определяемые

- 89. IR ? [[PC]] 2. Если память адресуется побайтово, следует увеличить содержимое регистра PC на 4 PC

- 90. Два возможных значения управляющего входа мультиплексора. Определяющих выбор константы 4 или регистра входа в АЛУ, мы

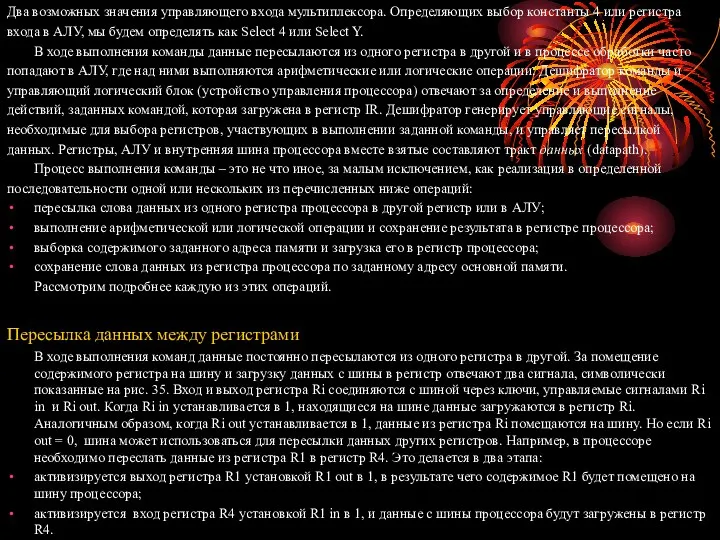

- 91. Все операции по пересылке данных внутри процессора выполняются в течение периода времени, определяемых тактовым сигналом процессора.

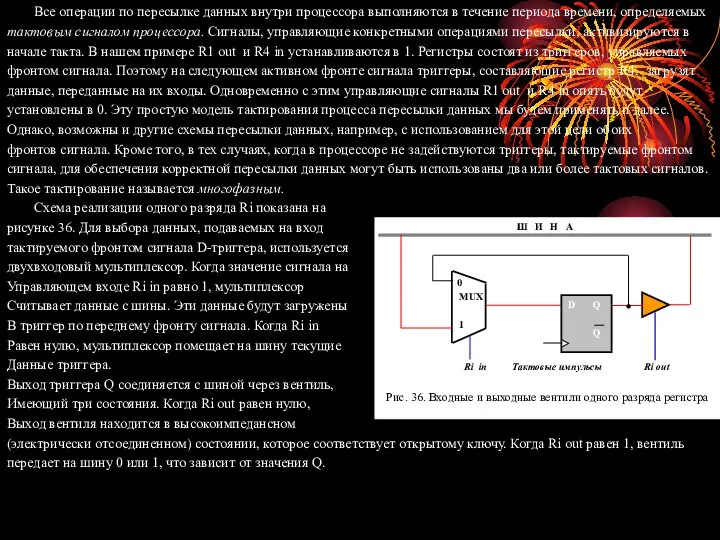

- 92. Выполнение арифметической или логической операции АЛУ представляет собой комбинированную схему, то есть такую, которая не способна

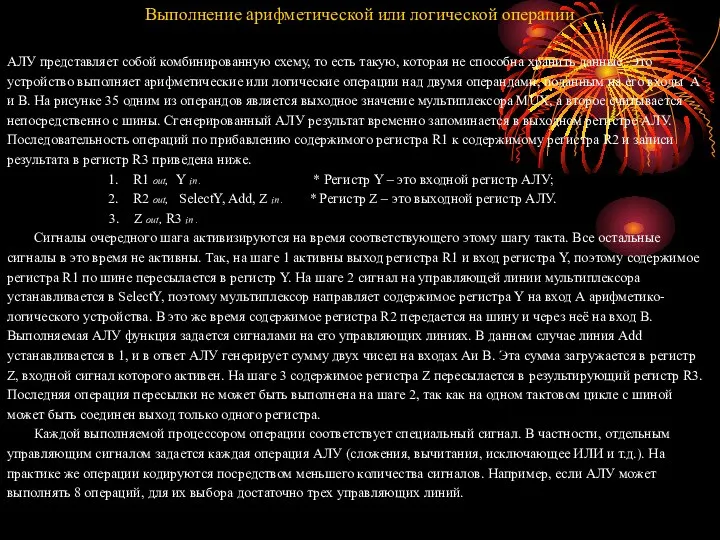

- 93. Выбор слова из памяти Чтобы выбрать из памяти слово информации, процессор должен задать адрес этого слова

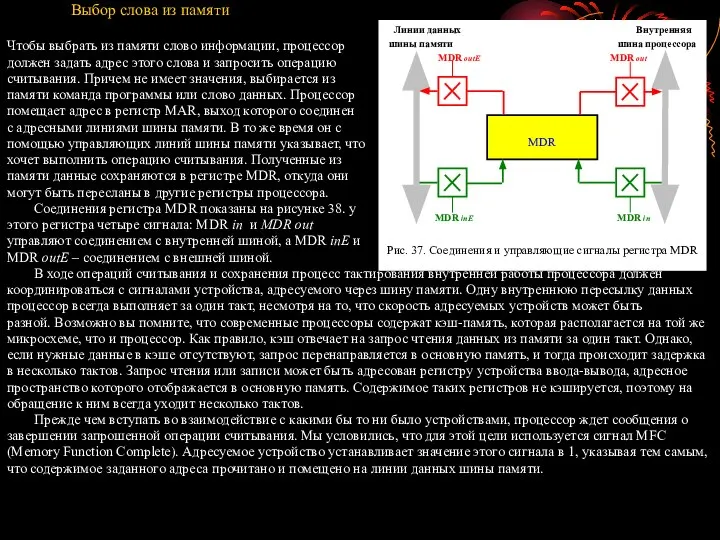

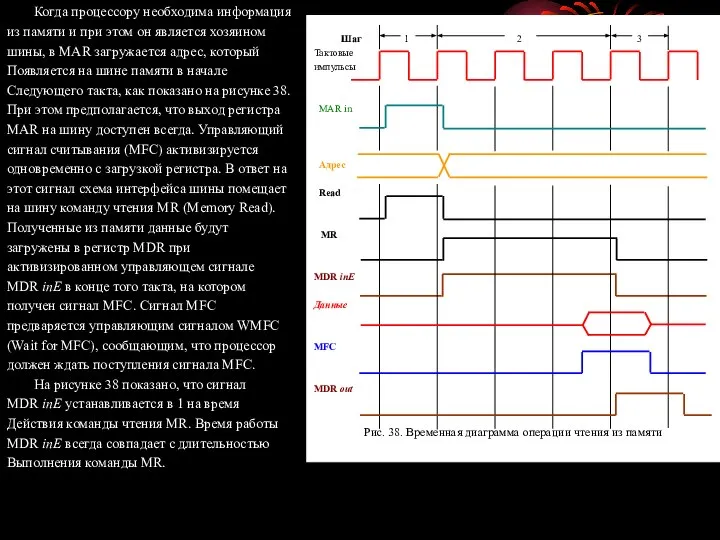

- 94. Когда процессору необходима информация из памяти и при этом он является хозяином шины, в MAR загружается

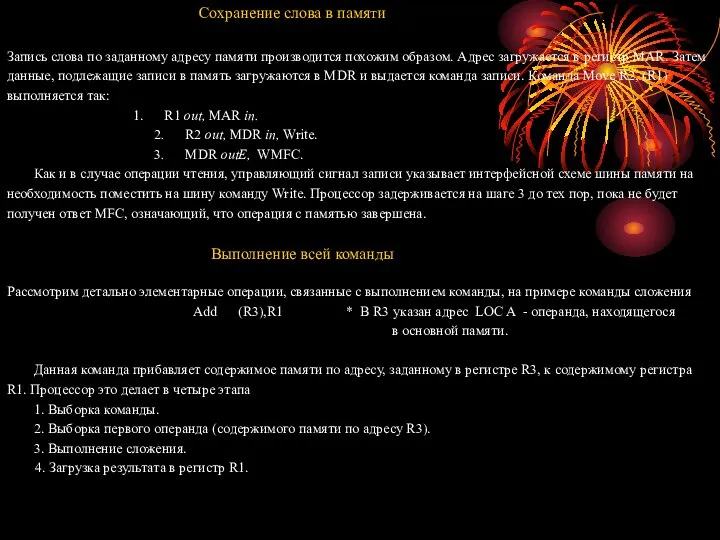

- 95. Сохранение слова в памяти Запись слова по заданному адресу памяти производится похожим образом. Адрес загружается в

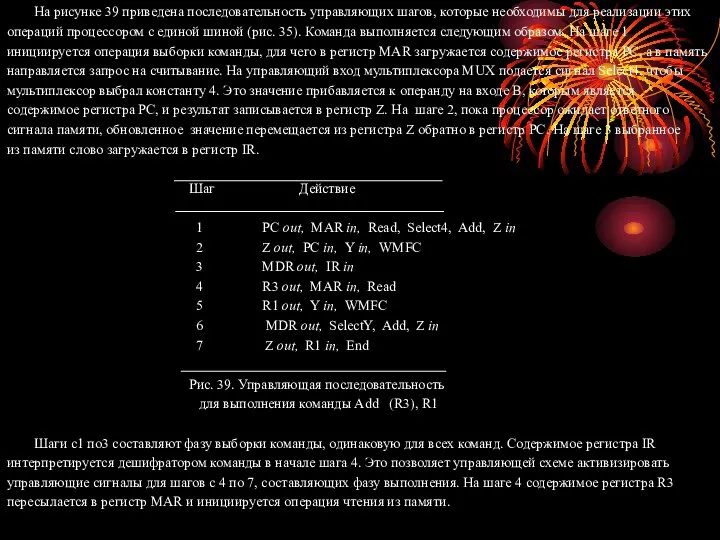

- 96. На рисунке 39 приведена последовательность управляющих шагов, которые необходимы для реализации этих операций процессором с единой

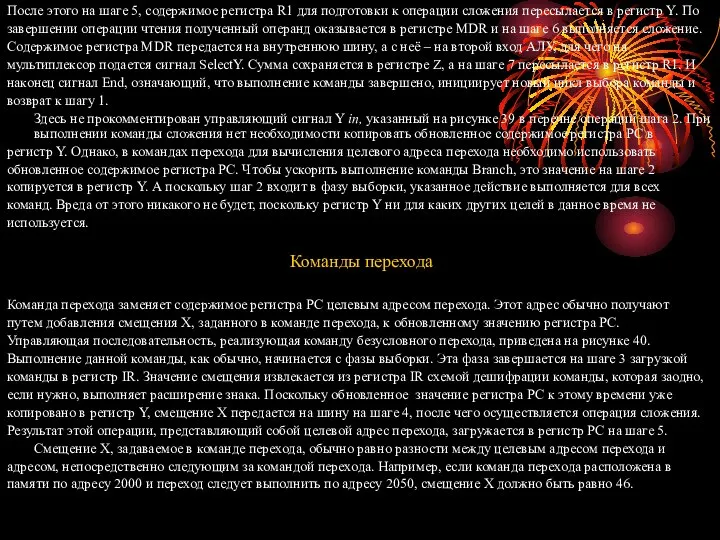

- 97. После этого на шаге 5, содержимое регистра R1 для подготовки к операции сложения пересылается в регистр

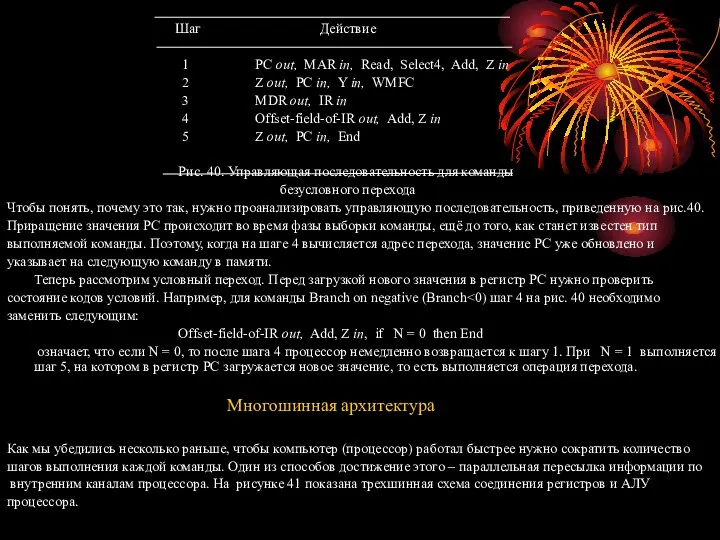

- 98. Шаг Действие 1 PC out, MAR in, Read, Select4, Add, Z in 2 Z out, PC

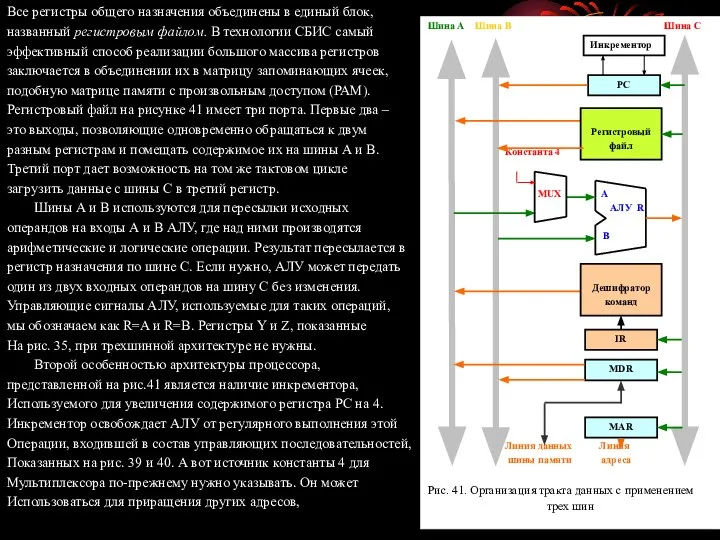

- 99. Все регистры общего назначения объединены в единый блок, названный регистровым файлом. В технологии СБИС самый эффективный

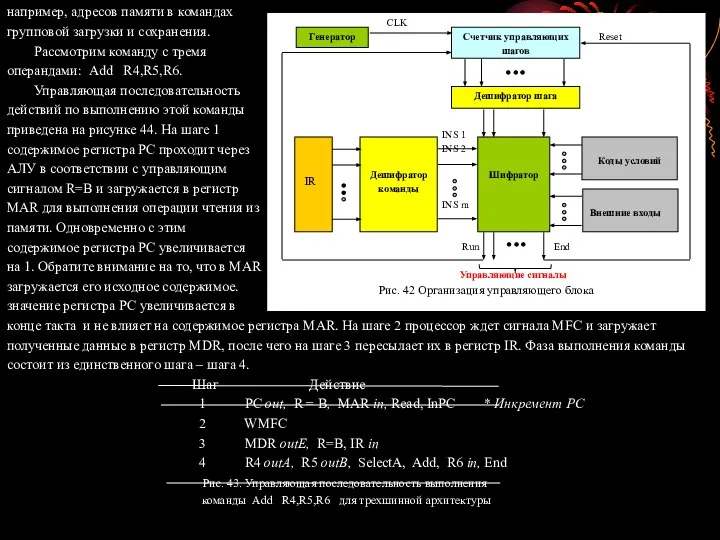

- 100. например, адресов памяти в командах групповой загрузки и сохранения. Рассмотрим команду с тремя операндами: Add R4,R5,R6.

- 101. Аппаратное управление Для выполнения команд процессор должен генерировать соответствующие последовательности управляющих сигналов. Разработчики компьютеров справляются с

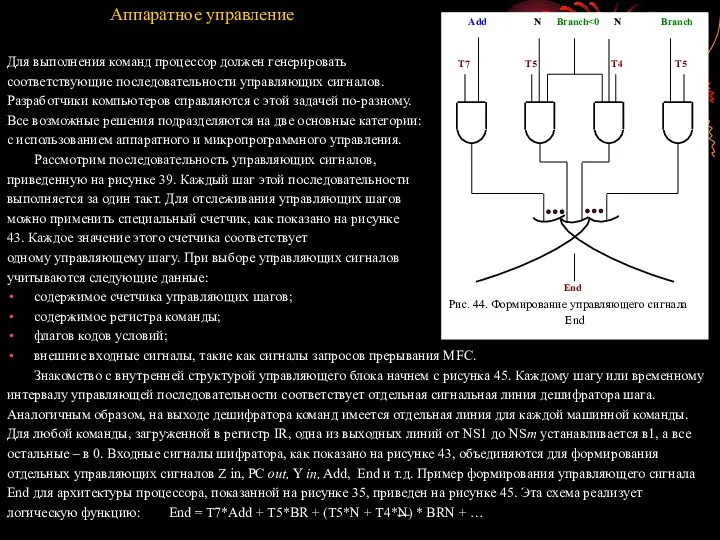

- 102. Сигнал End начинает новый цикл выборки команды, сбрасывая счетчик управляющих шагов в начальное состояние. На рисунке

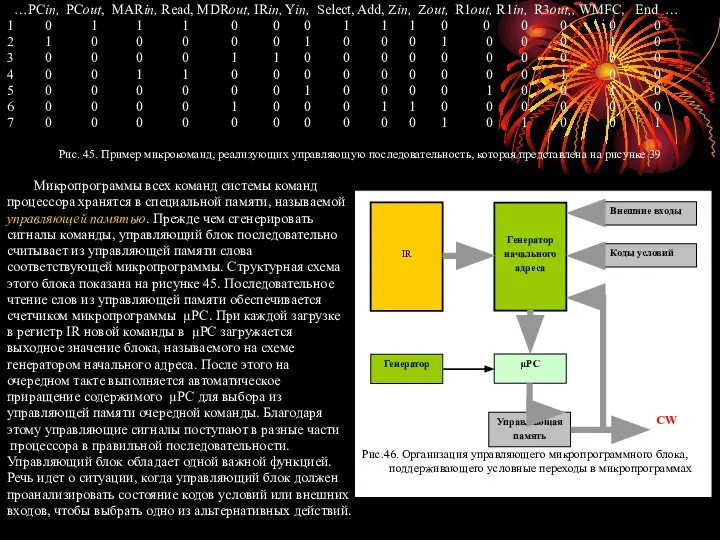

- 103. …PCin, PCout, MARin, Read, MDRout, IRin, Yin, Select, Add, Zin, Zout, R1out, R1in, R3out,, WMFC, End

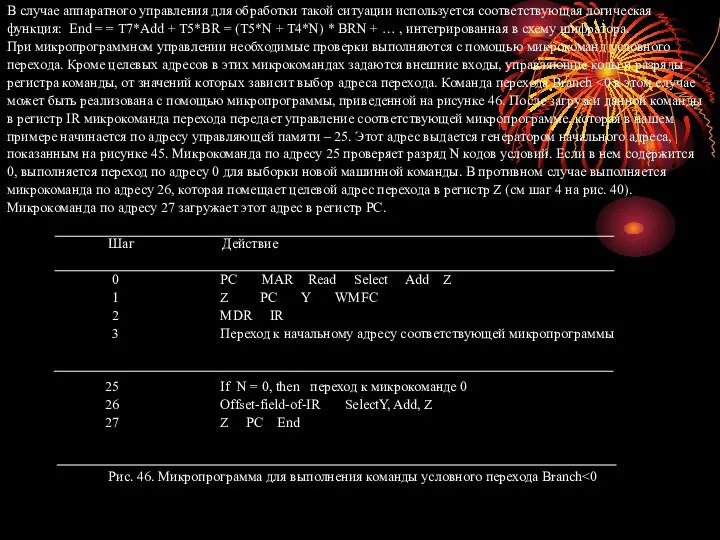

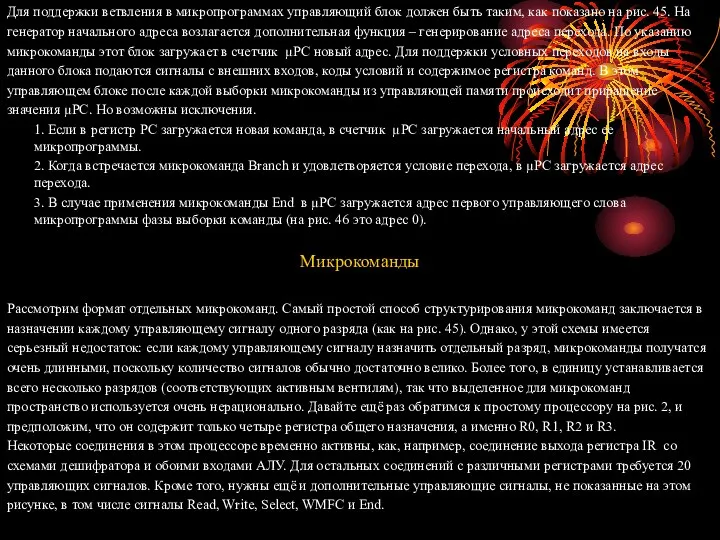

- 104. В случае аппаратного управления для обработки такой ситуации используется соответствующая логическая функция: End = = T7*Add

- 105. Для поддержки ветвления в микропрограммах управляющий блок должен быть таким, как показано на рис. 45. На

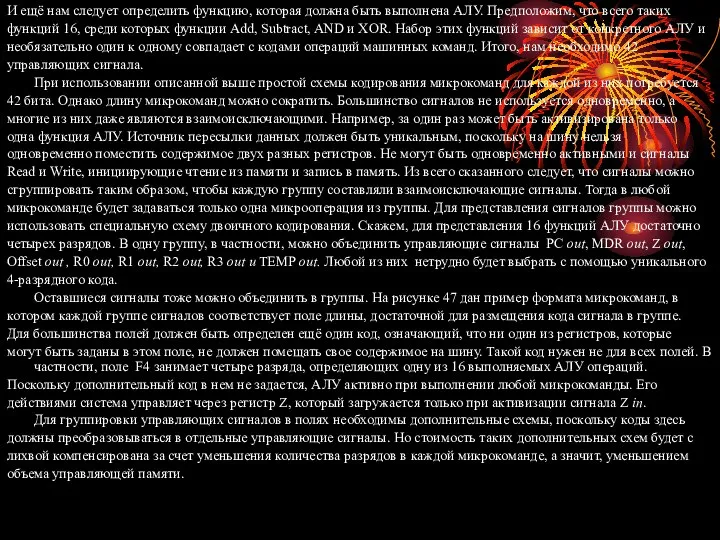

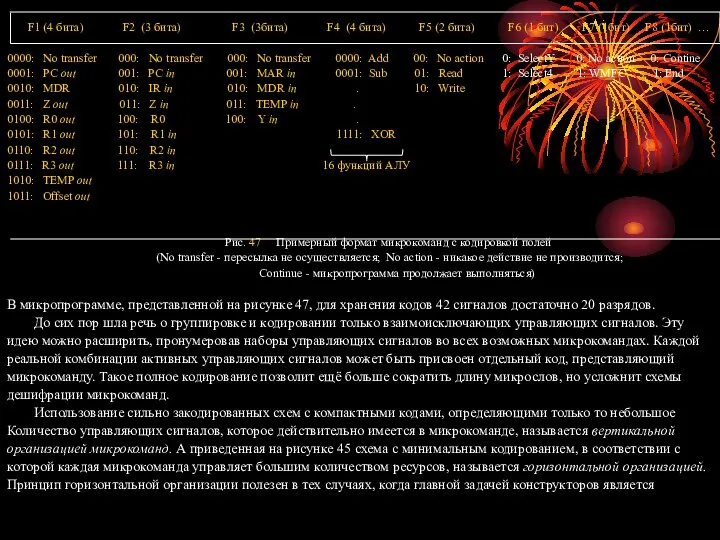

- 106. И ещё нам следует определить функцию, которая должна быть выполнена АЛУ. Предположим, что всего таких функций

- 107. F1 (4 бита) F2 (3 бита) F3 (3бита) F4 (4 бита) F5 (2 бита) F6 (1

- 109. Скачать презентацию

Базовая структура компьютера

Функциональная структура

Компьютер состоит из пяти главных , функционально

Базовая структура компьютера

Функциональная структура

Компьютер состоит из пяти главных , функционально

Полученные результаты отправляются обратно во внешний мир, посредством устройства вывода.

Полученные результаты отправляются обратно во внешний мир, посредством устройства вывода.

Обрабатываемую компьютером информацию принято разделять на две основные категории: команды и данные. Команды, или машинные команды, - это явно заданные инструкции, которые:

управляют пересылкой информации внутри компьютера, а также между компьютером и его устройствами ввода-вывода;

определяют подле6жащие выполнению арифметические и логические операции.

Список команд, выполняющих некоторую задачу, называется программой. Обычно программы хранятся в памяти. Процессор по очереди извлекает команды программы из памяти и реализует (выполняет) определяемые ими операции. Компьютер полностью управляется хранимой программой, если не считать возможность внешнего вмешательства оператора (человека управляющего ходом выполнения программы) и подсоединенных к машине устройств ввода-вывода.

Данные – это числа и закодированные символы, используемые в качестве операндов команд. Операнды – это то, над чем выполняются действия в команде. Однако, термин «данные» часто используется для обозначения любой цифровой информации. Согласно этому определению, сама программа (то е6сть список команд) также может считаться данными, если она обрабатывается другой программой. Примером обработки одной программой другой является компиляция исходной программы – перевод программы, написанной на языке высокого уровня, в список машинных команд, составляющих программу на машинном языке, которая начинает называться объектной программой. Исходная программа поступает на вход компилятора, который транслирует ее в программу на машинном языке.

Информация, предназначенная для обработки компьютером, должна быть закодирована, чтобы иметь подходящий для компьютера формат. Современное аппаратное обеспечение в большинстве своем основано на цифровых схемах, у которых имеется только два устойчивых состояния ON и OFF (включено и выключено 1 или 0). В результате кодирования любое число, символ или команда преобразуются в строку двоичных цифр, называемых битами, каждый из которых имеет одно из двух возможных значений: 0 или 1.

Буквы и цифры также представляются посредством двоичных кодов. Для них разработано несколько разных схем кодирования. Наиболее распространенными считаются схемы ASCII (American Standard Code for Information Interchange – американский стандартный код для обмена информацией), где каждый символ представлен 7-битным кодом, и EBCDIC (Extended Binary Coded Decimal Interchange Code –расширенный двоично-десятичный код для обмена информацией), в котором для кодирования символа используется 8 бит.

Устройство ввода

Компьютер принимает кодированную информацию через устройство ввода, задачей которого

Устройство ввода

Компьютер принимает кодированную информацию через устройство ввода, задачей которого

Существуют другие устройства ввода, например, такие как : джойстики, трекболы и мыши. Они используются совместно с дисплеем в качестве графических входных устройств. Для ввода звука могут использоваться микрофоны. Воспринимаемые ими звуковые колебания измеряются и конвертируются (преобразуются) в цифровые коды для хранения и обработки.

Блок памяти

Задачей блока памяти является хранение программ и данных. Существует два класса запоминающих устройств, а именно первичные и вторичные. Первичное запоминающее устройство (primary storage) – это память, быстродействие которой определяется скоростью работы электронных схем. Пока программа выполняется, она должна храниться в первичной памяти. Эта память состоит из большого количества полупроводниковых ячеек, каждая из которых может хранить один бит информации. Ячейки редко считываются по отдельности – обычно они обрабатываются группами фиксированного размера, называемыми словами. Память организована так, что содержимое одного слова, содержащего n бит, может записываться или считываться за одну базовую операцию.

Для облегчения доступа к словам в памяти с каждым словом связывается отдельный адрес. Адреса – это числа, идентифицирующие конкретные местоположения слов в памяти. Для того, чтобы прочитать слово из памяти или записать его в таковую, необходимо указать его адрес и задать управляющую команду, которая начнет соответствующую операцию.

Количество битов в каждом слове часто называю длиной машинного слова. Обычно слово имеет длину от 16 до 64 бит. Одним из факторов, характеризующих класс компьютера, является емкость его памяти. Малые машины обычно могут хранить лишь несколько десятков миллионов слов, тогда как средние и большие машины обычно способны хранить сотни миллионов слов. Типичными единицами измерения количества обрабатываемых машиной данных являются слово, несколько слов или часть слова. Как правило, за время одного обращения к памяти считывается или записывается только одно слово.

Во время выполнения программа все время должна находиться в памяти.

Во время выполнения программа все время должна находиться в памяти.

Арифметико-логическое устройство

Большинство компьютерных операций выполняется в арифметико-логическом устройстве (АЛУ) процессора. Типичным примером может служить выполнение сложения или другой арифметической или логической операции. АЛУ работает во много раз быстрее, чем все остальные устройства, подключенные к компьютерной системе. Это позволяет одному процессору контролировать множество внешних устройств, таких как клавиатуры, дисплеи, магнитные и оптические диски, сенсоры и механические управляющие устройства.

Блок вывода

Функция блока вывода противоположна функции блока ввода: он направляет результаты обработки данных в так называемый внешний мир. Типичным примером устройства вывода является принтер. Механизмами печати в принтерах используются ударные механизмы, головки, выпрыскивающие струи чернил, или технология фотокопирования, как в лазерных принтерах.

Некоторые устройства выполняют одновременно и функции устройства ввода и устройства вывода. Это, например, графические дисплеи. Поэтому такие устройства называют устройствами ввода-вывода.

Блок управления (устройство управления)

Работу всех устройств, в том числе устройств процессора нужно как-то координировать. Именно этим и занимается блок управления компьютера, с некоторых пор внесенный непосредственно в процессор. Это, если можно так выразиться, нервный центр компьютера, передающий управляющие сигналы другим устройствам и отслеживающий их состояние.

Управление операциями ввода-вывода осуществляется командами программ, в которых идентифицируются соответствующие устройства

Управление операциями ввода-вывода осуществляется командами программ, в которых идентифицируются соответствующие устройства

В целом, функционирование компьютера можно описать следующим образом.

Компьютер с помощью блока ввода принимает информацию в виде программ и данных и записывает ее в память.

Хранящаяся в памяти информация под управлением программы пересылается в арифметико-логическое устройство для дальнейшей обработки.

Данные, полученные в результате обработки информации, направляются на устройства вывода.

За все действия, производимые внутри машины, отвечает блок управления.

Основные концепции функционирования

Как было отмечено выше, действиями компьютера управляют инструкции. Для выполнения конкретной задачи в память записывается соответствующая программа, состоящая из множества команд. Команды по очереди пересылаются из памяти в процессор, который их выполняет. Данные, используемые в качестве операндов команд, также хранятся в памяти. Пример типичной команды, запрограммированной на языке Ассемблер:

Add LOCA, R0

Эта команда складывает операнд, хранящийся в памяти по адресу LOCA, с операндом, хранящимся в регистре R0 процессора, и помещает результат в этот же регистр. Состояние памяти, после того как из нее команда загрузится в процессор и операнд загрузится в процессор - не изменится, а содержимое регистра R0 после выполнения команды перезапишется. Данная команда выполняется в несколько этапов. Сначала она пересылается из памяти в процессор. Затем операнд команды считывается из памяти по адресу LOCA и складывается с содержимым регистра R0, после чего результирующая сумма записывается в регистр R0.

Пересылка данных между памятью и процессором начинается с отправки в устройство

Пересылка данных между памятью и процессором начинается с отправки в устройство

На рисунке 1.2 показано, как соединяются между собой память и процессор.

Кроме АЛУ и управляющих схем процессор содержит множество регистров, предназначенных для

Кроме АЛУ и управляющих схем процессор содержит множество регистров, предназначенных для

Ещё два регистра обеспечивают процесс взаимодействия с памятью. Это регистр адреса (Memory Address Register, MAR) и регистр данных (Memory Data Register, MDR). В регистре MAR содержится адрес, по которому производится обращение к памяти, а в регистре MDR – данные, которые должны быть записаны в память или прочитаны из неё по этому адресу.

Рассмотрим типичный пример процесса выполнения программы компьютером. Программа располагается в памяти, куда обычно попадает через какое-либо устройство ввода Её выполнение начинается с записи в регистр PC адреса первой команды. Содержимое этого регистра пересылается в регистр MAR, а в память направляется управляющий сигнал Read. Когда истекает время, необходимое для доступа к памяти, адресуемое слово ( в данном случае – первая команда программы) считывается из памяти и загружается в регистр MDR. Затем содержимое регистра MDR пересылается в регистр IR. Команда готова к декодированию и выполнению.

Если команда требует, чтобы АЛУ выполнило определенную операцию, для неё необходимо получить операнды. Операнд, располагающийся в памяти (он может находиться и в регистре общего назначения), нужно сначала из таковой извлечь, переслав его адрес в регистр MAR и инициализировав цикл Read. После пересылки из памяти в регистр MDR операнд будет направлен в АЛУ. Аналогичным образом туда же будут переданы и остальные необходимые команде операнды, после чего АЛУ сможет выполнить требуемую операцию. Если результат должен быть сохранен в памяти, он будет записан в регистр MDR. Затем адрес, по которому его нужно записать в память, будет помещен в регистр MAR. После чего будет инициирован цикл Write. В какой-то момент в ходе выполнения текущей инструкции содержимое регистра PC увеличивается, и он начинает указывать на следующую подлежащую выполнению инструкцию.

Другими словами, как только завершится выполнение текущей инструкции, можно будет приступить

Другими словами, как только завершится выполнение текущей инструкции, можно будет приступить

Компьютер не только пересылает данные между памятью и процессором, но и принимает их от входных устройств, а также отсылает выходным устройствам. Поэтому среди машинных команд имеются и команды для выполнения операций ввода-вывода.

Если возникает необходимость срочно обслужить некоторое устройство (например, когда устройство мониторинга в автоматизированном промышленном процессе обнаружит опасную ситуацию), нормальное выполнение программы может быть прервано. Для того чтобы немедленно отреагировать на эту ситуацию, компьютер должен прервать выполнение текущей программы. С этой целью устройство генерирует сигнал прерывания. Прерывание (interrupt) – это запрос, поступающий от устройства ввода-вывода, с требованием предоставить ему процессорное время. Для обслуживания этого устройства процессор выполняет соответствующую программу обработки прерывания. А поскольку её выполнение может изменить внутреннее состояние процессора, перед обслуживанием прерывания нужно сохранить его состояние в памяти. Обычно в ходе этой операции сохраняется содержимое регистра PC, регистров общего назначения и некоторая управляющая информация. По завершении работы программы обработки прерывания состояние процессора восстанавливается и прерванная программа продолжает свою работу. Процессор со всеми его элементами (рис.1.1) обычно реализуется в виде одной микросхемы, на которой располагается как минимум одно устройство кэш-памяти. Такие микросхемы – чипы – называются VLSI (VLSI – аббревиатура от Very Large Scale Integration, что переводится как очень крупномасштабная интеграция).

Структура шины

Чтобы составить и изготовить действующую систему, необходимо все ее части соединить между собой определенным образом. Способов соединения существует очень много. Мы рассмотрим лишь простейшие и самые распространенные из них.

Компьютер сможет работать с достаточной скоростью лишь при условии, что будет организован таким образом, чтобы полное слово данных обрабатывалось им за указанное время. Когда слово данных пересылается между устройствами, параллельно перемещаются все его биты. Каждый бит пересылается по своему проводу (линии), так что для пересылки слова требуется несколько параллельных линий. Группа линий, образующая соединение между несколькими устройствами, называется шиной (bus). Наряду с линиями, по которым пересылаются данные, шина содержит линии для передачи адреса и управляющих сигналов.

Для соединения нескольких функциональных устройств компьютера проще всего использовать общую шину

Для соединения нескольких функциональных устройств компьютера проще всего использовать общую шину

К этой шине подсоединяются все устройства компьютера. Поскольку за один раз по шине может пересылаться только одно слово данных, в каждый конкретный момент шину могут использовать только два устройства. Для организации процесса параллельной обработки нескольких запросов используются линии управления шиной. Главным достоинством архитектуры с общей шиной является ее низкая стоимость и гибкость в отношении подключения периферийных устройств. При наличии в системе нескольких шин возможно одновременное выполнение нескольких операций пересылки данных, благодаря чему такая система работает быстрее, но и стоимость выше.

Подсоединенные к шине устройства могут заметно отличаться друг от друга по скорости функционирования. Некоторые электромеханические устройства, в том числе клавиатуры и принтеры, работают относительно медленно. Значительно выше скорость работы, скажем магнитных и оптических дисков. А память и процессор функционируют со скоростью электронных схем, благодаря чему являются самыми быстрыми частями компьютера. Поскольку все эти три типа устройств могут взаимодействовать между собой через шину, необходим такой механизм пересылки данных, который не ограничивал бы скорость обмена информацией между любыми двумя устройствами скоростью более медленного из них и сглаживал бы разницу в скорости работы процессора, памяти и внешних устройств.

Самый распространенный подход к решению этой задачи основан на использовании буферных регистров , которые встраиваются во внешние устройства для хранения получаемой ими информации. Для примера можно рассмотреть процесс передачи кода символа от процессора принтеру. Процессор пересылает данные по шине в буфер принтера. Поскольку буфер представляет собой электронный регистр, пересылка выполняется очень быстро. Когда буфер будет заполнен, принтер начнет печатать, и вмешательство процессора больше не потребуется. Шина и процессор освобождаются для другой работы, которая может выполняться одновременно с печатью символа, хранящегося в буфере принтера. Таким образом, использование буферных регистров сглаживает различия в скорости функционирования процессора, памяти и устройств ввода-вывода и предотвращает блокирование высокоскоростного процессора медленными устройствами на все время выполнения операций ввода-вывода. Процессор может быстро переключаться от одного устройства к другому, обслуживая их параллельно.

Программное обеспечение

Для того, чтобы пользователь мог запустить прикладную программу, в памяти

Программное обеспечение

Для того, чтобы пользователь мог запустить прикладную программу, в памяти

получение и интерпретация команд пользователя;

ввод и редактирование прикладных программ, их сохранение в файлах на вторичных запоминающих устройствах;

управление процессом сохранения файлов на вторичных запоминающих устройствах и извлечение их с указанных устройств;

запуск стандартных прикладных программ, таких как текстовые процессоры, электронные таблицы или игры, с данными, которые предоставляются пользователем;

управление устройствами ввода-вывода для получения входной информации и вывода выходных данных;

трансляция исходного кода программ, подготовленных ранее пользователем, в объектные модули, состоящие из машинных команд;

компоновка пользовательских прикладных программ со стандартными библиотечными подпрограммами (например, выполняющими числовые вычисления) и запуск результирующих программ.

Таким образом, системное программное обеспечение отвечает за координирование всех операций, выполняемых в компьютерной системе. Прикладные программы обычно пишутся на языках программирования высокого уровня, в том числе на C, C++, Java и FORTRAN, позволяющих программисту задать действия, которые должна выполнить программа (скажем математические вычисления или обработку строк текста). Такие операции описываются в формате, не зависящем от компьютера, который будет выполнять программу.

Программисту, использующему язык высокого уровня, не нужно знать машинные команды и особенности их использования. Специальная системная программа, называемая компилятором, транслирует программу на языке высокого уровня в программу на машинном языке.

Ещё одна важная системная программа, которой пользуются все программисты, называется текстовым редактором. Она предназначена для ввода и редактирования прикладных программ. Пользователь такой программы с помощью клавиатуры вводит и редактирует инструкции исходного текста программы и накапливает их в файле. Файл – это просто последовательность буквенно-цифровых символов или двоичных данных, которая сохраняется в памяти ил на вторичном запоминающем устройстве.. К файлу можно обращаться по заданному пользователем имени.

Обратимся к важному для компьютера понятию операционная система (ОС). Это набор программ, используемый для управления взаимодействием различных устройств компьютера при выполнении прикладных программ. Компоненты операционной системы отвечают за предоставление прикладным программам ресурсов компьютера – основной памяти и памяти на магнитных дисках, устройств ввода-вывода и т.д.

рассмотрим как функционирует ОС на небольшом примере. Предположим, у нас имеется уже откомпилированная прикладная программа, сохраненная в виде машинных команд на диске. Процесс иллюстрирован линейной диаграммой, показанной на рисунке 1.4.

В течение времени от момента t0 до момента t1 одна из

В течение времени от момента t0 до момента t1 одна из

При этом имеется возможность более эффективного использования ресурсов компьютера, заключающийся в параллельном выполнении нескольких программ. Например, на отрезке времени работы принтера операционная система могла бы загрузить в память следующую программу. Аналогичным образом, в промежутке времени от t0 до t1 операционная система могла бы печатать результат, сгенерированные предыдущей программой (пока текущая программа загружается с диска). Именно так операционная система управляет параллельным выполнением нескольких прикладных программ, обеспечивая поочередное использование им ресурсов компьютера. Такая схема параллельного выполнения программ называется многозадачностью.

Производительность

Одним из важнейших параметров оценки того, насколько быстро компьютер выполняет программы

Производительность

Одним из важнейших параметров оценки того, насколько быстро компьютер выполняет программы

Общее время выполнения программы (см.рис. 1.4) t5 – t0 является мерой производительности всей компьютерной системы. Оно зависит от быстродействия процессора, диска и принтер. Рассматривая производительность процессора, мы должны учитывать только те периоды, в течение которых он активен. На рисунке 1.4 они соответствуют обозначениям «Прикладная программа» и «Программа ОС». Суммарное время выполнения прикладных программ и программ операционной системы называется процессорным временем, необходимым для выполнения программы.

Равно как общее время выполнения программы зависит от скорости работы всех устройств компьютерной системы, процессорное время зависит от аппаратного обеспечения, участвующего выполнении конкретных машинных команд. Аппаратное обеспечение включает процессор и память, обычно соединенные шиной ( см. рис. 1.3). Архитектура системы с общей шиной, представленная на рисунке 1.5 , отличается от приведенной на рис.1.3 лишь наличием кэш-памяти, включенной в состав процессорного устройства.

Какую роль играет кэш-память в производительности компьютера? По мере выполнения программы

Какую роль играет кэш-память в производительности компьютера? По мере выполнения программы

Процессор и относительно небольшая кэш-память могут располагаться на одном интегрированном чипе. Внутренняя скорость выполнения команд таким чипом очень высока – она гораздо выше, чем скорость выборки команд и данных из памяти. Поэтому программа будет выполняться быстрее при условии минимизации количества команд и объема данных, перемещаемых между процессором и основной памятью. Для этого и предназначается кэш процессора. Возьмем, к примеру, многократное выполнение одной и той же группы команд в течение короткого промежутка времени, как это часто бывает в программных циклах. Если эти команды находятся в кэше, их можно быстро извлекать оттуда в течение всего времени их по многу раз повторяющегося выполнения. Сказанное касается и многократно используемых данных.

Частота процессора

Управление процессором осуществляется с помощь сигналов, которые называются тактовыми импульсами (clock) и выдаются через фиксированные интервалы времени. Промежуток времени между двумя тактовыми импульсами составляет тактовый цикл (clock cycle), или просто такт. Для выполнения машинной команды процессор разделяет ее на последовательность базовых шагов, каждый из которых может быть выполнен за один такт. Длительность одного тактового цикла Т является важнейшим параметром, определяющим производительность процессора. Обратное значение F=1/Т, называется тактовой частотой (clock rate) процессора, измеряется количеством тактов в секунду и называется Гц (Герц). Процессоры современных компьютеров работают на частотах равных миллионам Гигагерц (ГГц).

Формула производительности, определяемой через тактовую частоту

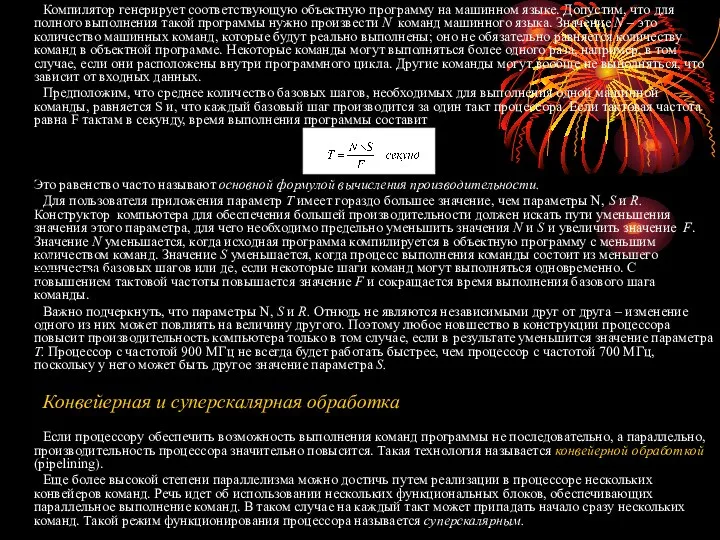

Одним из компонентов общего времени выполнения программы является процессорное время. Предположим, что для реализации программы, написанной на одном из языков высокого уровня, требуется Т секунд (с) процессорного времени.

Компилятор генерирует соответствующую объектную программу на машинном языке. Допустим, что для

Компилятор генерирует соответствующую объектную программу на машинном языке. Допустим, что для

Предположим, что среднее количество базовых шагов, необходимых для выполнения одной машинной команды, равняется S и, что каждый базовый шаг производится за один такт процессора. Если тактовая частота равна F тактам в секунду, время выполнения программы составит

Это равенство часто называют основной формулой вычисления производительности.

Для пользователя приложения параметр T имеет гораздо большее значение, чем параметры N, S и R. Конструктор компьютера для обеспечения большей производительности должен искать пути уменьшения значения этого параметра, для чего необходимо предельно уменьшить значения N и S и увеличить значение F. Значение N уменьшается, когда исходная программа компилируется в объектную программу с меньшим количеством команд. Значение S уменьшается, когда процесс выполнения команды состоит из меньшего количества базовых шагов или де, если некоторые шаги команд могут выполняться одновременно. С повышением тактовой частоты повышается значение F и сокращается время выполнения базового шага команды.

Важно подчеркнуть, что параметры N, S и R. Отнюдь не являются независимыми друг от друга – изменение одного из них может повлиять на величину другого. Поэтому любое новшество в конструкции процессора повысит производительность компьютера только в том случае, если в результате уменьшится значение параметра Т. Процессор с частотой 900 МГц не всегда будет работать быстрее, чем процессор с частотой 700 МГц, поскольку у него может быть другое значение параметра S.

Конвейерная и суперскалярная обработка

Если процессору обеспечить возможность выполнения команд программы не последовательно, а параллельно, производительность процессора значительно повысится. Такая технология называется конвейерной обработкой (pipelining).

Еще более высокой степени параллелизма можно достичь путем реализации в процессоре нескольких конвейеров команд. Речь идет об использовании нескольких функциональных блоков, обеспечивающих параллельное выполнение команд. В таком случае на каждый такт может припадать начало сразу нескольких команд. Такой режим функционирования процессора называется суперскалярным.

Оценка производительности

Чтобы оценить производительность компьютера, ее необходимо как-то измерить.

Руководствуясь показателем производительности,

Оценка производительности

Чтобы оценить производительность компьютера, ее необходимо как-то измерить.

Руководствуясь показателем производительности,

Ранее было определено, что наиболее точно определяющим производительность компьютера, является время выполнения программы Т. Несмотря на концептуальную простоту формулы вычислить значение Т не так-то просто. Поэтому производительность компьютеров принято измерять с помощью тестовых программ. Для того, чтобы можно было сравнивать производительность разных систем, эти программы должны быть стандартизированы. Показателем производительности является время, в течение которого компьютер выполняет заданный тест.

В настоящее время общепринятой практикой является использование некоторого набора специально подобранных реальных прикладных программ. Подбором таких приложений занимается некоммерческая организация под названием System Performance Evaluation Corporation (SPEC). Она публикует списки программ для разных прикладных областей и результаты тестирования многих имеющихся на рынке моделей компьютеров.

В этот список входят самые разнообразные программы, от игр, компиляторов и приложений баз данных до программ, производящих интенсивные вычисления в области астрофизики и квантовой химии. В каждом случае программа компилируется для тестируемого компьютера и измеряется реальное время её выполнения на этом компьютере. Никакая эмуляция не допускается. Та же самая программа компилируется и выполняется на компьютере, выбранном в качестве эталона. Для теста SPEC95 в качестве такового применяется компьютер SUN SPARCstation 10/40, а для теста SPEC2000 – рабочая станция UltraSPARC10 с процессором UltraSPARC –Iii, тактовая частота которого составляет 300 МГц. Коэффициент производительности SPEC вычисляется по следующей формуле:

Время выполнения на эталонном компьютере

SPEC – коэффициент =

Время выполнения на тестируемом компьютере

Таким образом, SPEC – коэффициент 50 указывает на то, что тестируемый компьютер выполняет данный тест в 50 раз быстрее, чем компилятор UltraSPARC10.

Для проведения полного тестирования по очереди компилируются и выполняются все программы из списка SPEC, а затем вычисляется среднее геометрическое полученных результатов. Итоговый SPEC – коэффициент для конкретного компьютера рассчитывается по формуле:

Символы

Компьютеры должны обрабатывать не только числа, но и текстовую информацию, состоящую

Символы

Компьютеры должны обрабатывать не только числа, но и текстовую информацию, состоящую

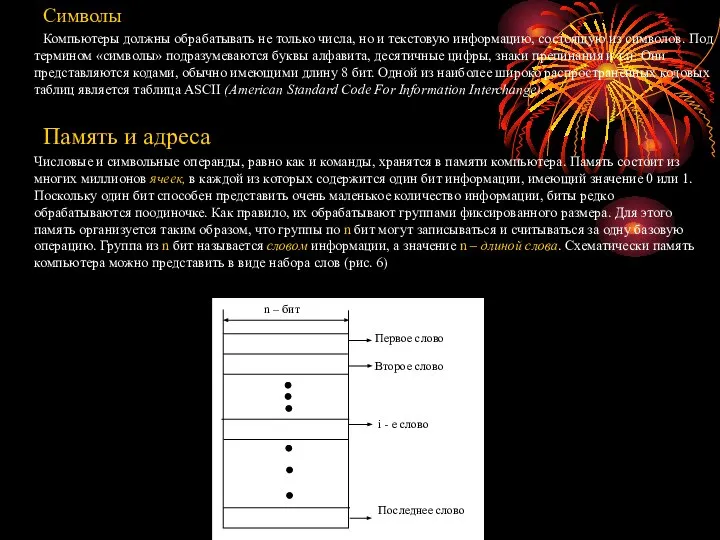

Память и адреса

Числовые и символьные операнды, равно как и команды, хранятся в памяти компьютера. Память состоит из многих миллионов ячеек, в каждой из которых содержится один бит информации, имеющий значение 0 или 1. Поскольку один бит способен представить очень маленькое количество информации, биты редко обрабатываются поодиночке. Как правило, их обрабатывают группами фиксированного размера. Для этого память организуется таким образом, что группы по n бит могут записываться и считываться за одну базовую операцию. Группа из n бит называется словом информации, а значение n – длиной слова. Схематически память компьютера можно представить в виде набора слов (рис. 6)

Длина слова современных компьютеров составляет от 16 до 64 бит. Если

Длина слова современных компьютеров составляет от 16 до 64 бит. Если

Восемь идущих подряд битов называются байтом. Для представления машинной команды требуется одно или несколько слов.

Для доступа к памяти с целью записи или чтения отдельных элементов информации, будь то слова или байты, необходимы имена или адреса, определяющие их расположение в памяти. В качестве адресов традиционно используются числа из диапазона от0 до 2k – 1 со значением k, достаточным для адресации всей памяти компьютера. Все 2k адресов составляют адресное пространство компьютера. Следовательно память состоит из 2k адресуемых элементов. Например, использование 240разрядных адресов позволяет адресовать 224 (16777216) элементов памяти. Обычно это количество адресуемых элементов обозначается как 16 М (16 мега), где 1 М = 220 (1048576). 32-разрядным адресам соответствует адресное пространство из 232 , или 4 Г (гига), элементов, где 1 Г = 230. Кроме того, часто используются обозначения К (кило), соответствующее 210 (1024), и Т (тера), соответствующее 240.

Байтовая адресация

Итак, есть три основные единицы информации: бит, байт и слово.

Байтовая адресация

Итак, есть три основные единицы информации: бит, байт и слово.

Прямой и обратный порядок байтов

Существует два способа адресации байтов в словах, а именно в прямом и обратном порядке (рисунок 8). Обратным порядком байтов называется система адресации, при которой байты адресуются слева направо, так, что самый старший байт слова (расположенный с левого края) имеет наименьший адрес. Прямым порядком байтов называется противоположная система адресации, при которой байты адресуются справа налево, так что наименьший адрес имеет самый младший байт слова (расположенный с правого края).Слова «старший» и «младший» определяют вес бита, то есть степень двойки, соответствующей данному биту, когда слово представляет число.

В машинах для коммерческих расчетов используются обе системы адресации. В обеих этих системах адреса байтов 0, 4, 8, и т.д. применяются в качестве адресов последовательных слов памяти в операциях чтения и записи слов

Наряду с порядком байтов в слове важно также определить порядок битов в байте типичный способ расположения битов показан на рисунке 7, а. Это наиболее естественный порядок битов для кодирования числовых данных, непосредственно соответствующий их разрядам Однако существуют компьютеры, для которых характерен обратный порядок битов.

Расположение слов в памяти

В случае 32-разрядных слов их естественные границы располагаются по адресам 0,

В случае 32-разрядных слов их естественные границы располагаются по адресам 0,

Слова, начинающиеся с произвольных адресов называются невыровненными.

Базовые типы команд

Сложение двух чисел относится к числу фундаментальных операций любого компьютера. Инструкция

Сложение двух чисел относится к числу фундаментальных операций любого компьютера. Инструкция

В программе на языке высокого уровня – это команда компьютеру сложить текущие значения двух переменных, А и В, и присвоить их сумму третьей переменной, С. При компиляции программы, содержащей эту инструкцию, переменным А, В и С назначаются конкретные адреса памяти. Содержимое памяти по этим адресам представляет значения трех переменных. Поэтому приведенная выше инструкция на языке высокого уровня требует выполнения компьютером следующего действия:

C [A] + [B]

Для выполнения этого действия содержимое памяти по адресам А и В должно быть переслано в процессор, где будет вычислена сумма. Полученная сумма должна быть отправлена обратно в память и записана по адресу С.

Для начала предположим, что действие может быть выполнено посредством одной машинной команды. Эта команда содержит адреса трех операндов: А, В и С. Структурно такую команду назвали трехадресной, а символически её можно представить как

Add A,B,C

Переменные: A, B и C называют операндами. Операнды A и B называются исходными операндами, а C – операндом назначения или результирующим операндом. В общем случае команда этого типа имеет такой формат:

Операция Источник 1, Источник 2, Место назначения

Если для указания адреса одного операнда в памяти необходимо k бит, в закодированной форме данной инструкции для адресов должно быть отведено 3k бит и ещё сколько-то бит для кода самой операции Add. В случае современного процессора с 32-разрядным адресным пространством трехадресная команда слишком громоздка для одного слова разумной длины. Поэтому для представления команд такого типа обычно используется формат длиной в несколько слов.

Для выполнения этой же задачи в качестве альтернативы можно использовать несколько более простых команд, с одним-двумя операндами. Предположим, что процессором поддерживаются двухадресные команды в виде:

Операция Источник, Место назначения

Команда Add такого типа Add A,B

Будет выполнять операцию B [A] + [B]. После вычисления суммы результат

Будет выполнять операцию B [A] + [B]. После вычисления суммы результат

Для решения задачи с изначальной формулировкой двухадресной команды недостаточно. Потребуется ещё одна двухадресная команда, которая копирует значение из одного места памяти в другое. Вот она:

Move B,C

Эта команда выполняет операцию C [B], оставляя содержимое памяти по адресу B неизменным. Слово Move, означает перемещение.

Операция может быть выполнена и в другой комбинации двух команд:

Move B,C

Add A,C

Во всех приведенных выше командах первыми задаются исходные операнды, после них – операнд назначения. Этот порядок характерен для выражений на языке ассемблера, используемых в машинных командах многих компьютеров. Но существует достаточно много компьютеров, в которых порядок операндов обратный.

Нами определены двух- и трехадресные команды. Но даже двухадресные команды далеко не всегда помещаются в одно слово памяти. Поэтому используют команды, имеющие всего один операнд. При этом всегда предполагается, что второй операнд находится в конкретном известном месте. Обычно в качестве такого «оговоренного» места служит регистр процессора, называемый сумматором (accumulator). Таким образом, одноадресная команда Add A означает следующее: добавить содержимое памяти по адресу A к содержимому сумматора и поместить результат в сумматор.

Если ввести ещё две команды, такие как:

Load A и Store A,

тогда операцию C [A] + [B] можно выполнить следующим образом:

Load A

Add B

Store C

Скопировать в сумматор содержимое памяти по адресу А, выполнить сложение A с B и поместить результат в сумматор, из которого командой Store сохранить в памяти по адресу C

Следует обратить внимание на то, что в зависимости от типа команды

Следует обратить внимание на то, что в зависимости от типа команды

В некоторых старых компьютерах сумматор был единственным регистром. В современных компьютерах регистров общего назначения обычно довольно много – от8 до 32, а иногда и больше. Доступ к данным в этих регистрах осуществляется намного быстрее, чем доступ к памяти, поскольку, как уже было сказано, регистры располагаются внутри процессора и чтобы адресоваться к ним, достаточно всего несколько битов. Так, для задания одного из 32 регистров нужно 5 битов. Это гораздо меньше того количества битов, которое необходимо для задания адреса в памяти. А поскольку регистры позволяют быстрее обрабатывать результаты и применять более короткие команды, они широко используются для временного хранения обрабатываемых данных.

Пусть Ri – это регистр общего назначения. Команды

Load A, Ri

Store Ri ,A

и

Add A, Ri

представляют собой пример команд Load, Store и Add, в которых Ri выполняет функцию сумматора. Но даже в том случае, когда в команде явно задается единственный адрес, она все равно может занимать больше одного слова памяти.

Если в процессоре имеется несколько регистров общего назначения, он может поддерживать ряд команд, все операнды которых располагаются в регистрах. Во многих современных процессорах вычисления фактически выполняются непосредственно только над данными, хранящимися в регистрах. К командам такого типа относятся

Add Ri , Rj

и

Add Ri , Rj, Rk

В обеих этих командах исходными операндами является содержимое регистров ,, Ri , Rj. В первой команде регистр Rj служит и приемником данных, тогда как во второй роль приемника играет третий регистр, Rk . Такие команды, содержащие лишь имена регистров, обычно умещаются в одно слово.

В программах часто требуется переслать данные из одного места в другое. Для этого используется команда

Move Источник, Приемник

Эта команда помещает в приемник копию содержимого источника. Команда Move может

Эта команда помещает в приемник копию содержимого источника. Команда Move может

Move A,Ri

Означает тоже, что и команда

Load A,Ri

а команда Move Ri , A

- то же, что и команда Store Ri , A

Таким образом, при использовании регистров команды можно реализовывать следующим образом:

Move A, Ri

Add B, Ri

Move Ri ,C

Время выполнения конкретной команды зависит от того, насколько быстро команды пересылаются из памяти в процессор и насколько быстро осуществляется доступ к операндам этих команд. Операции, в которых участвует память, выполняются гораздо медленнее, чем операции с участием регистров. Поэтому значительного ускорения работы можно добиться в тех случаях, когда несколько операций подряд выполняются над хранящимися в регистрах данными без обращения к памяти. При компиляции программ, написанных на языке высокого уровня, в машинный язык важно минимизировать частоту перемещений данных между памятью и регистрами процессора.

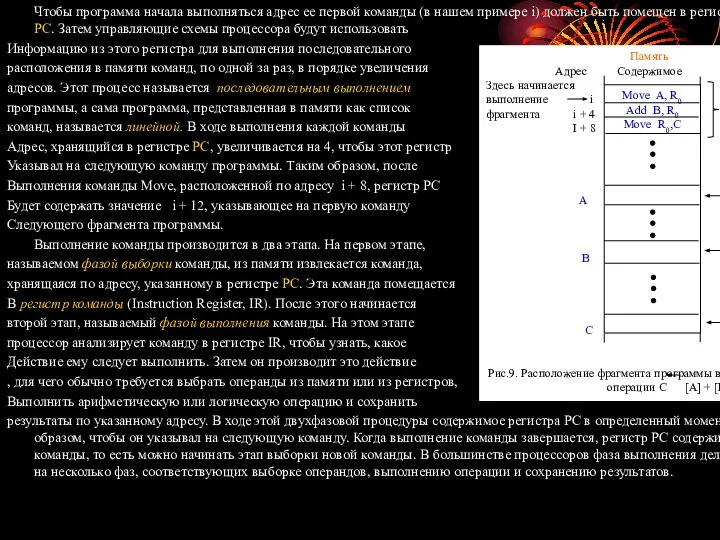

Выполнение команд и линейный код

На рисунке 9 показан фрагмент программы, выполняющий команду C [A] + [B] в той последовательности, в какой он представлен в памяти компьютера. При этом предполагается, что длина слова составляет 32 разряда, а память адресуется побайтово. Три команды программы расположены в следующих друг за другом словах, начиная с адреса i . Поскольку каждая команда занимает 4 байта, вторая и третья команды начинаются по адресам i + 4 и i + 8. Чтобы упростить задачу, предполагаем, что полный адрес целиком задается в команде, занимающей одно слово, хотя при таких размерах адресного пространства и той длине слова, которая поддерживается современными процессорами, подобное, как правило, невозможно.

Чтобы программа начала выполняться адрес ее первой команды (в нашем

Чтобы программа начала выполняться адрес ее первой команды (в нашем

Информацию из этого регистра для выполнения последовательного

расположения в памяти команд, по одной за раз, в порядке увеличения

адресов. Этот процесс называется последовательным выполнением

программы, а сама программа, представленная в памяти как список

команд, называется линейной. В ходе выполнения каждой команды

Адрес, хранящийся в регистре PC, увеличивается на 4, чтобы этот регистр

Указывал на следующую команду программы. Таким образом, после

Выполнения команды Move, расположенной по адресу i + 8, регистр PC

Будет содержать значение i + 12, указывающее на первую команду

Следующего фрагмента программы.

Выполнение команды производится в два этапа. На первом этапе,

называемом фазой выборки команды, из памяти извлекается команда,

хранящаяся по адресу, указанному в регистре PC. Эта команда помещается

В регистр команды (Instruction Register, IR). После этого начинается

второй этап, называемый фазой выполнения команды. На этом этапе

процессор анализирует команду в регистре IR, чтобы узнать, какое

Действие ему следует выполнить. Затем он производит это действие

, для чего обычно требуется выбрать операнды из памяти или из регистров,

Выполнить арифметическую или логическую операцию и сохранить

результаты по указанному адресу. В ходе этой двухфазовой процедуры содержимое регистра PC в определенный момент увеличивается таким образом, чтобы он указывал на следующую команду. Когда выполнение команды завершается, регистр PC содержит адрес следующей команды, то есть можно начинать этап выборки новой команды. В большинстве процессоров фаза выполнения делится, в свою очередь, на несколько фаз, соответствующих выборке операндов, выполнению операции и сохранению результатов.

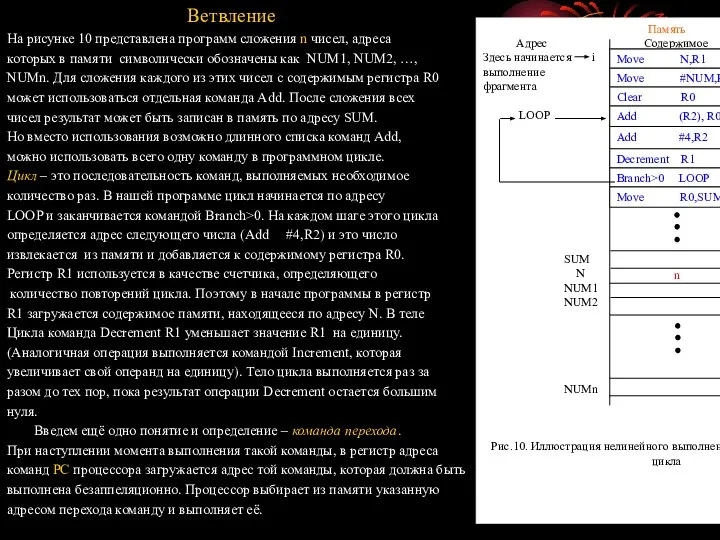

Ветвление

На рисунке 10 представлена программ сложения n чисел, адреса

которых в

Ветвление

На рисунке 10 представлена программ сложения n чисел, адреса

которых в

NUMn. Для сложения каждого из этих чисел с содержимым регистра R0

может использоваться отдельная команда Add. После сложения всех

чисел результат может быть записан в память по адресу SUM.

Но вместо использования возможно длинного списка команд Add,

можно использовать всего одну команду в программном цикле.

Цикл – это последовательность команд, выполняемых необходимое

количество раз. В нашей программе цикл начинается по адресу

LOOP и заканчивается командой Branch>0. На каждом шаге этого цикла

определяется адрес следующего числа (Add #4,R2) и это число

извлекается из памяти и добавляется к содержимому регистра R0.

Регистр R1 используется в качестве счетчика, определяющего

количество повторений цикла. Поэтому в начале программы в регистр

R1 загружается содержимое памяти, находящееся по адресу N. В теле

Цикла команда Decrement R1 уменьшает значение R1 на единицу.

(Аналогичная операция выполняется командой Increment, которая

увеличивает свой операнд на единицу). Тело цикла выполняется раз за

разом до тех пор, пока результат операции Decrement остается большим

нуля.

Введем ещё одно понятие и определение – команда перехода.

При наступлении момента выполнения такой команды, в регистр адреса

команд PC процессора загружается адрес той команды, которая должна быть

выполнена безаппеляционно. Процессор выбирает из памяти указанную

адресом перехода команду и выполняет её.

Имеет место определение команды условного перехода, при котором переход в

Имеет место определение команды условного перехода, при котором переход в

В программе на рисунке 10, команда Branch>0 LOOP (переход, если больше нуля) является командой условного перехода, выполняющей перемещение по адресу LOOP в том случае, если в результате выполнения предыдущей команды (инструкции), значение в регистре R1 остается больше нуля. Это означает, что цикл повторяется до тех пор, пока в списке чисел остаются необработанные элементы, которые следует добавить к содержимому регистра R0. В конце n-го прохода по циклу команда Decrement возвращает значение 0, поэтому переход на начало цикла не осуществляется, а выполняется следующая по порядку команда – Move. Команда Move перемещает окончательный результат суммирования из регистра R0 в память по адресу SUM.

Проверка условия с последующим выбором одного из нескольких альтернативных путей реализации программы, называемая ветвлением, выполняется гораздо чаще, чем просто программные циклы. Такая возможность имеется в системах команд любых компьютеров, поскольку ветвления и циклы относятся к числу фундаментальных операций, без которых невозможно запрограммировать сколько-нибудь нетривиальную задачу.

Флаги кодов условий

Процессор отслеживает выполнения различных операций и сохраняет их для использования в последующих инструкциях условного перехода. Эту информацию он записывает в специальные биты, называемые флагами кодов условий. В зависимости от результата выполненной операции отдельные флаги устанавливаются в 1 или 0. к наиболее распространенным относят четыре флага:

N (negative) – устанавливается в 1, если результат отрицателен; в противном случае очищается (то есть устанавливается в 0);

Z (zero) – устанавливается в 1, если результат равен 0; в противном случае очищается;

V (overflow) – устанавливается в 1, если в результате арифметической операции произошло переполнение; в противном случае очищается;

C (carry) – устанавливается в1, если в ходе операции был выпонен перенос; в противном случае очищается.

Флаги N и Z указывают, является результат арифметической операции отрицательным или

Флаги N и Z указывают, является результат арифметической операции отрицательным или

Флаг C устанавливается в 1, если в ходе арифметической операции осуществляется перенос из позиции

Режимы адресации

Если говорить в общем, каждая программа обрабатывает данные, хранящиеся в памяти компьютера. Эти данные могут быть организованы разными способами. Для представления данных , используемых в вычислениях, программисты обычно применяют стандартные способы их организации, называемые структурами данных. Примерами структур данных могут служить списки, связные списки, массивы, очереди и т.д.

Программы, как правило, пишутся на языках высокого уровня, позволяющих программистам оперировать константами, глобальными и локальными переменными, указателями и массивами. В процессе трансляции такой программы с языка высокого уровня на язык ассемблера компилятор (транслятор) должен реализовать эти конструкции средствами, предоставляемыми набором команд того компьютера, на котором будет выполняться программа. При этом используются различные способы задания местоположения операндов команд, называемые режимами адресации. Далее рассмотрим наиболее важные режимы адресации, поддерживаемые современными процессорами, список которых приведен в нижеследующей таблице. В таблице EA – это исполнительный адрес (effective address). Значение – это число со знаком

Таблица1. Стандартные режимы адресации

Таблица1. Стандартные режимы адресации

Реализация переменных и констант

Переменные и константы – это простейшие виды данных,

Реализация переменных и констант

Переменные и константы – это простейшие виды данных,

Ранее в примерах, мы обращались к операндам по именам регистров или по их адресам в памяти. Приведем точное определение этих двух режимов адресации.

Регистровая адресация – это режим, в котором операнд является содержимым регистра процессора; в команде задается имя (адрес) регистра.

Абсолютная адресация – это режим, в котором операнд хранится в памяти; его адрес в памяти задается непосредственно в команде. (В некоторых языках ассемблера данный режим называется прямым). В следующей команде, например, используются оба названных режима адресации:

Move LOC,R2

Если для временного хранения данных задействуются регистры процессора, режим адресации этих данных называется регистровым. Абсолютный режим может использоваться для представления глобальных переменных программы. Например, встретив объявление

Integer A,B;

в программе на языке высокого уровня, компилятор выделит адреса памяти для переменных A и B. Теперь, если в программе будут встречаться ссылки на указанные переменные, компилятор сможет генерировать команды на языке ассемблера с абсолютными адресами этих переменных.

Что касается констант, то их адреса и данные могут быть представлены на языке ассемблера с использованием непосредственной адресации.

Непосредственная адресация – это режим, в котором операнд задается в команде явно. В языке ассемблера для обозначения непосредственной адресации используется символ « # » перед значением, применяемым в качестве непосредственного операнда.

Так команда Move #200,R0 помещает значение 200 в регистр процессора R0. Значения констант часто используются в программах на языках высокого уровня, как, например, A= B + 6 или

языком ассемблера Add #6,R1.

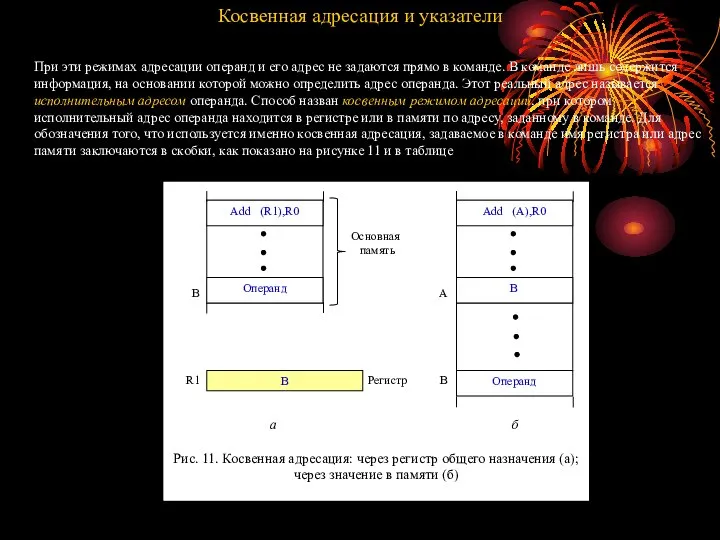

Косвенная адресация и указатели

При эти режимах адресации операнд и его адрес

Косвенная адресация и указатели

При эти режимах адресации операнд и его адрес

Для выполнения команды Add, схематически представленной на рисунке 11, а, процессор

Для выполнения команды Add, схематически представленной на рисунке 11, а, процессор

И регистр, и адрес в памяти, содержащий адрес операнда, называются указателями. Косвенная адресация и использование указателей являются очень важным и исключительно мощными концепциями программирования. Их суть можно понять, проведя аналогию с процессом поиска сокровищ. Предположим, вам, чтобы найти таковые, велено идти в дом, распложенный по определенному адресу. Но вместо того, чтобы обнаружить там сокровище, вы находите записку, в которой указан совершенно другой адрес. Заменив одну записку другой, можно изменить адрес сокровища, но исходное указание (команда) останется неизменным. Изменение содержимого записки эквивалентно изменению содержимого указателя в компьютерной программе. Например, если изменить на рисунке 11 содержимое регистра R1 или памяти по адресу A , команда Add получит для сложения другой операнд.

Вернемся к рисунку 10, иллюстрирующему сложение последовательности чисел. Для доступа к последовательным числам, хранящимся в этом списке, мы можем применить косвенную адресацию, в результате чего получим программу, представленную на рисунке10. Регистр R2 используется в качестве указателя на числа в списке, и доступ к операндам осуществляется косвенно, через этот регистр. В программе, в разделе инициализации, из памяти по адресу N в регистр R1 загружается значение счетчика n. Затем, в режиме прямой адресации, адрес первого элемента в списке, NUM1, помещается в регистр R2. После этого очищается регистр R0 (то есть ему присваивается значение 0). На первом шаге цикла команда Add (R2),R0 извлекает из памяти операнд, хранящийся по адресу NUM1, и прибавляет его к содержимому R0. Вторая команда Add увеличивает значение указателя R2 на 4, чтобы на втором шаге цикла, когда предыдущая команда будет выполняться во второй раз, в не содержался адрес NUM2.

Из разновидностей косвенной адресации наиболее широкое применение получила косвенная регистровая адресация (рис.10). Нерегистровая косвенная адресация имеет ограниченное применение из-за плохой совместимости с режимом конвейерной обработки.

Индексация и массивы

Режим адресации, который будет рассматриваться сейчас считается наиболее полезным

Индексация и массивы

Режим адресации, который будет рассматриваться сейчас считается наиболее полезным

Индексная адресация – это режим адресации, при котором исполнительный адрес операнда генерируется путем добавления заданного значения к содержимому регистра.

При индексной адресации можно использовать как специально предназначенный для этого регистр, так и один из регистров общего назначения. В любом случае речь идет об индексном регистре. Символическое обозначение индексного режима адресации таково:

X (Ri),

где X представляет заданное в команде значение константы, а Ri – имя регистра. Исполнительный адрес операнда этой команды вычисляется так:

EA = X + [Ri]

В процессе формирования исполнительного адреса операнда содержимое индексного регистра не меняется.

В программе на языке ассемблера константа X может быть задана либо явно в виде числа, либо в виде символического имени, представляющего числовое значение. Когда команда транслируется в машинный код , в неё включается непосредственное значение константы X, обычно представленное меньшим количеством битов, чем слово компьютера. Поскольку константа X является целым числом со знаком, то прежде чем она будет сложена с содержимым регистра, ее знак должен быть расширен до длины этого регистра. Существует два способа применения индексного режима адресации. На рисунке 12, а индексный регистр R1 содержит адрес в памяти компьютера, а значение X определяет смещение операнда относительно этого адреса. Альтернативный способ применения индексной адресации продемонстрирован на рисунке 12, б. Здесь константа X соответствует адресу в памяти, а содержимое индексного регистра определяет смещение операнда относительно данного адреса. В любом из этих двух случаев исполнительный адрес является суммой пары значений, одно из которых явно задается в команде, а другое хранится в регистре.

Чтобы понять, чем хороша индексная адресация, достаточно рассмотреть простой пример со списком оценок, полученных студентами по некоторому предмету. Предположим, что это список начинается по адресу LIST и организован так, как показано на рисунке 13.

Информация о каждом из студентов хранится в памяти в виде записи,

Информация о каждом из студентов хранится в памяти в виде записи,

Следует отметить, что список на рис.13 представляет собой двумерный массив, содержащий n строк и четыре столбца.

В каждой такой строке содержится запись об одном

Студенте, а в столбцах

В каждой такой строке содержится запись об одном

Студенте, а в столбцах

Если стоит задача подсчитать суммы баллов, полученных всеми

студентами по каждому из трех тестов и записать эти три суммы

в память по адресам SUM1, SUM2 и SUM3, можно в качестве

одного из вариантов использовать нижеприведенную программу

(рис.14)

В теле цикла программы для доступа к записям с каждой из

В теле цикла программы для доступа к записям с каждой из

На каждом шаге цикла оценки очередного студента прибавляются к текущим суммам, хранящимся в регистрах R2, R2, и R3 (перед началом цикла все три регистра обнуляются – устанавливаются в 0) Доступ к оценкам осуществляется посредством индексов 4(R0), 8(R0) и 12(R0). Затем значение в индексном регистре увеличивается на 16, чтобы он указывал на код следующего студента. Из содержимого регистра R4, куда перед началом цикла было помещено значение n, вычитается 1. На этом очередной шаг цикла заканчивается, а на следующем шаге все повторяется сначала, пока содержимое регистра R4 не станет равным нулю. С помощью команды условного перехода «Branch>0 LOOP» управление передается обратно на начало цикла, для обработки следующей записи. Последние три команды программы пересылают итоговые суммы из регистров R1, R2 и R3 в память по адресам SUM1, SUM2 и SUM3.

Обратите внимание, что содержимое индексного регистра R0 при обращении к записям с оценками студентов не меняется. Оно будет изменено только последней командой Add, предназначенной для перехода от одной записи к другой в конце очередного шага цикла.

Можно сказать, что индексная адресация предназначена для доступа к операнду, расположение которого определено относительно некоторой базовой точки в структуре данных, где хранится этот операнд.

Для наиболее эффективного доступа к операндам в памяти в разных ситуациях применяются различные вариации этой базовой формы. Так смещение X может содержаться во втором регистре. В этом случае для представления операнда используется такая запись:

(Ri,Rj)

Исполнительный адрес вычисляется как сумма содержимого регистров Ri и Rj. Второй регистр обычно называют базовым, а содержащееся в нем значение – базой.

Еще одна разновидность индексного режима адресации основывается на использовании двух регистров и константы. Она обозначается так: X(Ri,Rj). В этом случае исполнительный адрес является суммой константы X и содержимого регистров Ri и Rj. Этот еще более гибкий способ адресации используется для доступа к нескольким компонентам каждого элемента записи, когда начало элемента записи определяется частью (Ri,Rj), а X задает смещение компонента относительного начала элемента. Другими словами, этот режим используется для работы с трехмерными массивами.

Относительная адресация

Запись X(PC) означает, что исполнительный адрес смещен на X байтов

Относительная адресация

Запись X(PC) означает, что исполнительный адрес смещен на X байтов

Относительная адресация – это способ адресации, при котором исполнительный адрес определяется так же, как в индексном режиме, но вместо регистра общего назначения используется счетчик команд. Более типичным использованием этого режима является определение целевого адреса в команде перехода. Например, команда

Branch>0 LOOP приводит к передаче управления по целевому адресу, определяемому именем LOOP, в случае, если удовлетворяется условие перехода. Целевой адрес можно не задавать жестко, а вычислять как смещение относительно текущего значения счетчика команд. А поскольку целевой адрес может находиться как выше, так и ниже команды перехода, смещение задается в виде целого числа со знаком. Вспомним, что в ходе выполнения команды процессор увеличивает значение счетчика, чтобы он указывал на следующую команду программы. В связи с этим, например, в программе, представленной на рисунке 14, на момент, когда будет генерироваться целевой адрес перехода – метка LOOP, уже обновленное значение в регистре PC будет на 24 единицы больше. Чтобы перейти по адресу LOOP, нужно использовать смещение X = - 24.

В языке ассемблера в командах перехода для указания целевого адреса используются метки (LOOP, например). Когда компилятор при обработке ассемблерной программы встречает такую команду, он вычисляет значение смещения, в нашем случае -24, и генерирует соответствующую машинную команду, используя относительную адресацию, то есть -24(PC).

Дополнительные режимы адресации

Хотя описанных выше базовых режимов адресации вполне достаточно, некоторые компьютеры поддерживают еще и дополнительные режимы, облегчающие решение программных задач. Рассмотрим два таких режима, полезных для доступа к элементам данных, расположенных последовательно в памяти.

Автоинкрементная адресация – это режим адресации, при котором исполнительный адрес содержится в указанном в команде регистре. После обращения к операнду значение в этом регистре автоматически увеличивается таким образом, чтобы он указывал на следующий элемент списка.

В команде на языке ассемблера автоинкрементная адресация обозначается так: имя регистра

В команде на языке ассемблера автоинкрементная адресация обозначается так: имя регистра

(Ri)+

Если режим адресации задается в такой форме, то есть неявно, значит, значение в регистре увеличивается на 1. Однако в случае памяти с побайтовой адресацией такой режим полезен лишь для доступа к последовательным байтам списка. Если же требуется получить доступ к последовательным словам, а длина слова составляет 32 разряда, приращение должно быть равным 4. Компьютеры, поддерживающие автоинкрементную адресацию, автоматически увеличивают содержимое регистра на значение, соответствующее размеру операнда. Таким образом, для операнда размером в 1 байт приращение равняется 1, для 16-разрядного операнда -2, для 32-разрядного операнда -4. Поскольку размер операнда команды обычно определяется как часть кода операции, в самой команде для указания автоинкрементного режима достаточно обозначения (Ri)+ .

В дополнение к автоинкрементному режиму адресации компьютером может поддерживаться аналогичный ему режим, предназначенный для доступа к элементам списка в обратном порядке.

Автоинкрементная адресация – это режим адресации, при котором содержимое указанного в команде регистра сначала автоматически уменьшается, а затем используется в качестве исполнительного адреса операнда.

При автодекрементном режиме имя регистра

заключается в скобки, перед которыми ставится знак

«-», указывающий, что сначала из хранящегося в регистре

значения должна быть вычтена некоторая константа:

-(Ri). В таком режиме доступ к операндам осуществляется

в порядке уменьшения значений адресов.

ЗАПИСЬ ЧИСЕЛ НА АССЕМБЛЕРЕ

При работе с числовыми значениями обычно используют

привычную десятичную запись. В компьютере числовые значения

Move N,R1

Move #NUM1,R2

Clear R0

LOOP Add (R2)+,R0

Decrement R1

Branch>0 LOOP

Move R0,SUM

Рис.15. Пример автоинкрементной адресации

В некоторых случаях удобнее прямо задавать числовые значения различными способами, используя

В некоторых случаях удобнее прямо задавать числовые значения различными способами, используя

ADD #93,R1

или же в виде двоичного числа, на что указывает специальный префикс, такой как символ %:

ADD #%01011101,R1

Двоичные числа можно записывать более компактно, используя шестнадцатеричную систему, в которой каждые четыре бита числа представлены одной шестнадцатеричной цифрой. Шестнадцатеричную запись можно считать расширенной версией двоично-десятичной записи. Первые десять кодов, 0000, 0001, …,1001, обозначаются цифрами 0, 1,…, 9, как в двоично-десятичной системе кодирования. Оставшиеся шесть 4-разрядных кодов, 1010, 1011,…,1111, обозначаются буквами A, B, …,F. В шестнадцатеричном представлении десятичное значение 93 записывается как 5D. В языке ассемблера шестнадцатеричное представление часто задается с помощью префикса в виде знака доллара ($). Таким образом, команда прибавляющая к содержимому регистра 93, при использовании шестнадцатеричной системы кодирования чисел:

ADD #$5D,R1.

Базовые операции ввода-вывода

Рассмотрим процессы, с помощью которых данные пересылаются между памятью компьютера и внешним миром. Операции ввода-вывода являются одной из важнейших составляющих работы компьютера, и от того, как они выполняются, в значительной мере зависит его производительность. Рассмотрим несколько базовых концепций ввода-вывода.

Предположим, нам необходимо считать вводимые с клавиатуры символы и вывести их на экран дисплея. Простейший способ выполнения подобных задач заключается в использовании метода, который называется программно управляемым вводом-выводом. Скорость передачи данных от клавиатуры к компьютеру зависит от того, насколько быстро пользователь может их вводить (это порядка нескольких символов в секунду). Скорость передачи данных от компьютера к дисплею гораздо выше. Она определяется пропускной способностью соединения между компьютером и дисплеем. Которая обычно составляет несколько тысяч символов в секунду.

Однако и это невероятно мало, если

сравнивать со скоростью работы процессора,

выполняющего

Однако и это невероятно мало, если

сравнивать со скоростью работы процессора,

выполняющего

Разница в быстродействии процессора и

устройств ввода-вывода вызывает потребность

в механизмах синхронизации процесса

передачи данных между ними.

Решение этой проблемы заключается в

следующем. Процессор отсылает дисплею

первый символ и ждет от него сигнала о том,

что символ получен. Затем он отсылает

второй символ, снова ждет сигнала и т.д.

Точно также отсылаются процессору данные,

вводимые с клавиатуры. Процессор ждет

Сигнала, означающего, что пользователь

нажал одну из клавиш и что ее код помещен

в некоторый буферный регистр, связанный с

клавиатурой. Получив сигнал, процессор

считывает код клавиши. Как показано на

рисунке 15, клавиатура и дисплей являются совершенно независимыми устройствами. Нажатие

клавиши на клавиатуре само по себе не вызывает вывода на экран соответствующего символа. Один блок команд в

программе ввода-вывода пересылает символы в процессор, а другой выводит таковые на экран. Рассмотрим, как

пересылается код символа от клавиатуры процессору. В ответ на нажатие клавиши соответствующий ей код символа

сохраняется в 8-разрядном буферном регистре, связанном с клавиатурой. Он назван условно DATAIN

(см.рис.15). Для уведомления процессора о наличии нового кода символа в регистре DATAIN специальный флаг

состояния SIN устанавливается в 1. Программа отслеживает состояние этого флага, и когда он оказывается

установленным в 1, процессор считывает содержимое регистра. После пересылки символа в процессор значение

флага SIN автоматически сбрасывается в 0. Когда с клавиатуры вводится второй символ, флаг SIN снова

устанавливается в 1 и процесс повторяется.

Вывод символа на экран осуществляется аналогичным образом. Но в этом случае для его пересылки от

процессора к монитору используются буферный регистр DATAOUT и флаг SOUT.

Если значение SOUT равно 1, значит, дисплей готов к приему символа.

Если значение SOUT равно 1, значит, дисплей готов к приему символа.

отслеживает содержимое флага SOUT, и когда его значение оказывается равным1,процессор пересылает код

символа в регистр DATAOUT. После этого флаг SOUT сразу же снимается. Когда дисплей готов к приему

следующего символа, флаг SOUT опять устанавливается в 1 и процесс повторяется. Буферные регистры DATAIN

и DATAOUT совместно с флагами состояния SIN и SOUT являются частью схемы, называемой интерфейсом

устройства. Такая схема имеется у каждого устройства ввода-вывода. С процессором она соединяется через шину

(рис.15). Предполагается, что в исходном состоянии флаг SIN сброшен, а флаг SOUT установлен. Буферы данных,

такие как DATAIN и DATAOUT (см.рис.15) могут адресоваться так, как если бы они располагались в основной

памяти компьютера. Точно также можно было бы поступить и с флагами SIN и SOUT, присвоив им разные адреса.

Но чаще эти флаги включают в состав регистров состояния устройства (такой регистр имеется у каждого

устройства ввода-вывода). Предположим, что в интерфейсных схемах клавиатуры и дисплея бит b3 соответствует