Слайд 10

Особенности Core 2 Duo

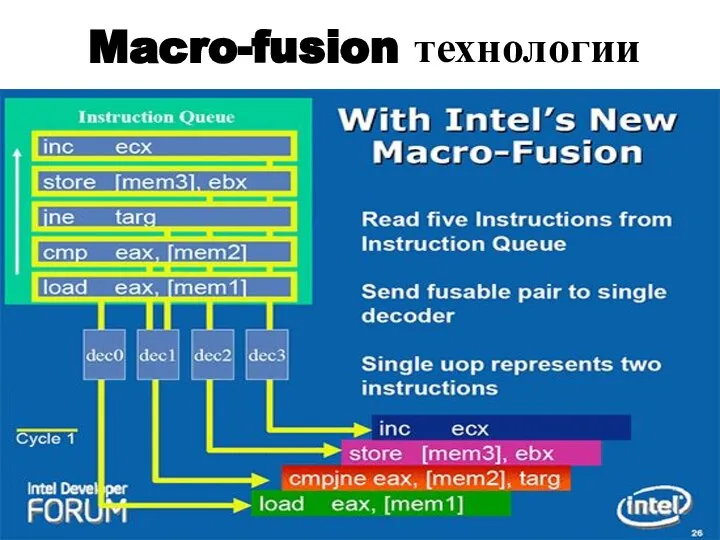

Intel Wide Dynamic Execution — технология выполнения большего количества

команд за каждый такт, повышающая эффективность выполнения приложений и сокращающая энергопотребление. Каждое ядро — технология выполнения большего количества команд за каждый такт, повышающая эффективность выполнения приложений и сокращающая энергопотребление. Каждое ядро может выполнять до 4-х инструкций одновременно с помощью 14-стадийного конвейера.

Intel Intelligent Power Capability — технология, с помощью которой для исполнения задач активируется работа отдельных узлов чипа по мере необходимости, что значительно снижает энергопотребление системы в целом.

Intel Advanced Smart Cache — технология использования общей для всех ядер кэш-памяти 2-го уровня, что снижает энергопотребление и повышает производительность, при этом, по мере необходимости, одно из ядер может использовать весь

объём кэш-памяти при динамическом отключении другого ядра.

Intel Smart Memory Access — технология оптимизации работы подсистемы памяти, сокращающая время отклика и повышающая пропускную способность подсистемы памяти.

Intel Advanced Digital Media Boost — технология обработки 128-разрядных команд SSE — технология обработки 128-разрядных команд SSE, SSE2 — технология обработки 128-разрядных команд SSE, SSE2 и SSE3, широко используемых в мультимедийных и графических приложениях, за один такт.

Компьютерная игра The Epic

Компьютерная игра The Epic Коммуникационные технологии

Коммуникационные технологии Презентация "РАСТРОВАЯ И ВЕКТОРНАЯ ГРАФИКА" - скачать презентации по Информатике_

Презентация "РАСТРОВАЯ И ВЕКТОРНАЯ ГРАФИКА" - скачать презентации по Информатике_ Компьютерные вирусы и антивирусные программы

Компьютерные вирусы и антивирусные программы Базы и банки данных. Раздел 6. SQL. Data Control Language. Управление транзакциями

Базы и банки данных. Раздел 6. SQL. Data Control Language. Управление транзакциями Информатика. 3 класс.

Информатика. 3 класс. Библиотеки и экологическое просвещение населения

Библиотеки и экологическое просвещение населения Контент для приложения Bmw Start. Новые информационные блоки

Контент для приложения Bmw Start. Новые информационные блоки Макет заголовка с рисунком

Макет заголовка с рисунком Flash-презентации Выполнила: Дадаева Э.Г Преподаватель: Иманова О.А Красноярск, 2013

Flash-презентации Выполнила: Дадаева Э.Г Преподаватель: Иманова О.А Красноярск, 2013 Тест-опрос Multator

Тест-опрос Multator Системы счисления

Системы счисления Инструкция по использованию Среды дистанционного обучения Мираполис

Инструкция по использованию Среды дистанционного обучения Мираполис Что такое информация? Виды информации

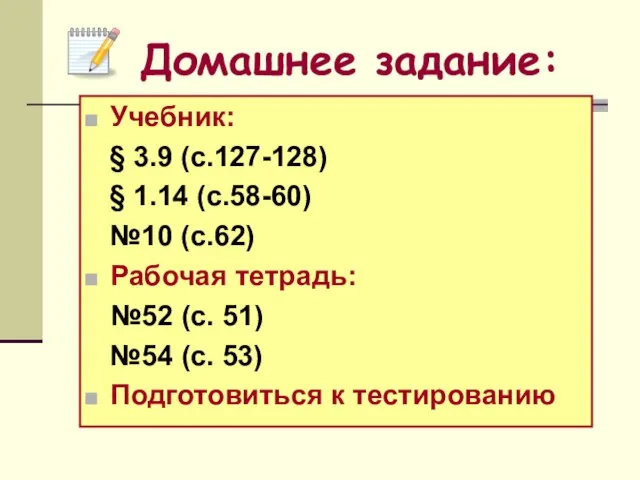

Что такое информация? Виды информации  Домашнее задание: Учебник: § 3.9 (с.127-128) § 1.14 (с.58-60) №10 (с.62) Рабочая тетрадь: №52 (c. 51) №54 (c. 53) Подготовиться к тестированию

Домашнее задание: Учебник: § 3.9 (с.127-128) § 1.14 (с.58-60) №10 (с.62) Рабочая тетрадь: №52 (c. 51) №54 (c. 53) Подготовиться к тестированию Система управления версиями Git, Github аnd Github Flow

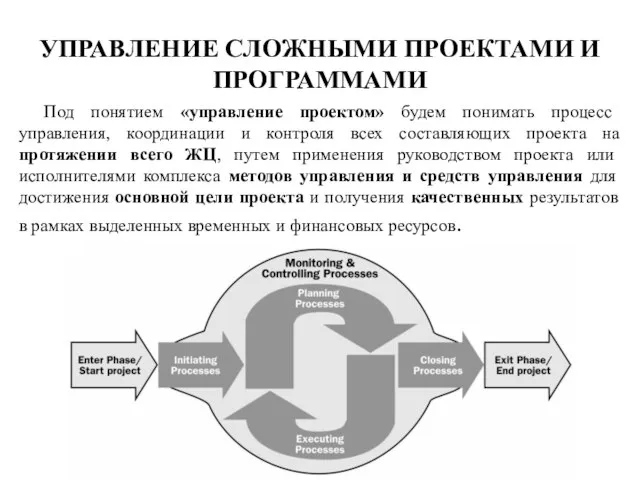

Система управления версиями Git, Github аnd Github Flow Управление сложными проектами и программами. (Лекция 3)

Управление сложными проектами и программами. (Лекция 3) 2008г.

2008г. Одномерные массивы целых чисел. Алгоритмизация и программирование

Одномерные массивы целых чисел. Алгоритмизация и программирование Цифрова обробка сингалів та зображень. Методи компресії аудіоінформації

Цифрова обробка сингалів та зображень. Методи компресії аудіоінформації Повторение пройденного материала

Повторение пройденного материала  Операционные системы реального времени QNX и интегрированный комплект разработчика QNX Momentics

Операционные системы реального времени QNX и интегрированный комплект разработчика QNX Momentics Stepik Academy. Автоматизация тестирования на Python

Stepik Academy. Автоматизация тестирования на Python Файловая система

Файловая система  Spring Core. Spring AOP

Spring Core. Spring AOP Организация вычислений в таблице

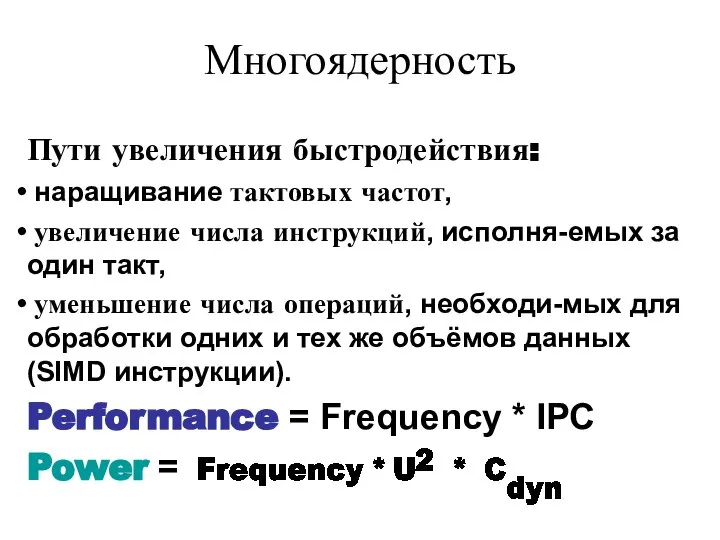

Организация вычислений в таблице Производительность. Варианты увеличения производительности

Производительность. Варианты увеличения производительности Настройка D-link’а

Настройка D-link’а