Содержание

- 2. Цифровая схемотехника и архитектура компьютера Эти слайды предназначены для преподавателей, которые читают лекции на основе учебника

- 3. Благодарности Перевод данных слайдов на русский язык был выполнен командой сотрудников университетов и компаний из России,

- 4. Глава 5 :: Темы Введение Арифметические схемы Представление чисел Последовательностные функциональные блоки Матрицы памяти Матрицы логических

- 5. Цифровые функциональные блоки: Логические элементы, мультиплексоры, декодеры, регистры, схемы арифметики, счетчики, матрицы памяти и матрицы логических

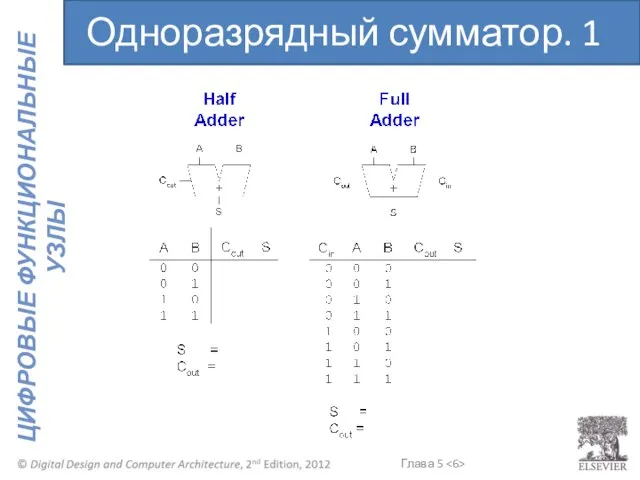

- 6. Одноразрядный сумматор. 1

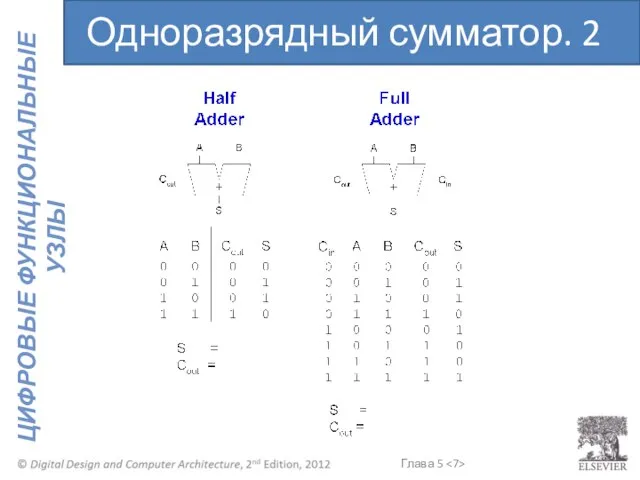

- 7. Одноразрядный сумматор. 2

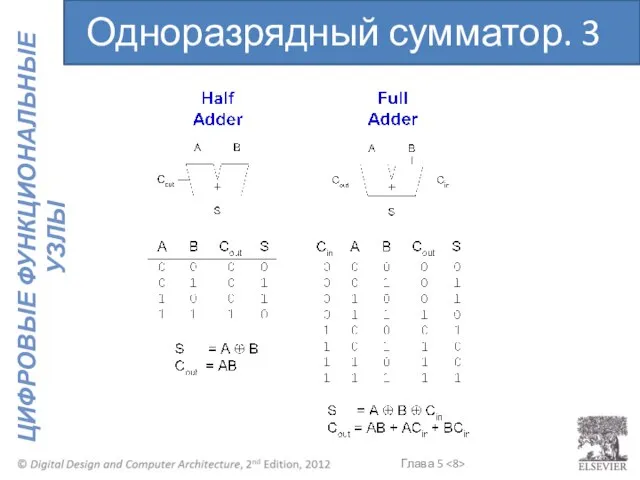

- 8. Одноразрядный сумматор. 3

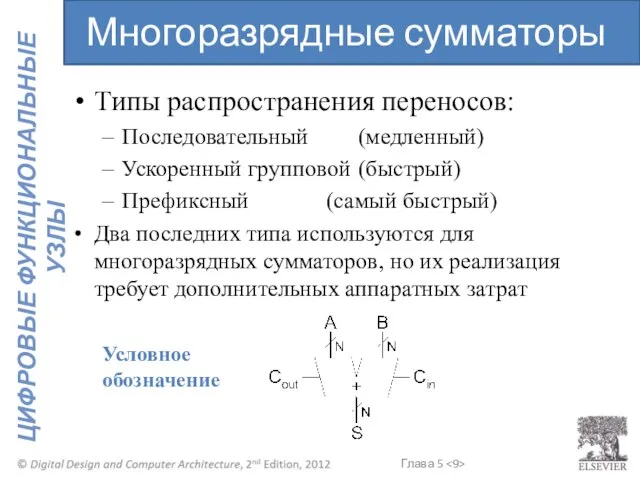

- 9. Типы распространения переносов: Последовательный (медленный) Ускоренный групповой (быстрый) Префиксный (самый быстрый) Два последних типа используются для

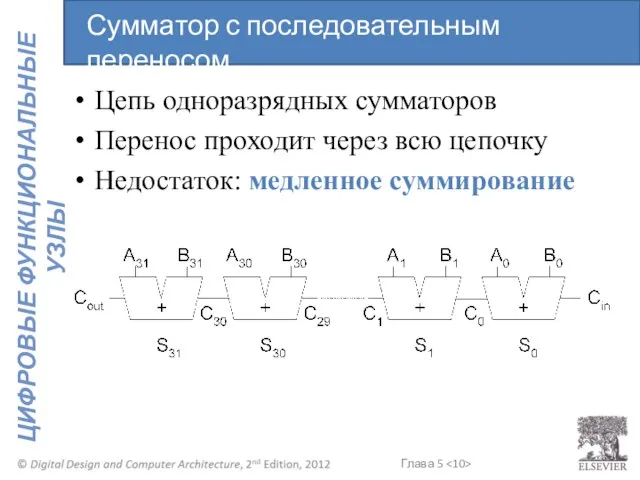

- 10. Цепь одноразрядных сумматоров Перенос проходит через всю цепочку Недостаток: медленное суммирование Сумматор с последовательным переносом

- 11. Задержка сумматора складывается из задержек разрядов в каждом звене: tripple = NtFA где tFA – задержка

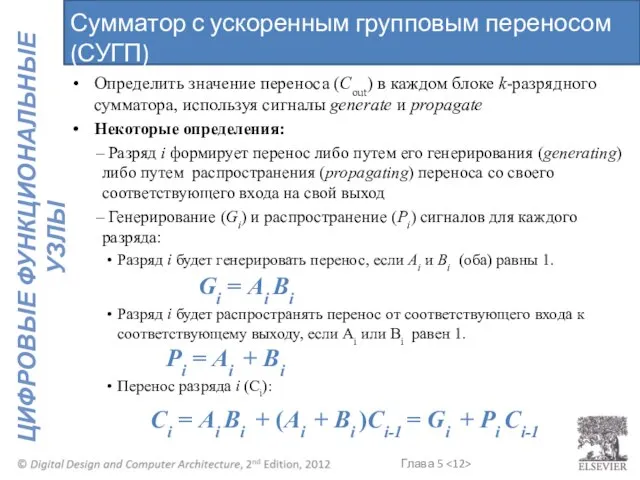

- 12. Определить значение переноса (Cout) в каждом блоке k-разрядного сумматора, используя сигналы generate и propagate Некоторые определения:

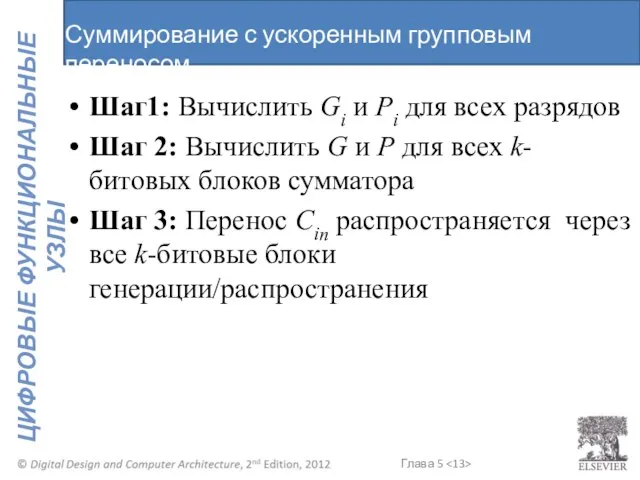

- 13. Шаг1: Вычислить Gi и Pi для всех разрядов Шаг 2: Вычислить G и P для всех

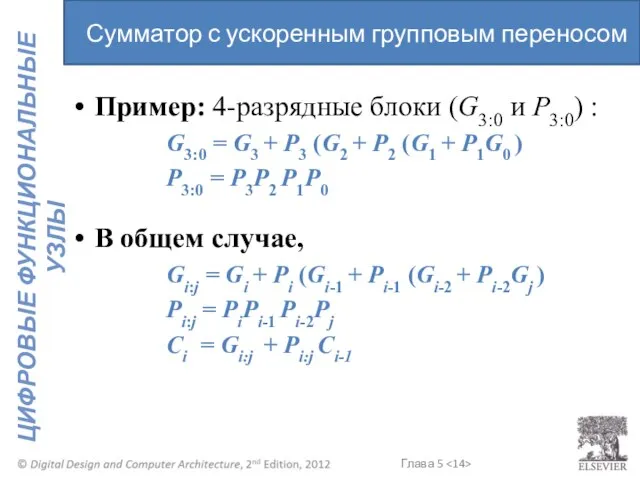

- 14. Пример: 4-разрядные блоки (G3:0 и P3:0) : G3:0 = G3 + P3 (G2 + P2 (G1

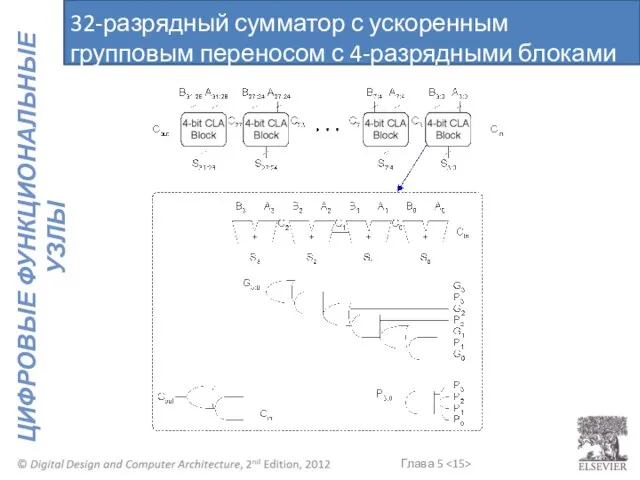

- 15. 32-разрядный сумматор с ускоренным групповым переносом с 4-разрядными блоками

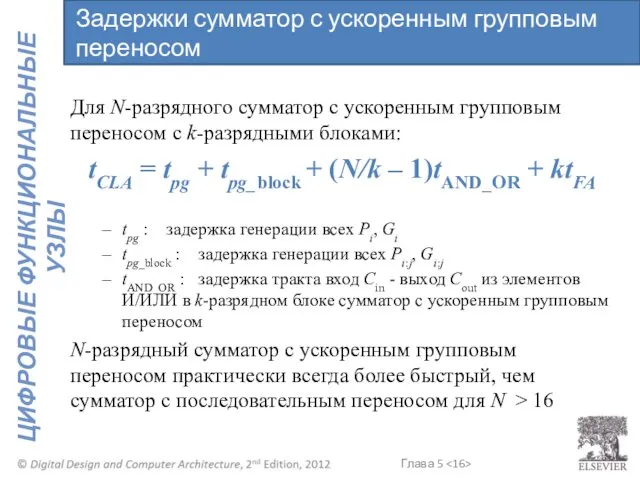

- 16. Для N-разрядного сумматор с ускоренным групповым переносом с k-разрядными блоками: tCLA = tpg + tpg_block +

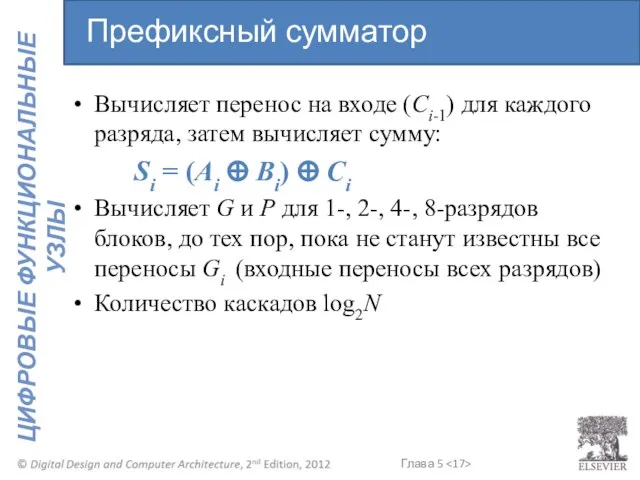

- 17. Вычисляет перенос на входе (Ci-1) для каждого разряда, затем вычисляет сумму: Si = (Ai ⊕ Bi)

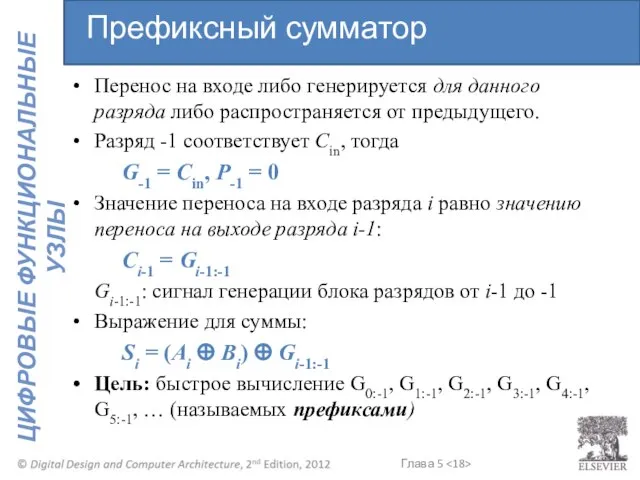

- 18. Перенос на входе либо генерируется для данного разряда либо распространяется от предыдущего. Разряд -1 соответствует Cin,

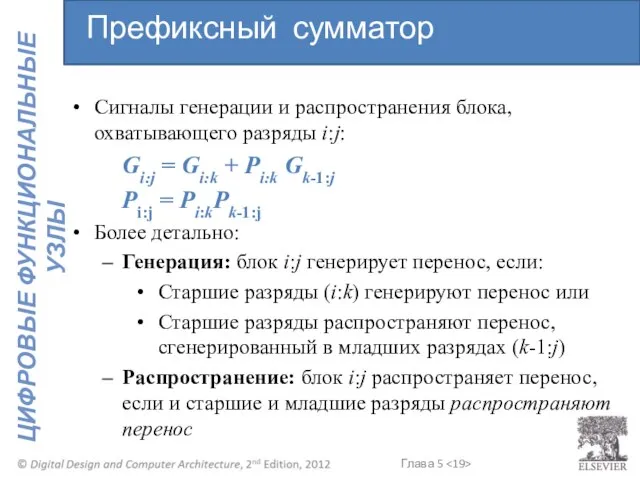

- 19. Сигналы генерации и распространения блока, охватывающего разряды i:j: Gi:j = Gi:k + Pi:k Gk-1:j Pi:j =

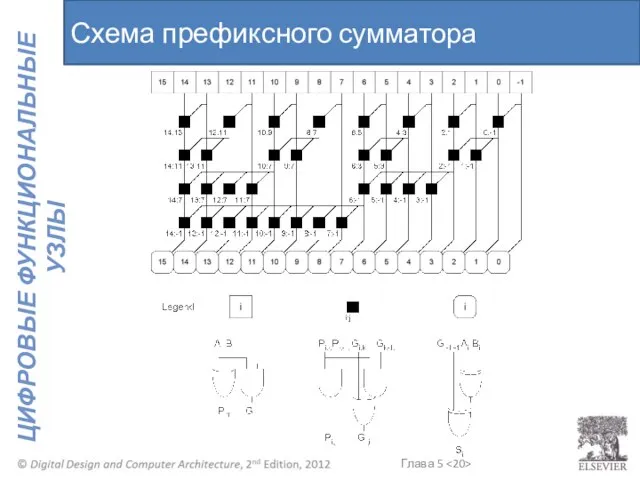

- 20. Схема префиксного сумматора

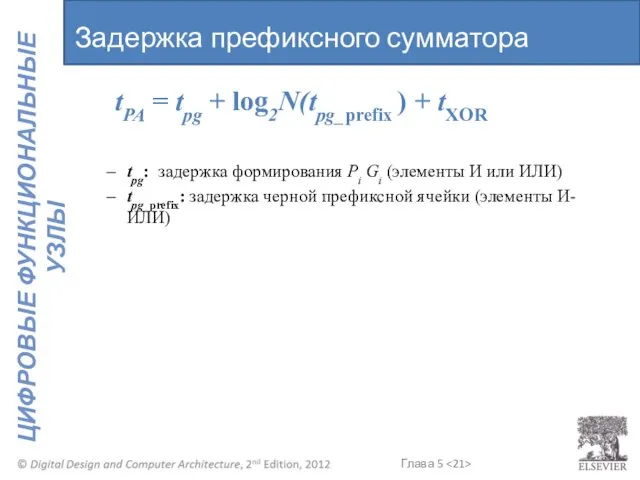

- 21. tPA = tpg + log2N(tpg_prefix ) + tXOR tpg: задержка формирования Pi Gi (элементы И или

- 22. Сравнить задержки: 32-разрядный сумматор с последовательным переносом, сумматор с ускоренным групповым переносом, и префиксного сумматора сумматор

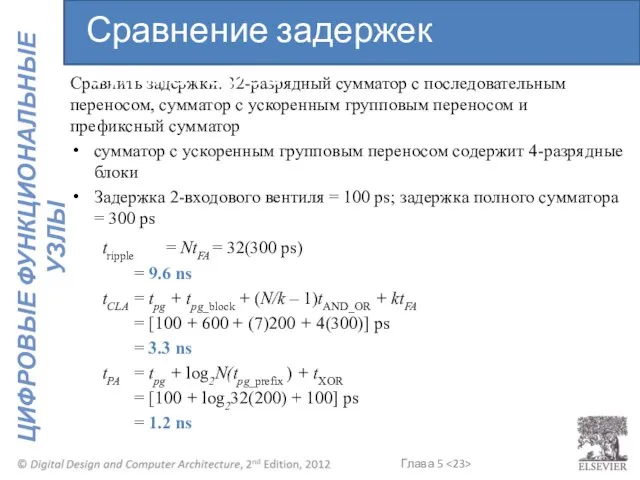

- 23. Сравнить задержки: 32-разрядный сумматор с последовательным переносом, сумматор с ускоренным групповым переносом и префиксный сумматор сумматор

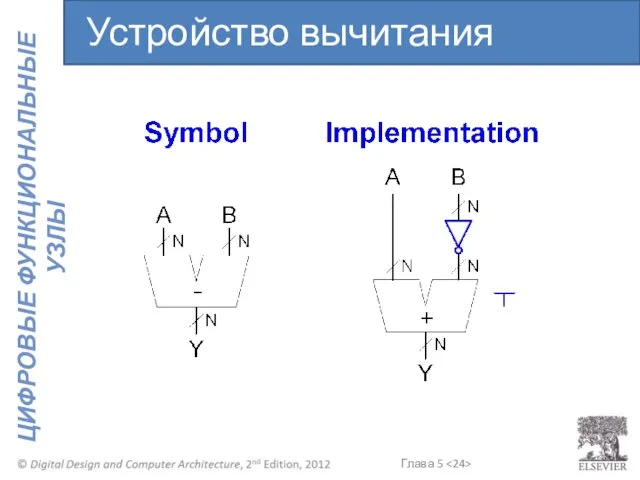

- 24. Устройство вычитания

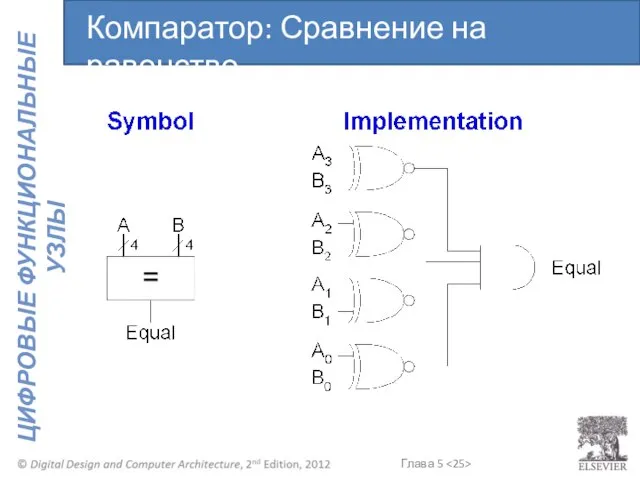

- 25. Компаратор: Сравнение на равенство

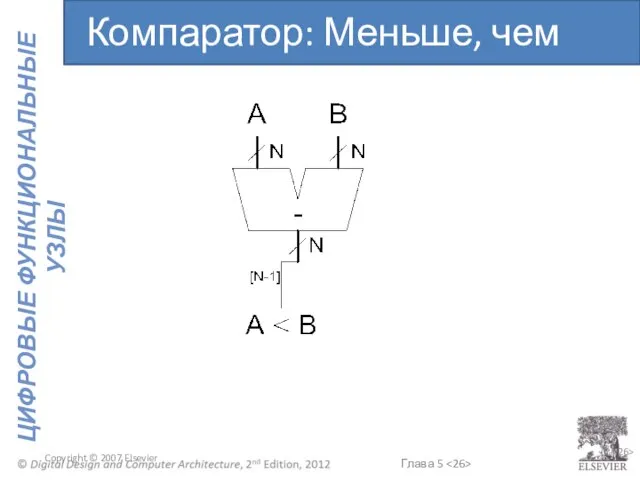

- 26. Copyright © 2007 Elsevier 5- Компаратор: Меньше, чем

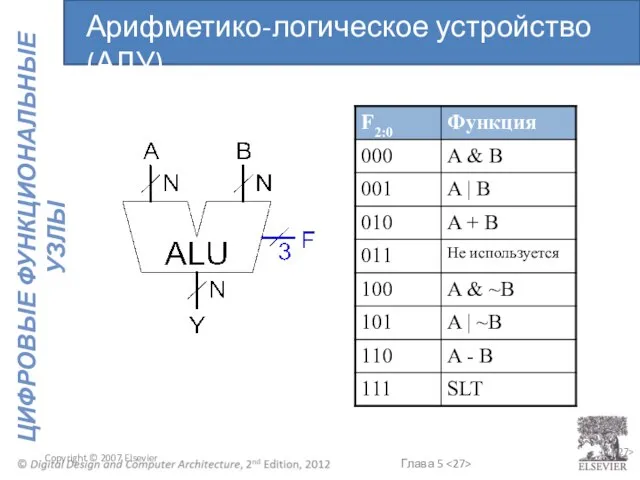

- 27. Copyright © 2007 Elsevier 5- Арифметико-логическое устройство (АЛУ)

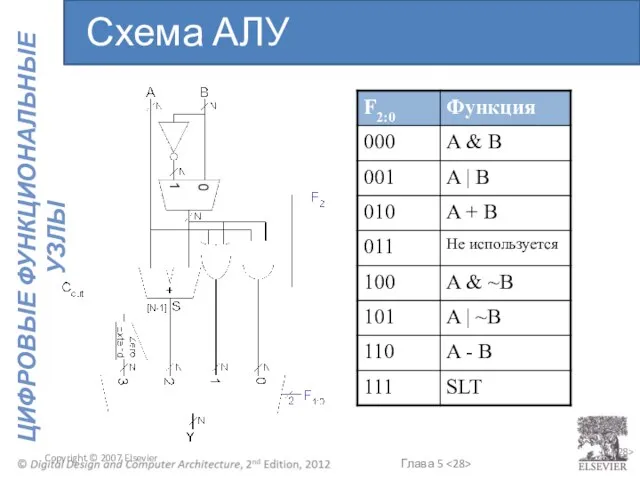

- 28. Copyright © 2007 Elsevier 5- Схема АЛУ

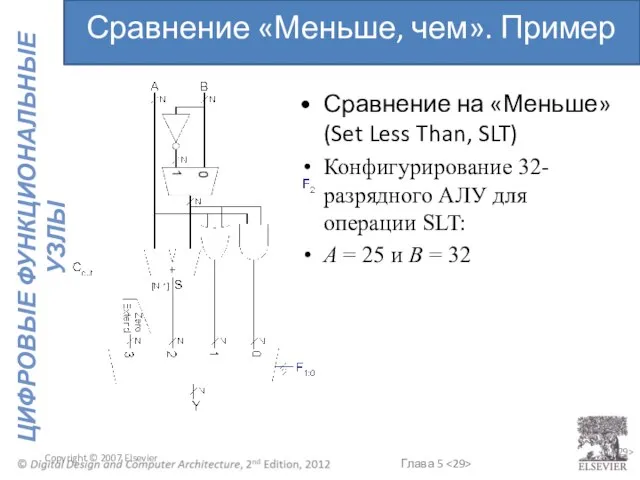

- 29. Copyright © 2007 Elsevier 5- Сравнение на «Меньше» (Set Less Than, SLT) Конфигурирование 32-разрядного АЛУ для

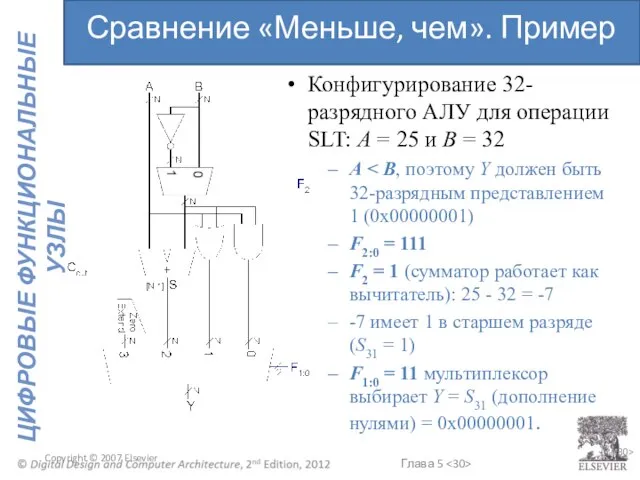

- 30. Copyright © 2007 Elsevier 5- Конфигурирование 32-разрядного АЛУ для операции SLT: A = 25 и B

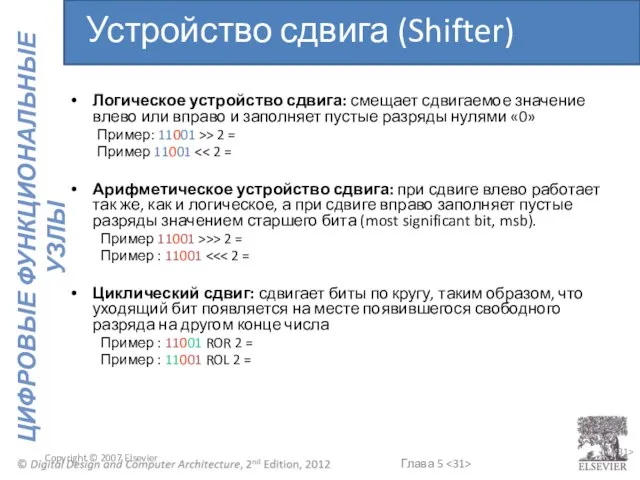

- 31. Copyright © 2007 Elsevier 5- Логическое устройство сдвига: смещает сдвигаемое значение влево или вправо и заполняет

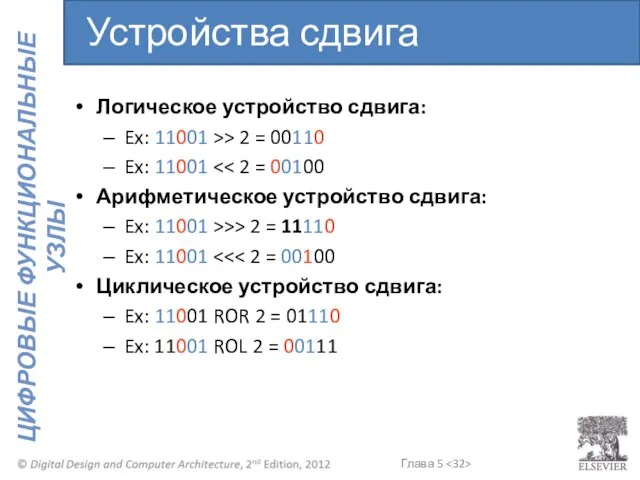

- 32. Логическое устройство сдвига: Ex: 11001 >> 2 = 00110 Ex: 11001 Арифметическое устройство сдвига: Ex: 11001

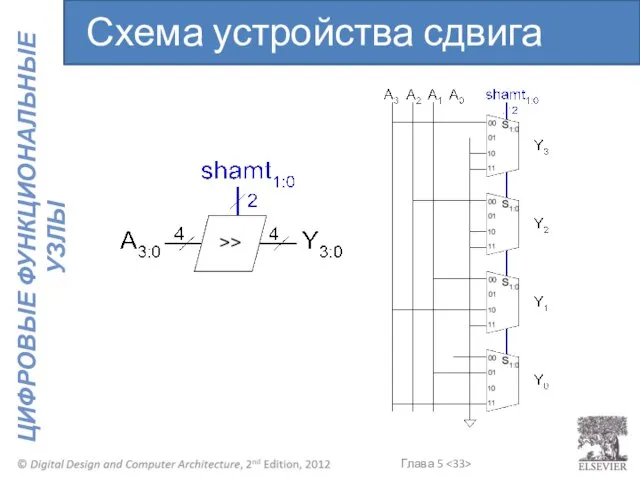

- 33. Схема устройства сдвига

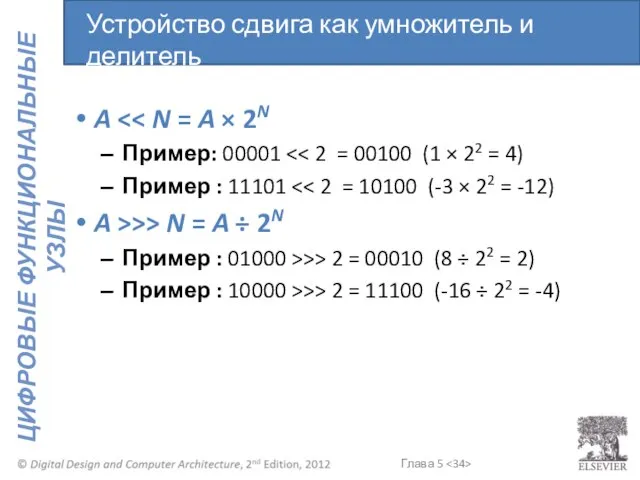

- 34. A Пример: 00001 Пример : 11101 A >>> N = A ÷ 2N Пример : 01000

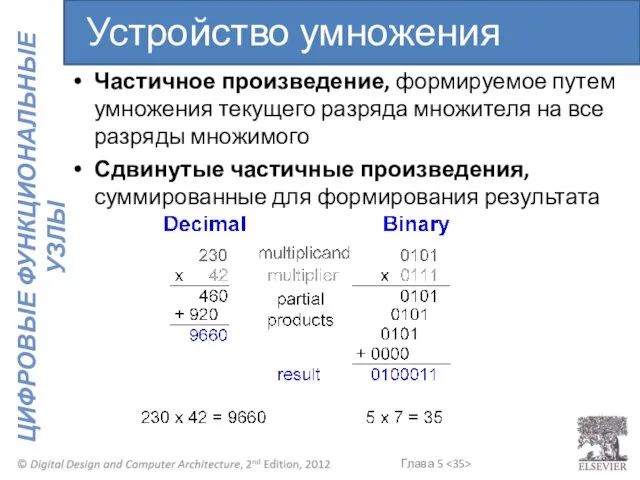

- 35. Частичное произведение, формируемое путем умножения текущего разряда множителя на все разряды множимого Сдвинутые частичные произведения, суммированные

- 36. Умножитель 4 x 4

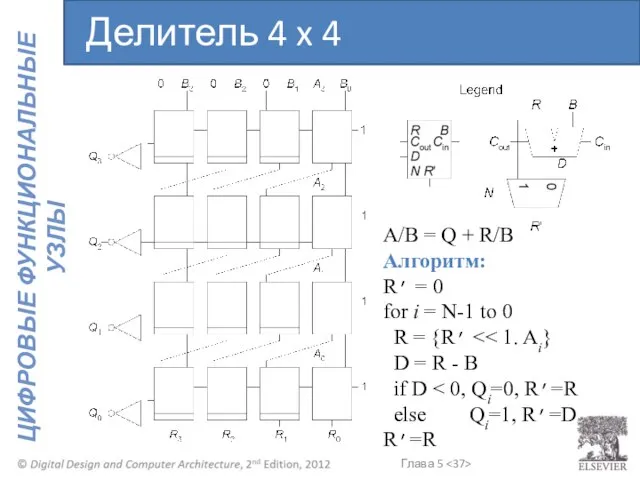

- 37. Делитель 4 x 4 A/B = Q + R/B Алгоритм: R’ = 0 for i =

- 38. Числа можно представить с помощью двоичного представления Положительные числа Беззнаковое двоичное Отрицательные числа Дополнительный код Прямой

- 39. Две основных способа представления: Fixed-point: двоичное число с фиксированной точкой Floating-point: двоичное число с плавающей точкой

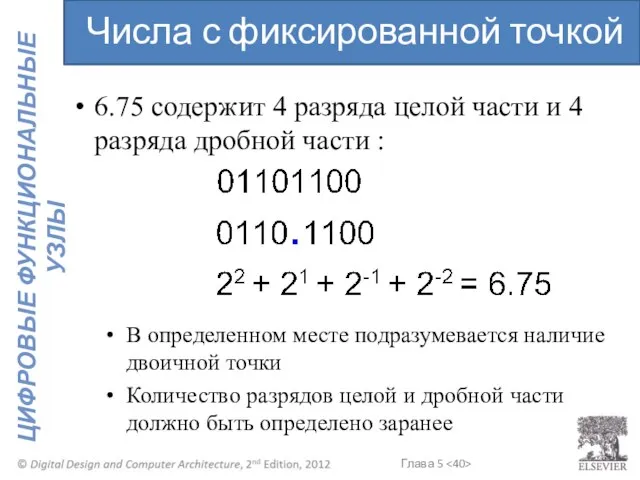

- 40. 6.75 содержит 4 разряда целой части и 4 разряда дробной части : В определенном месте подразумевается

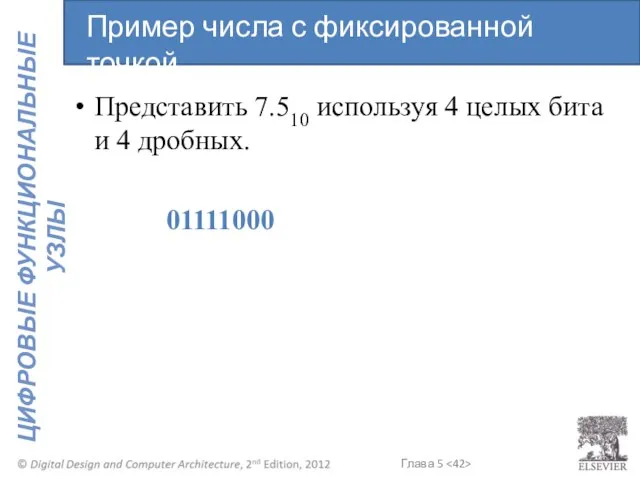

- 41. Представить 7.510 используя 4 целых бита и 4 дробных. Пример числа с фиксированной точкой

- 42. Представить 7.510 используя 4 целых бита и 4 дробных. 01111000 Пример числа с фиксированной точкой

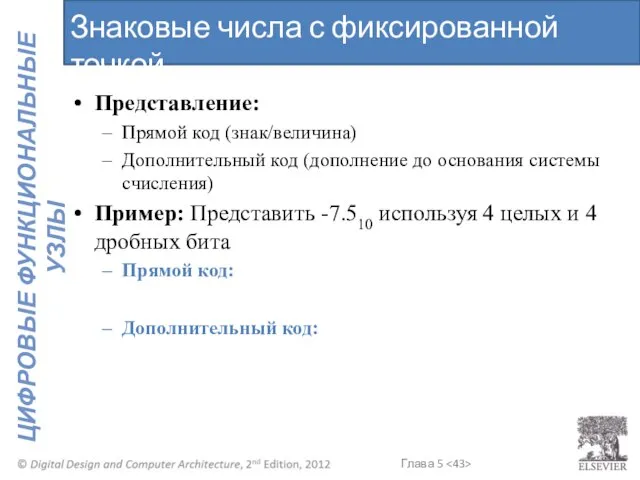

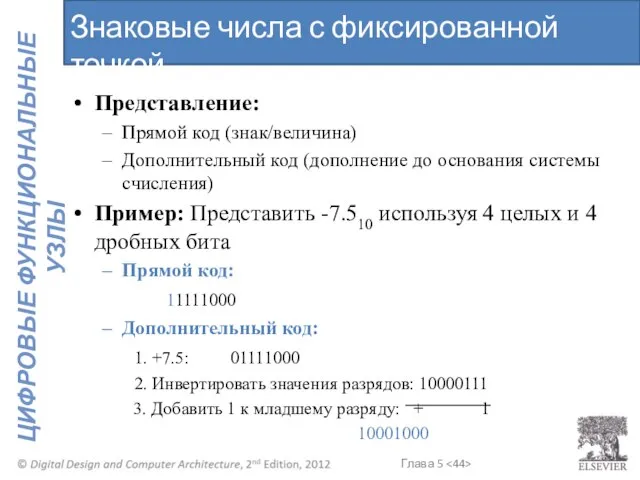

- 43. Представление: Прямой код (знак/величина) Дополнительный код (дополнение до основания системы счисления) Пример: Представить -7.510 используя 4

- 44. Представление: Прямой код (знак/величина) Дополнительный код (дополнение до основания системы счисления) Пример: Представить -7.510 используя 4

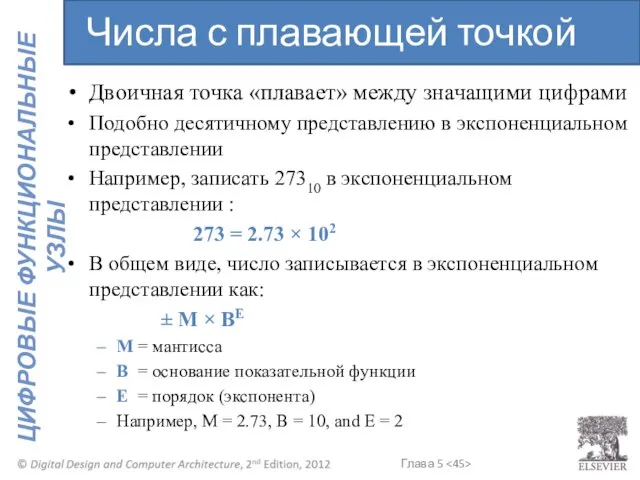

- 45. Двоичная точка «плавает» между значащими цифрами Подобно десятичному представлению в экспоненциальном представлении Например, записать 27310 в

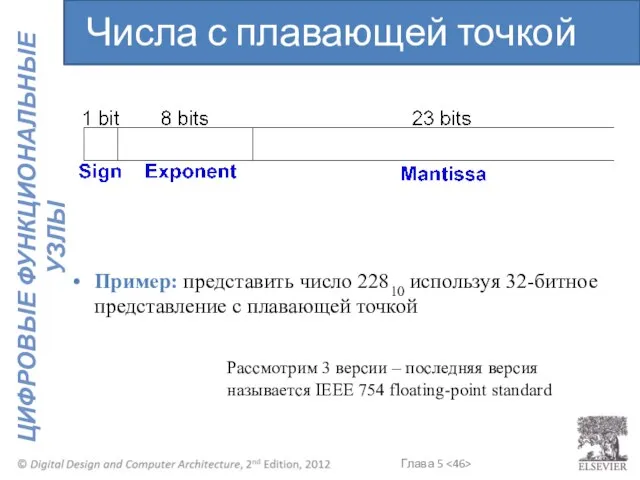

- 46. Пример: представить число 22810 используя 32-битное представление с плавающей точкой Рассмотрим 3 версии – последняя версия

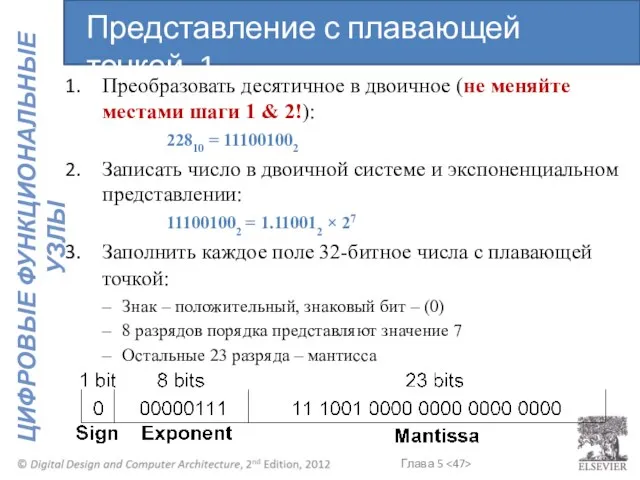

- 47. Преобразовать десятичное в двоичное (не меняйте местами шаги 1 & 2!): 22810 = 111001002 Записать число

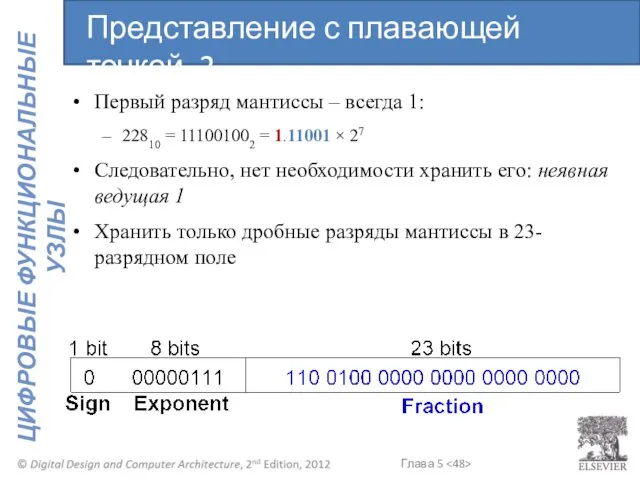

- 48. Первый разряд мантиссы – всегда 1: 22810 = 111001002 = 1.11001 × 27 Следовательно, нет необходимости

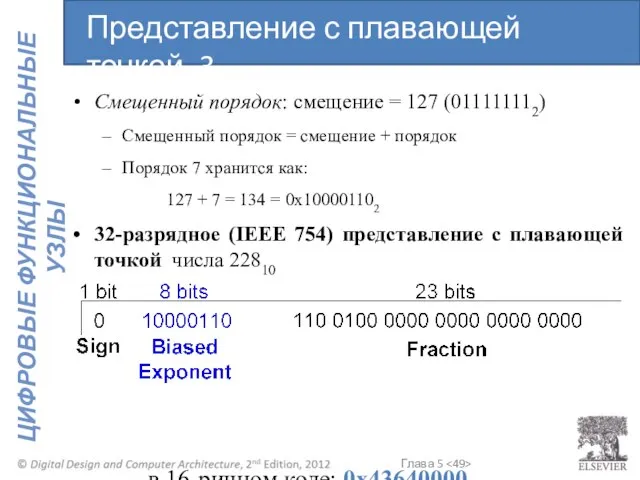

- 49. Смещенный порядок: смещение = 127 (011111112) Смещенный порядок = смещение + порядок Порядок 7 хранится как:

- 50. Записать число -58.2510 с плавающей точкой (IEEE 754) Представление с плавающей точкой. Пример

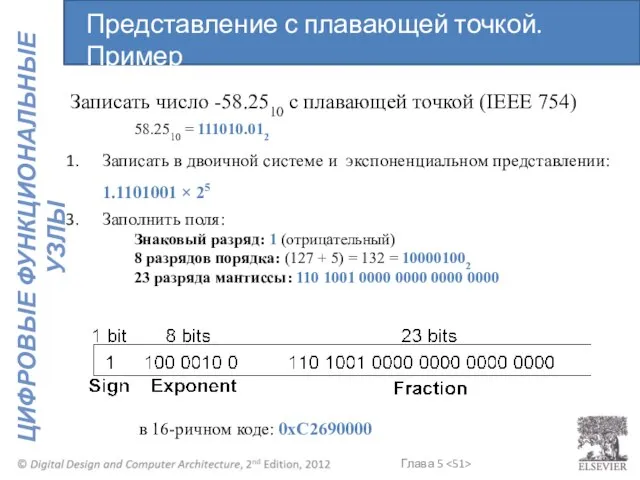

- 51. Записать число -58.2510 с плавающей точкой (IEEE 754) 58.2510 = 111010.012 Записать в двоичной системе и

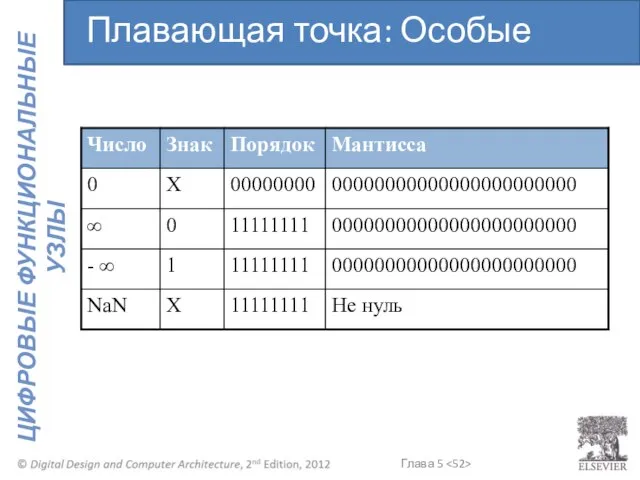

- 52. Плавающая точка: Особые случаи

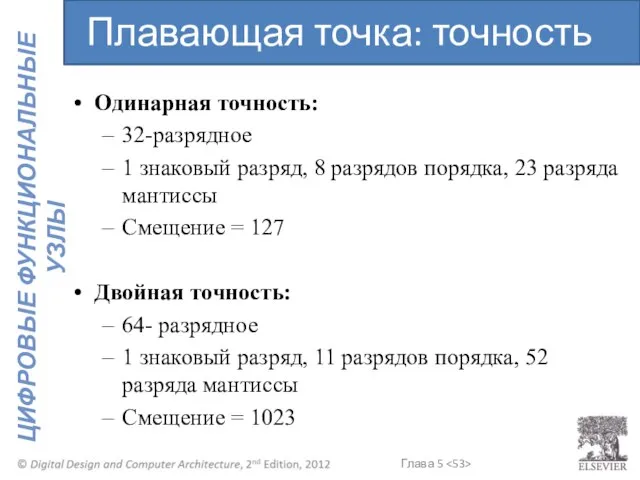

- 53. Одинарная точность: 32-разрядное 1 знаковый разряд, 8 разрядов порядка, 23 разряда мантиссы Смещение = 127 Двойная

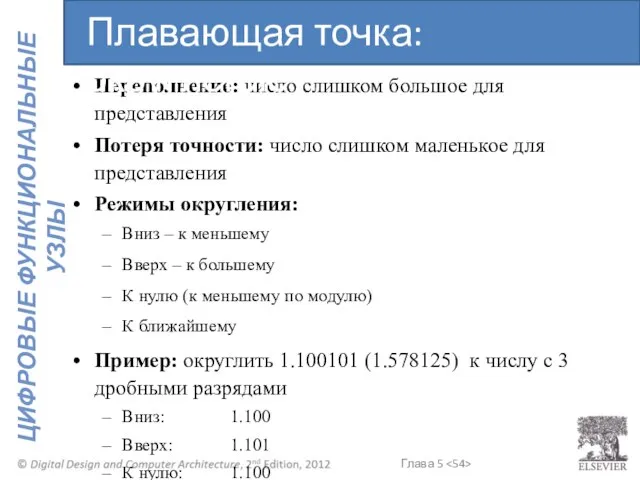

- 54. Переполнение: число слишком большое для представления Потеря точности: число слишком маленькое для представления Режимы округления: Вниз

- 55. Выделить порядок числа и мантиссу Присоединить ведущую 1 к мантиссе Сравнить порядки Выполнить сдвиг меньшей мантиссы

- 56. Сложить числа с плавающей точкой: 0x3FC00000 0x40500000 Суммирование с плавающей точкой. Пример

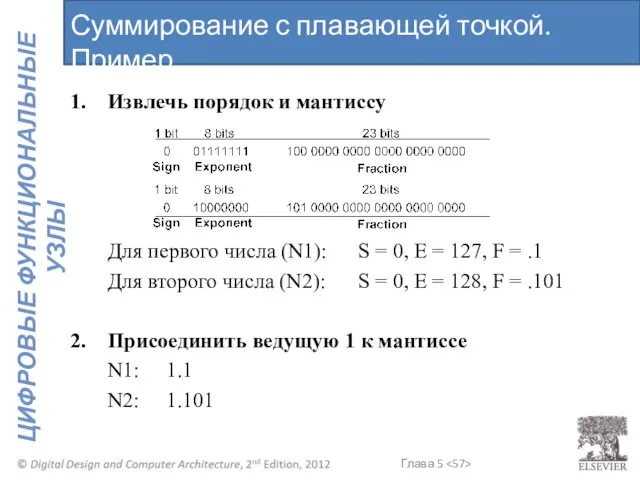

- 57. 1. Извлечь порядок и мантиссу Для первого числа (N1): S = 0, E = 127, F

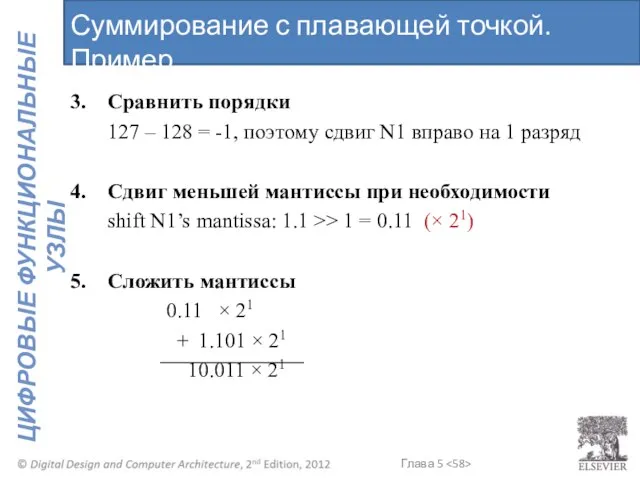

- 58. 3. Сравнить порядки 127 – 128 = -1, поэтому сдвиг N1 вправо на 1 разряд 4.

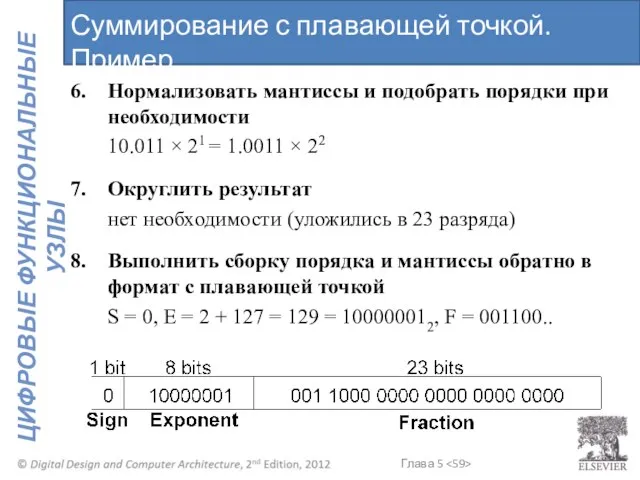

- 59. 6. Нормализовать мантиссы и подобрать порядки при необходимости 10.011 × 21 = 1.0011 × 22 7.

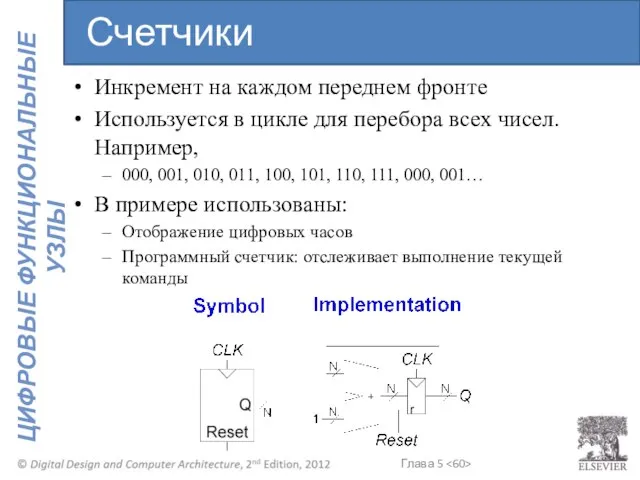

- 60. Инкремент на каждом переднем фронте Используется в цикле для перебора всех чисел. Например, 000, 001, 010,

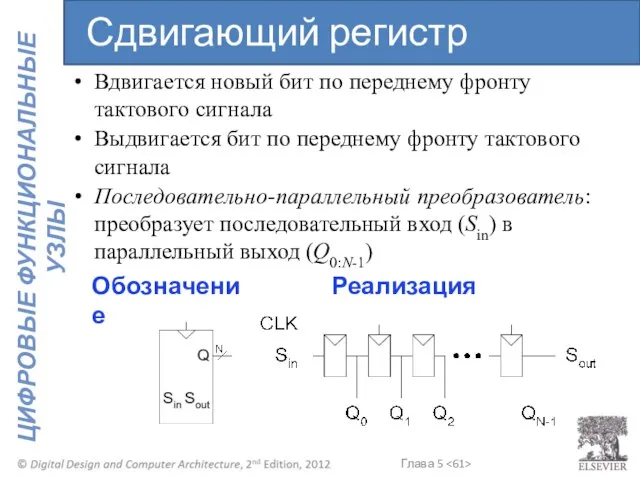

- 61. Реализация Вдвигается новый бит по переднему фронту тактового сигнала Выдвигается бит по переднему фронту тактового сигнала

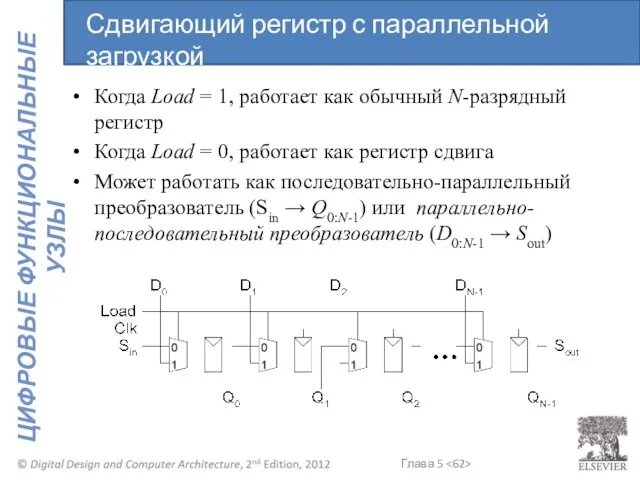

- 62. Когда Load = 1, работает как обычный N-разрядный регистр Когда Load = 0, работает как регистр

- 63. Эффективно хранят большие объемы данных 3 основных типа: Динамическое оперативное запоминающее устройство (ОЗУ) (DRAM) Статическое оперативное

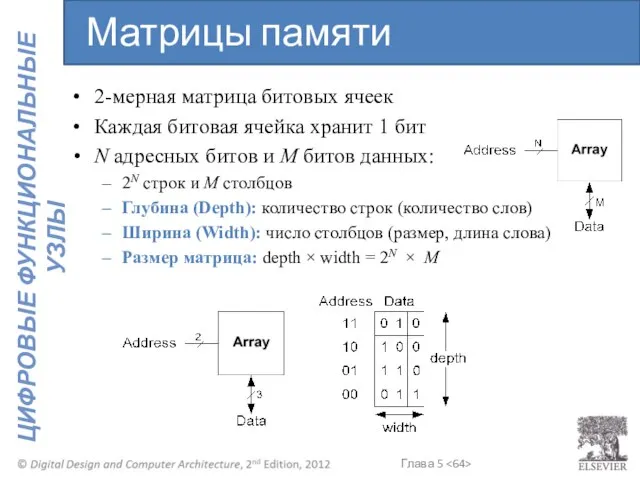

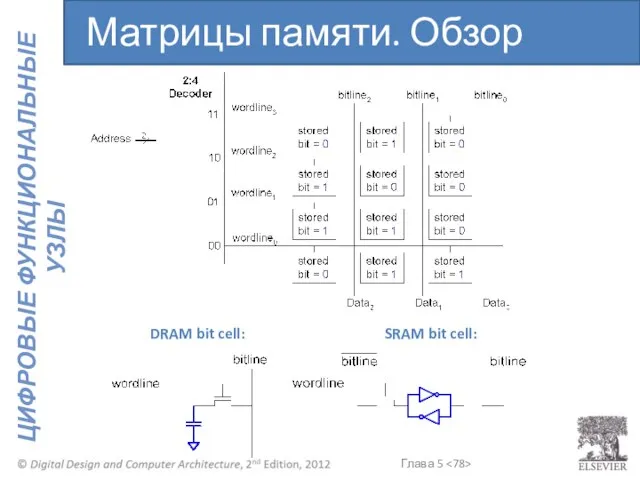

- 64. 2-мерная матрица битовых ячеек Каждая битовая ячейка хранит 1 бит N адресных битов и M битов

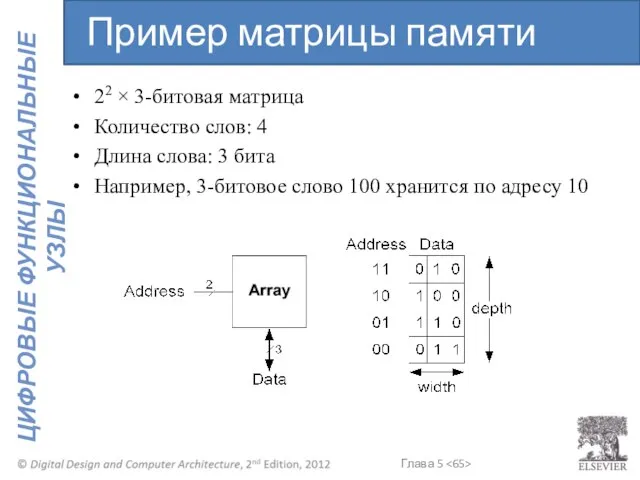

- 65. 22 × 3-битовая матрица Количество слов: 4 Длина слова: 3 бита Например, 3-битовое слово 100 хранится

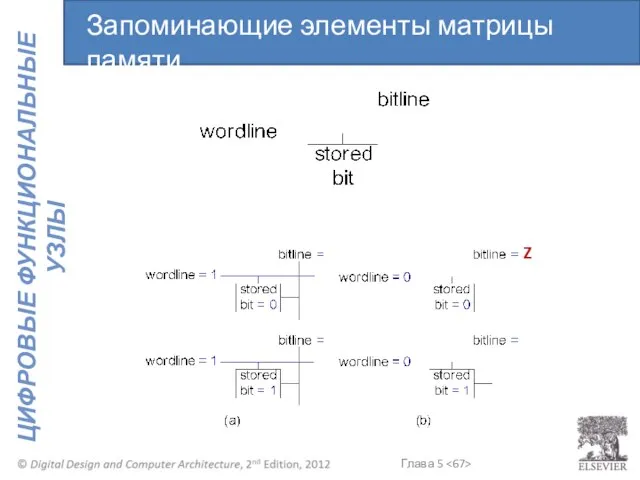

- 66. Матрицы памяти

- 67. Z Запоминающие элементы матрицы памяти

- 68. 0 1 Z Z Запоминающие элементы матрицы памяти

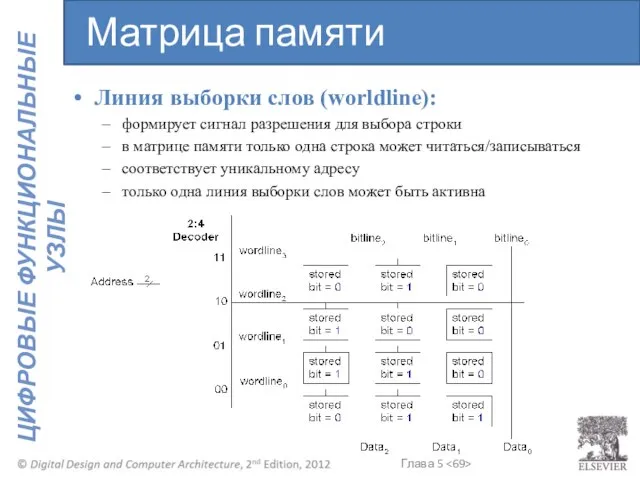

- 69. Линия выборки слов (worldline): формирует сигнал разрешения для выбора строки в матрице памяти только одна строка

- 70. с произвольным доступом, оперативная память (RAM, ОЗУ): энергозависимая (volatile) Память только для чтения (ROM, ПЗУ): энергонезависимая

- 71. Энергозависимая: содержимое памяти теряется при отключении электропитания Быстрые чтение и запись Основная память в компьютере –

- 72. Энергонезависимая: содержимое памяти сохраняется при отключении электропитания Чтение быстрое, но запись невозможна или медленная Флэш память

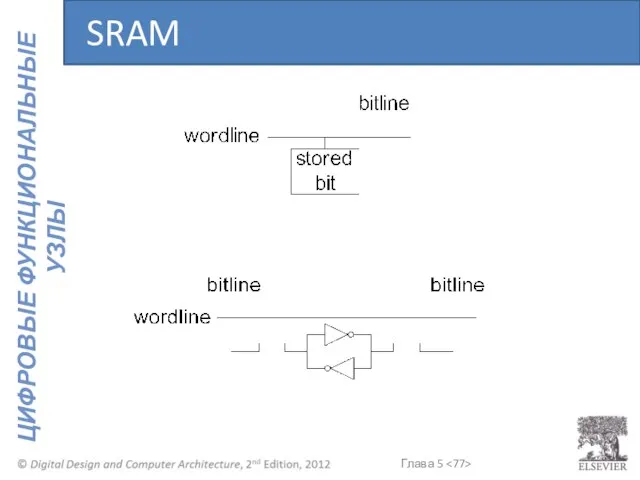

- 73. DRAM (динамическое ОЗУ - Dynamic random access memory) SRAM (Статическое ОЗУ - Static random access memory)

- 74. Изобрел DRAM в 1966, IBM Многие были настроены скептически к работоспособности его идеи С середины 1970-х

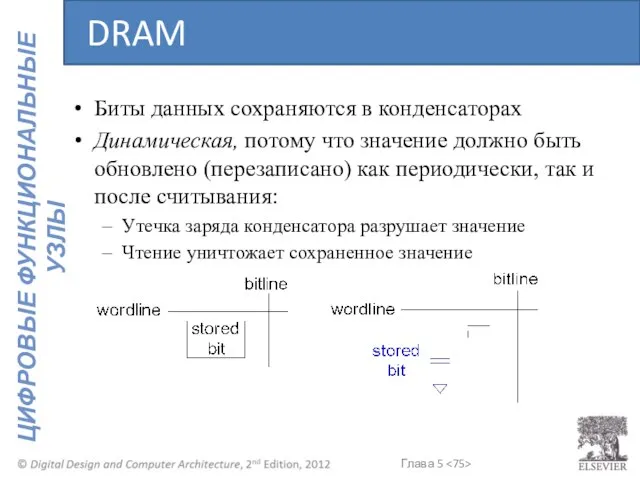

- 75. Биты данных сохраняются в конденсаторах Динамическая, потому что значение должно быть обновлено (перезаписано) как периодически, так

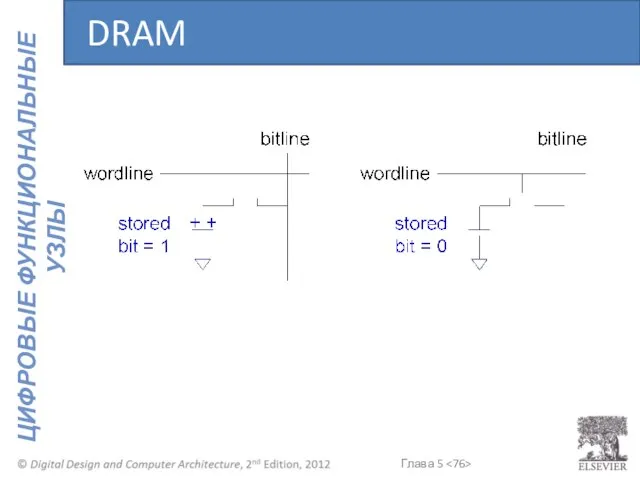

- 76. DRAM

- 77. SRAM

- 78. DRAM bit cell: SRAM bit cell: Матрицы памяти. Обзор

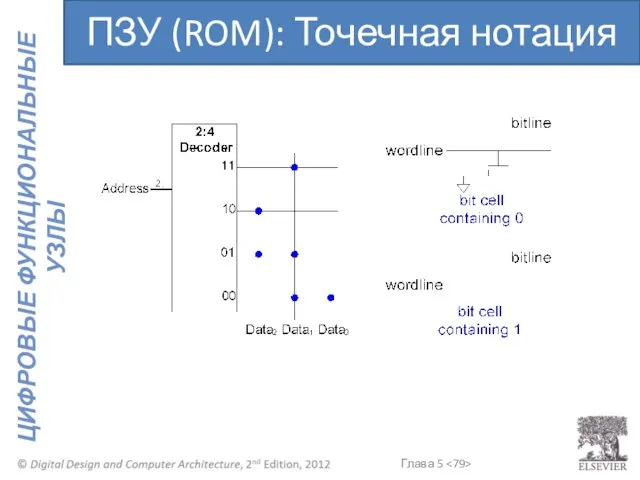

- 79. ПЗУ (ROM): Точечная нотация

- 80. Разрабатывал память и быстродействующие схемы для Toshiba, 1971-1994 Изобрел флэш-память в процессе самостоятельной работы, проводимой по

- 81. Хранение данных в ПЗУ (ROM)

- 82. Data2 = A1 ⊕ A0 Data1 = A1 + A0 Data0 = A1A0 Логические функции и

- 83. Реализовать следующие логические функции, используя ПЗУ 22 × 3-бит: X = AB Y = A +

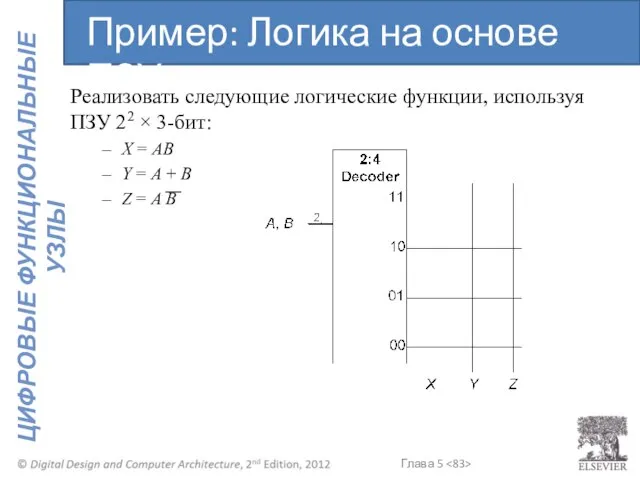

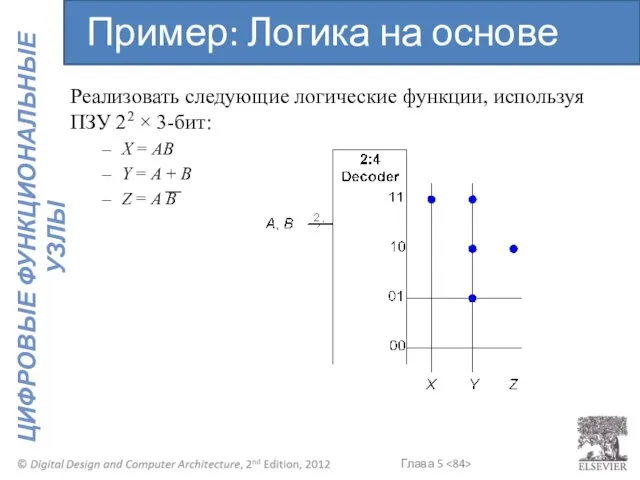

- 84. Реализовать следующие логические функции, используя ПЗУ 22 × 3-бит: X = AB Y = A +

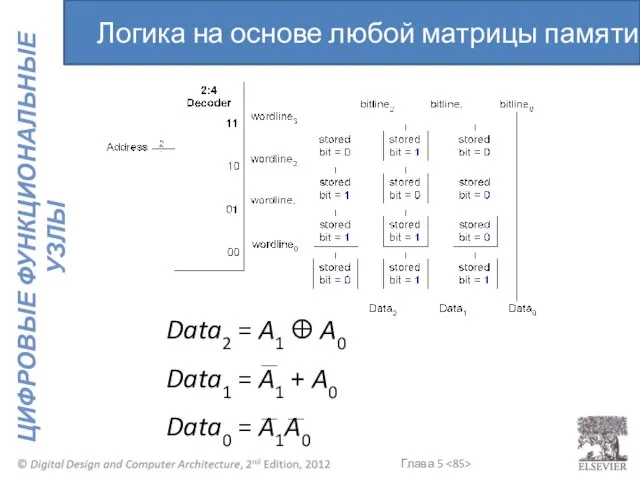

- 85. Data2 = A1 ⊕ A0 Data1 = A1 + A0 Data0 = A1A0 Логика на основе

- 86. Реализовать следующие логические функции, используя 22 × 3-битовую матрицу памяти: X = AB Y = A

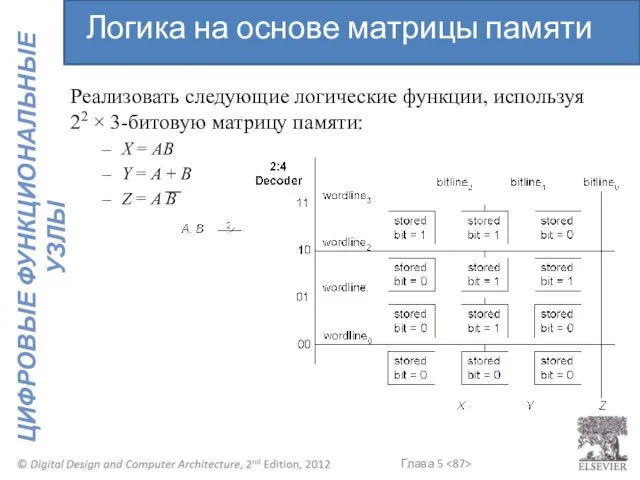

- 87. Реализовать следующие логические функции, используя 22 × 3-битовую матрицу памяти: X = AB Y = A

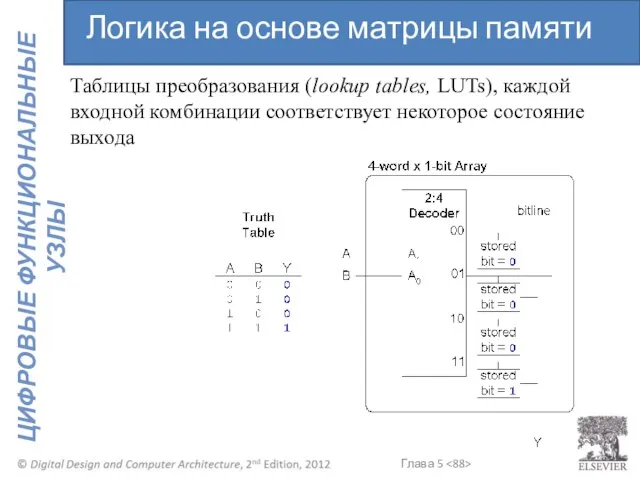

- 88. Таблицы преобразования (lookup tables, LUTs), каждой входной комбинации соответствует некоторое состояние выхода Логика на основе матрицы

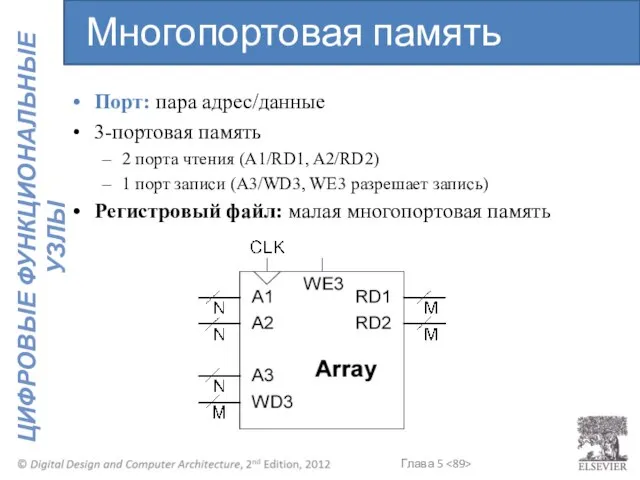

- 89. Порт: пара адрес/данные 3-портовая память 2 порта чтения (A1/RD1, A2/RD2) 1 порт записи (A3/WD3, WE3 разрешает

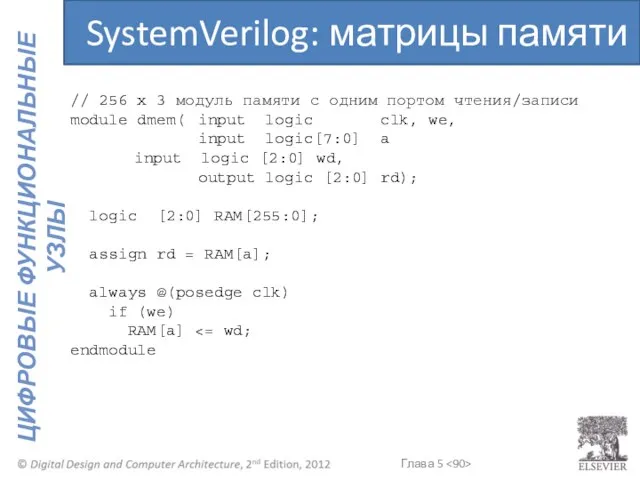

- 90. // 256 x 3 модуль памяти с одним портом чтения/записи module dmem( input logic clk, we,

- 91. PLAs (ПЛМ, Programmable logic arrays) –программируемая логическая матрица AND матрица, затем OR матрица Только комбинационная логика

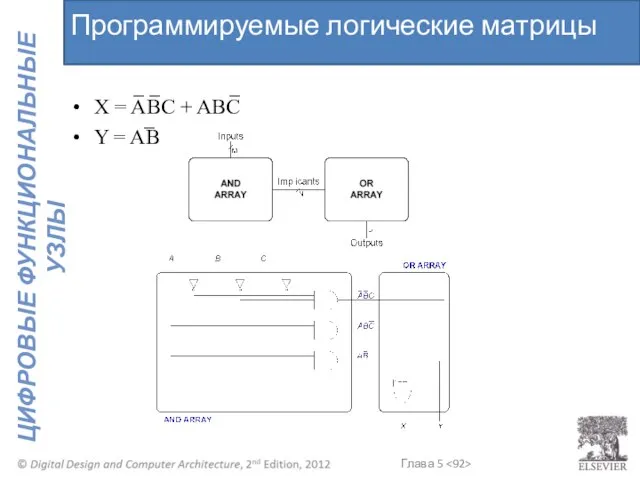

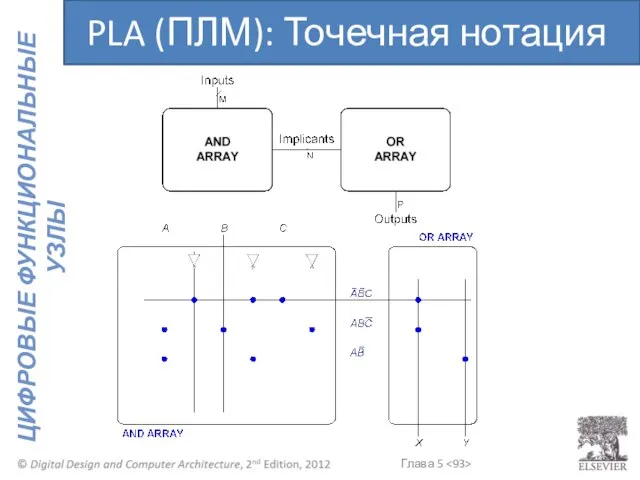

- 92. X = ABC + ABC Y = AB Программируемые логические матрицы

- 93. PLA (ПЛМ): Точечная нотация

- 94. Состоит из: LE (логических элементов): реализуют логику IOE (Элементов ввода/вывода): интерфейс с внешним миром Programmable interconnection:

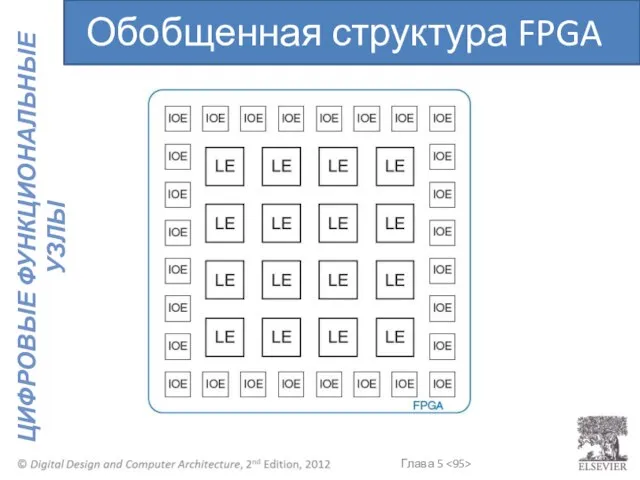

- 95. Обобщенная структура FPGA

- 96. Состоят из: Таблиц преобразования (LUT): реализуют комбинационную логику Триггеров: реализуют последовательностную логику Мультиплексоров: соединяют таблицы преобразования

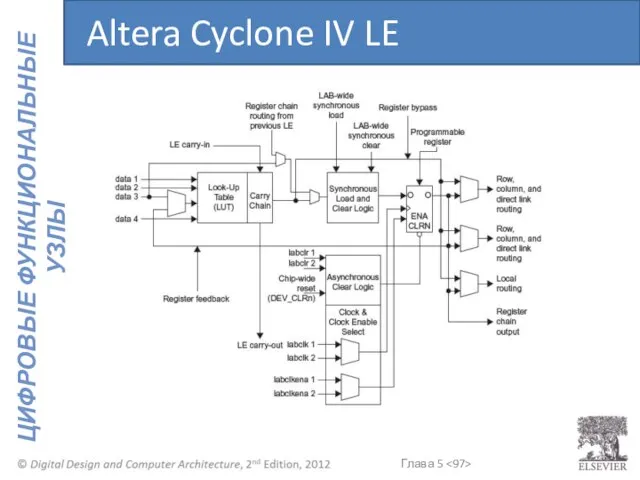

- 97. Altera Cyclone IV LE

- 98. Конфигурируемые логические блоки (CLB) Spartan имеют: 1 четырехвходовую LUT 1 регистровый выход 1 комбинационный выход Altera

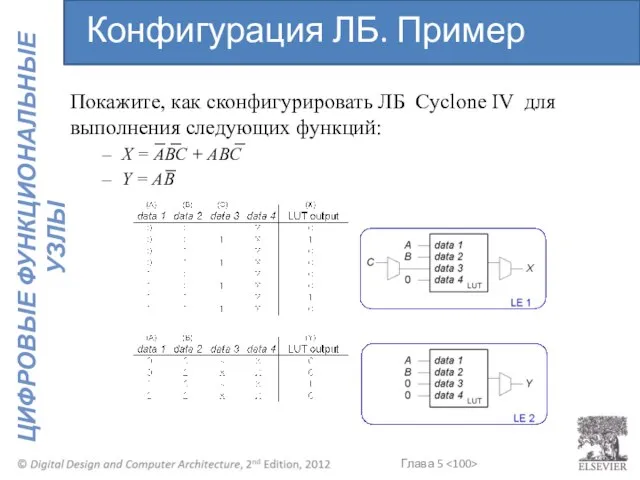

- 99. Покажите, как сконфигурировать логические блоки Cyclone IV для выполнения следующих функций: X = ABC + ABC

- 100. Покажите, как сконфигурировать ЛБ Cyclone IV для выполнения следующих функций: X = ABC + ABC Y

- 102. Скачать презентацию

Проектировка и разработка игры в жанре RPG

Проектировка и разработка игры в жанре RPG Кибернетика и синергетика

Кибернетика и синергетика Информационные технологии в металлургии (лекция 2)

Информационные технологии в металлургии (лекция 2) Создание курса в СДО Moodle

Создание курса в СДО Moodle Презентация "Понятие модели. Моделирование" - скачать презентации по Информатике

Презентация "Понятие модели. Моделирование" - скачать презентации по Информатике Реляционная алгебра. (Лекция 7)

Реляционная алгебра. (Лекция 7) ОКСИОН - Общероссийская Комплексная Система Информирования и Оповещения Населения

ОКСИОН - Общероссийская Комплексная Система Информирования и Оповещения Населения Верстка web-страниц. Выполнение верстки в соответствии с техническим заданием. (Этап 2)

Верстка web-страниц. Выполнение верстки в соответствии с техническим заданием. (Этап 2) Путешествие в страну информатики

Путешествие в страну информатики Создание интерактивных тестов в программе MyTestX

Создание интерактивных тестов в программе MyTestX Тема №7 Маршрутизация стегосистем. Занятие №2 Tor (луковичная) маршрутизация

Тема №7 Маршрутизация стегосистем. Занятие №2 Tor (луковичная) маршрутизация Великие ученые. Информатика

Великие ученые. Информатика Дополнительные технологии интеллектуализации ГИС

Дополнительные технологии интеллектуализации ГИС Магистрально-модульный принцип построения компьютера

Магистрально-модульный принцип построения компьютера Обработка информации в системе управления базами данных

Обработка информации в системе управления базами данных Вопросы авторских прав в сети Интернет

Вопросы авторских прав в сети Интернет Блочная модель

Блочная модель Standart funksiýalar: modul; sanyň kwadraty

Standart funksiýalar: modul; sanyň kwadraty Установка Otkell для самых маленьких

Установка Otkell для самых маленьких Классификация компьютеров

Классификация компьютеров  Разработка приложения Квест с использованием веб-технологии

Разработка приложения Квест с использованием веб-технологии Арифметические операции в позиционных системах счисления (4). 8 класс

Арифметические операции в позиционных системах счисления (4). 8 класс Разновидности компьютерных сетей Учитель информатики МБОУ Селезянской СОШ Челябинская область Коркина Наталья Юрьевна

Разновидности компьютерных сетей Учитель информатики МБОУ Селезянской СОШ Челябинская область Коркина Наталья Юрьевна  Презентация "Разомкнутая и замкнутая информационная системы" - скачать презентации по Информатике

Презентация "Разомкнутая и замкнутая информационная системы" - скачать презентации по Информатике Поиск и сортировка информации в базах данных

Поиск и сортировка информации в базах данных Динамические массивы и примеры на С++ для АСУб и ЭВМб. Тема 5-2

Динамические массивы и примеры на С++ для АСУб и ЭВМб. Тема 5-2 Системы счисления

Системы счисления Профилактика кибербуллинга

Профилактика кибербуллинга