Содержание

- 2. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Интегральная микросхема – микроэлектронное изделие,

- 3. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 1952 — Джэффри Даммер, идея

- 4. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Серия ИМС – набор типов

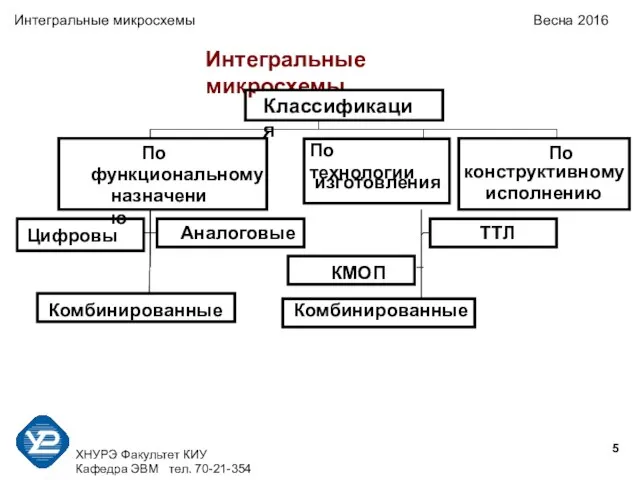

- 5. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016

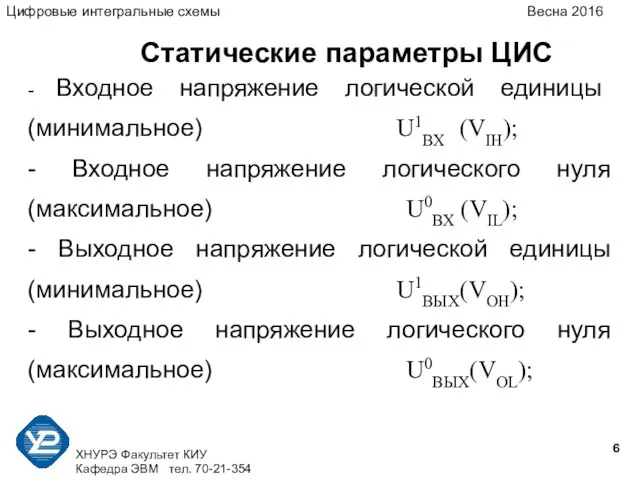

- 6. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Статические параметры ЦИС - Входное напряжение логической единицы (минимальное)

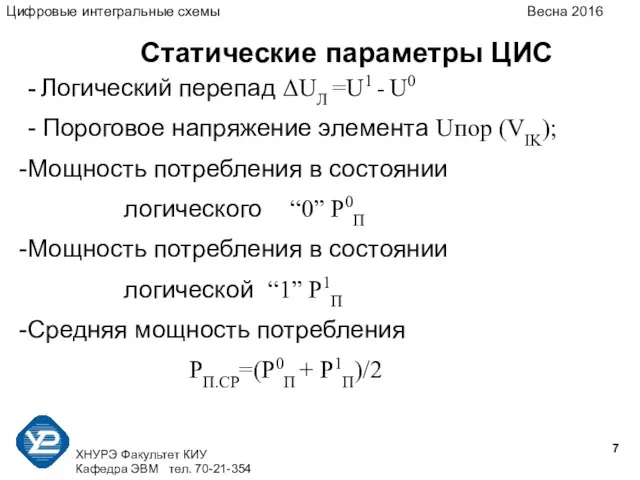

- 7. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Статические параметры ЦИС - Логический перепад ΔUЛ =U1 -

- 8. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Поля допусков входных и выходных сигналов ИМС ТТЛ-технологии Цифровые

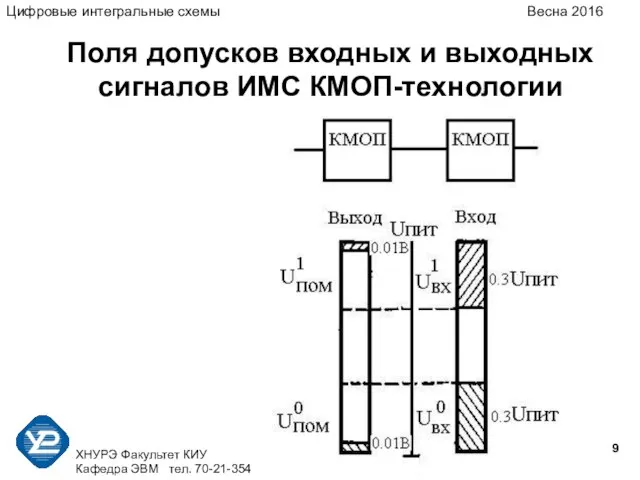

- 9. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Поля допусков входных и выходных сигналов ИМС КМОП-технологии Цифровые

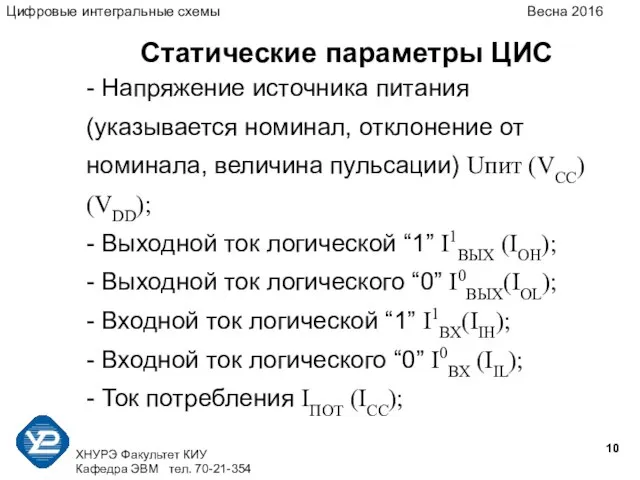

- 10. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Статические параметры ЦИС - Напряжение источника питания (указывается номинал,

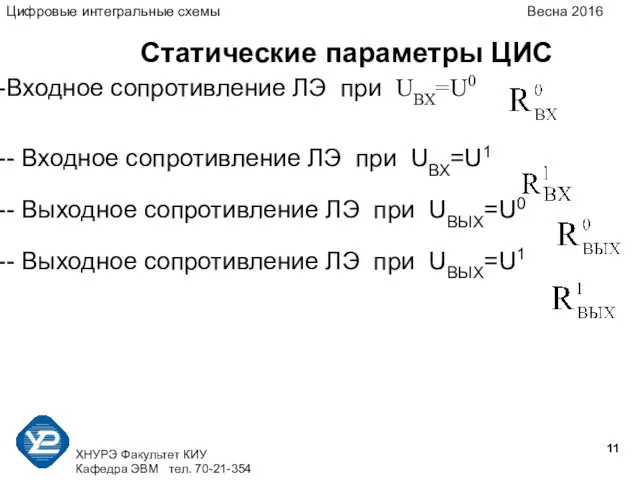

- 11. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Статические параметры ЦИС Входное сопротивление ЛЭ при UВХ=U0 -

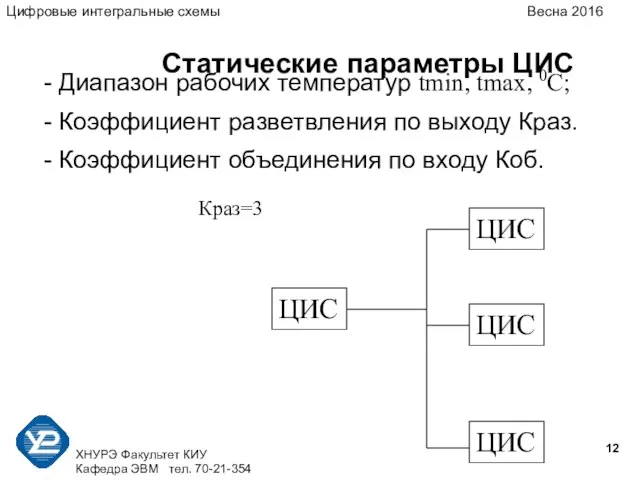

- 12. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Статические параметры ЦИС - Диапазон рабочих температур tmin, tmax,

- 13. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Передаточная характеристика Uвых=f(Uвх) Цифровые интегральные схемы Весна 2016

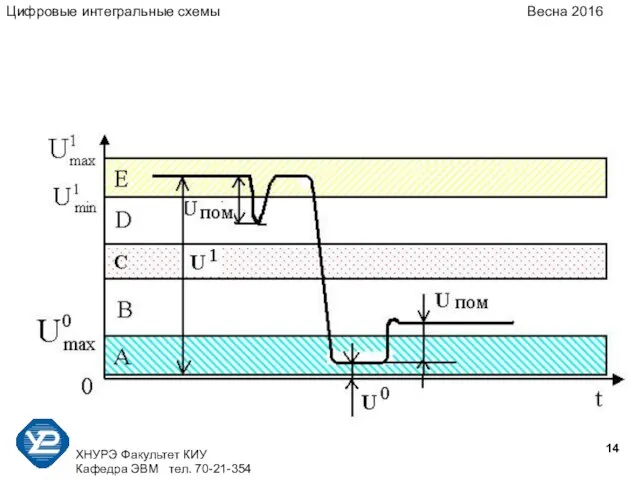

- 14. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Цифровые интегральные схемы Весна 2016

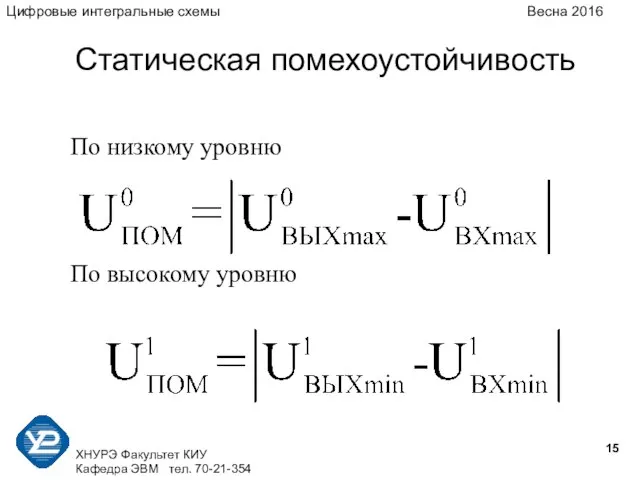

- 15. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Цифровые интегральные схемы Весна 2016 Статическая помехоустойчивость По низкому

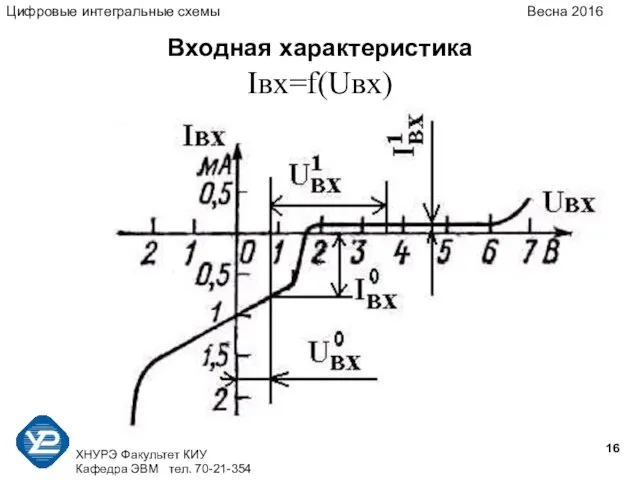

- 16. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Входная характеристика Iвх=f(Uвх) Цифровые интегральные схемы Весна 2016

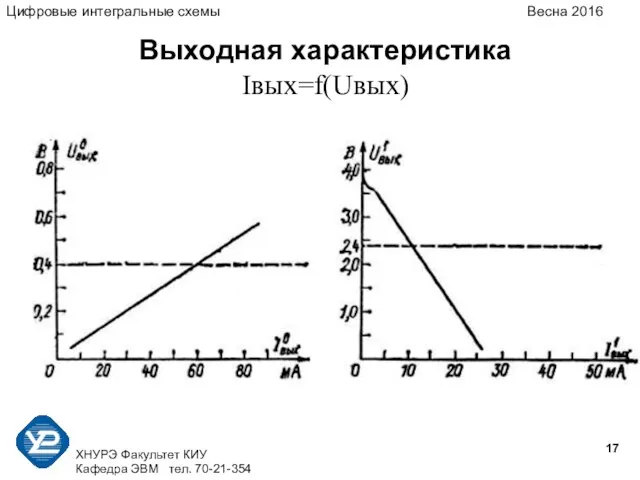

- 17. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Выходная характеристика Iвых=f(Uвых) Цифровые интегральные схемы Весна 2016

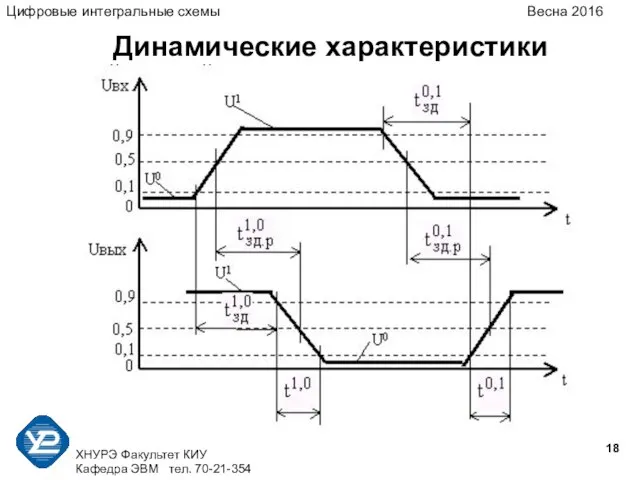

- 18. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Динамические характеристики Цифровые интегральные схемы Весна 2016

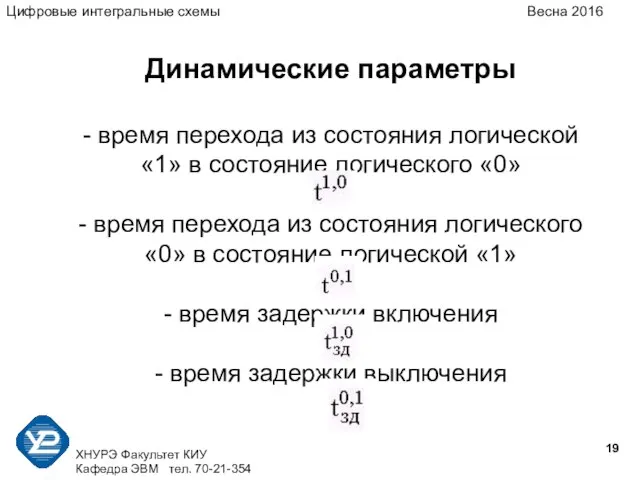

- 19. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Динамические параметры - время перехода из состояния логической «1»

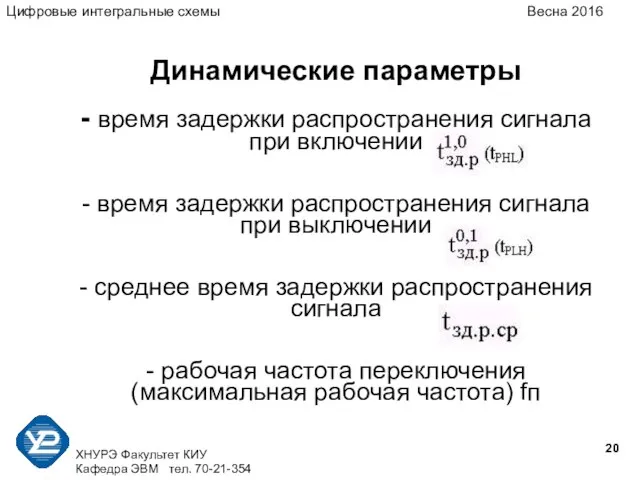

- 20. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Динамические параметры - время задержки распространения сигнала при включении

- 21. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Динамические параметры Предельно допустимая емкость нагрузки СН, Ф Предельно

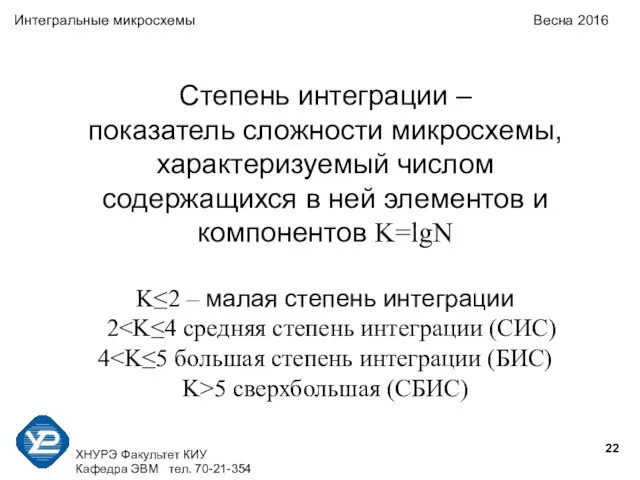

- 22. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Степень интеграции – показатель сложности

- 23. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Элемент – часть ИС, в

- 24. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Подложка ИС – заготовка, предназначенная

- 25. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Полупроводниковая пластина – заготовка, используемая

- 26. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Контактные площадки – металлизированные участки

- 27. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Сформированные микросхемы на кристалле

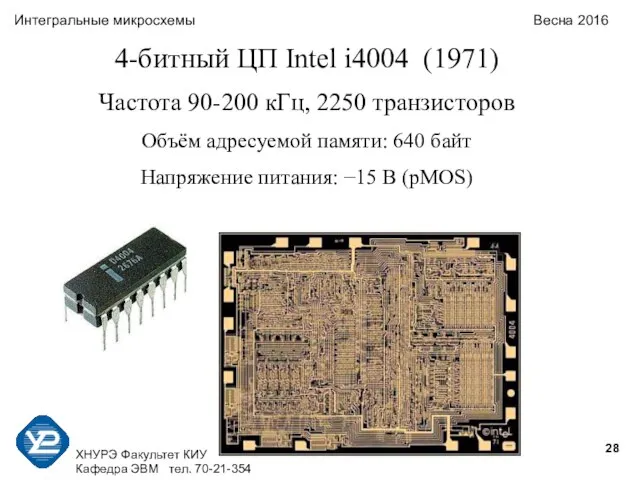

- 28. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 4-битный ЦП Intel i4004 (1971)

- 29. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Корпус – часть конструкции ИС,

- 30. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Примеры корпусов микросхем

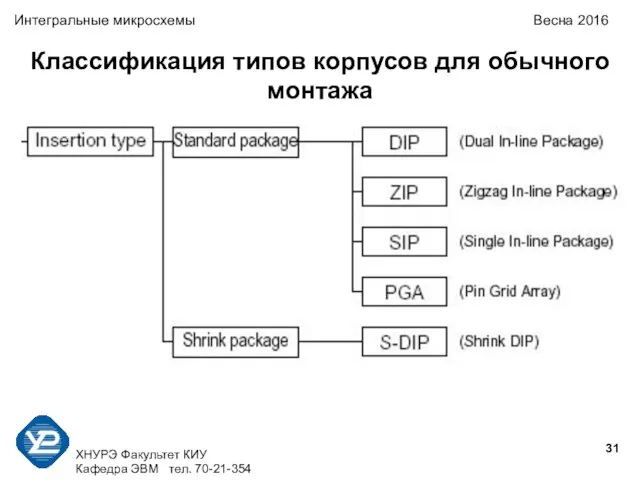

- 31. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Классификация типов корпусов для обычного

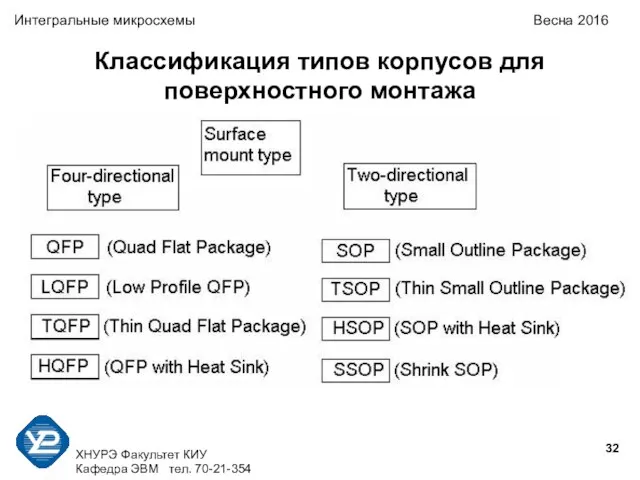

- 32. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Классификация типов корпусов для поверхностного

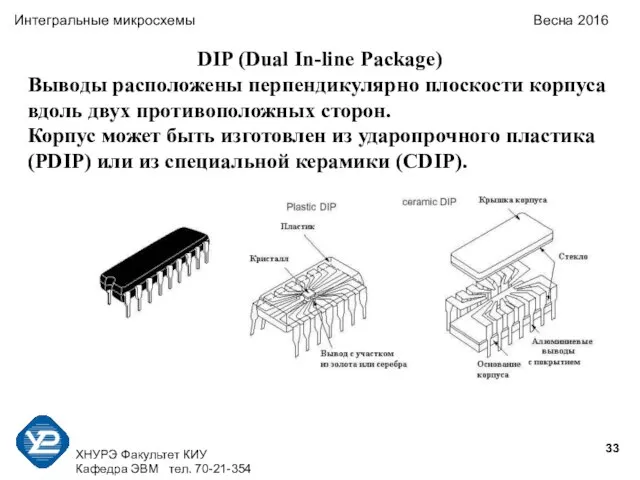

- 33. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 DIP (Dual In-line Package) Выводы

- 34. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 SDIP (Shrink DIP) Корпус типа

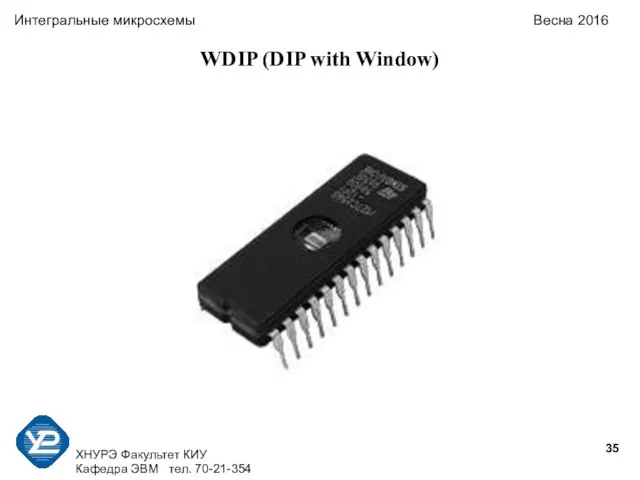

- 35. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 WDIP (DIP with Window)

- 36. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 QFI (Quad Flat I-leaded Package)

- 37. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 SIP (Single In-line Package) Выводы

- 38. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 HSIP (SIP with Heat Sink)

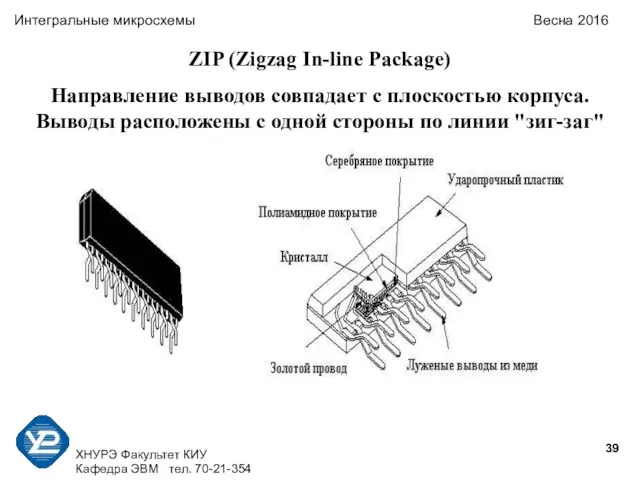

- 39. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 ZIP (Zigzag In-line Package) Направление

- 40. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 ИМС в корпусах для поверхностного

- 41. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 SSOP (Shrink SOP) Корпус типа

- 42. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 TSOP(Thin Small Outline Package) От

- 43. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 TSSOP (Thin Shrink Small Outline

- 44. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 HSOP(SOP with Heat Sink) Корпус

- 45. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 PSOP (Power Small Outline Package)

- 46. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 РQFP (Plastic Quad Flat Packagе)

- 47. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 TQFP(Thin Quad Flat Package) Корпус

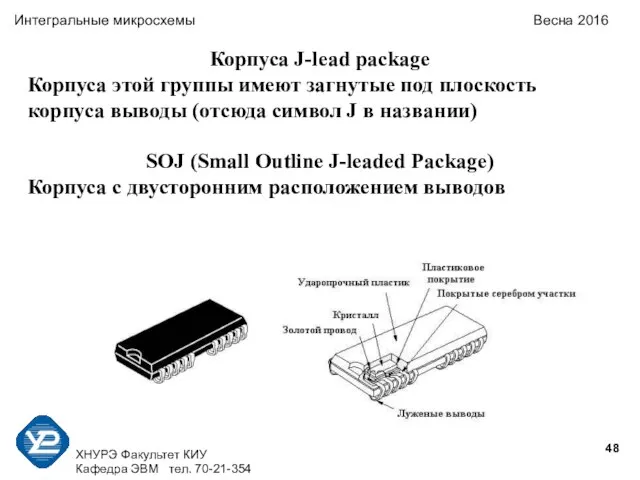

- 48. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Корпуса J-lead package Корпуса этой

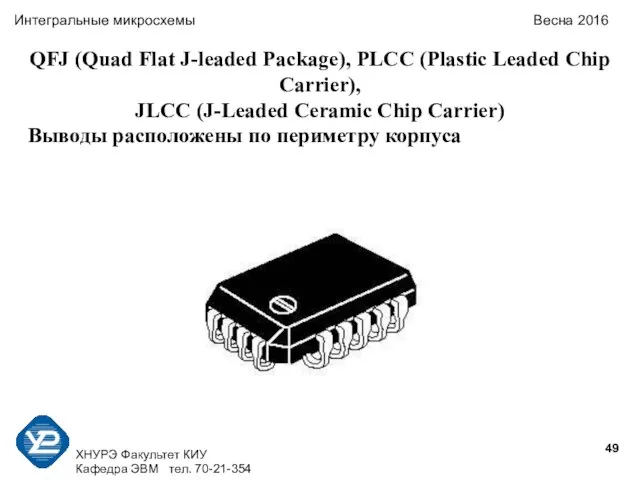

- 49. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 QFJ (Quad Flat J-leaded Package),

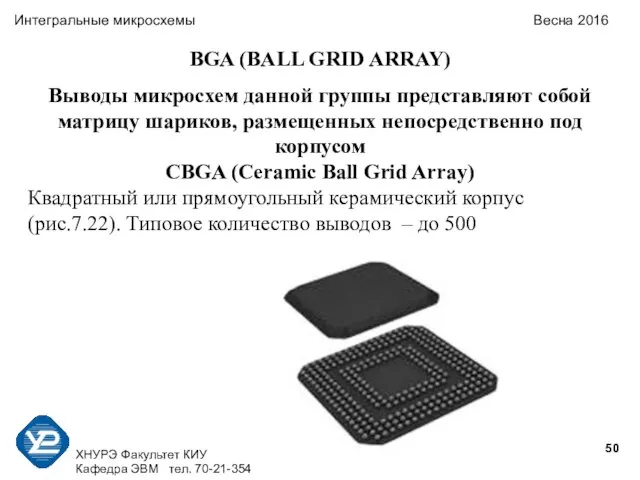

- 50. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 BGA (BALL GRID ARRAY) Выводы

- 51. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 CPGA (Ceramic Pin Grid Array)

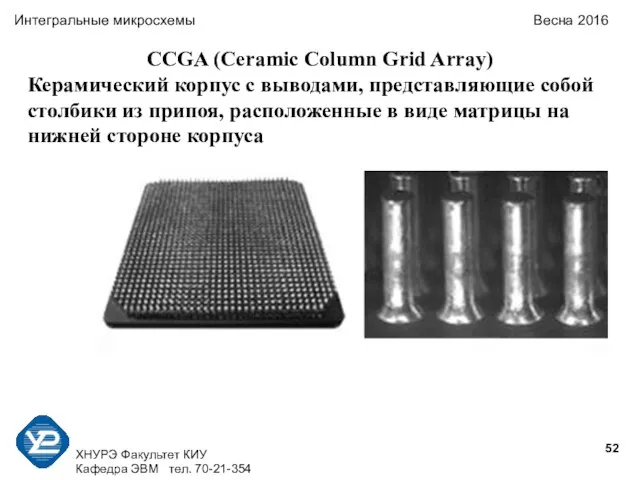

- 52. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 CCGA (Ceramic Column Grid Array)

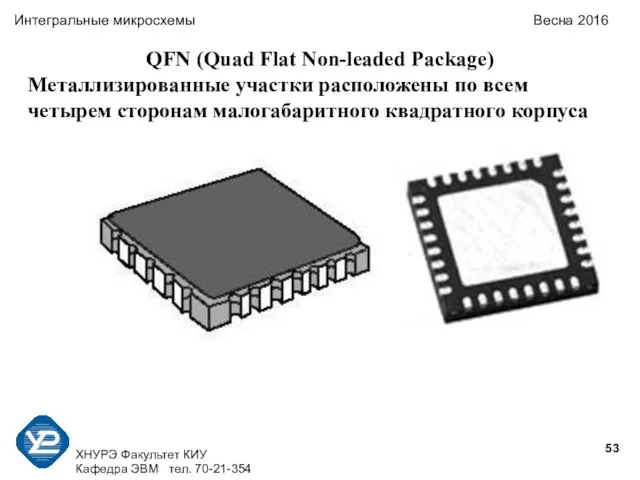

- 53. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 QFN (Quad Flat Non-leaded Package)

- 54. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 PQFN (Power Quad Flat No

- 55. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 DFN (Dual Flat No Leads)

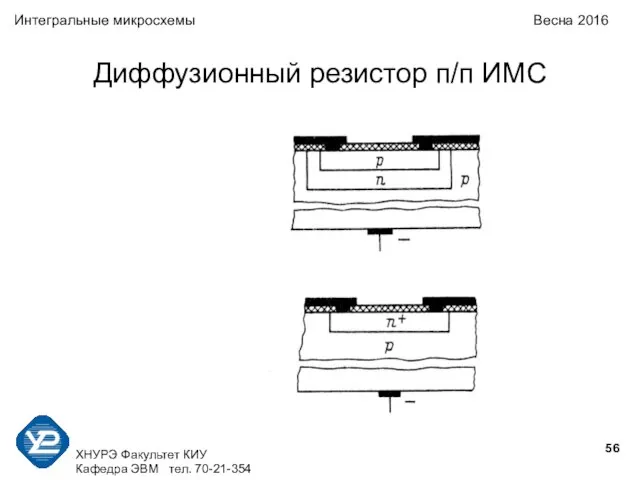

- 56. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Диффузионный резистор п/п ИМС

- 57. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Диффузионный конденсатор п/п ИМС

- 58. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 МОП-конденсатор

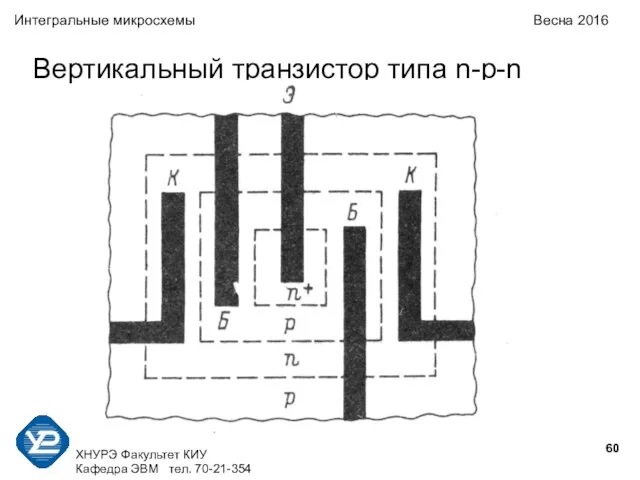

- 59. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Вертикальный транзистор типа n-p-n

- 60. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Вертикальный транзистор типа n-p-n

- 61. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Горизонтальный транзистор типа p-n-p

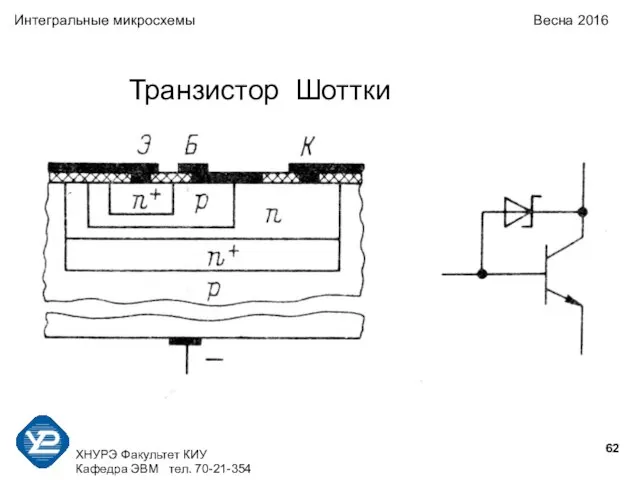

- 62. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Транзистор Шоттки

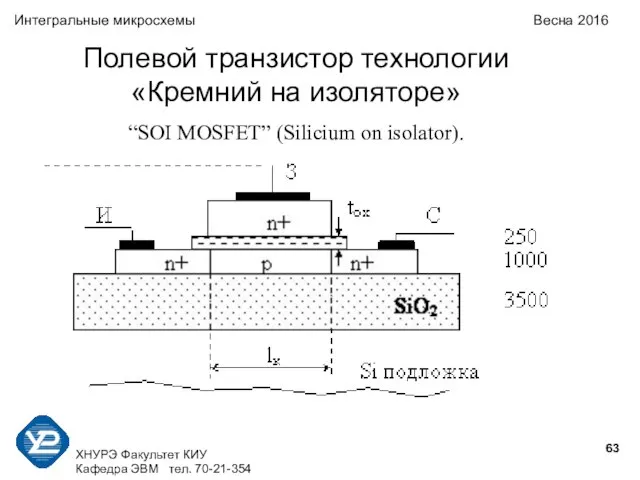

- 63. ХНУРЭ Факультет КИУ Кафедра ЭВМ тел. 70-21-354 Интегральные микросхемы Весна 2016 Полевой транзистор технологии «Кремний на

- 65. Скачать презентацию

Тайна имени

Тайна имени Машины для сварки давлением. (Лекция 20)

Машины для сварки давлением. (Лекция 20) Уход за одеждой из искусственных и синтетических тканей. Значение символов на ярлыках одежды

Уход за одеждой из искусственных и синтетических тканей. Значение символов на ярлыках одежды Воспалительные заболевания тазовых органов у женщин

Воспалительные заболевания тазовых органов у женщин 20130619_istoriya_prazdnika_1_maya

20130619_istoriya_prazdnika_1_maya 20140924_kak_govoriat_zhivotnie_dom

20140924_kak_govoriat_zhivotnie_dom Русские имена. Имена исконные и заимствованные, традиционные и новые, устаревшие и популярные

Русские имена. Имена исконные и заимствованные, традиционные и новые, устаревшие и популярные Как сделать простой ламповый приемник

Как сделать простой ламповый приемник социология 13.04.17

социология 13.04.17 20150111_vot_eto_kot

20150111_vot_eto_kot Счастливы вместе

Счастливы вместе K19 SMT Issue List

K19 SMT Issue List 20120303_roman_olgi_slavnikovoy_2017

20120303_roman_olgi_slavnikovoy_2017 Требования к транспорту и правила / примеры погрузки

Требования к транспорту и правила / примеры погрузки Собака- как объект окружающего мира

Собака- как объект окружающего мира Молодежная одежда Весна-2021 Бренд Roomyroom_showroom

Молодежная одежда Весна-2021 Бренд Roomyroom_showroom Развитие логического мышления

Развитие логического мышления Дана - консультант по продуктовым характеристикам табачной компании JTI

Дана - консультант по продуктовым характеристикам табачной компании JTI Информационные технологии – движущая сила развития общества

Информационные технологии – движущая сила развития общества Страх публичных выступлений

Страх публичных выступлений Краснобаев 12 пр

Краснобаев 12 пр Perfect Drilling & Downhole Tools

Perfect Drilling & Downhole Tools Оборудование участка железной дороги устройствами АПК-ДК

Оборудование участка железной дороги устройствами АПК-ДК Қаңтардың жиырма алтысы Нәтиже сабақ

Қаңтардың жиырма алтысы Нәтиже сабақ New 3kol logo

New 3kol logo Портфолио педагога-психолога Маскиной Ольги Николаевны

Портфолио педагога-психолога Маскиной Ольги Николаевны лекция

лекция Клоун. Найди 4 отличия

Клоун. Найди 4 отличия