Содержание

- 2. Логические элементы на МОП-транзисторах

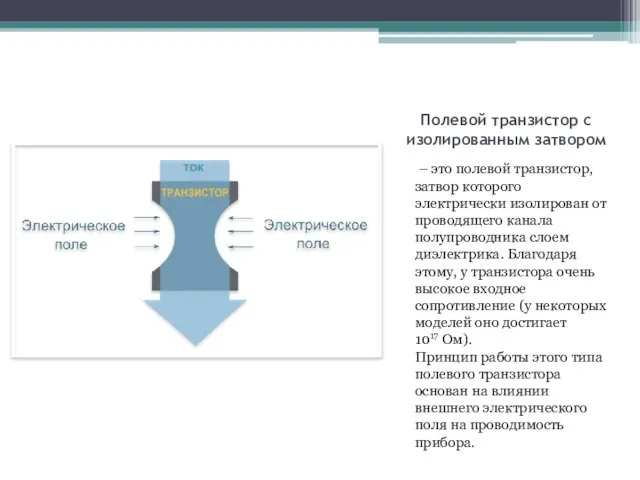

- 3. Полевой транзистор с изолированным затвором – это полевой транзистор, затвор которого электрически изолирован от проводящего канала

- 4. В соответствии со своей физической структурой, полевой транзистор с изолированным затвором носит название МОП-транзистор (Металл-Оксид-Полупроводник) МОП-транзисторы

- 5. МОП-транзистор с индуцированным каналом.

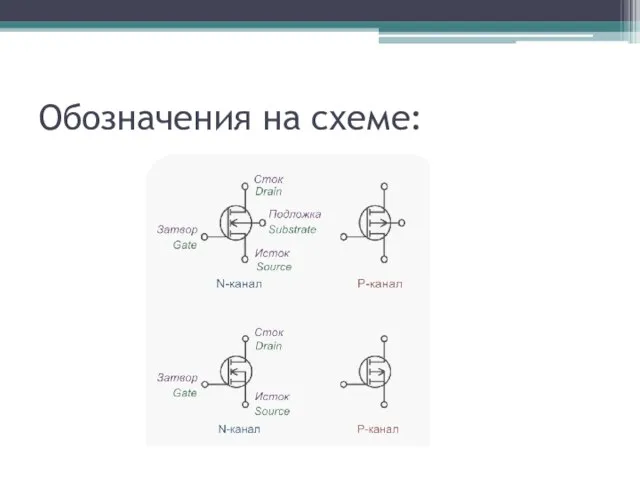

- 6. Обозначения на схеме:

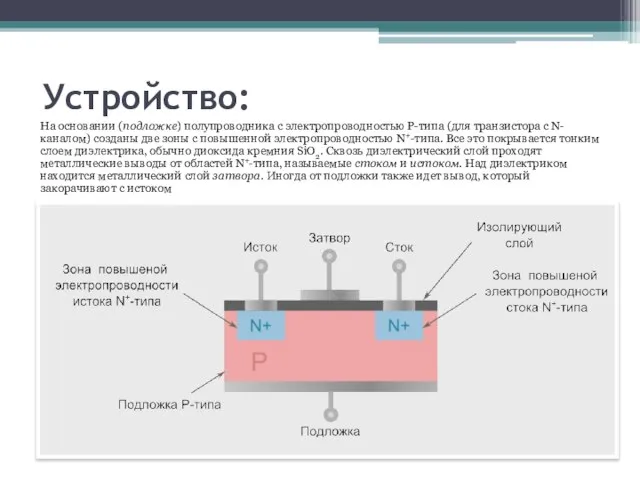

- 7. Устройство: На основании (подложке) полупроводника с электропроводностью P-типа (для транзистора с N-каналом) созданы две зоны с

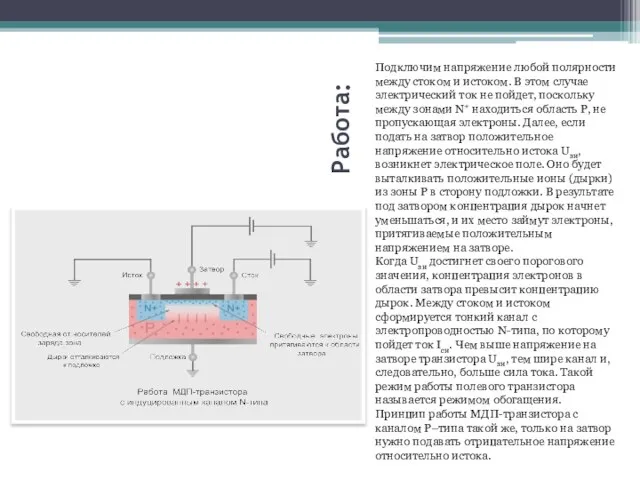

- 8. Работа: Подключим напряжение любой полярности между стоком и истоком. В этом случае электрический ток не пойдет,

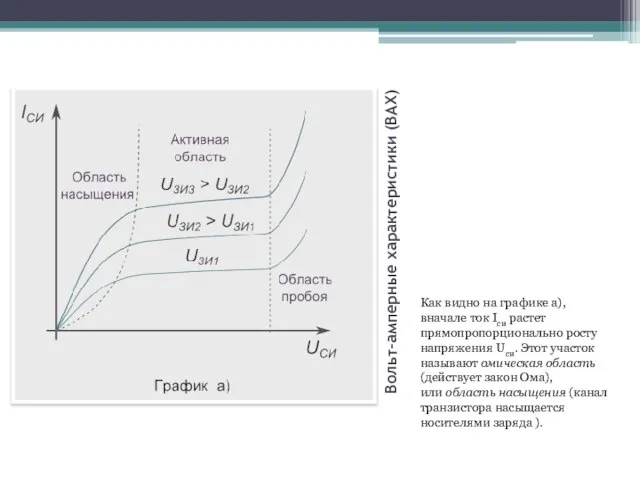

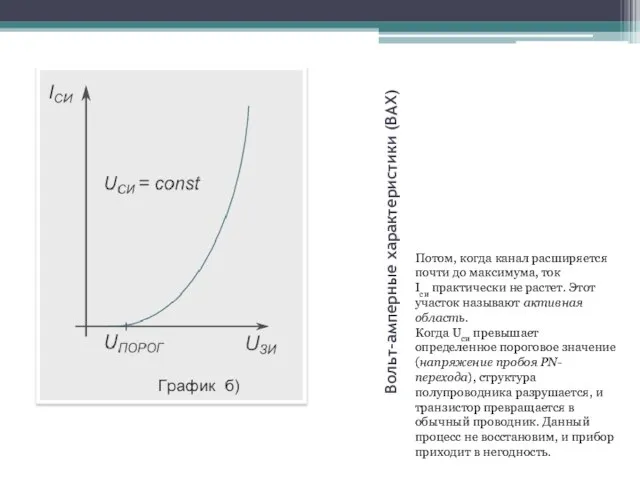

- 9. Вольт-амперные характеристики (ВАХ) Как видно на графике а), вначале ток Iси растет прямопропорционально росту напряжения Uси.

- 10. Вольт-амперные характеристики (ВАХ) Потом, когда канал расширяется почти до максимума, ток Iси практически не растет. Этот

- 11. Преимущества: Благодаря очень высокому входному сопротивлению, цепь полевых транзисторов расходует крайне мало энергии, так как практически

- 12. Недостатки: Структура полевых транзисторов начинает разрушаться при меньшей температуре (150С), чем структура биполярных транзисторов (200С). Несмотря

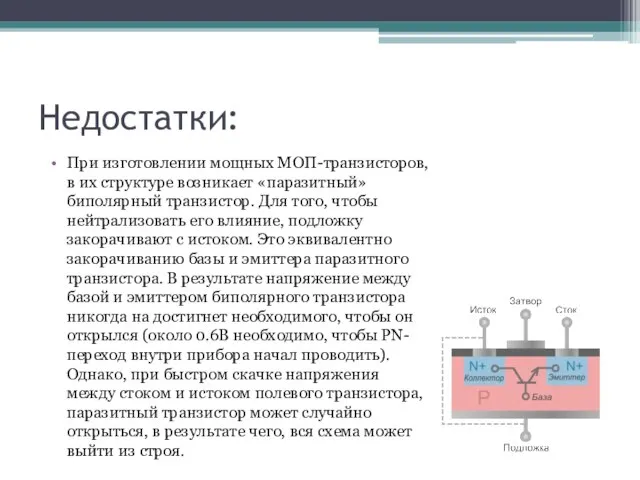

- 13. Недостатки: При изготовлении мощных МОП-транзисторов, в их структуре возникает «паразитный» биполярный транзистор. Для того, чтобы нейтрализовать

- 14. Недостатки: Важнейшим недостатком полевых транзисторов является их чувствительность к статическому электричеству. Поскольку изоляционный слой диэлектрика на

- 15. Логические элементы на КМОП-транзисторах

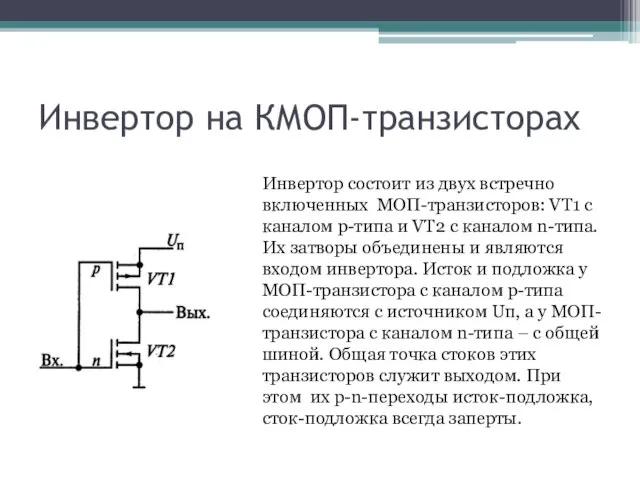

- 16. Инвертор на КМОП-транзисторах Инвертор состоит из двух встречно включенных МОП-транзисторов: VT1 с каналом р-типа и VT2

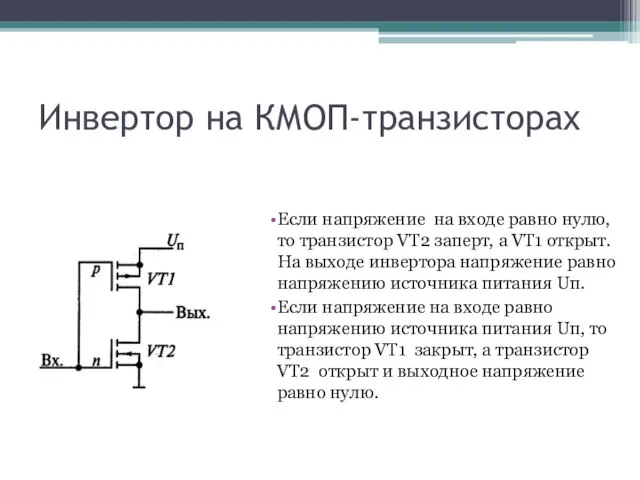

- 17. Инвертор на КМОП-транзисторах Если напряжение на входе равно нулю, то транзистор VT2 заперт, а VT1 открыт.

- 18. Фактор, позволяющий создавать схемы с высокой степенью интеграции: В статическом состоянии потребляемая мощность микросхем равна нулю.

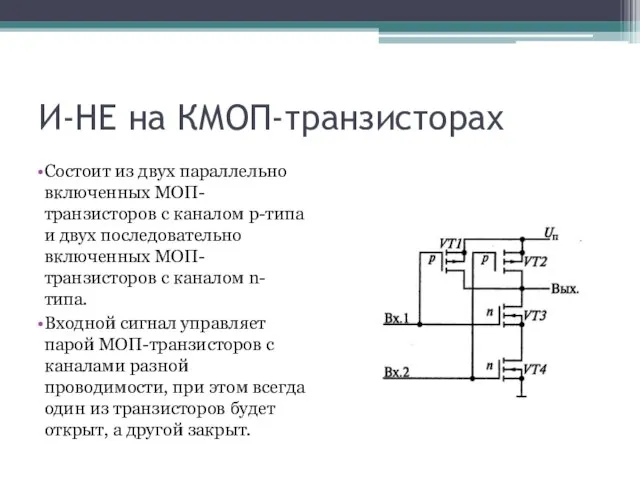

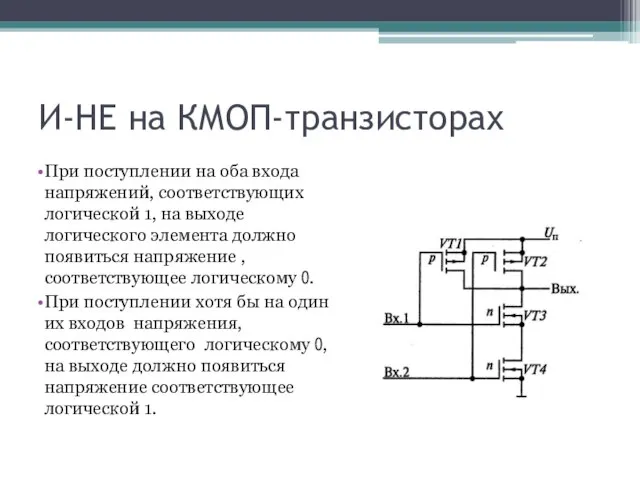

- 19. И-НЕ на КМОП-транзисторах Состоит из двух параллельно включенных МОП-транзисторов с каналом р-типа и двух последовательно включенных

- 20. И-НЕ на КМОП-транзисторах При поступлении на оба входа напряжений, соответствующих логической 1, на выходе логического элемента

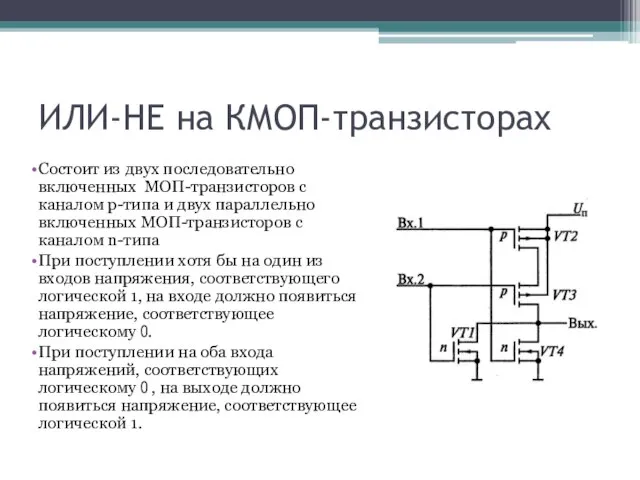

- 21. ИЛИ-НЕ на КМОП-транзисторах Состоит из двух последовательно включенных МОП-транзисторов с каналом р-типа и двух параллельно включенных

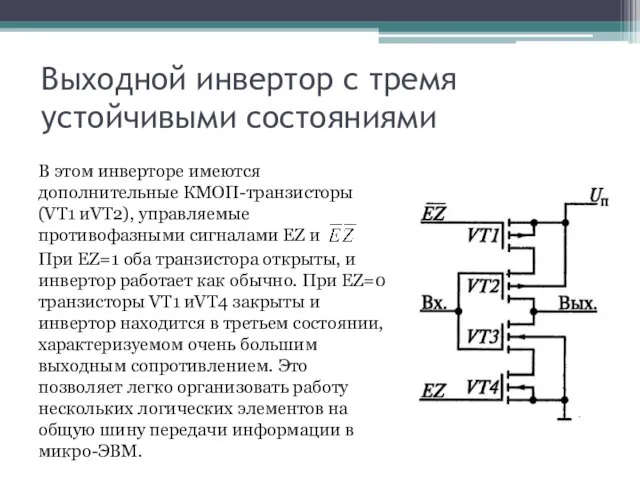

- 22. Выходной инвертор с тремя устойчивыми состояниями В этом инверторе имеются дополнительные КМОП-транзисторы (VT1 иVT2), управляемые противофазными

- 23. Особенности применения микросхем на КМОП-транзисторах при построении цифровых устройств

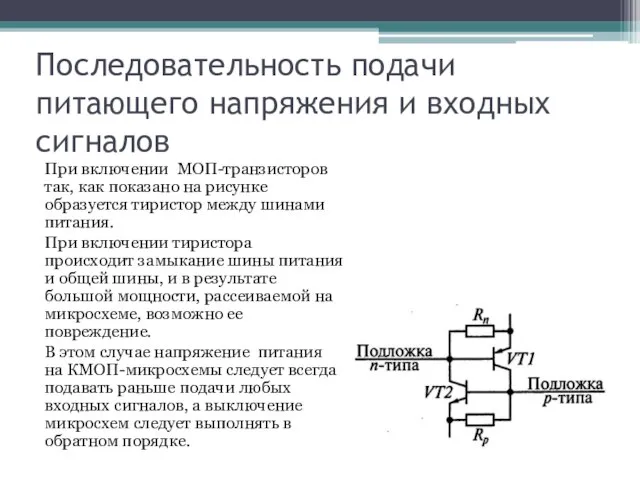

- 24. Последовательность подачи питающего напряжения и входных сигналов При включении МОП-транзисторов так, как показано на рисунке образуется

- 25. Токоограничивающие резисторы на выходе и входе логического элемента Если на выходе КМОП-микросхемы включен конденсатор с достаточно

- 26. Подавление помех в цепи питания Для подавление помех в цепи питания между шиной питания и общей

- 27. Неиспользуемые входы КМОП-микросхемы Если вход не подсоединен, то на нем возникают непредсказуемые напряжения за счет наводок

- 28. Правила обращения с КМОП-транзисторами: В процессе хранения и транспортирования отдельных микросхем выводы их должны быть соединены

- 29. Сопряжение микросхем ТТЛ и КМОП Совместное использование логических элементов на ТТЛ и КМОП-транзисторах применяют для снижения

- 31. Скачать презентацию

Фосфорное сырье, методы его обогащения

Фосфорное сырье, методы его обогащения Logitech_VC_solutions

Logitech_VC_solutions urok-konkurs

urok-konkurs Технологія отримання міді

Технологія отримання міді Расчет прочности нормальных сечений

Расчет прочности нормальных сечений Аттестационная работа. Создание безбарьерной среды для незрячих людей

Аттестационная работа. Создание безбарьерной среды для незрячих людей Электрическая ёмкость. Конденсаторы

Электрическая ёмкость. Конденсаторы Объемно-конструктивные решения. Инженерное обустройство

Объемно-конструктивные решения. Инженерное обустройство Sistema_Chelovek_Mashina

Sistema_Chelovek_Mashina Религиозный туризм. Буддизм

Религиозный туризм. Буддизм 았 었

았 었 Металлургическая промышленность Казахстана

Металлургическая промышленность Казахстана Получение тканей из химических волокон

Получение тканей из химических волокон Ознаки зими. (Природознавство 2 клас)

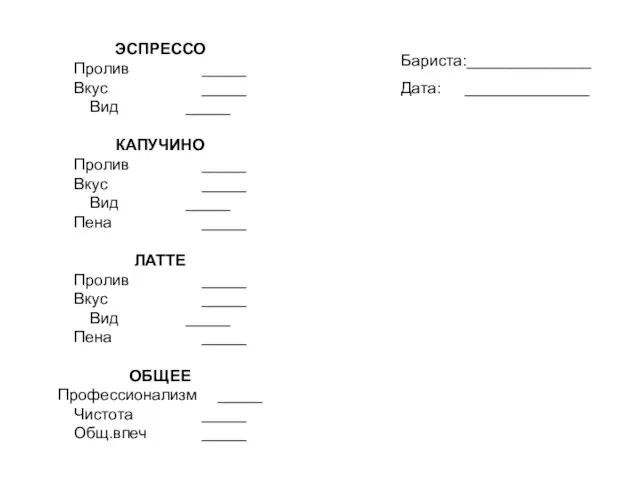

Ознаки зими. (Природознавство 2 клас) аттестационный лист бариста

аттестационный лист бариста Загадки о городских птицах

Загадки о городских птицах Расчет на срез и смятие

Расчет на срез и смятие Юбки женские. Тест

Юбки женские. Тест Храм гроба господня

Храм гроба господня My teaching Background

My teaching Background 20150924_voda_kopirovanie_nxpowerlite

20150924_voda_kopirovanie_nxpowerlite Вот оно какое, наше лето

Вот оно какое, наше лето Удмуртия - моя малая Родина

Удмуртия - моя малая Родина Натюрморт с предметом цилиндрической формы в горизонтальном положении и драпировкой. Процесс рисования натюрмортов

Натюрморт с предметом цилиндрической формы в горизонтальном положении и драпировкой. Процесс рисования натюрмортов И глаза дорогих солдат с фотографий увядших глядят

И глаза дорогих солдат с фотографий увядших глядят APQP

APQP Кузнецкий и Канско-Ачинский угольные бассейны

Кузнецкий и Канско-Ачинский угольные бассейны Назначение и устройство токарно - винторезного станка ТВ - 6. Виды и назначение токарных резцов

Назначение и устройство токарно - винторезного станка ТВ - 6. Виды и назначение токарных резцов