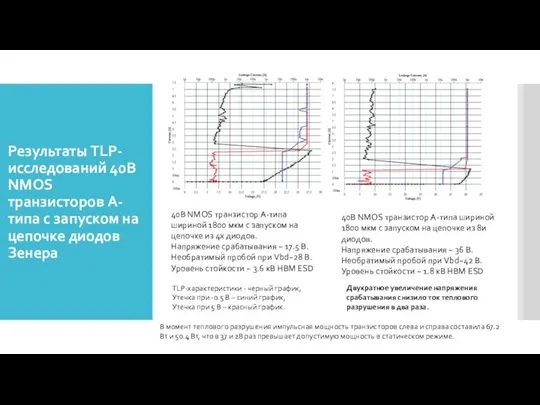

Результаты TLP-исследований 40В NMOS транзисторов A-типа с запуском на цепочке диодов Зенера

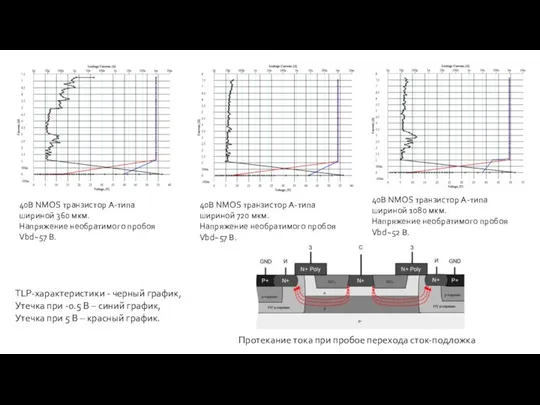

40В NMOS

транзистор A-типа шириной 1800 мкм с запуском на цепочке из 4х диодов.

Напряжение срабатывания ~ 17.5 В. Необратимый пробой при Vbd~28 В.

Уровень стойкости ~ 3.6 кВ HBM ESD

40В NMOS транзистор A-типа шириной 1800 мкм с запуском на цепочке из 8и диодов.

Напряжение срабатывания ~ 36 В. Необратимый пробой при Vbd~42 В.

Уровень стойкости ~ 1.8 кВ HBM ESD

В момент теплового разрушения импульсная мощность транзисторов слева и справа составила 67.2 Вт и 50.4 Вт, что в 37 и 28 раз превышает допустимую мощность в статическом режиме.

TLP-характеристики - черный график,

Утечка при -0.5 В – синий график,

Утечка при 5 В – красный график.

Двукратное увеличение напряжения срабатывания снизило ток теплового разрушения в два раза.

Залежи нефти и газа

Залежи нефти и газа 20120622_logopedicheskoe_soprovozhdenie_uchashchihsya_nachalnoy_shkoly

20120622_logopedicheskoe_soprovozhdenie_uchashchihsya_nachalnoy_shkoly Церковь и армия. Силы внутренней свободы ради защиты Веры и Отечества

Церковь и армия. Силы внутренней свободы ради защиты Веры и Отечества Фрукты

Фрукты Общие сведения о плотинах (Лекция 2)

Общие сведения о плотинах (Лекция 2) Информационно–аналитический центр комплекса градостроительной политики и строительства города Москвы Мосстройинформ

Информационно–аналитический центр комплекса градостроительной политики и строительства города Москвы Мосстройинформ a78f-a59a90fd

a78f-a59a90fd PET_p65

PET_p65 Плавающий дом

Плавающий дом Ручные швы для шитья игрушки

Ручные швы для шитья игрушки Мой выбор профессии

Мой выбор профессии Срок службы зданий износ

Срок службы зданий износ Реализация типовых законов регулирования системами на базе релейно-импульсных регуляторов. Лекция 13

Реализация типовых законов регулирования системами на базе релейно-импульсных регуляторов. Лекция 13 Религиозность во Франции

Религиозность во Франции Комментарии к рендерам

Комментарии к рендерам Узоры на крыльях бабочки

Узоры на крыльях бабочки Поздравления

Поздравления New debate modul

New debate modul Бирюков Л.Е. Основы планировки и благоустройства населенных мест и промышленных территорий

Бирюков Л.Е. Основы планировки и благоустройства населенных мест и промышленных территорий Святые, в земле Омской просиявшие

Святые, в земле Омской просиявшие Я служу Росси. 23 февраля

Я служу Росси. 23 февраля Искусство века. Искусство на века. Самые известные творения Челлини

Искусство века. Искусство на века. Самые известные творения Челлини Установочные элементы приспособлений

Установочные элементы приспособлений Услуги Компании Финам

Услуги Компании Финам Осложнения ветряной оспы у детей

Осложнения ветряной оспы у детей Электрические аппараты управления и защиты

Электрические аппараты управления и защиты Профессия аппаратчик

Профессия аппаратчик Пишем сочинение по художественному тексту

Пишем сочинение по художественному тексту