Содержание

- 2. Способы достижения универсальности компонентов Программный. СБИС обрабатывают цифровые данные по заданной программе (микропроцессоры). Аппаратный. Состав и

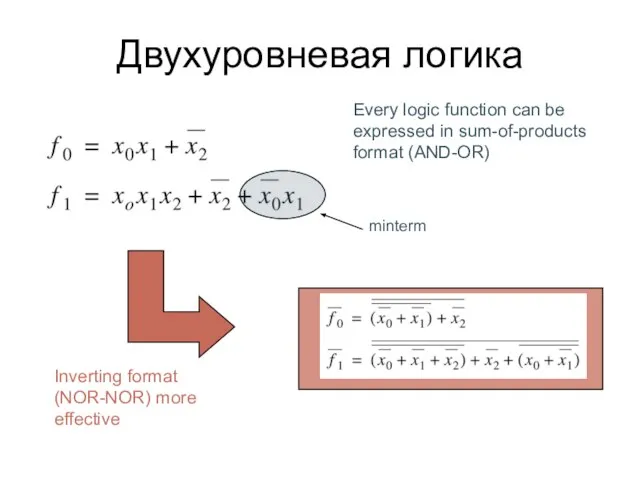

- 3. Двухуровневая логика Inverting format (NOR-NOR) more effective Every logic function can be expressed in sum-of-products format

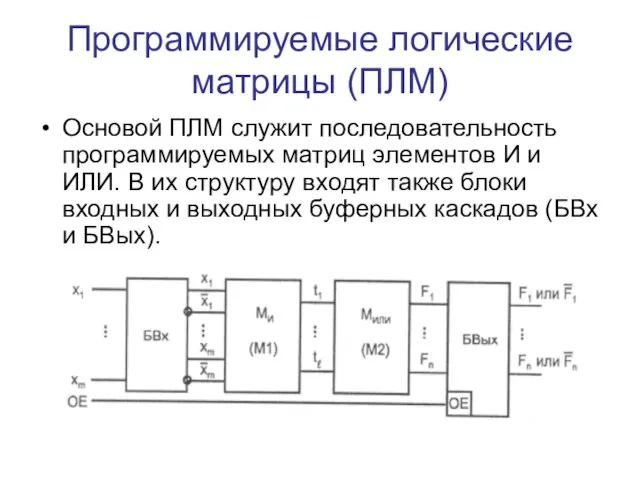

- 4. Программируемые логические матрицы (ПЛМ) Основой ПЛМ служит последовательность программируемых матриц элементов И и ИЛИ. В их

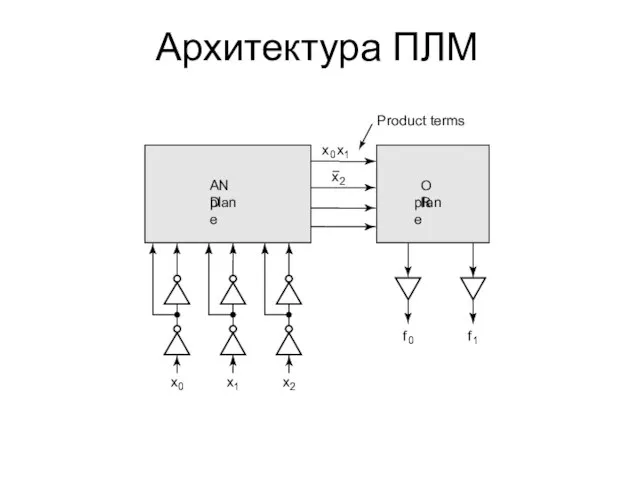

- 5. Архитектура ПЛМ

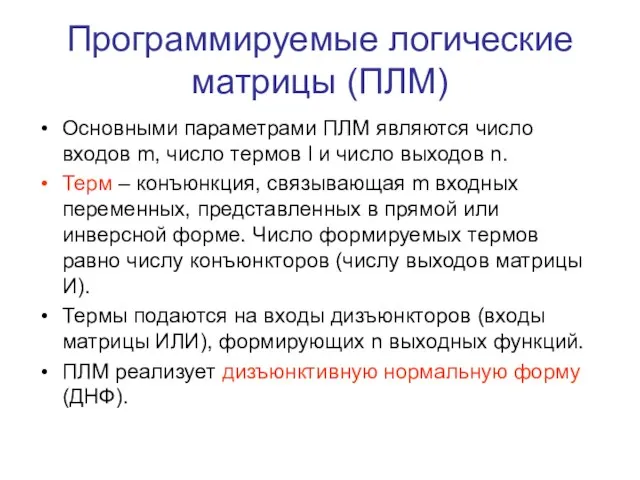

- 6. Программируемые логические матрицы (ПЛМ) Основными параметрами ПЛМ являются число входов m, число термов l и число

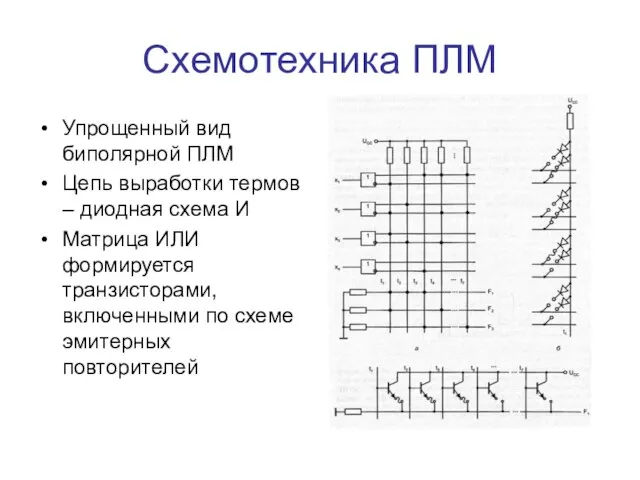

- 7. Схемотехника ПЛМ Упрощенный вид биполярной ПЛМ Цепь выработки термов – диодная схема И Матрица ИЛИ формируется

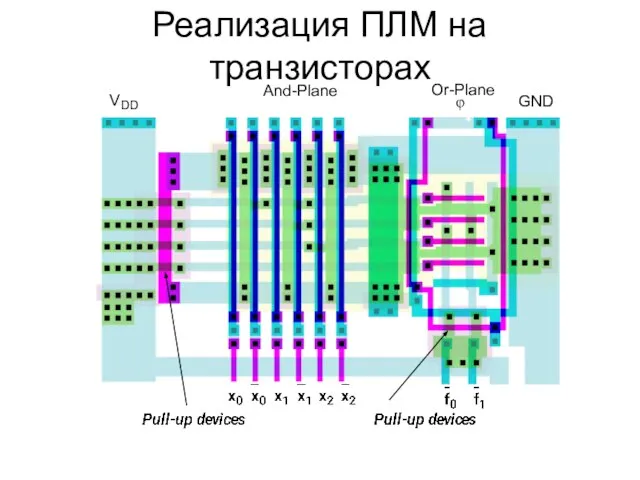

- 8. Реализация ПЛМ на транзисторах

- 9. Способы реализации ПЛМ ПЗУ ПМЛ O 1 O 2 O 3 Programmable AND array Programmable OR

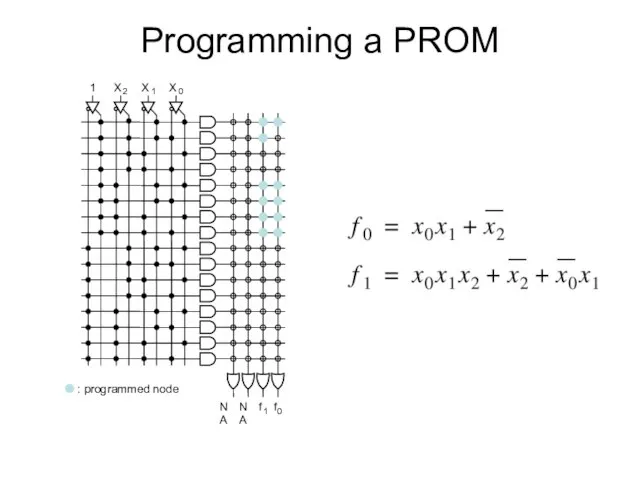

- 10. Programming a PROM

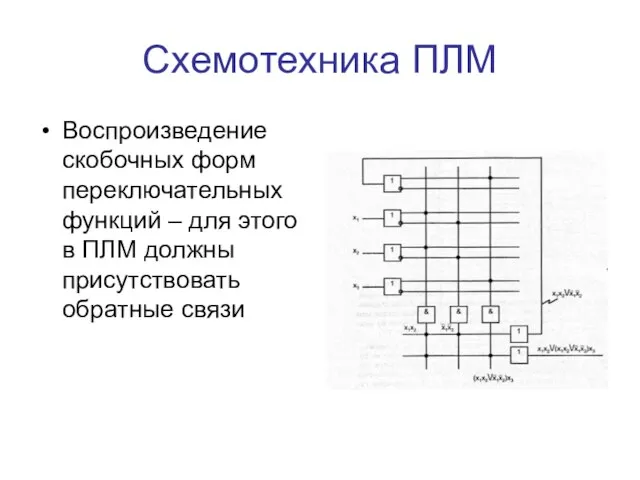

- 11. Схемотехника ПЛМ Воспроизведение скобочных форм переключательных функций – для этого в ПЛМ должны присутствовать обратные связи

- 12. Схемотехника ПЛМ Для формирования прямого или инверсного выходного сигнала используются сумматоры по модулю 2

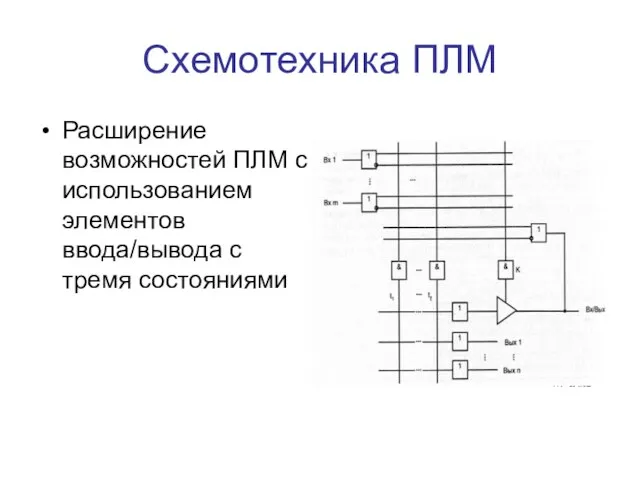

- 13. Схемотехника ПЛМ Расширение возможностей ПЛМ с использованием элементов ввода/вывода с тремя состояниями

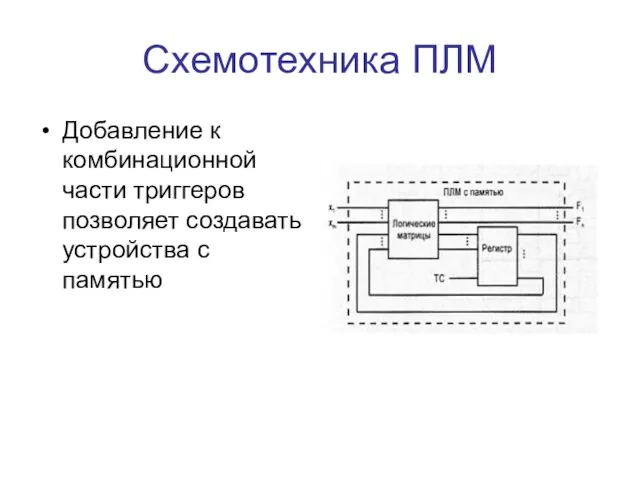

- 14. Схемотехника ПЛМ Добавление к комбинационной части триггеров позволяет создавать устройства с памятью

- 15. Обобщенная структура классической ПЛМ

- 16. Дальнейшее развитие ПЛМ Недостаток классических ПЛМ – фиксированная настройка выходных макроячеек. Совершенствование архитектуры выходных макроячеек привело

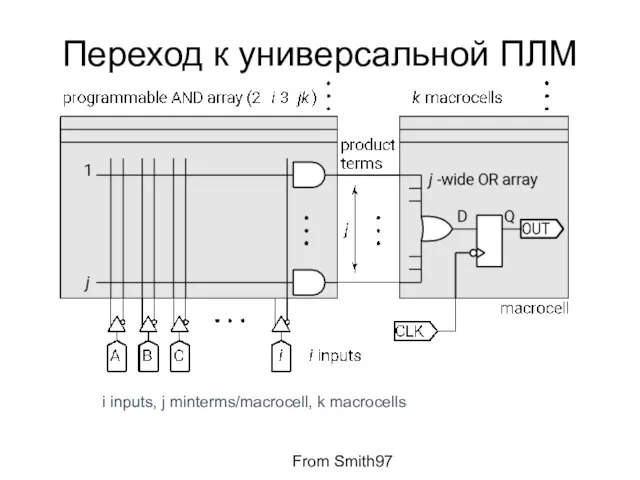

- 17. Переход к универсальной ПЛМ From Smith97 i inputs, j minterms/macrocell, k macrocells

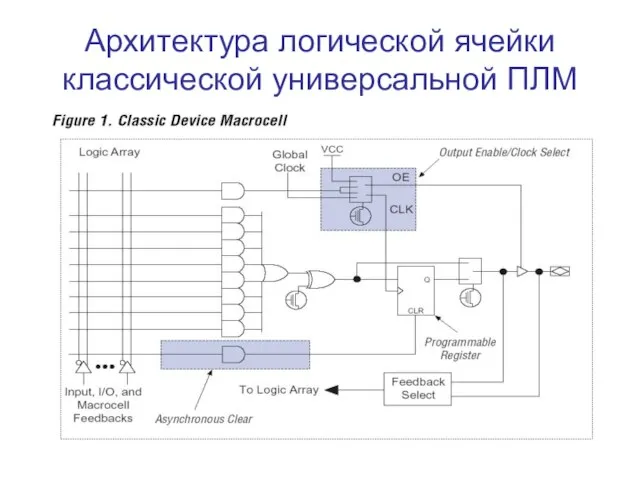

- 18. Архитектура логической ячейки классической универсальной ПЛМ

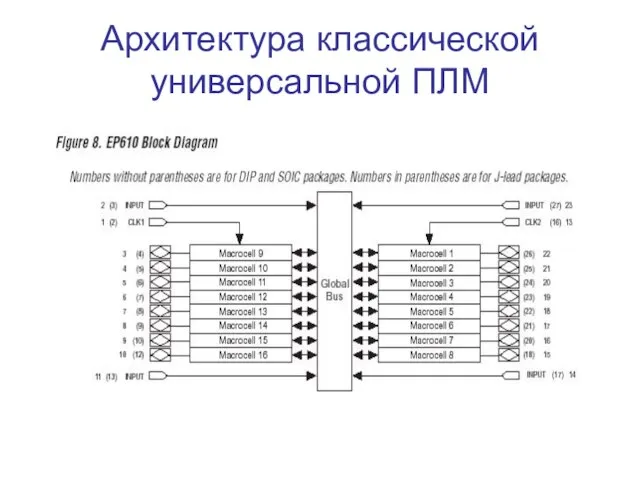

- 19. Архитектура классической универсальной ПЛМ

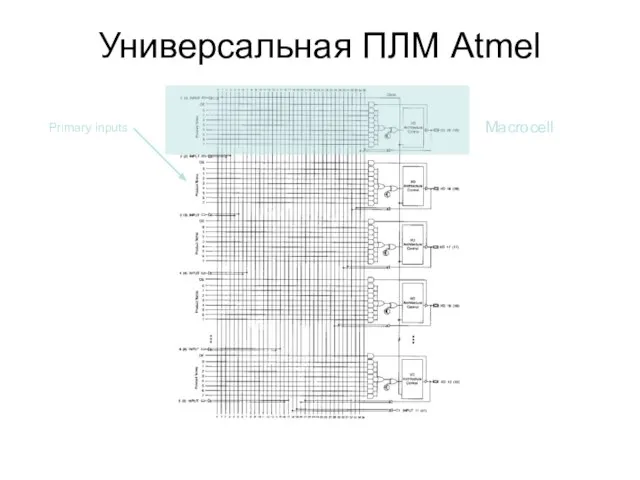

- 20. Универсальная ПЛМ Atmel Macrocell Primary inputs

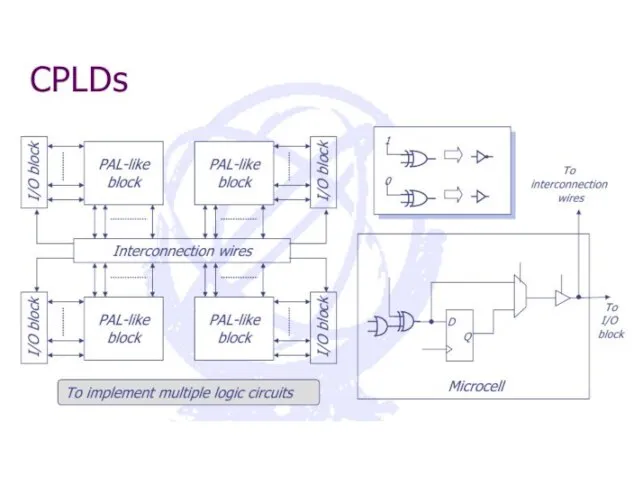

- 21. Сложные программируемые логические интегральные схемы (CPLD) СПЛИС (CPLD ) являются дальнейшим развитием структур ПЛМ Архитектурно CPLD

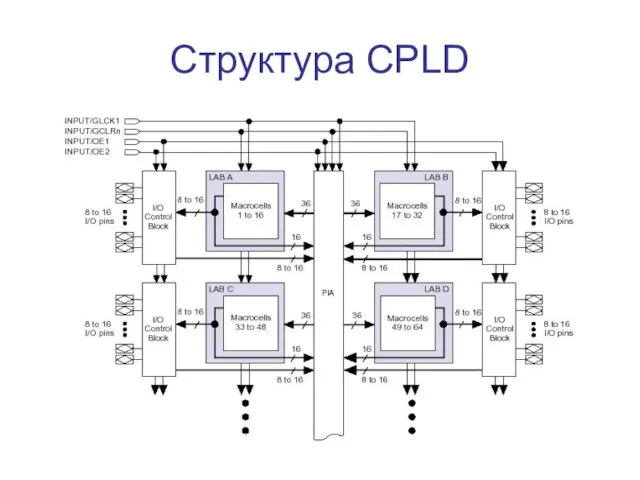

- 22. Структура CPLD

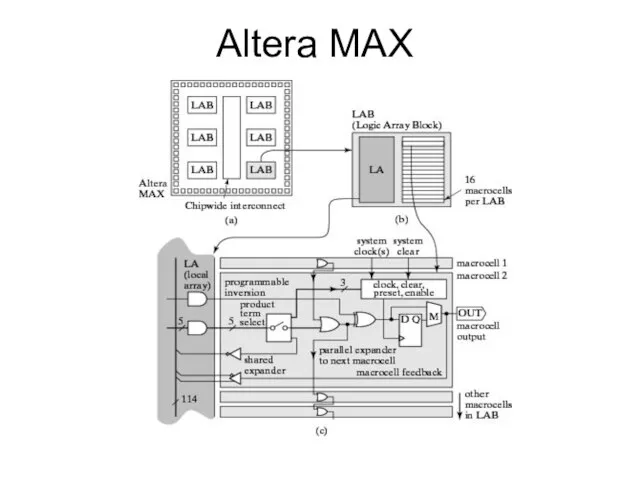

- 23. Altera MAX

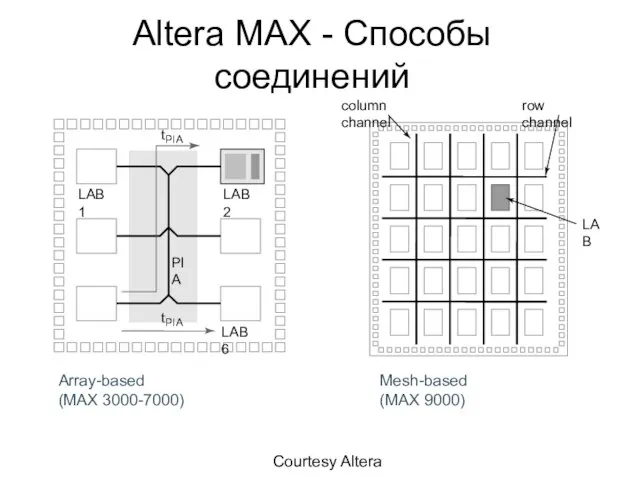

- 24. Altera MAX - Способы соединений row channel column channel LAB Courtesy Altera Array-based (MAX 3000-7000) Mesh-based

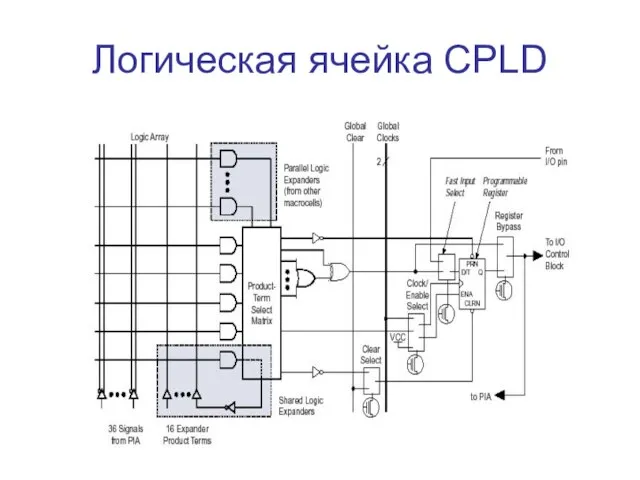

- 25. Логическая ячейка CPLD

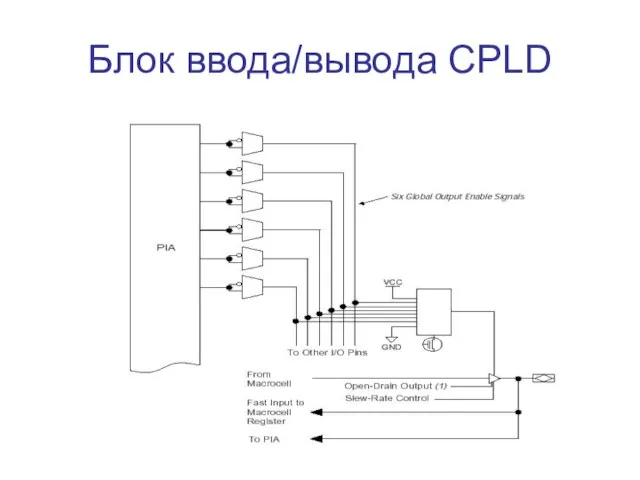

- 26. Блок ввода/вывода CPLD

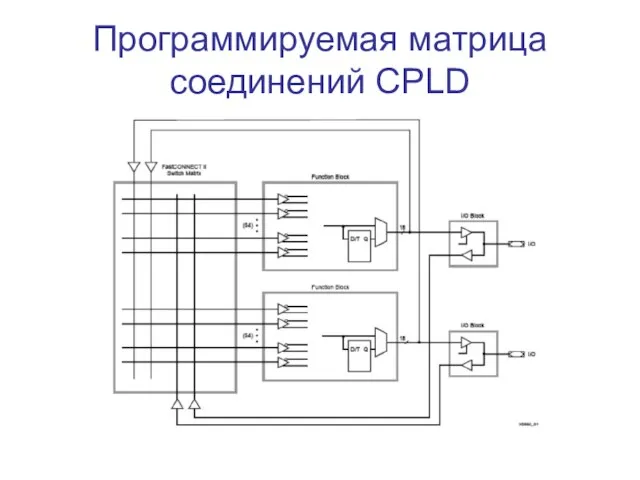

- 27. Программируемая матрица соединений CPLD

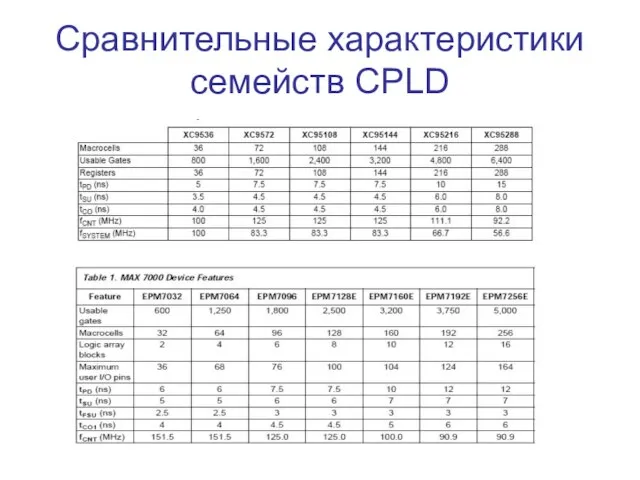

- 28. Сравнительные характеристики семейств CPLD

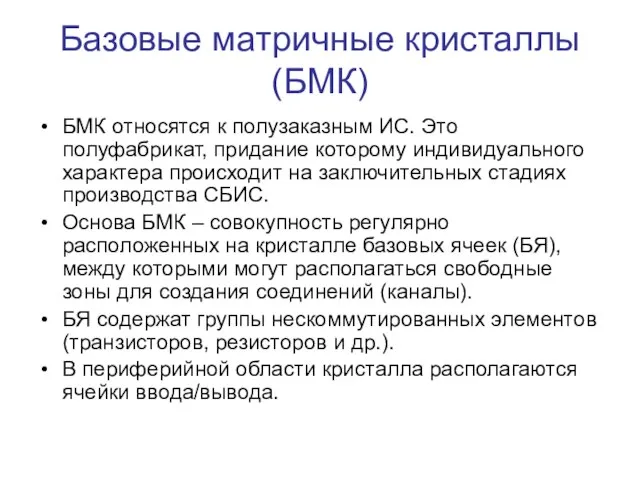

- 30. Базовые матричные кристаллы (БМК) БМК относятся к полузаказным ИС. Это полуфабрикат, придание которому индивидуального характера происходит

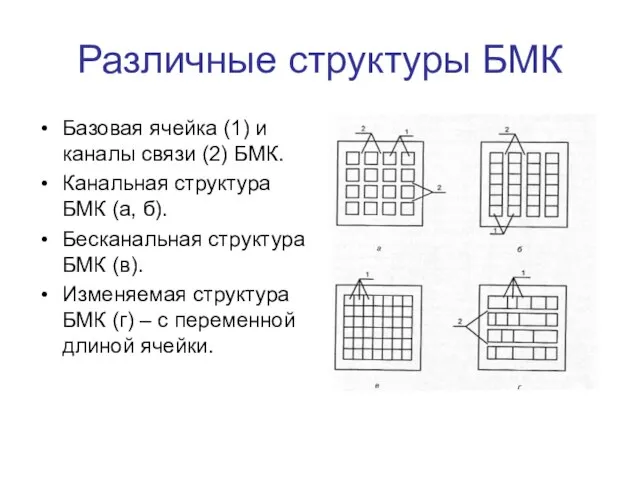

- 31. Различные структуры БМК Базовая ячейка (1) и каналы связи (2) БМК. Канальная структура БМК (а, б).

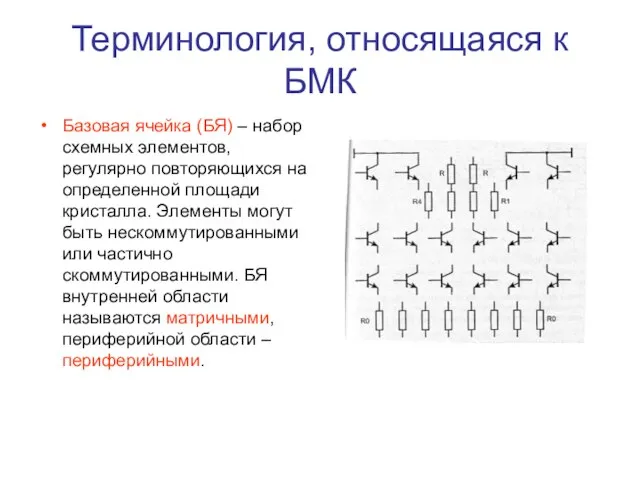

- 32. Терминология, относящаяся к БМК Базовая ячейка (БЯ) – набор схемных элементов, регулярно повторяющихся на определенной площади

- 33. Терминология, относящаяся к БМК Способы организации ячеек БМК: - Из элементов МБЯ может быть сформирован один

- 34. Терминология, относящаяся к БМК Библиотека функциональных ячеек – совокупность ФЯ, используемых при проектировании БИС. Создается на

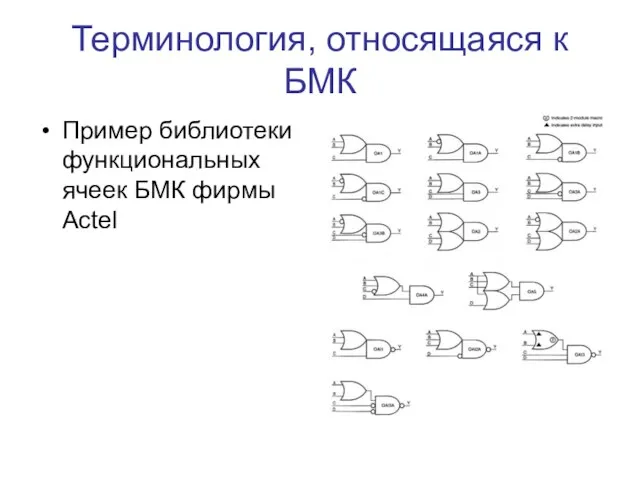

- 35. Терминология, относящаяся к БМК Пример библиотеки функциональных ячеек БМК фирмы Actel

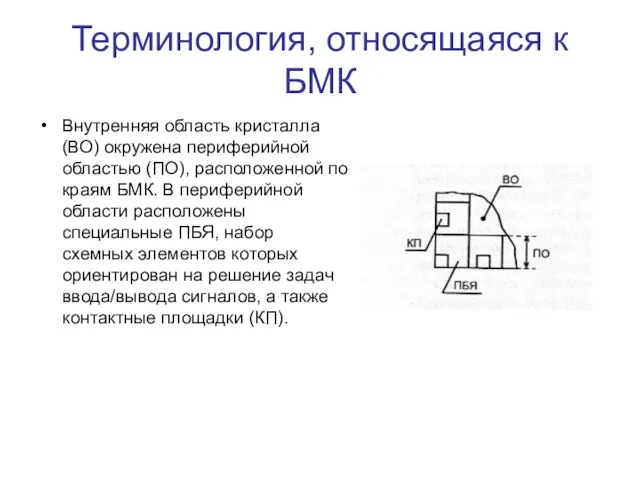

- 36. Терминология, относящаяся к БМК Внутренняя область кристалла (ВО) окружена периферийной областью (ПО), расположенной по краям БМК.

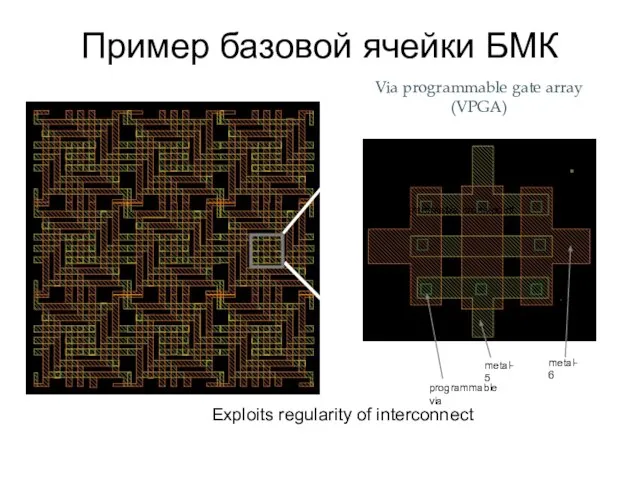

- 37. Пример базовой ячейки БМК metal-5 metal-6 Via-programmable cross-point programmable via Via programmable gate array (VPGA) Exploits

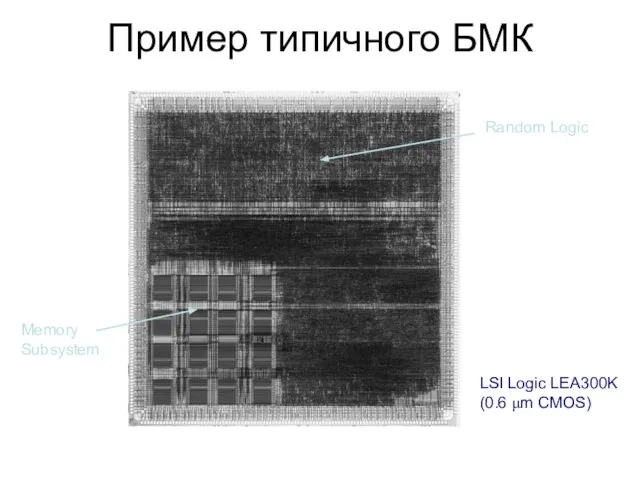

- 38. Пример типичного БМК Random Logic Memory Subsystem LSI Logic LEA300K (0.6 μm CMOS)

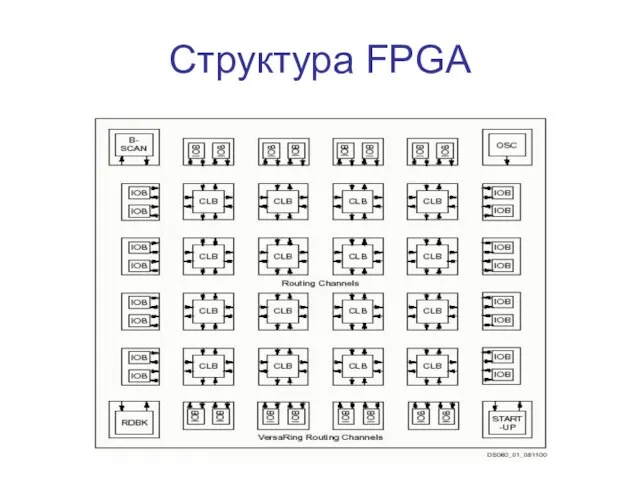

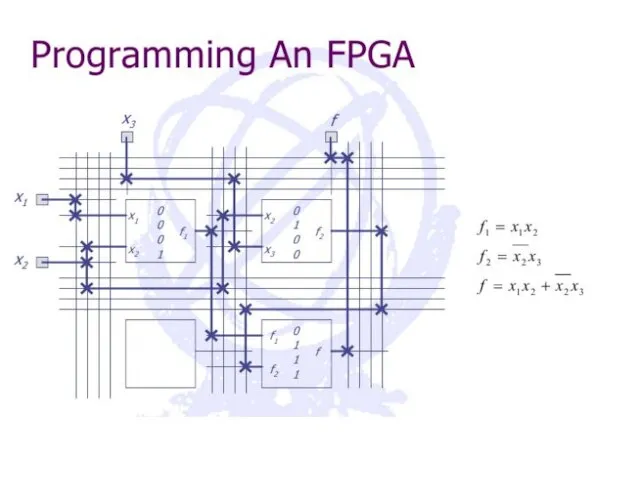

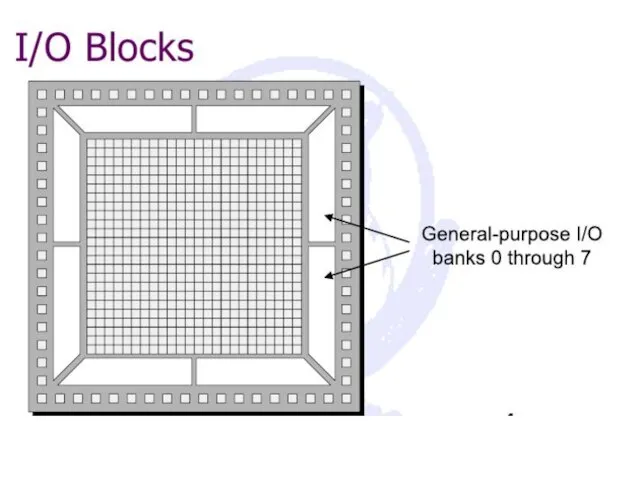

- 39. Программируемые пользователем вентильные матрицы (FPGA) Топологически сходны с канальными БМК Во внутренней области размещается множество регулярно

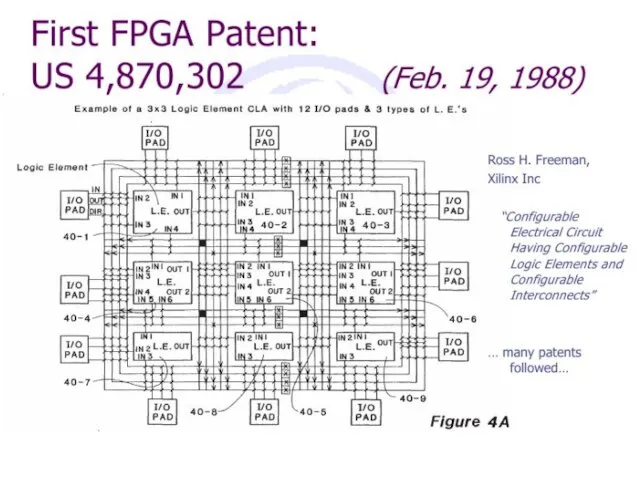

- 41. Структура FPGA

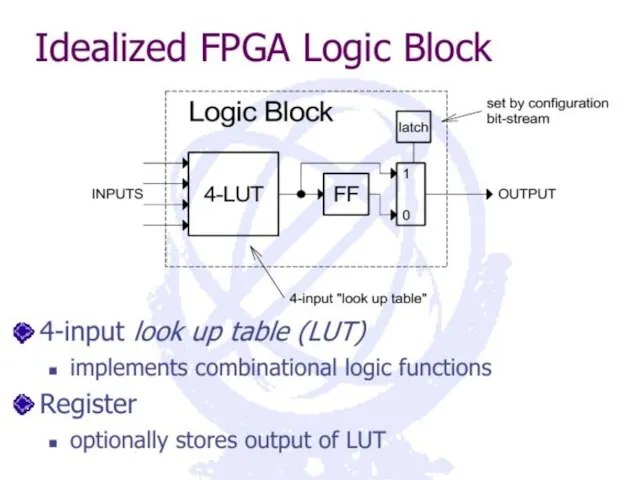

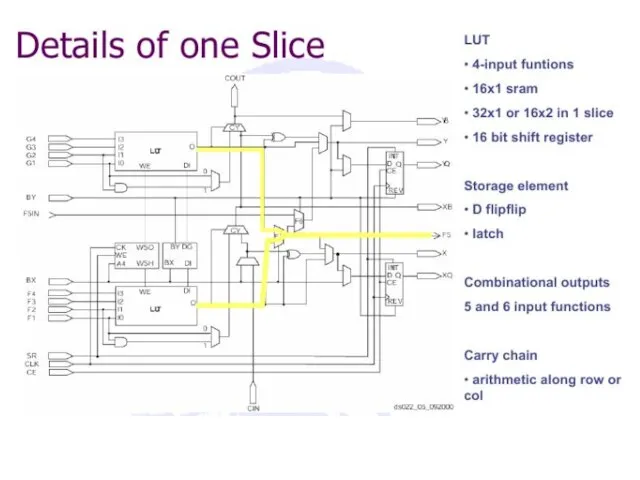

- 42. Структура логического блока FPGA Свойства и возможности FPGA зависят в первую очередь от характера их КЛБ

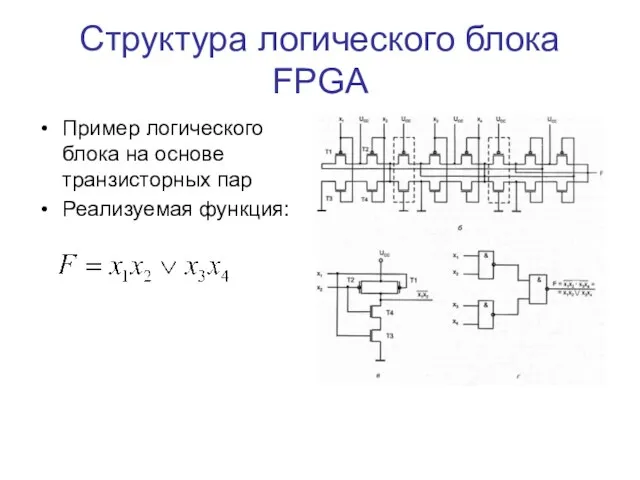

- 43. Структура логического блока FPGA Пример логического блока на основе транзисторных пар Реализуемая функция:

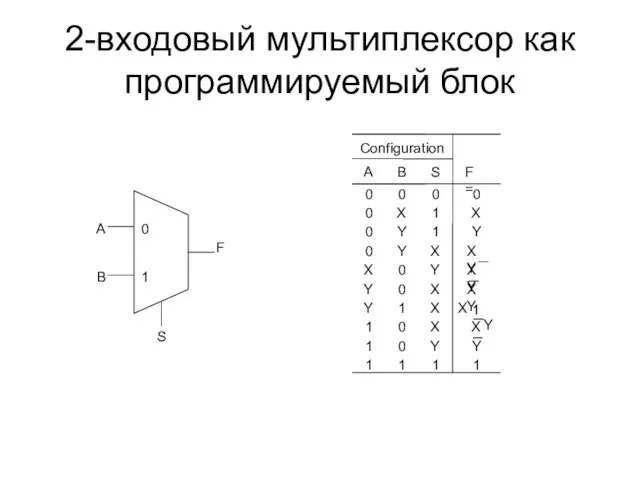

- 44. 2-входовый мультиплексор как программируемый блок F A 0 B S 1

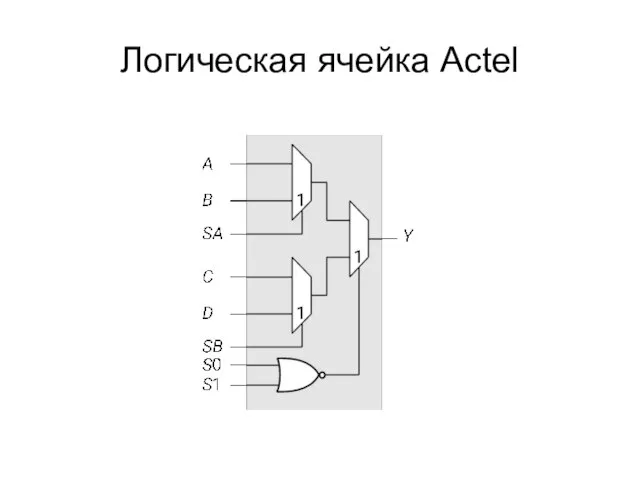

- 45. Логическая ячейка Actel

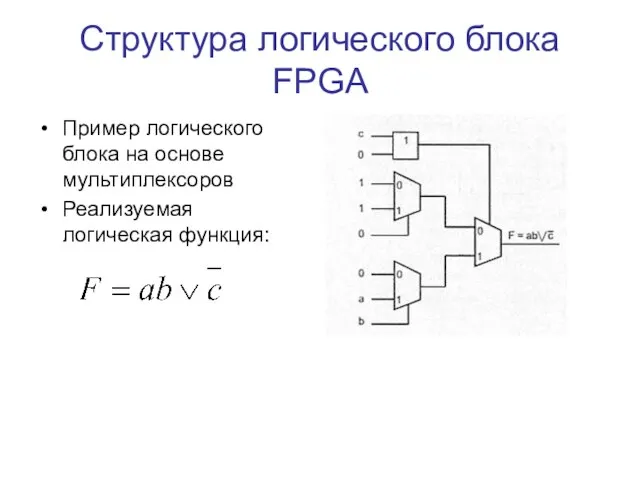

- 46. Структура логического блока FPGA Пример логического блока на основе мультиплексоров Реализуемая логическая функция:

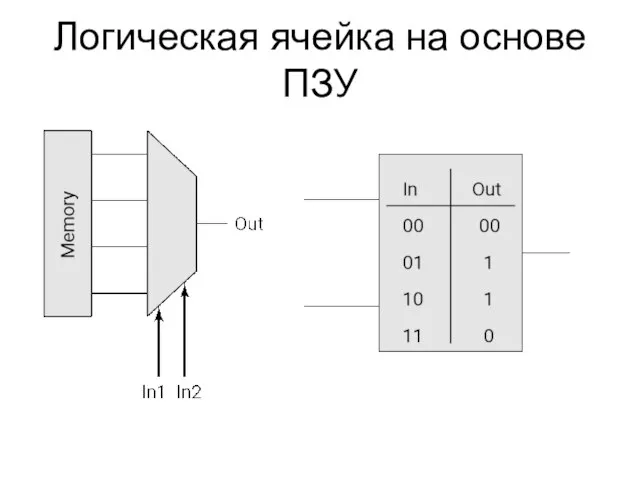

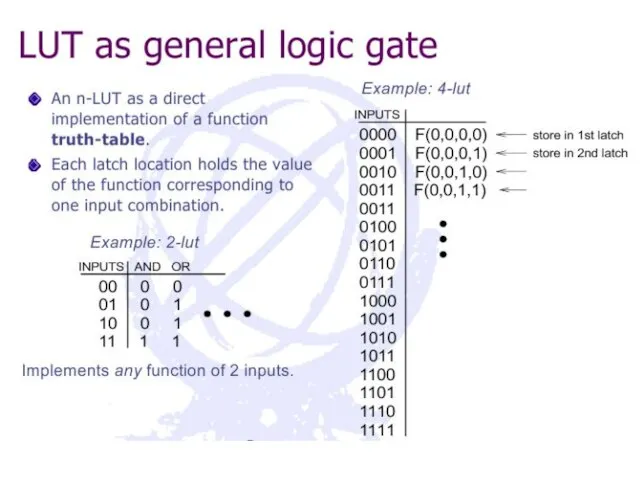

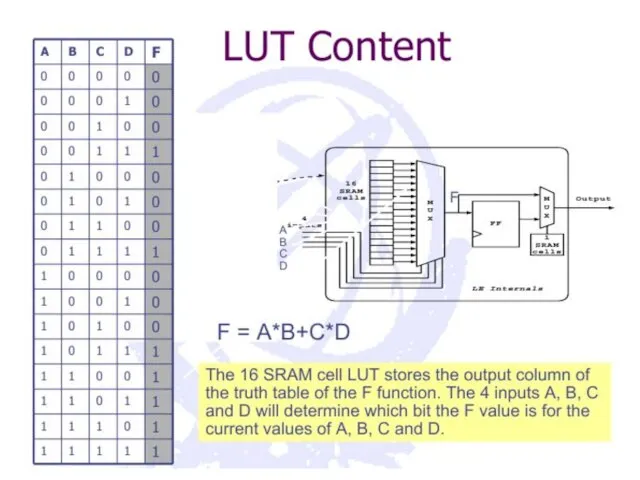

- 47. Логическая ячейка на основе ПЗУ

- 52. Структура логического блока FPGA на основе ПЗУ

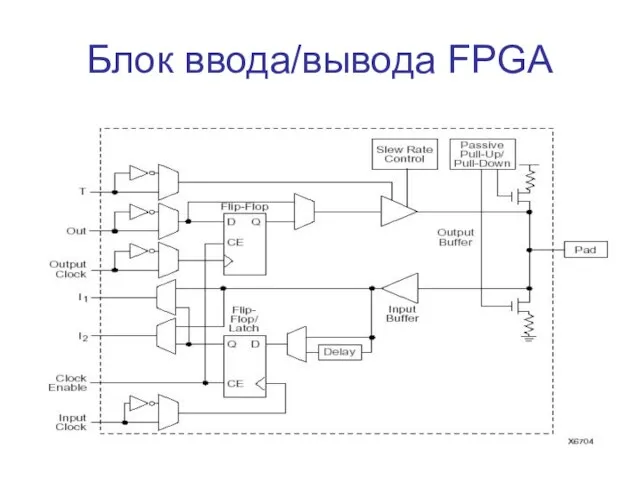

- 55. Блок ввода/вывода FPGA

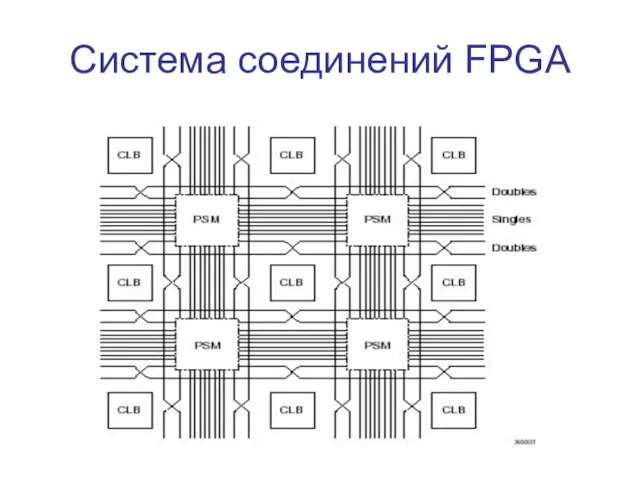

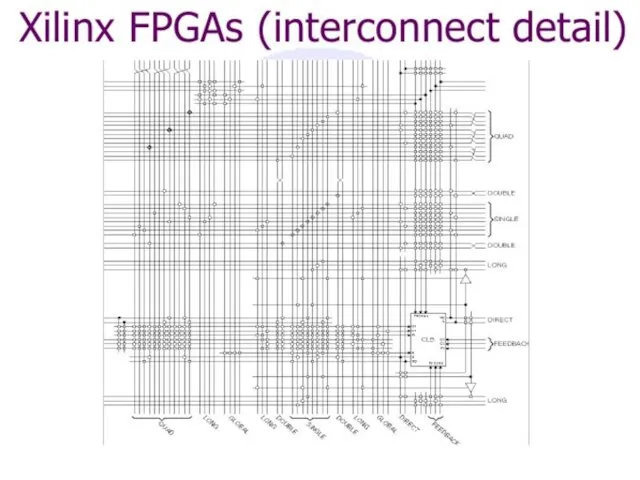

- 56. Система соединений FPGA

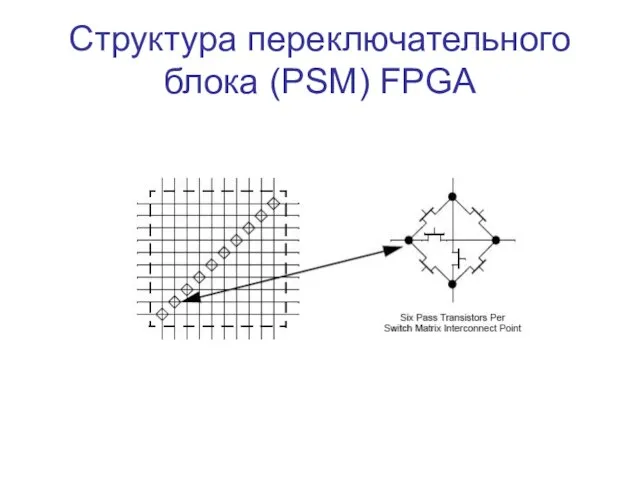

- 57. Структура переключательного блока (PSM) FPGA

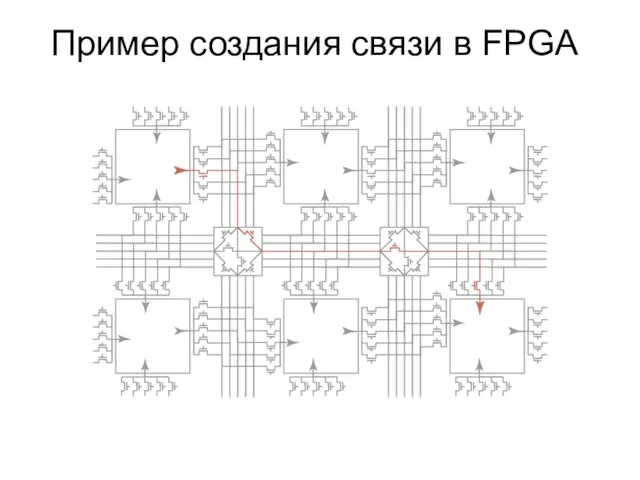

- 58. Пример создания связи в FPGA

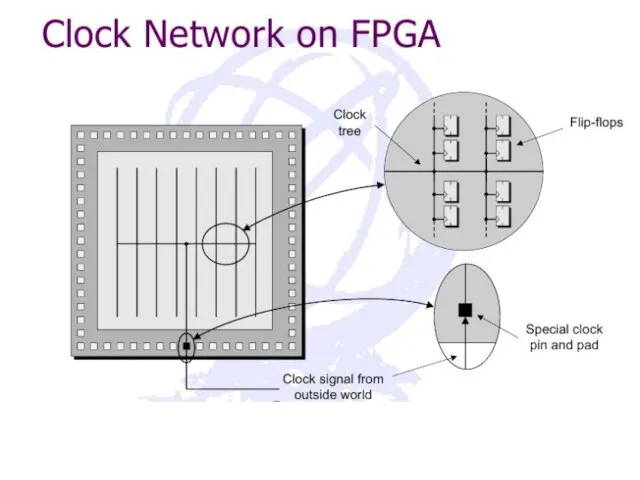

- 64. Дополнительные блоки FPGA Встроенные блоки памяти (небольшого объема) – 16х1 или 32х1 бит

- 65. Дополнительные блоки FPGA Блок интерфейса граничного сканирования (JTAG) – для отладки и конфигурирования FPGA

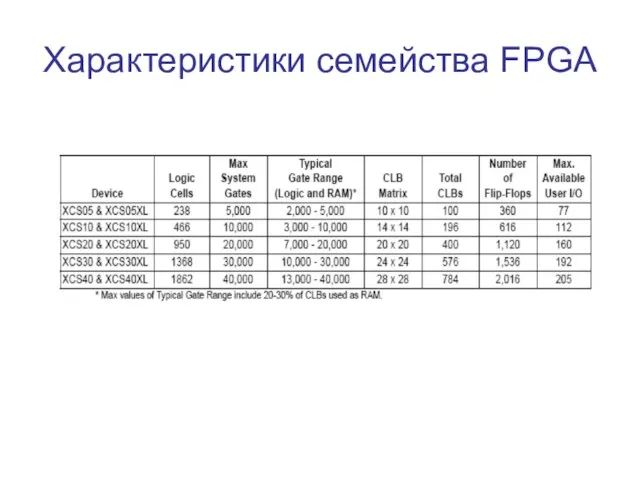

- 67. Характеристики семейства FPGA Микросхемы FPGA построены по SRAM-технологии и требуют загрузки управляющей (конфигурационной) программы либо из

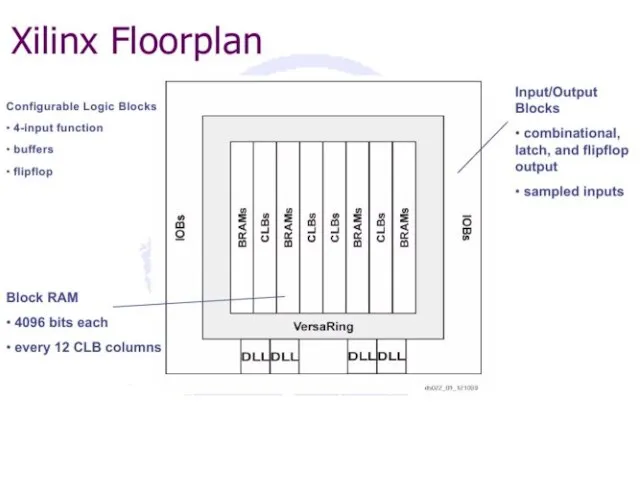

- 68. Пример кристалла FPGA Xilinx XC4000ex

- 71. Характеристики семейства FPGA

- 72. Системы на кристалле (SoC) Предпосылки появления «Систем на Кристалле» (System-on-Chip): - уменьшение топологических норм проектирования; -

- 73. Пример системы на кристалле

- 74. Системы на кристалле (SoC) Архитектурные особенности SoC: - наличие универсальных программируемых блоков, позволяющих реализовать любое устройство

- 75. Системы на кристалле (SoC) К специализированным ядрам относятся: - блоки ОЗУ с возможностью изменения организации памяти,

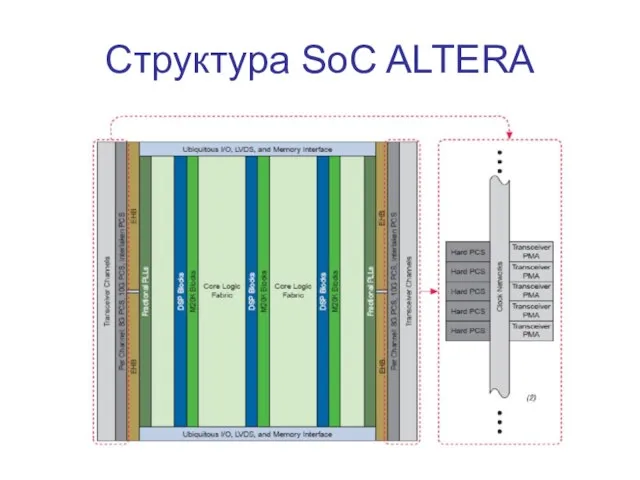

- 76. Структура SoC ALTERA

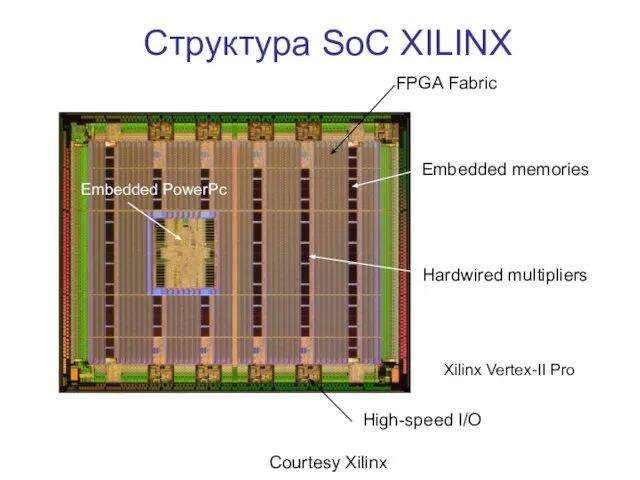

- 77. Структура SoC XILINX Xilinx Vertex-II Pro Courtesy Xilinx High-speed I/O Embedded PowerPc Embedded memories Hardwired multipliers

- 78. Логическая ячейка SoC

- 79. Режимы настройки логической ячейки

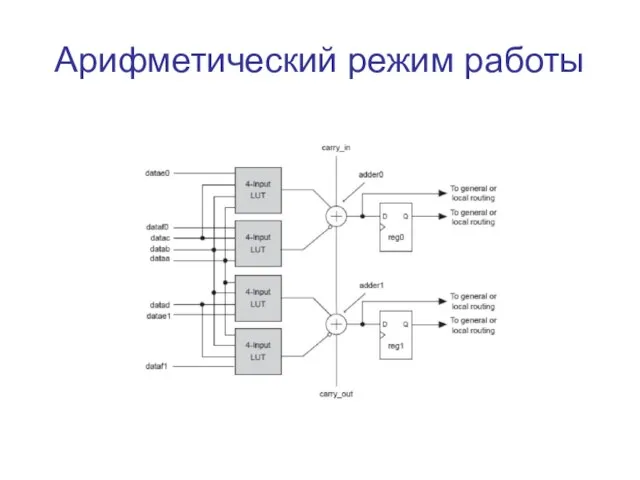

- 80. Арифметический режим работы

- 81. Организация регистровой цепочки

- 82. Объединение логических ячеек в логический блок

- 83. Блок памяти SoC

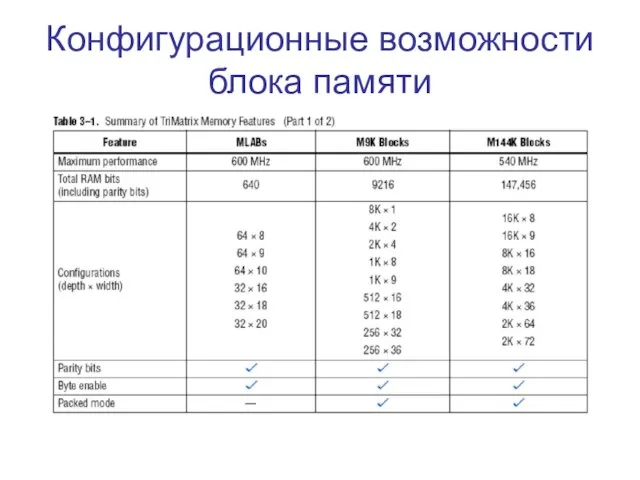

- 84. Конфигурационные возможности блока памяти

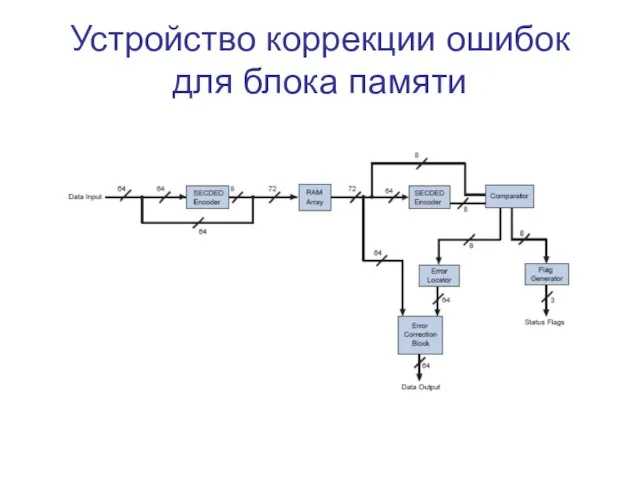

- 85. Устройство коррекции ошибок для блока памяти

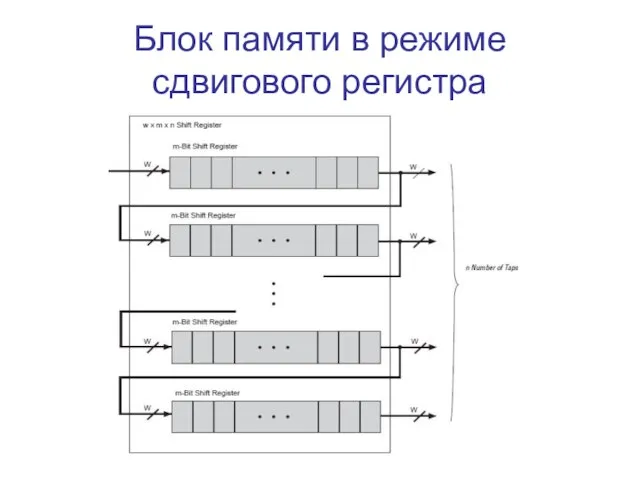

- 86. Блок памяти в режиме сдвигового регистра

- 87. Арифметический блок SoC

- 88. Архитектурные особенности арифметического блока

- 89. Последовательная загрузка данных в арифметическом блоке

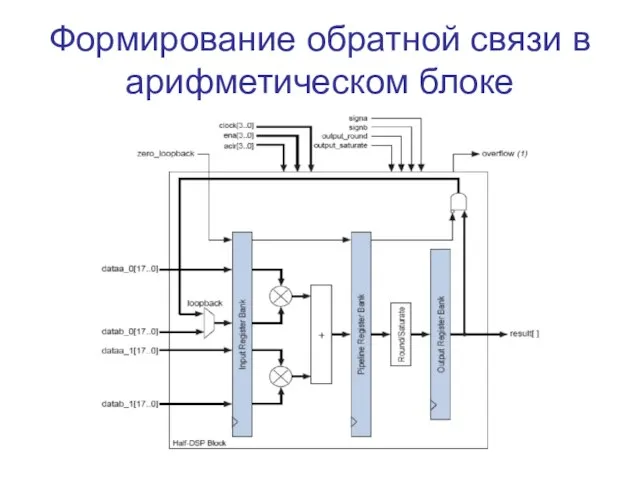

- 90. Формирование обратной связи в арифметическом блоке

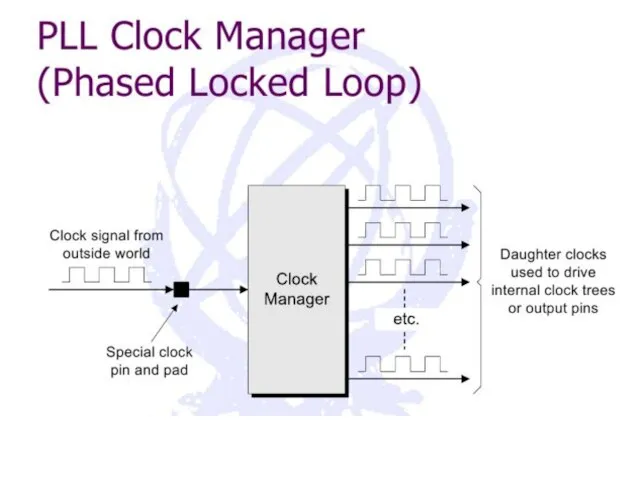

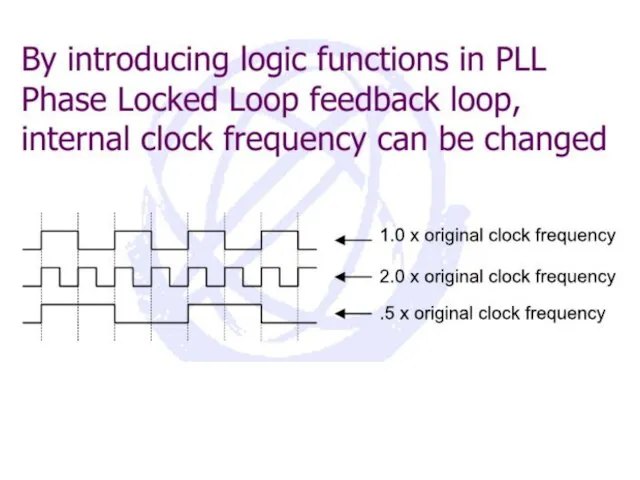

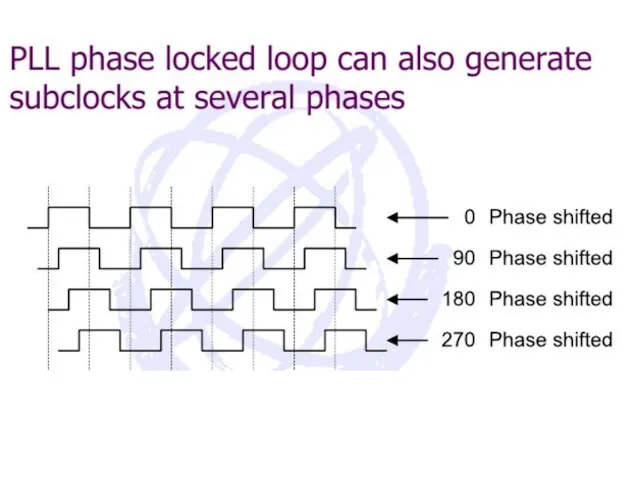

- 91. Блок управления тактовыми сигналами SoC

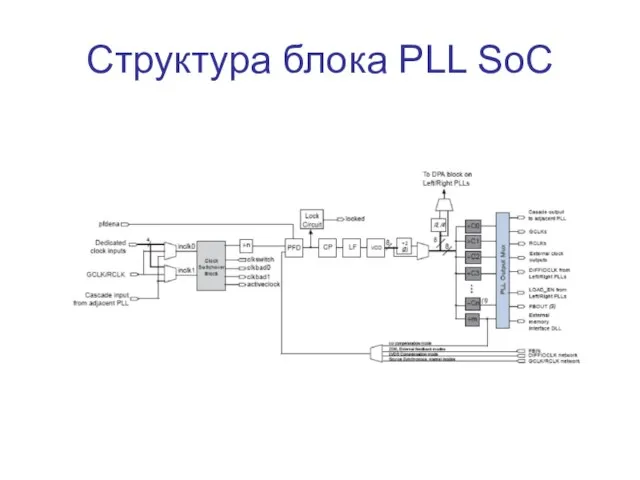

- 92. Структура блока PLL SoC

- 93. Блок ввода\вывода SoC

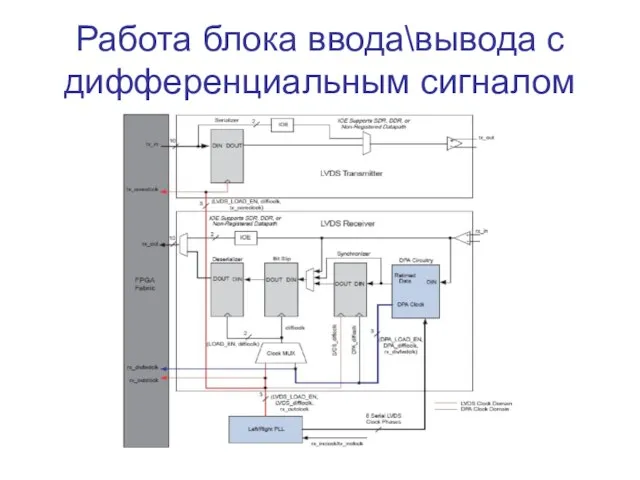

- 94. Работа блока ввода\вывода с дифференциальным сигналом

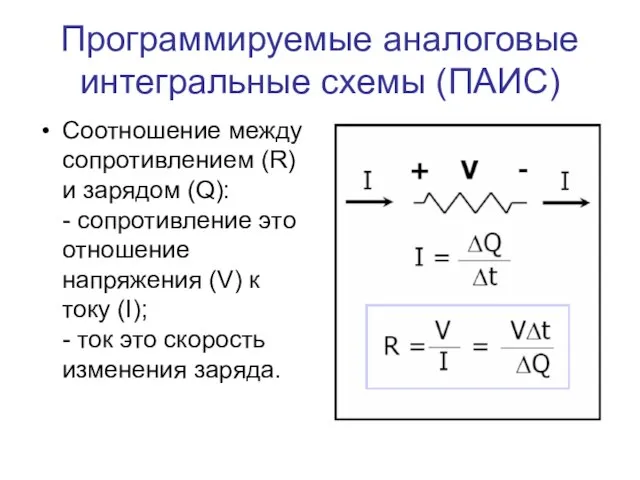

- 95. Программируемые аналоговые интегральные схемы (ПАИС) Соотношение между сопротивлением (R) и зарядом (Q): - сопротивление это отношение

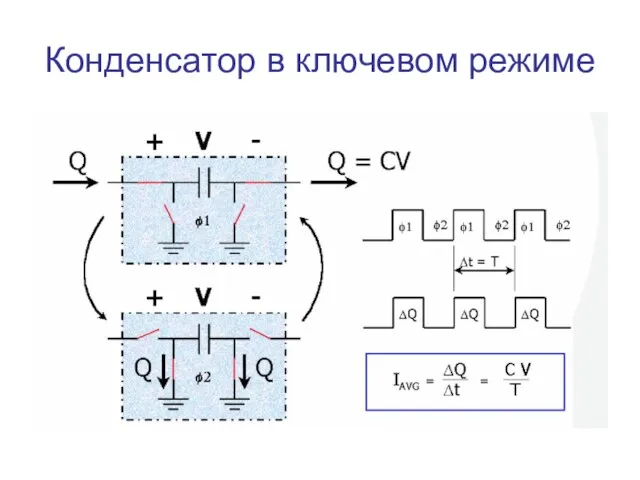

- 96. Конденсатор в ключевом режиме

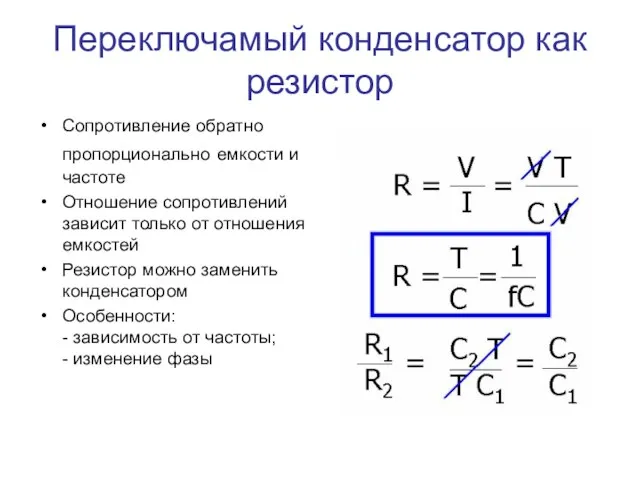

- 97. Переключамый конденсатор как резистор Сопротивление обратно пропорционально емкости и частоте Отношение сопротивлений зависит только от отношения

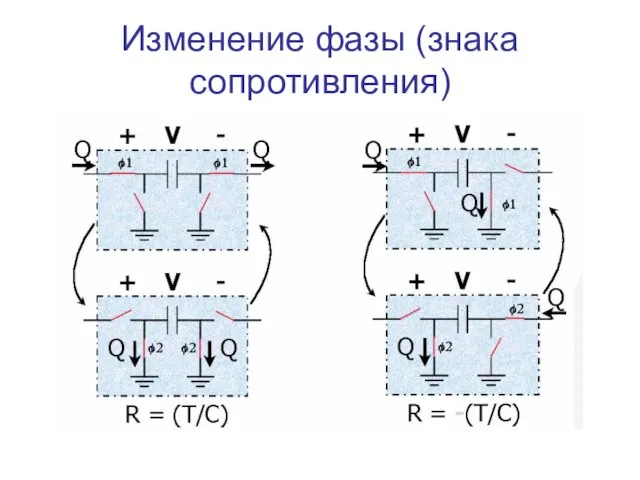

- 98. Изменение фазы (знака сопротивления)

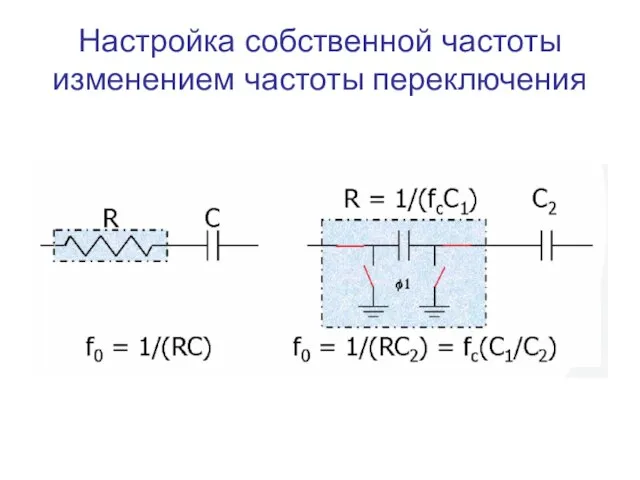

- 99. Настройка собственной частоты изменением частоты переключения

- 100. Дискретизация входного сигнала Входной и выходной сигналы обрабатываются в разные моменты времени Удобно для создания устройств

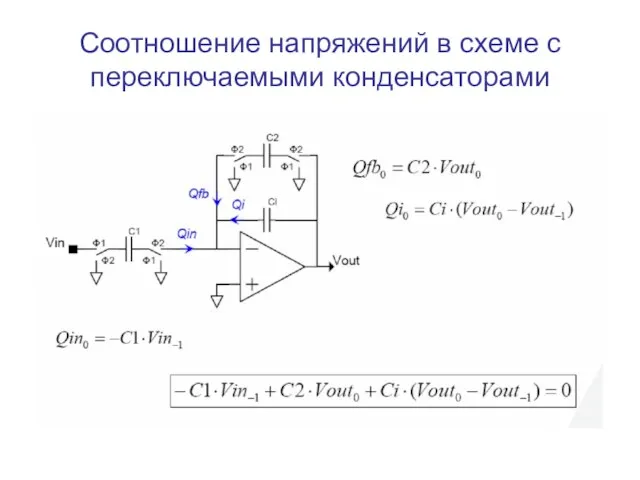

- 101. Соотношение напряжений в схеме с переключаемыми конденсаторами

- 102. Переключаемые конденсаторы – базовый элемент ПАИС Они позволяют реализовывать: - изменение коэффициента усиления операционных усилителей; -

- 103. Простые ПАИС Схема простой ПАИС ispPAC10 фирмы Lattice Semi Позволяет создавать различные усилители, интеграторы, простые фильтры

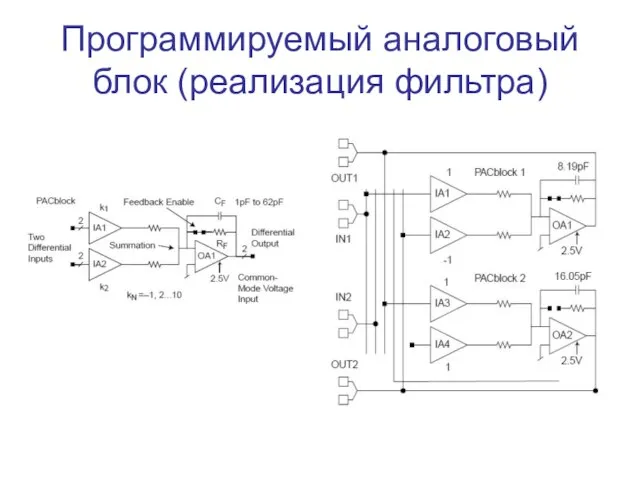

- 104. Программируемый аналоговый блок (реализация фильтра)

- 105. Простые ПАИС (ispPAC20)

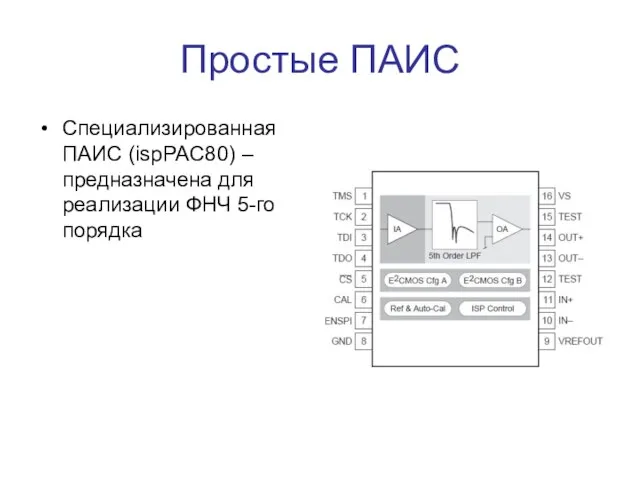

- 106. Простые ПАИС Специализированная ПАИС (ispPAC80) – предназначена для реализации ФНЧ 5-го порядка

- 107. Упрощенная схема ПАИС для реализации ФНЧ

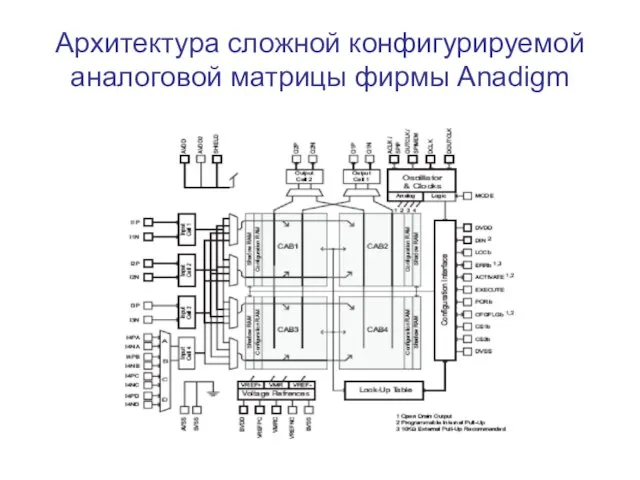

- 108. Архитектура сложной конфигурируемой аналоговой матрицы фирмы Anadigm

- 109. Структура входной ячейки

- 110. Структура выходной ячейки

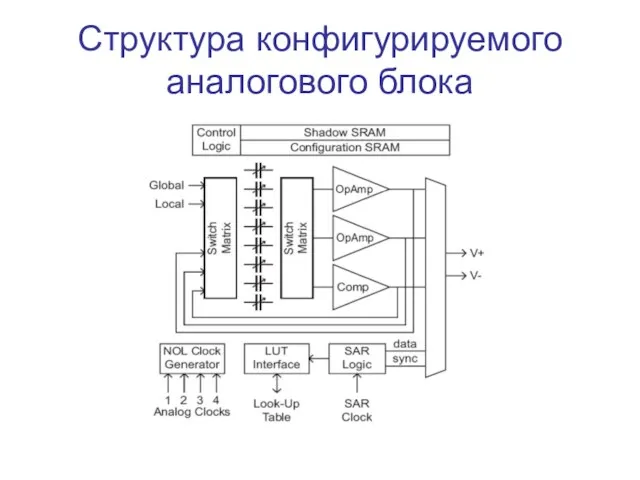

- 111. Структура конфигурируемого аналогового блока

- 112. Программируемые матрицы смешанной архитектуры В их состав обычно включают: - аппаратно реализованное процессорное ядро; - программируемые

- 113. Пример матрицы со смешанной архитектурой (PSoC5 фирмы Cypress)

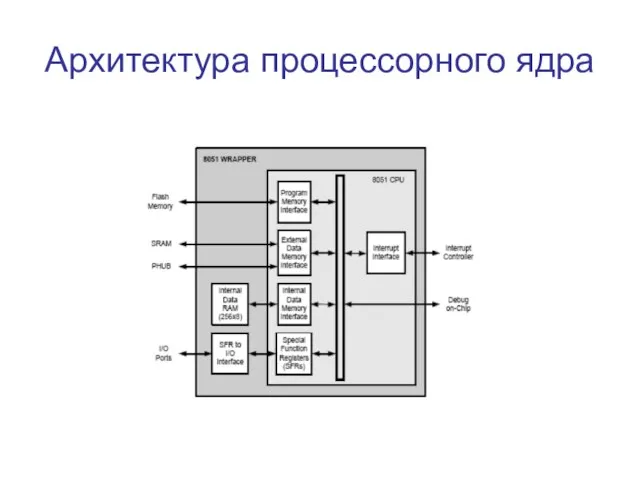

- 114. Архитектура процессорного ядра

- 115. Архитектура процессорного ядра

- 116. Встроенный блок ОЗУ

- 117. Блок интерфейса внешней памяти (EMIF)

- 118. Блок формирования тактовых частот

- 119. Сторожевой таймер

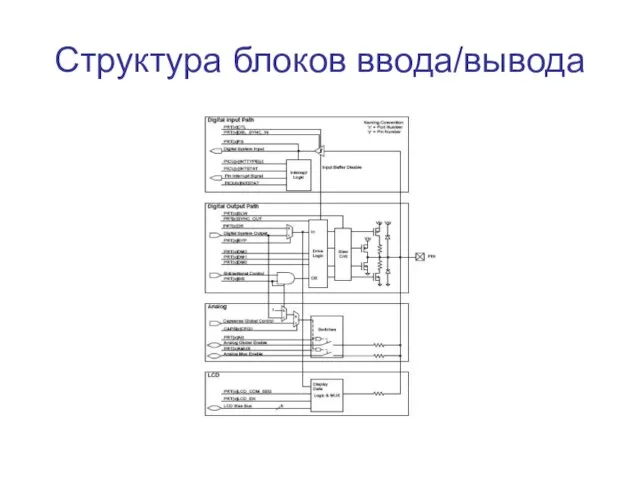

- 120. Структура блоков ввода/вывода

- 121. Массив программируемых цифровых блоков

- 122. Архитектура программируемого цифрового блока

- 123. Структура узла обработки данных

- 124. Пример настройки массива цифровых блоков

- 125. Встроенный контроллер шины CAN

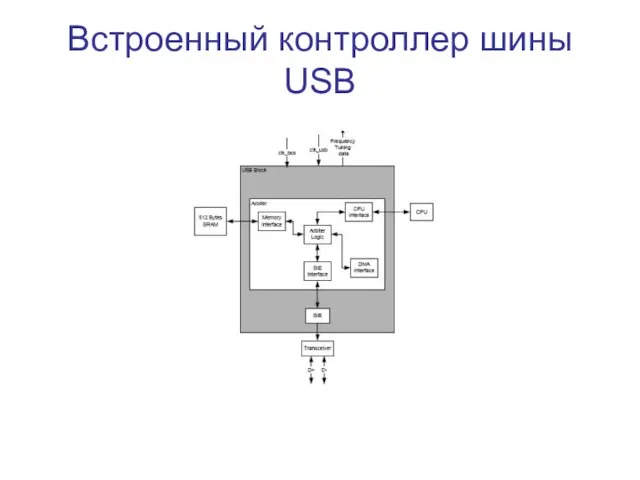

- 126. Встроенный контроллер шины USB

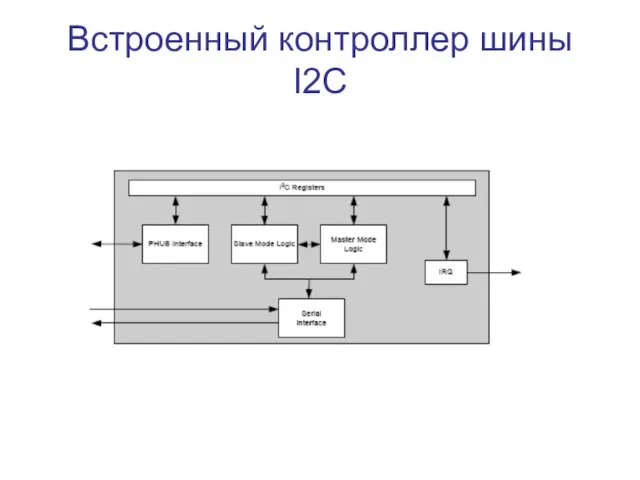

- 127. Встроенный контроллер шины I2C

- 128. Встроенный блок конфигурируемого таймера

- 129. Массив программируемых аналоговых блоков

- 130. Сигма-дельта АЦП и АЦП последовательного приближения

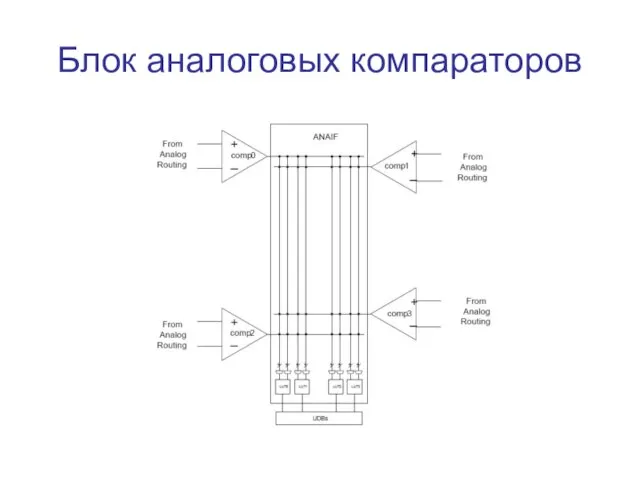

- 131. Блок аналоговых компараторов

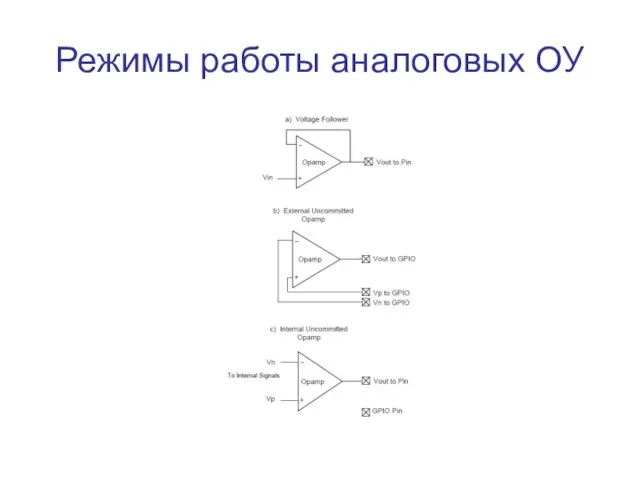

- 132. Режимы работы аналоговых ОУ

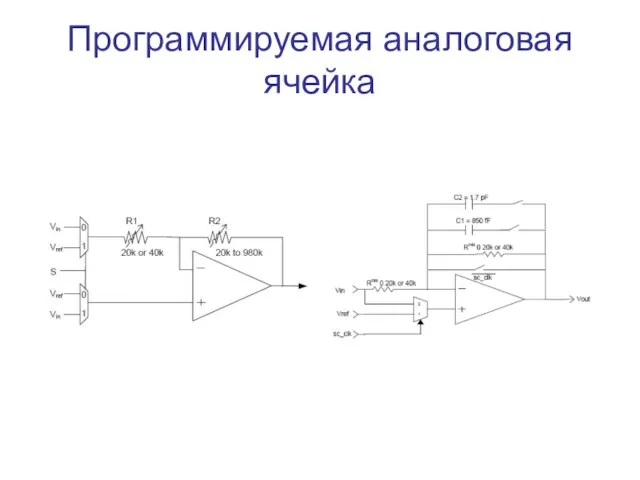

- 133. Программируемая аналоговая ячейка

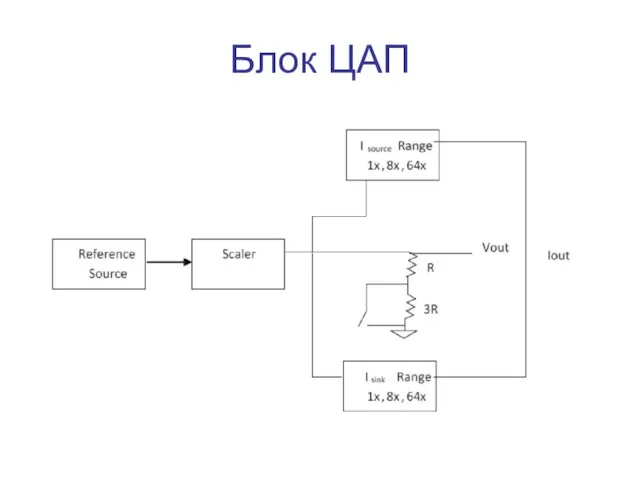

- 134. Блок ЦАП

- 136. Скачать презентацию

Конструктивный состав системы ЧПК

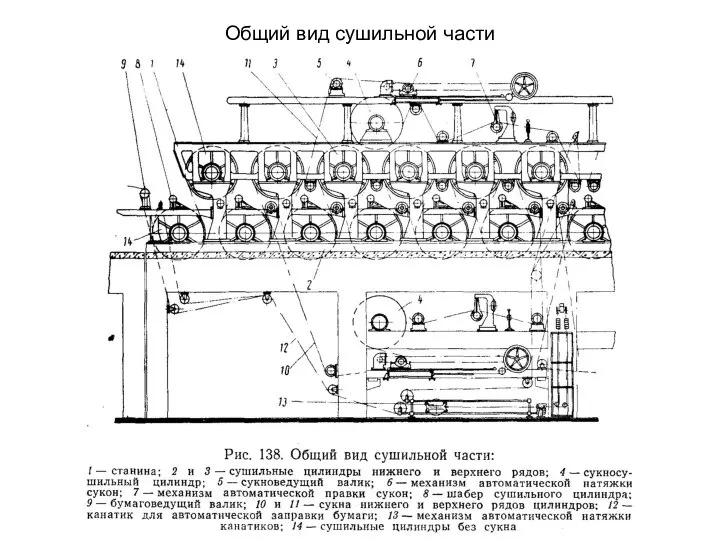

Конструктивный состав системы ЧПК Сушильная часть

Сушильная часть 20130413_vladimir_vysockiy

20130413_vladimir_vysockiy Полупроводниковый диод

Полупроводниковый диод Аннонс фрилансер

Аннонс фрилансер Бейджики 1-Б

Бейджики 1-Б Назначение и характеристика маневров (лекция 2)

Назначение и характеристика маневров (лекция 2) Starbucks

Starbucks Термины и определения

Термины и определения времена года

времена года Чарльз Дарвин

Чарльз Дарвин Theatre

Theatre Основи побудови та моделі каналів електрозв’язку

Основи побудови та моделі каналів електрозв’язку Технологический процесс и его элементы

Технологический процесс и его элементы Повторяем изученные части речи

Повторяем изученные части речи Самооценка и уровень притязаний личности

Самооценка и уровень притязаний личности Карарга анализ

Карарга анализ Линейная часть магистральных нефтепроводов

Линейная часть магистральных нефтепроводов Технотекстиль!

Технотекстиль! Узагальнення вивченого про складне речення з різними видами зв’язку

Узагальнення вивченого про складне речення з різними видами зв’язку фантастическое дерево

фантастическое дерево 20130224_vospitatelnyy_aspekt

20130224_vospitatelnyy_aspekt Интерактивный робот-помощник

Интерактивный робот-помощник Толерантность

Толерантность В мире профессий

В мире профессий (2)

(2) Презентация1

Презентация1 Быть здоровым - значит быть счастливым

Быть здоровым - значит быть счастливым