Слайд 12

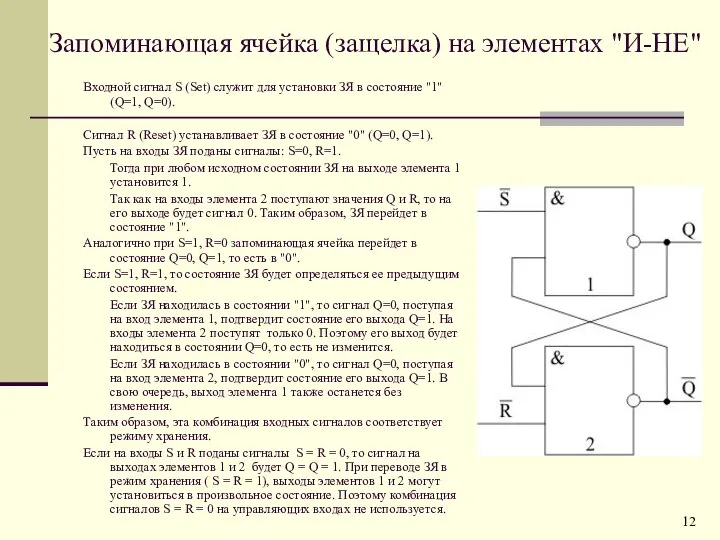

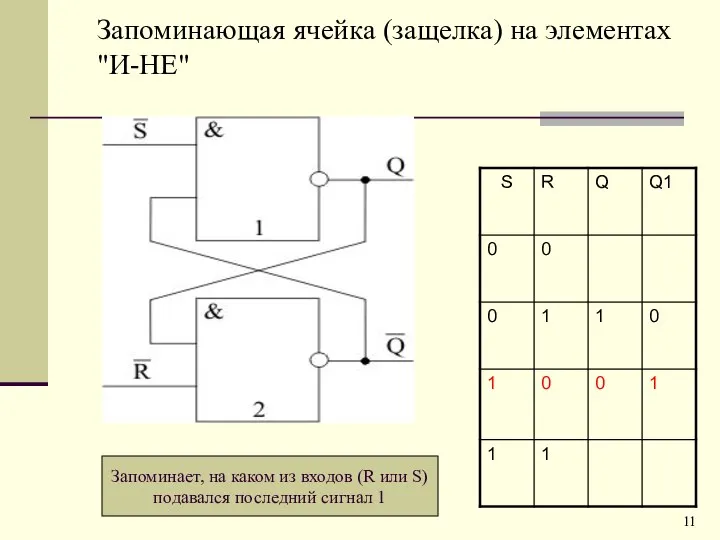

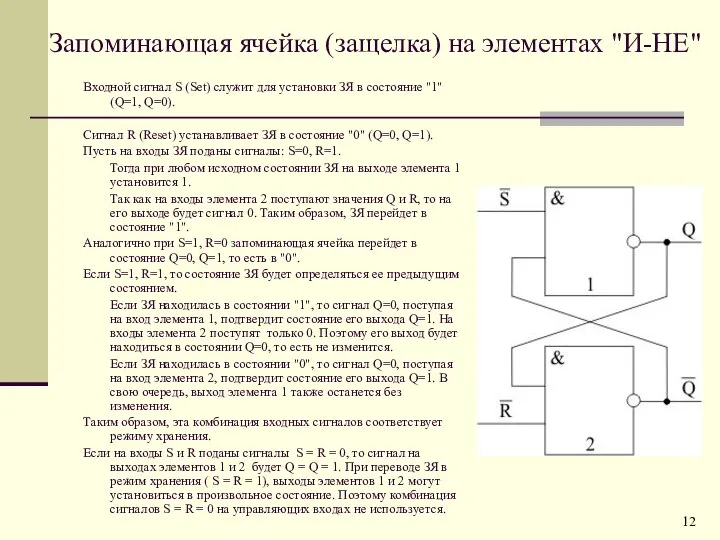

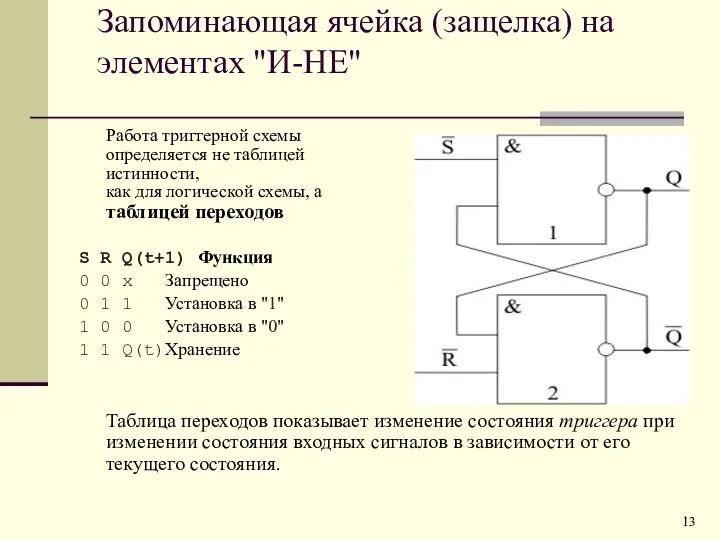

Запоминающая ячейка (защелка) на элементах "И-НЕ"

Входной сигнал S (Set) служит для

установки ЗЯ в состояние "1" (Q=1, Q=0).

Сигнал R (Reset) устанавливает ЗЯ в состояние "0" (Q=0, Q=1).

Пусть на входы ЗЯ поданы сигналы: S=0, R=1.

Тогда при любом исходном состоянии ЗЯ на выходе элемента 1 установится 1.

Так как на входы элемента 2 поступают значения Q и R, то на его выходе будет сигнал 0. Таким образом, ЗЯ перейдет в состояние "1".

Аналогично при S=1, R=0 запоминающая ячейка перейдет в состояние Q=0, Q=1, то есть в "0".

Если S=1, R=1, то состояние ЗЯ будет определяться ее предыдущим состоянием.

Если ЗЯ находилась в состоянии "1", то сигнал Q=0, поступая на вход элемента 1, подтвердит состояние его выхода Q=1. На входы элемента 2 поступят только 0. Поэтому его выход будет находиться в состоянии Q=0, то есть не изменится.

Если ЗЯ находилась в состоянии "0", то сигнал Q=0, поступая на вход элемента 2, подтвердит состояние его выхода Q=1. В свою очередь, выход элемента 1 также останется без изменения.

Таким образом, эта комбинация входных сигналов соответствует режиму хранения.

Если на входы S и R поданы сигналы S = R = 0, то сигнал на выходах элементов 1 и 2 будет Q = Q = 1. При переводе ЗЯ в режим хранения ( S = R = 1), выходы элементов 1 и 2 могут установиться в произвольное состояние. Поэтому комбинация сигналов S = R = 0 на управляющих входах не используется.

20170916_my

20170916_my СИЗ глаз_Подбор

СИЗ глаз_Подбор 20161208_industrializatsiya_sssr

20161208_industrializatsiya_sssr 20170425_test_chehov

20170425_test_chehov СД_11.08

СД_11.08 С днём рождения, мамуля моя милая и родная

С днём рождения, мамуля моя милая и родная UCS. Универсальная зарядная станция

UCS. Универсальная зарядная станция The most amazing museum

The most amazing museum День правовой помощи детям

День правовой помощи детям Земля пробуждается

Земля пробуждается Web-school. Академия современных профессий

Web-school. Академия современных профессий Северо-Западная торфяная компания

Северо-Западная торфяная компания Общественное волонтерское движение Друзья малых рек

Общественное волонтерское движение Друзья малых рек Свойства сложения

Свойства сложения Главный этап хода в игре Русская Цивилизация. Расклад

Главный этап хода в игре Русская Цивилизация. Расклад Инструкция по Qlik (Bi) для подтверждения смен при закрытии

Инструкция по Qlik (Bi) для подтверждения смен при закрытии Ромашки из Бектяшки

Ромашки из Бектяшки презентация Основные методы решения уравнений высших степеней

презентация Основные методы решения уравнений высших степеней Коновалова_Городская

Коновалова_Городская Мужской стриптиз

Мужской стриптиз ребусы

ребусы Милосердие и сострадание

Милосердие и сострадание Памятки в помощь лицам, прибывающим из Украины

Памятки в помощь лицам, прибывающим из Украины Sustainable & Carbon Economy

Sustainable & Carbon Economy КГ М3У1 п Персональная информация

КГ М3У1 п Персональная информация 20180307_slozhenie_i_vychitanie_desyatichnyh_drobey

20180307_slozhenie_i_vychitanie_desyatichnyh_drobey Организация работы службы документационного обеспечения

Организация работы службы документационного обеспечения DAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA

DAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA