Содержание

- 2. Алгоритм Тамасуло Разрешение конфликтов RAW происходит за счет запуска инструкции, только когда готовы ее операнды. Устранение

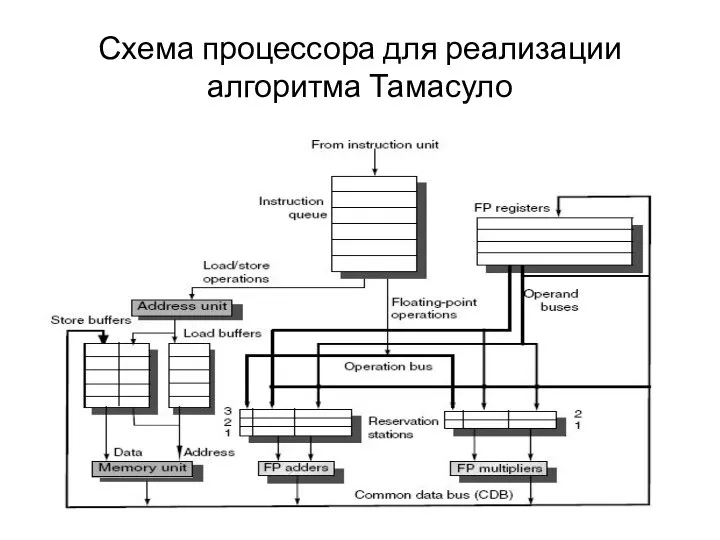

- 3. Схема процессора для реализации алгоритма Тамасуло

- 4. Состав процессора Очередь планирования (Instruction queue)[ОП] Регистровый файл (FP Registers) [РФ] Станции резервирования (Reserve Station) [СР]

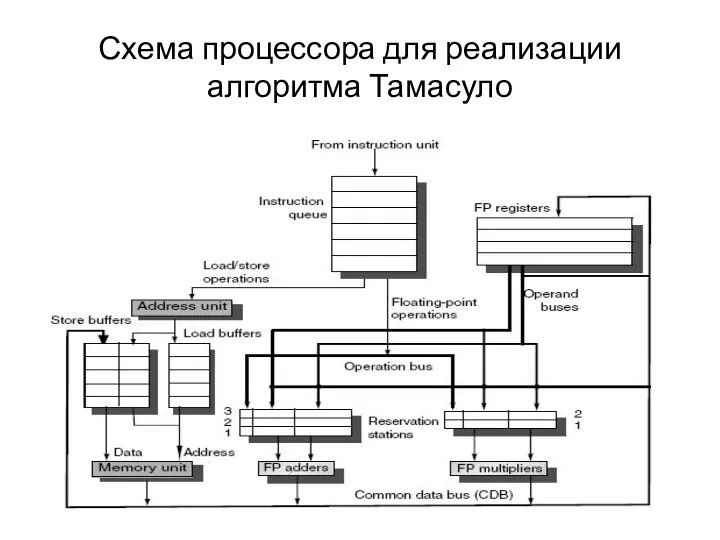

- 5. Схема процессора для реализации алгоритма Тамасуло

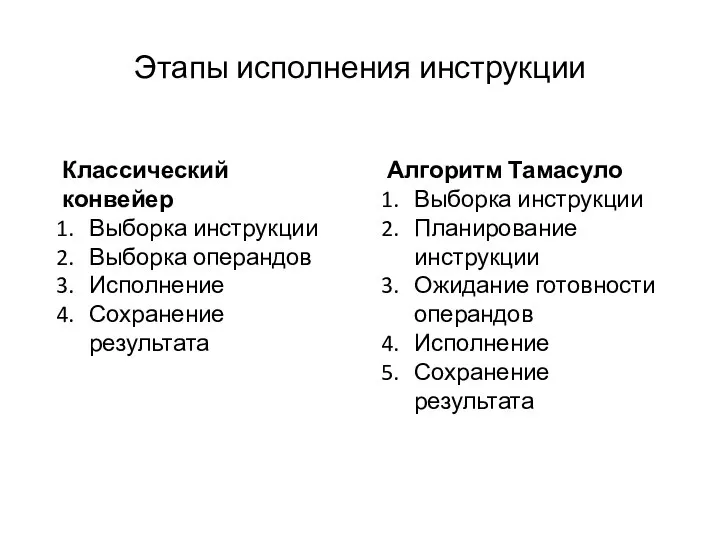

- 6. Этапы исполнения инструкции Классический конвейер Выборка инструкции Выборка операндов Исполнение Сохранение результата Алгоритм Тамасуло Выборка инструкции

- 7. Устройство СР Состоит из двух дескрипторов операндов. Дескриптор операнда содержит значение операнда или ссылку, если значение

- 8. Планирование инструкций Выборка с вершины ОП. Выборка происходит по 1 инструкции за такт. Выборка осуществляется в

- 9. Ожидание готовности операндов, исполнение, сохранение результатов Инструкция ожидает в СР до тех пор, пока не будут

- 10. Обработка инструкций загрузки и сохранения. Инструкция загрузки: Вычисление адреса Выполнение загрузки по адресу Инструкция сохранения: Вычисление

- 11. Порядок исполнения инструкций загрузки и сохранения. Определяется наличием зависимостей между инструкциями по ячейкам памяти. Адреса ячеек

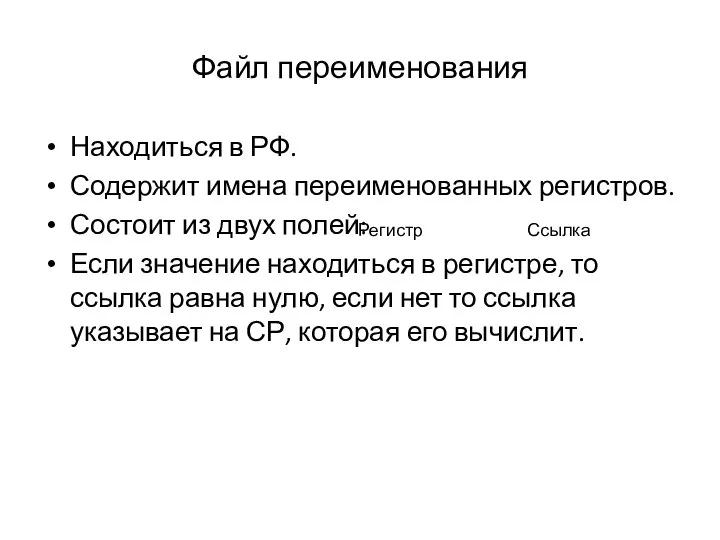

- 12. Файл переименования Находиться в РФ. Содержит имена переименованных регистров. Состоит из двух полей: Если значение находиться

- 13. Пример 1 1. L.D F6,34(R2) 2. L.D F2,45(R3) 3. MUL.D F0,F2,F4 4. SUB.D F8,F2,F6 5. DIV.D

- 14. Обозначения Op — операция, которая будет выполняться Vj, Vk— готовые значения операндов. Qj, Qk— ссылка на

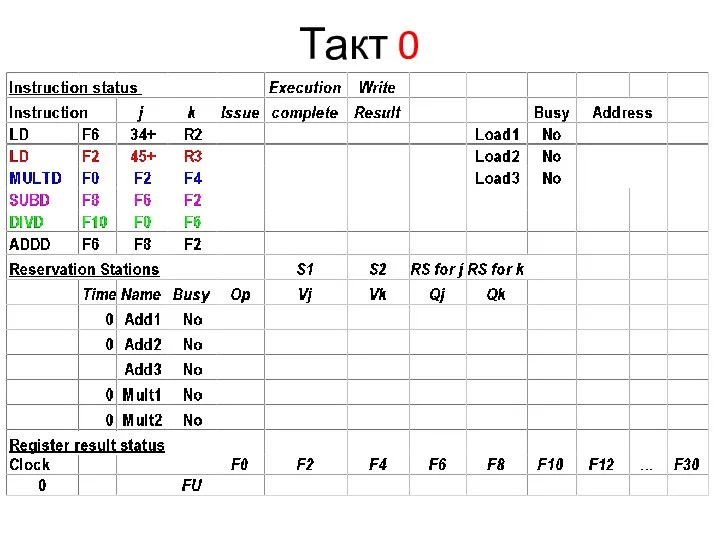

- 15. Такт 0

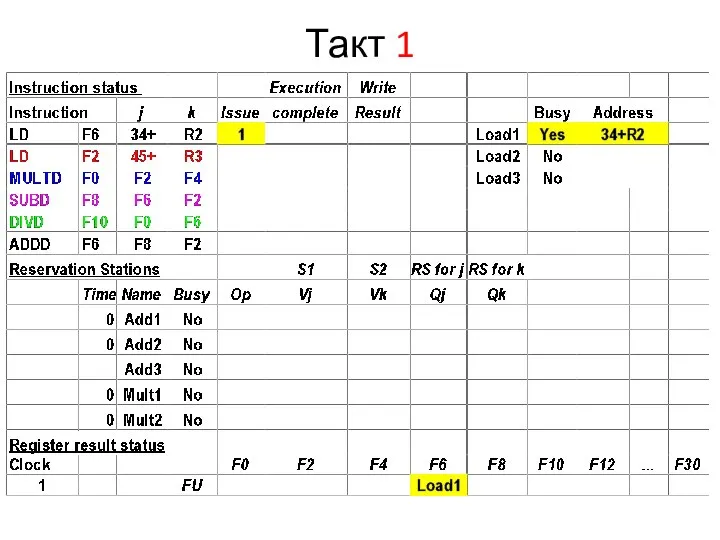

- 16. Такт 1

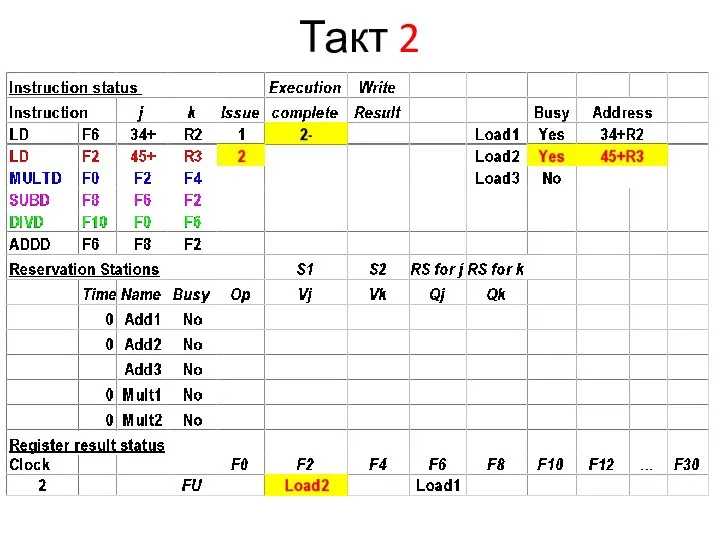

- 17. Такт 2

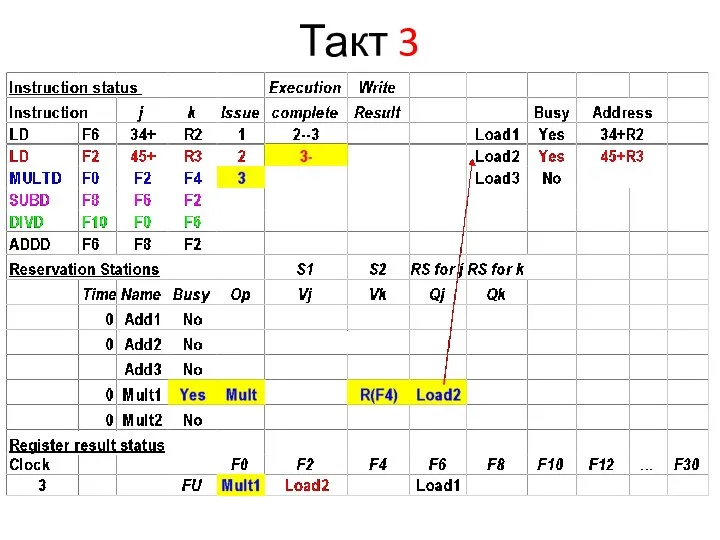

- 18. Такт 3

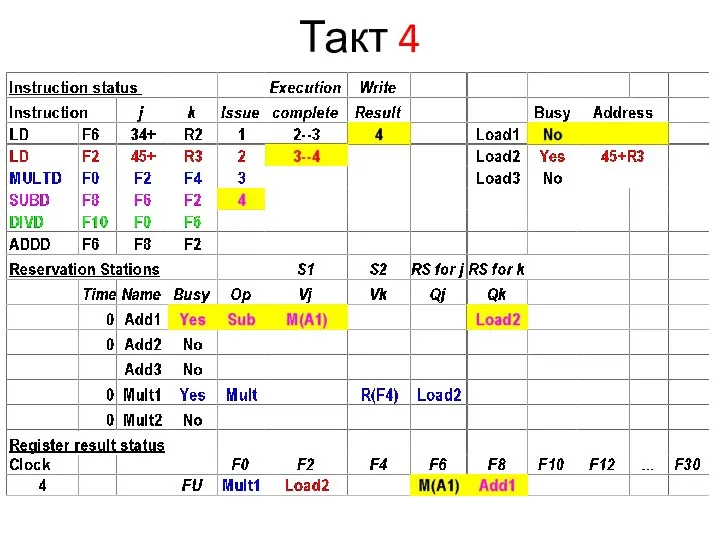

- 19. Такт 4

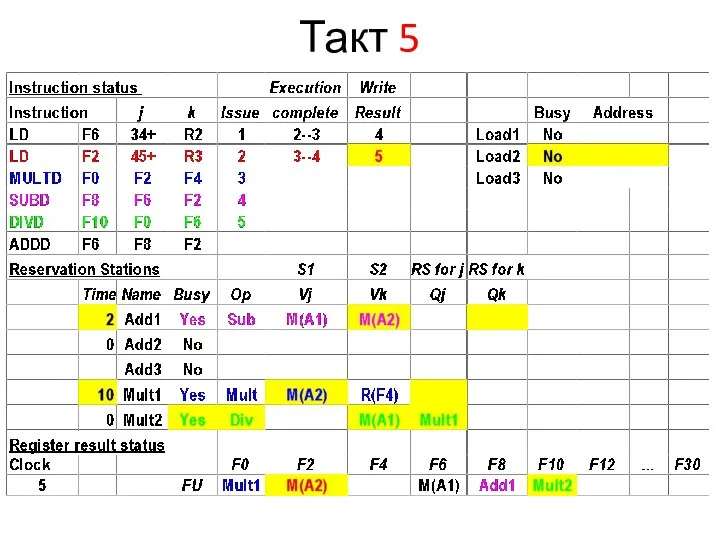

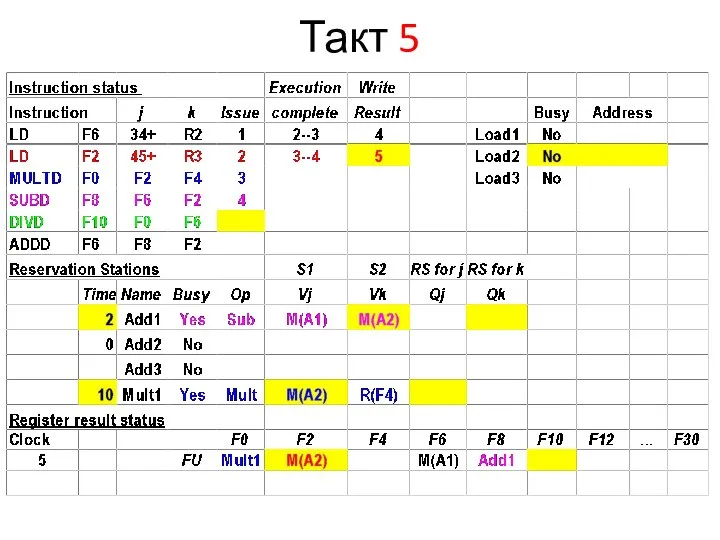

- 20. Такт 5

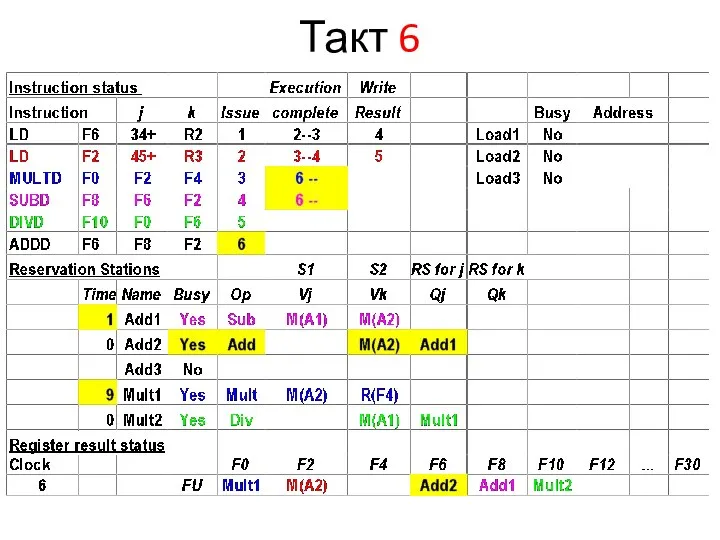

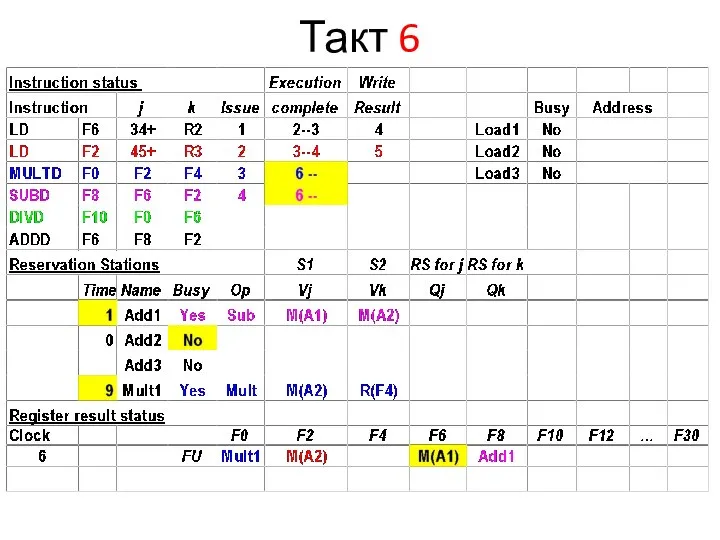

- 21. Такт 6

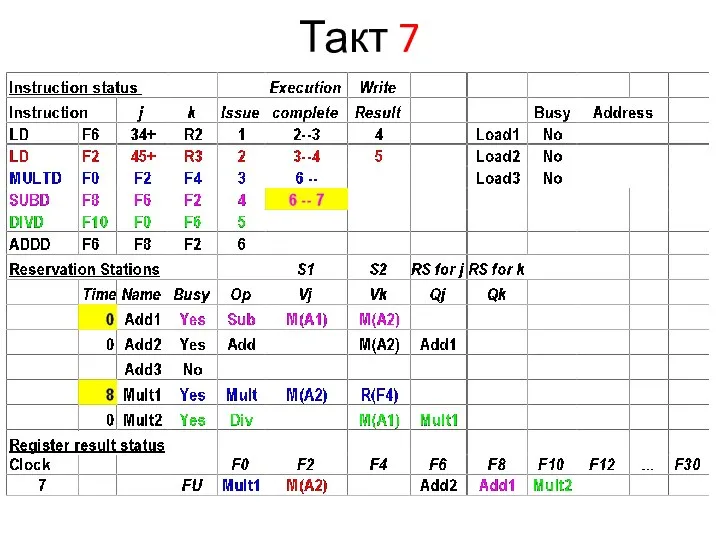

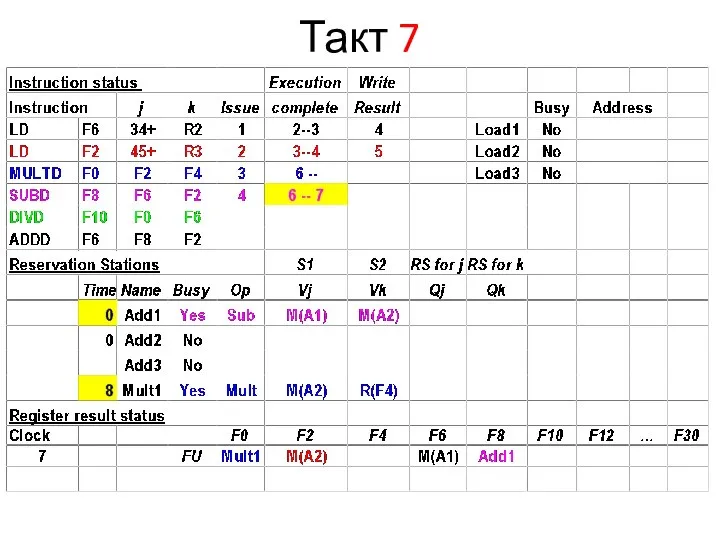

- 22. Такт 7

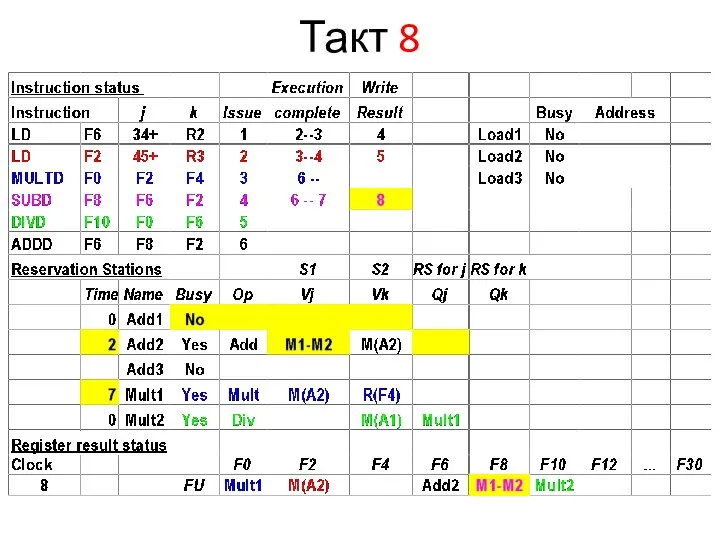

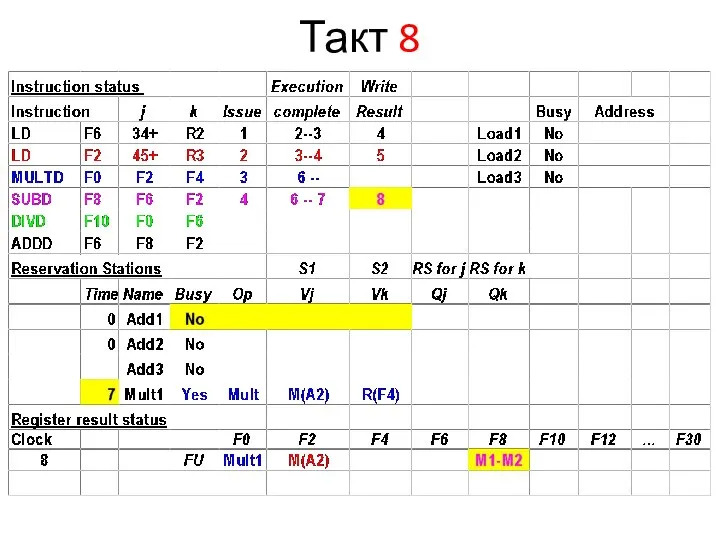

- 23. Такт 8

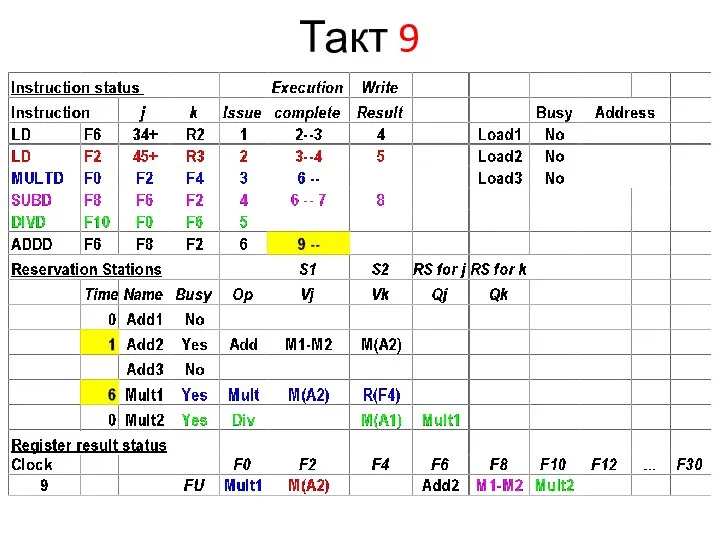

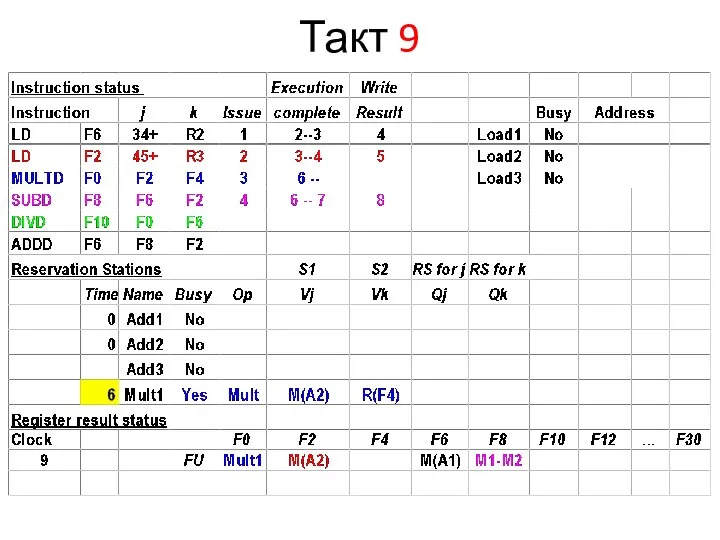

- 24. Такт 9

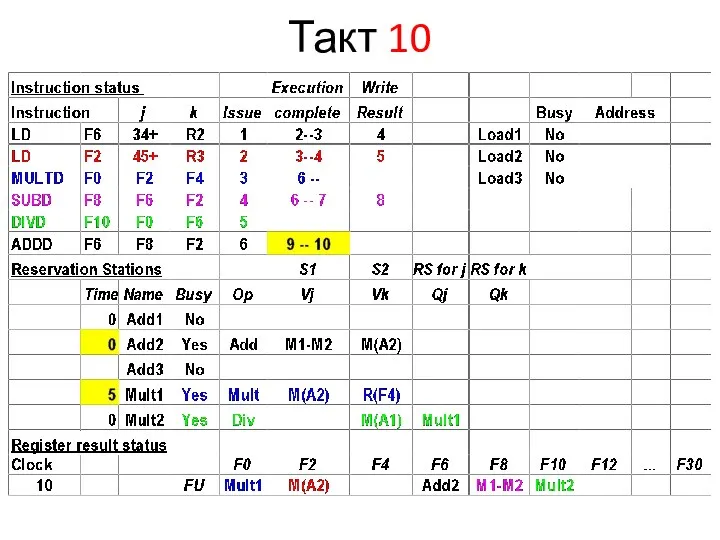

- 25. Такт 10

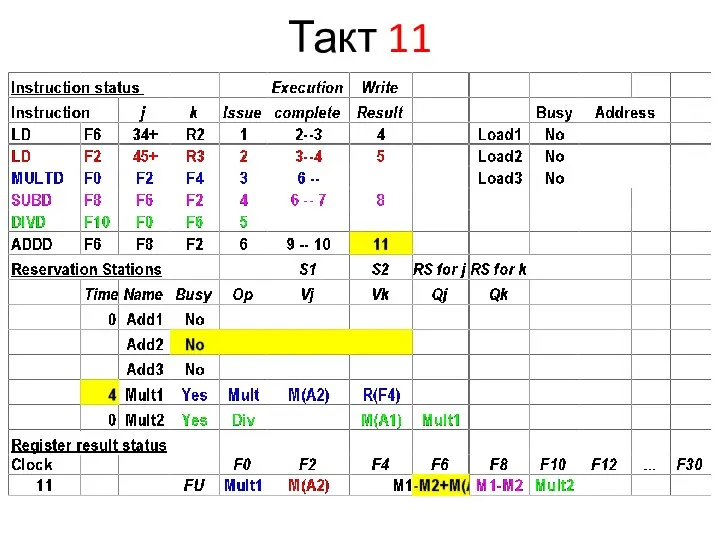

- 26. Такт 11

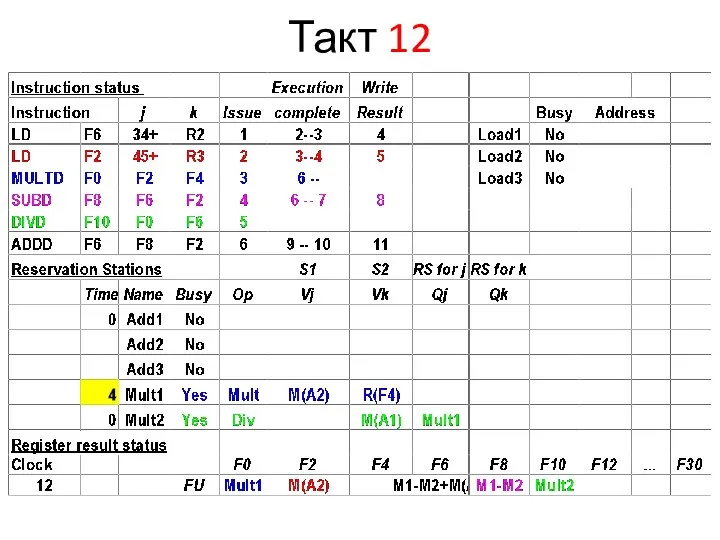

- 27. Такт 12

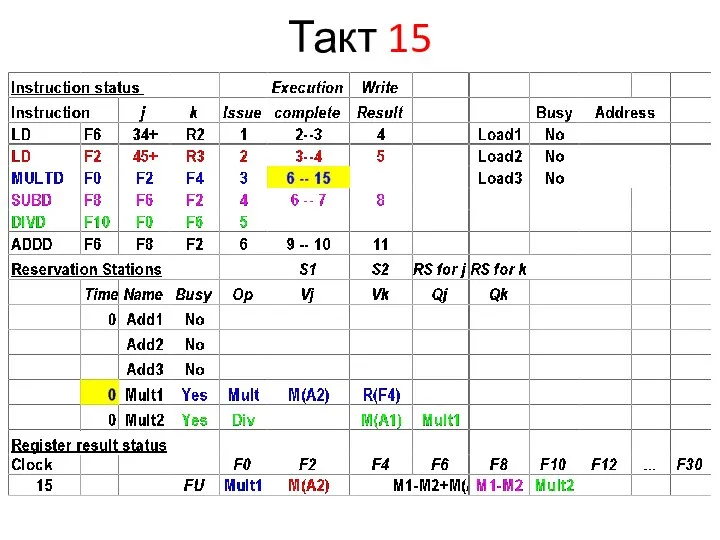

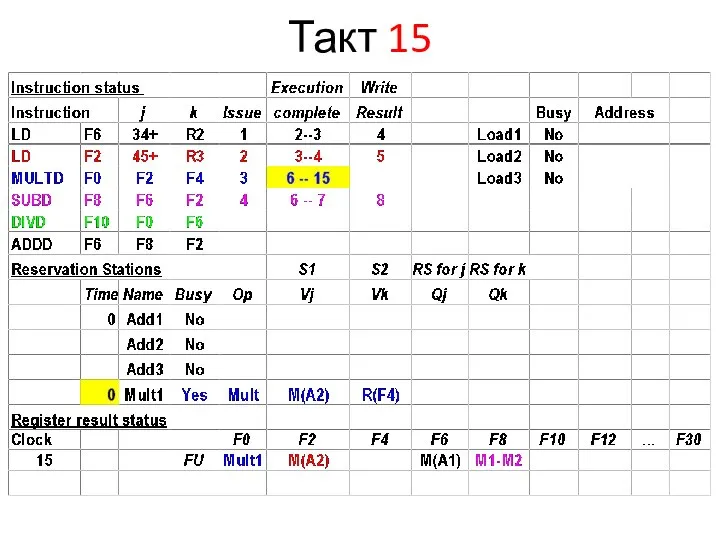

- 28. Такт 15

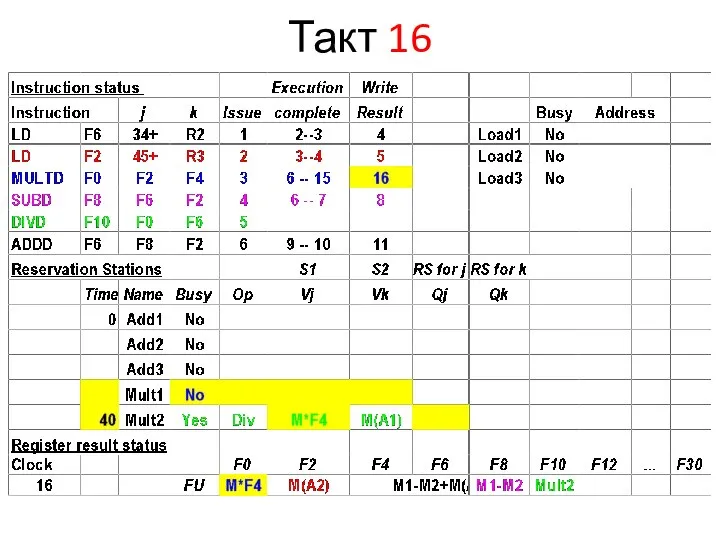

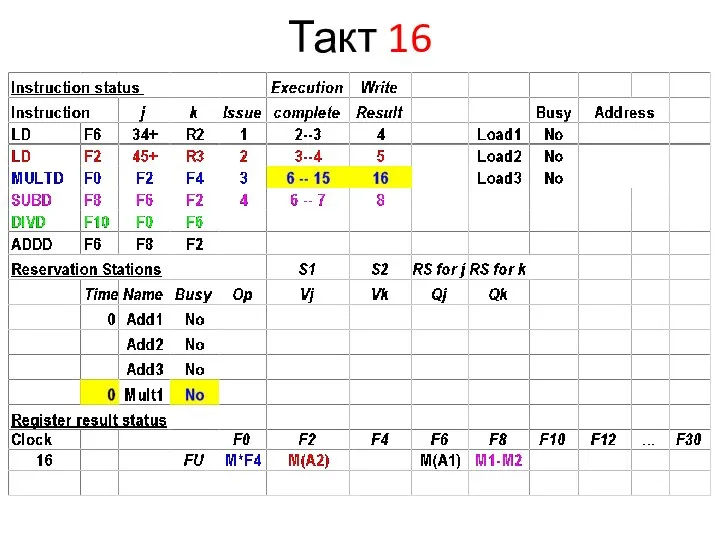

- 29. Такт 16

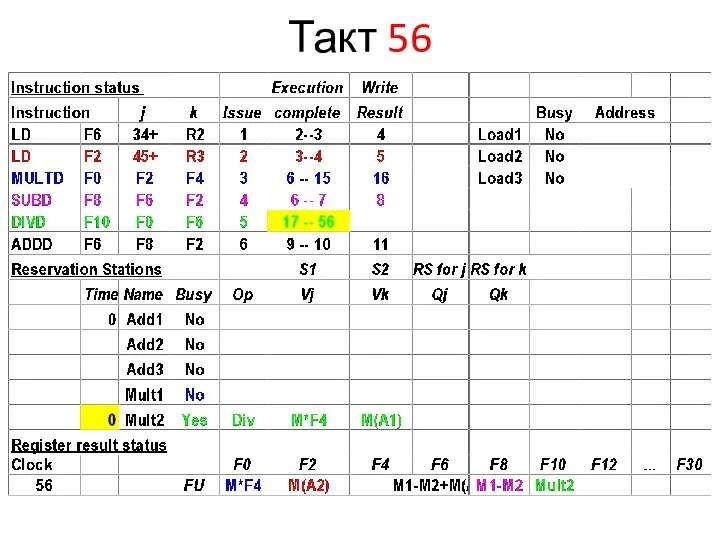

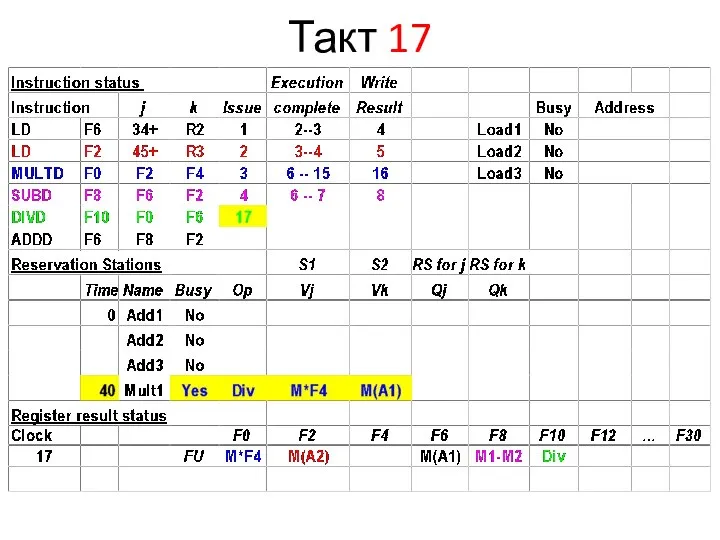

- 30. Такт 56

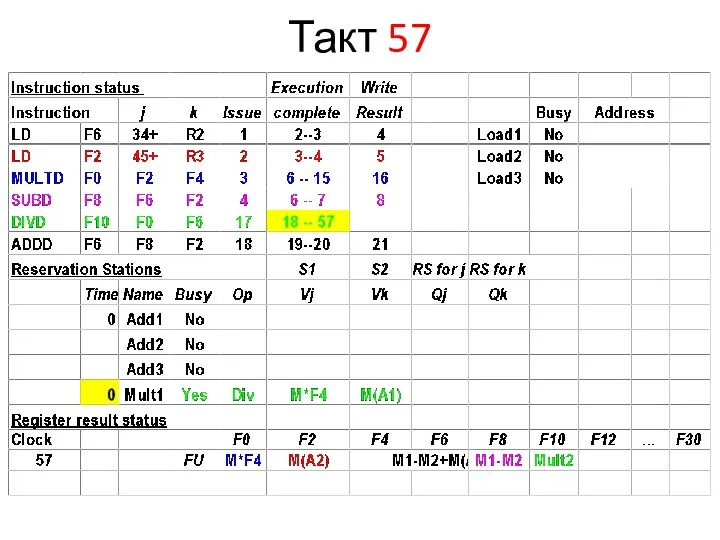

- 31. Такт 57

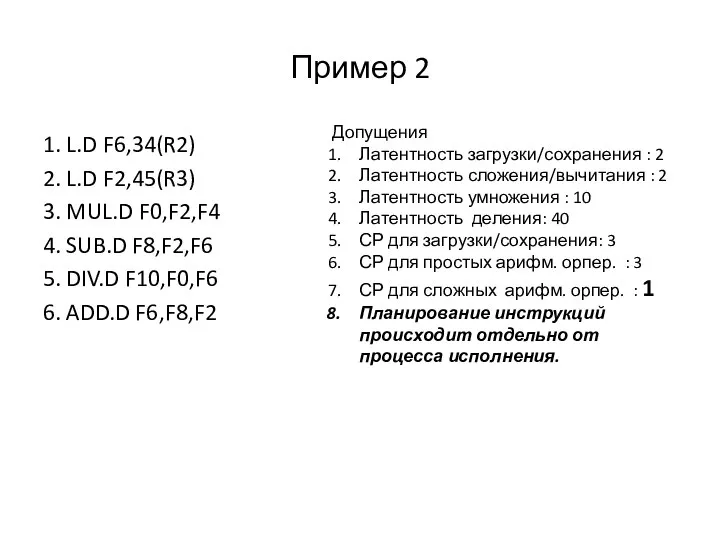

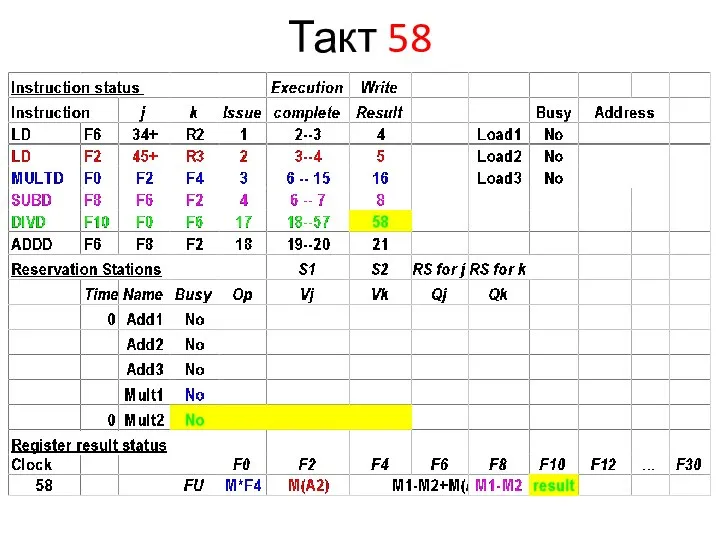

- 32. Пример 2 1. L.D F6,34(R2) 2. L.D F2,45(R3) 3. MUL.D F0,F2,F4 4. SUB.D F8,F2,F6 5. DIV.D

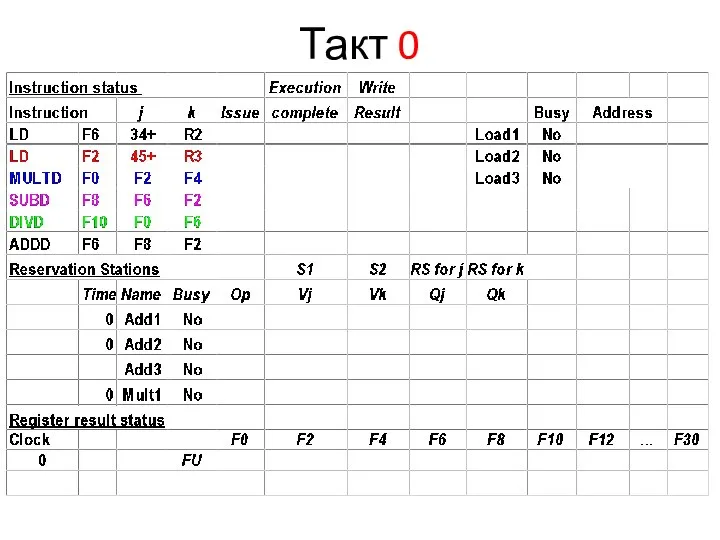

- 33. Такт 0

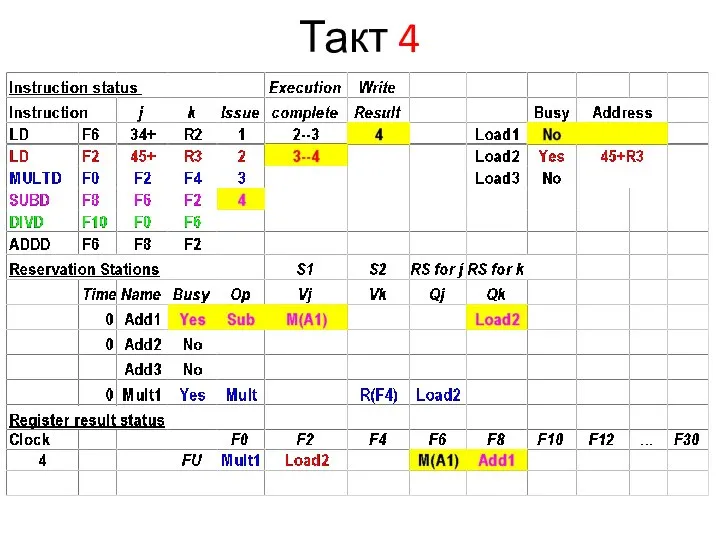

- 34. Такт 4

- 35. Такт 5

- 36. Такт 6

- 37. Такт 7

- 38. Такт 8

- 39. Такт 9

- 40. Такт 15

- 41. Такт 16

- 42. Такт 17

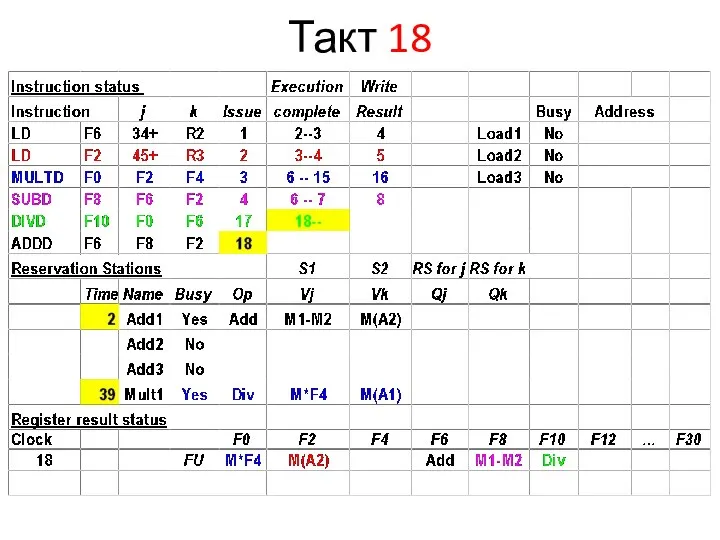

- 43. Такт 18

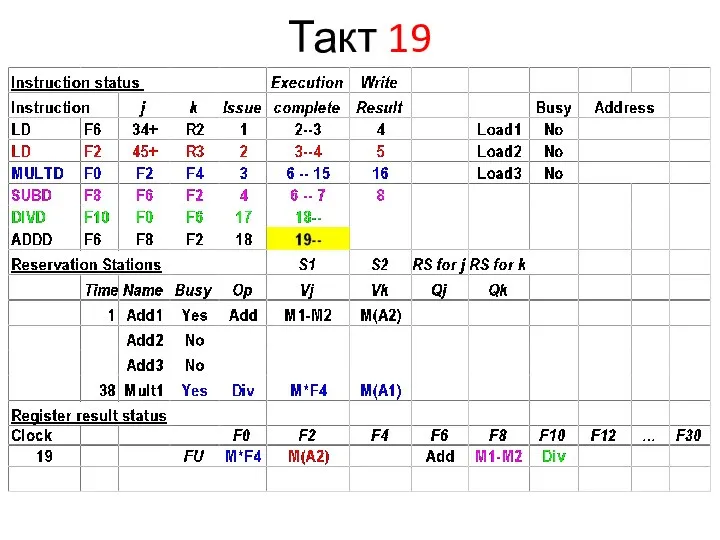

- 44. Такт 19

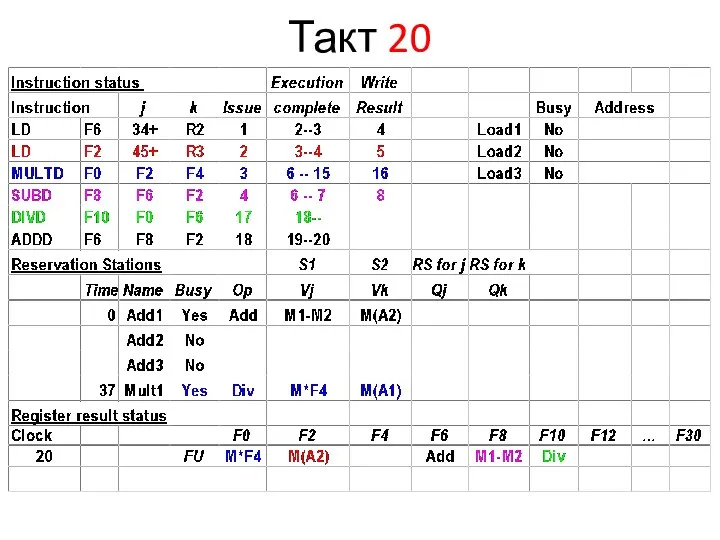

- 45. Такт 20

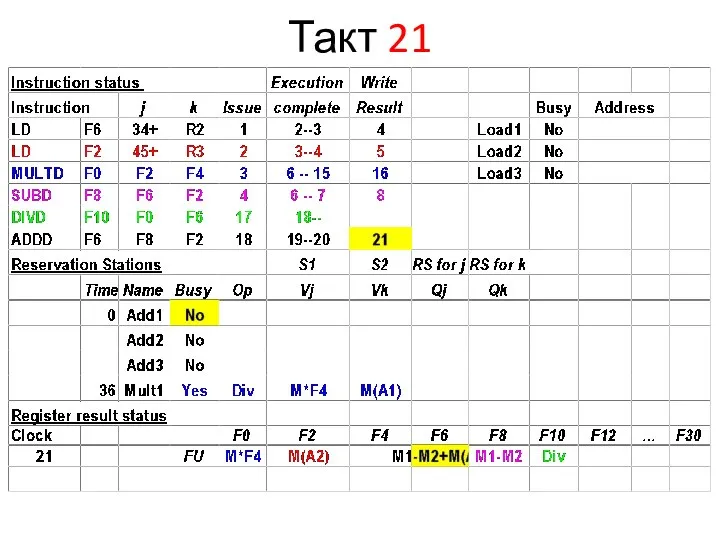

- 46. Такт 21

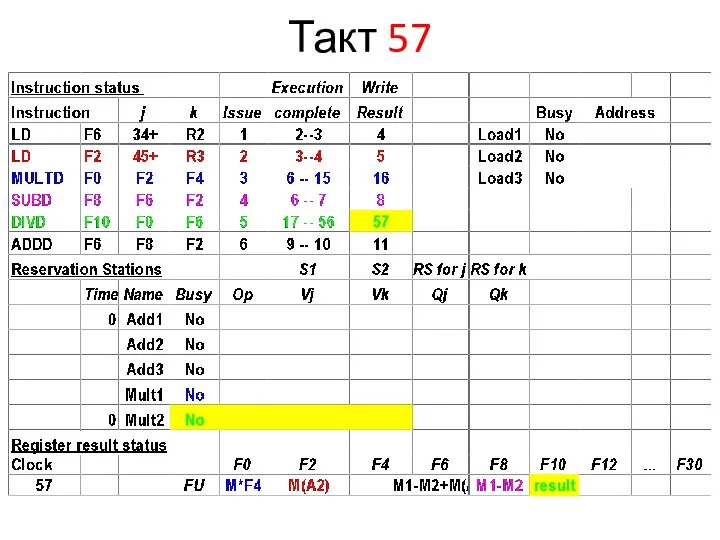

- 47. Такт 57

- 48. Такт 58

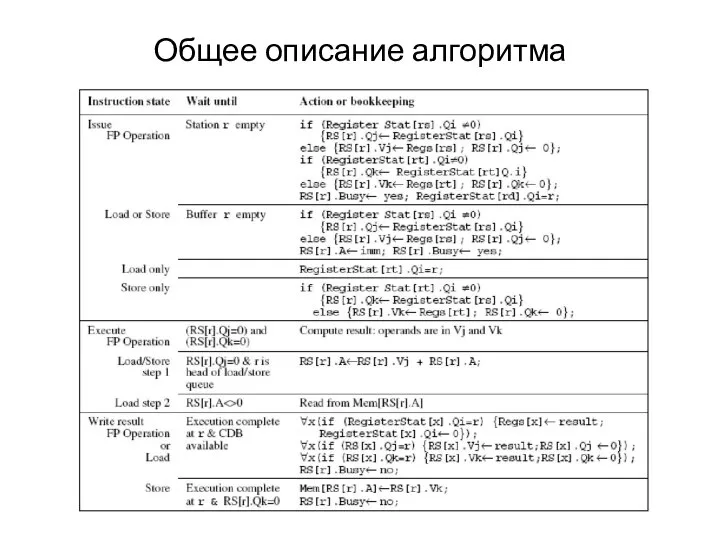

- 49. Общее описание алгоритма

- 50. Достоинства и недостатки алгоритма. Достоинства: Повышение пропускной способности Уменьшение времени простоя процессора Недостатки Большие аппаратные затраты

- 52. Скачать презентацию

![Состав процессора Очередь планирования (Instruction queue)[ОП] Регистровый файл (FP Registers) [РФ]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1305935/slide-3.jpg)

Экологическое право в системе российского права

Экологическое право в системе российского права МУНИЦИПАЛЬНОЕ ОБЩЕОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ «СРЕДНЯЯ ОБЩЕОБРАЗОВАТЕЛЬНАЯ ШКОЛА №5» г.Усинск ПРОЕКТ «ДЕКОРАТИВНОЕ ПАННО «С

МУНИЦИПАЛЬНОЕ ОБЩЕОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ «СРЕДНЯЯ ОБЩЕОБРАЗОВАТЕЛЬНАЯ ШКОЛА №5» г.Усинск ПРОЕКТ «ДЕКОРАТИВНОЕ ПАННО «С Формирование бюджета расходов на персонал. Зачем это нужно бизнесу?

Формирование бюджета расходов на персонал. Зачем это нужно бизнесу? Қазақстан Республикасының құқығының негіздері

Қазақстан Республикасының құқығының негіздері Правоохранительные органы. Правоохранительная система и ее задачи

Правоохранительные органы. Правоохранительная система и ее задачи Как мужик гусей делил

Как мужик гусей делил  Изменения в источниках и системе права в Новейшее время

Изменения в источниках и системе права в Новейшее время Презентация "Святой Георгий Победоносец" - скачать презентации по МХК

Презентация "Святой Георгий Победоносец" - скачать презентации по МХК Крымская республиканская библиотека имени И. Франко

Крымская республиканская библиотека имени И. Франко Деятельность Русской Праввославной Церкви по противодействию алкоголизации общества и утверждению трезвости

Деятельность Русской Праввославной Церкви по противодействию алкоголизации общества и утверждению трезвости Жизнь и творчество Александра Исаевича Солженицына

Жизнь и творчество Александра Исаевича Солженицына Використання файлової системи і функцій символьного введення/виведення у сучасних операційних середовищах (Лекція № 3)

Використання файлової системи і функцій символьного введення/виведення у сучасних операційних середовищах (Лекція № 3) «Сделки. Виды сделок»

«Сделки. Виды сделок»  Патофизиология воспаления

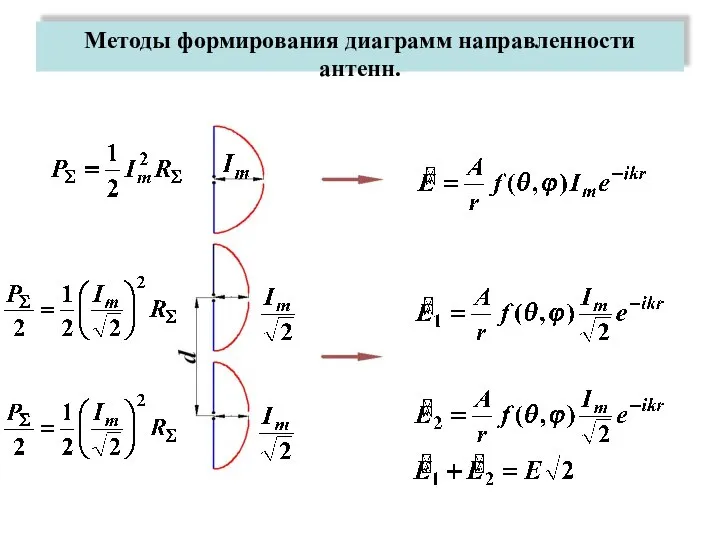

Патофизиология воспаления Методы формирования диаграмм направленности антенн

Методы формирования диаграмм направленности антенн Minecraft. Координаты и условия. Запускаем Python. Занятие 2

Minecraft. Координаты и условия. Запускаем Python. Занятие 2 Презентация на тему "Новый образовательный стандарт" - скачать презентации по Педагогике

Презентация на тему "Новый образовательный стандарт" - скачать презентации по Педагогике Архитектура барокко

Архитектура барокко Презентация на тему "Образование Гагаузской Автономии" - скачать презентации по Педагогике

Презентация на тему "Образование Гагаузской Автономии" - скачать презентации по Педагогике ОБЪЕДИНЕНИЕ РУССКИХ ЗЕМЕЛЬ ВОКРУГ МОСКВЫ (XIV—XVI) План. 1. Причины образования единого государства. 2. Усиление Московского кня

ОБЪЕДИНЕНИЕ РУССКИХ ЗЕМЕЛЬ ВОКРУГ МОСКВЫ (XIV—XVI) План. 1. Причины образования единого государства. 2. Усиление Московского кня РВП

РВП Копия Презентация1.ppt

Копия Презентация1.ppt Фокина Л. П. Вычитание в пределах 100 - презентация для начальной школы

Фокина Л. П. Вычитание в пределах 100 - презентация для начальной школы Развитие вычислительной техники

Развитие вычислительной техники Lista Światowego Dziedzictwa Kulturowego i Przyrodniczego UNESCO

Lista Światowego Dziedzictwa Kulturowego i Przyrodniczego UNESCO Тема: Закрепление изученного.

Тема: Закрепление изученного. Система воспитательной работы в классе Классный руководитель Буткевич И.В.

Система воспитательной работы в классе Классный руководитель Буткевич И.В. Наноэлектроника. Программы по нанотехнологиям

Наноэлектроника. Программы по нанотехнологиям