Содержание

- 2. Типы суперскалярных процессоров Статический. Выполняет инструкции по порядку (in-order) Динамический. Выполняет инструкции вне порядка (out of

- 3. Статический суперскалярный процессор Схож с классическим конвейерным скалярным процессором. Все инструкции выполнятся в рамках одного конвейера.

- 4. Стадия планирования и группировки инструкций. Проверяет группу из n инструкций на наличие конфликтов внутри группы и

- 5. Достоинства и недостатки Достоинства: Относительная аппаратная простота. Высокая пиковая производительность. Возможно достижения высокой рабочей частоты. Недостатки:

- 6. Модели статический суперскалярных процессоров. Sun Ultra Sparc III / IV IBM POWER 6

- 7. Динамический суперскалярный процессор. Для планирования использует алгоритм Тамасуло. Усовершенствована стадия планирования, которая может планировать более 2

- 8. Что быстрее динамического суперскалярного процессора? Динамический суперскалярный процессор использует параллелизм инструкций только в одном базовом блоке.

- 9. Спекулятивный суперскалярный процессор. (ССП) Спекуляция - выполнение некоторой операции, необходимость выполнения которой носит вероятностный характер. ССП

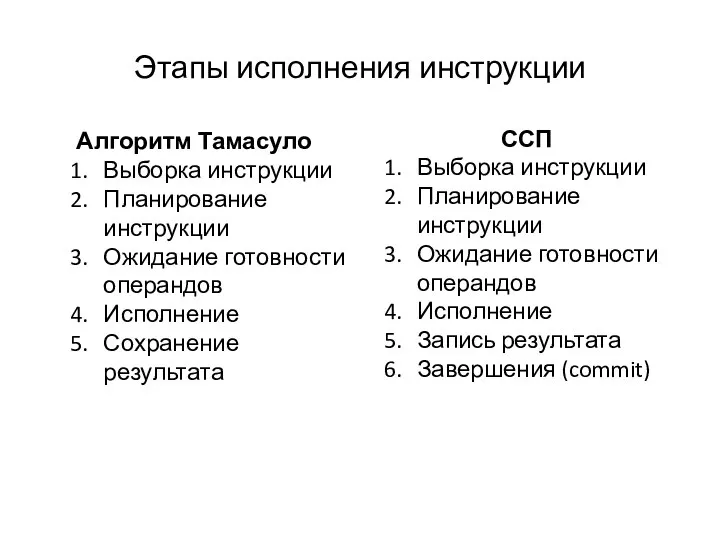

- 10. Этапы исполнения инструкции Алгоритм Тамасуло Выборка инструкции Планирование инструкции Ожидание готовности операндов Исполнение Сохранение результата ССП

- 11. Стадии записи результата и завершения На стадии записи результата результат работы инструкции помещается в промежуточное хранилище,

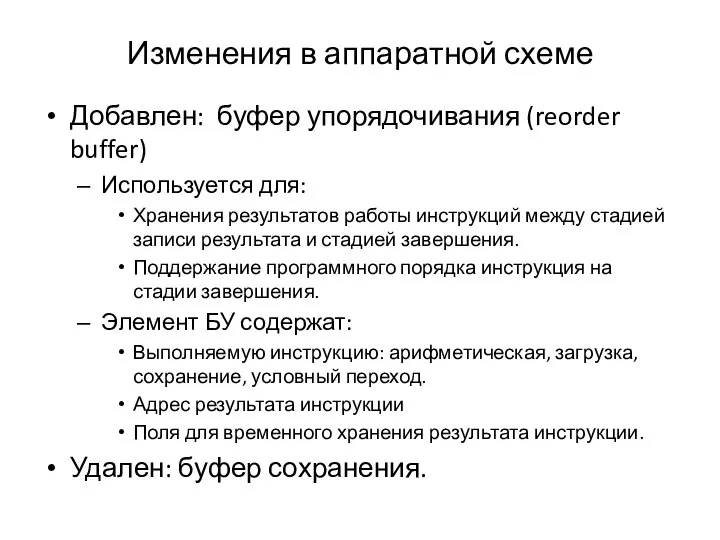

- 12. Изменения в аппаратной схеме Добавлен: буфер упорядочивания (reorder buffer) Используется для: Хранения результатов работы инструкций между

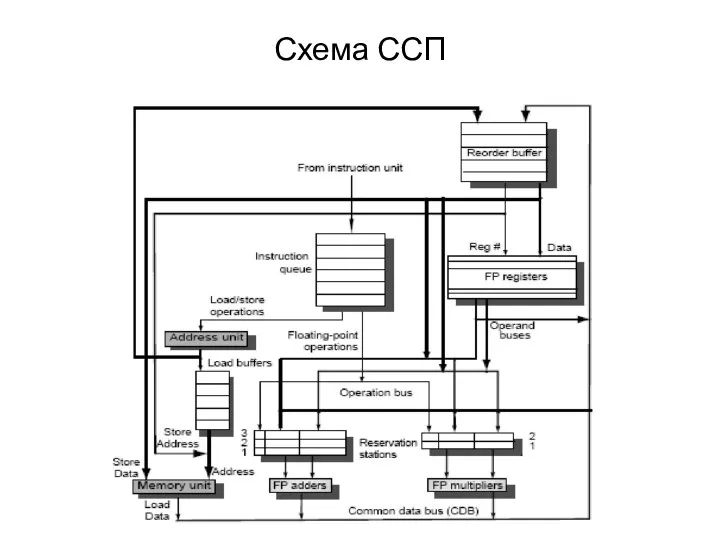

- 13. Схема ССП

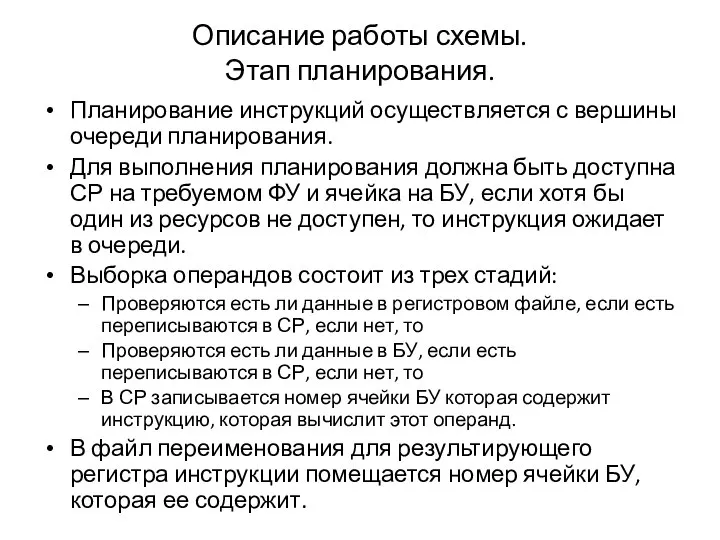

- 14. Описание работы схемы. Этап планирования. Планирование инструкций осуществляется с вершины очереди планирования. Для выполнения планирования должна

- 15. Описание работы схемы. Этап исполнения и записи результат. Инструкции запускаются на исполнении по мере готовности их

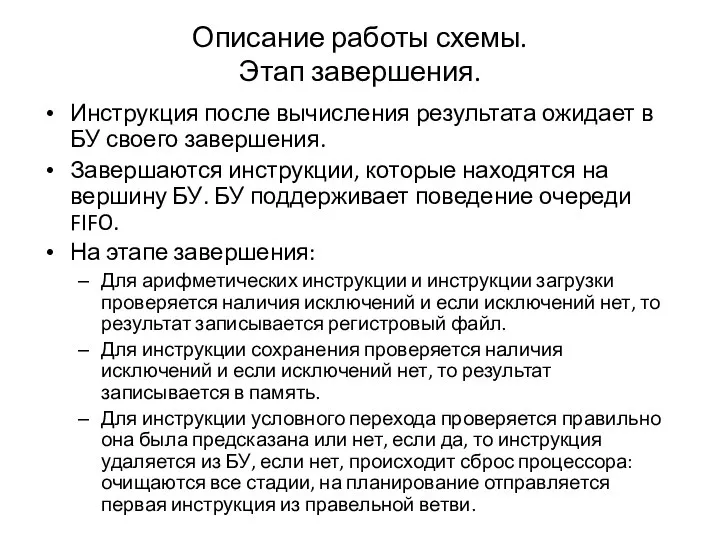

- 16. Описание работы схемы. Этап завершения. Инструкция после вычисления результата ожидает в БУ своего завершения. Завершаются инструкции,

- 17. Пример 1. L.D F6,34(R2) 2. L.D F2,45(R3) 3. MUL.D F0,F2,F4 4. SUB.D F8,F2,F6 5. DIV.D F10,F0,F6

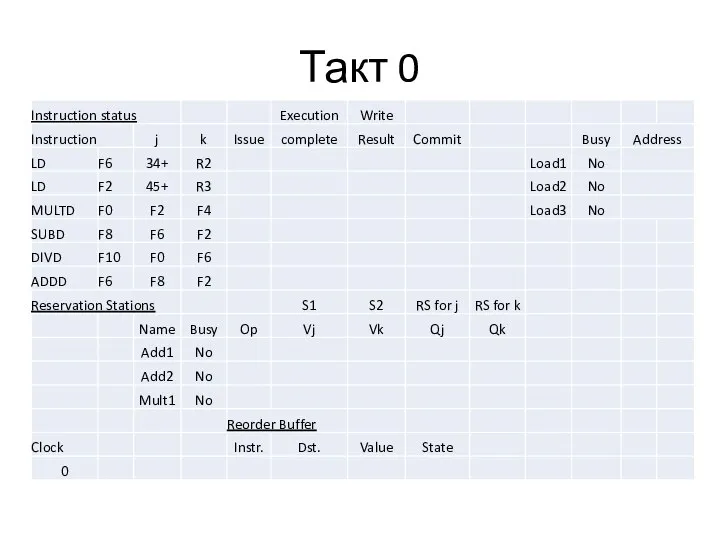

- 18. Такт 0

- 19. Такт 1

- 20. Такт 2

- 21. Такт 3

- 22. Такт 4

- 23. Такт 5

- 24. Такт 6

- 25. Такт 7

- 26. Такт 8

- 27. Такт 9

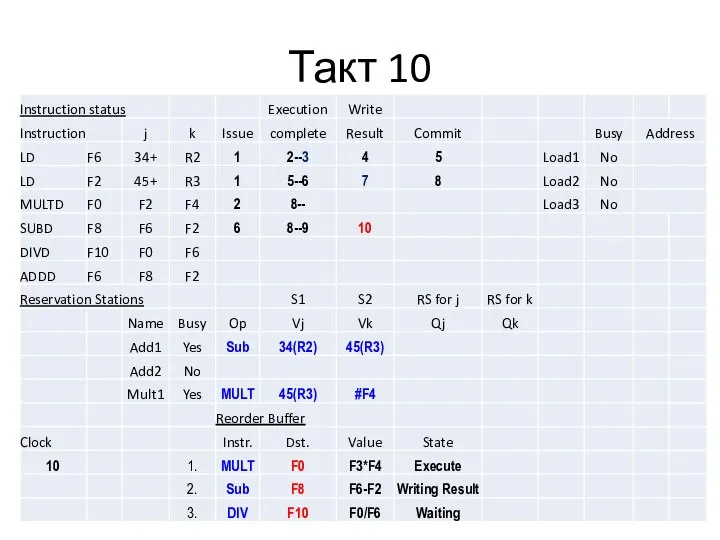

- 28. Такт 10

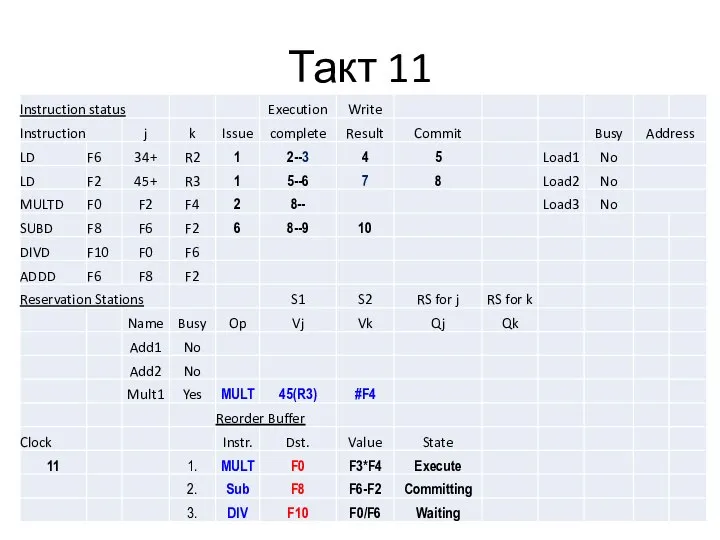

- 29. Такт 11

- 30. Такт 17

- 31. Такт 18

- 32. Такт 19

- 33. Такт 20

- 34. Такт 21

- 35. Такт 22

- 36. Такт 23

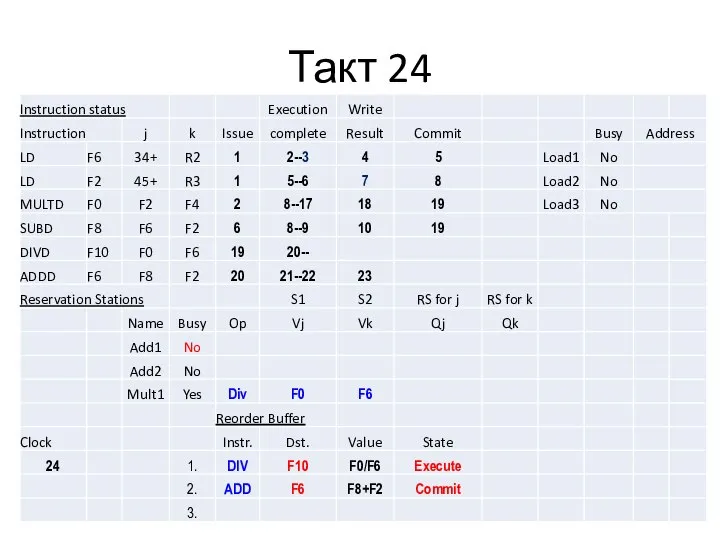

- 37. Такт 24

- 38. Такт 59

- 39. Такт 60

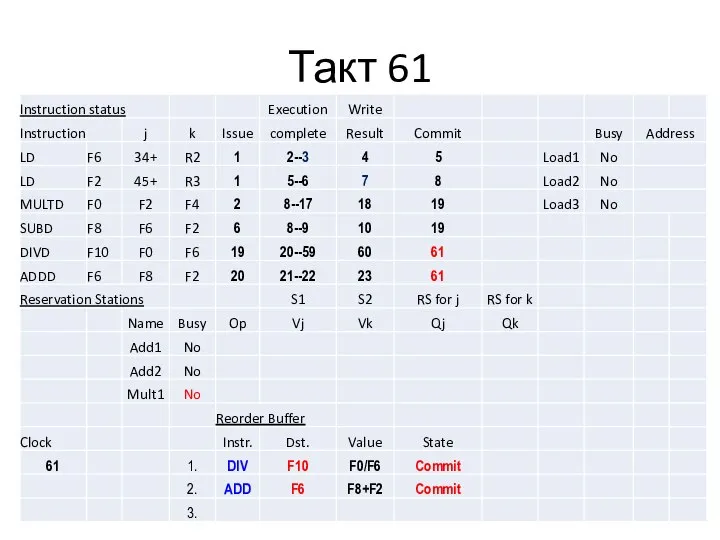

- 40. Такт 61

- 41. Что произойдет если будет сгенерировано исключение? Если в процессе завершения инструкции выяснится, что она сгенерировала исключение,

- 42. Что обеспечивает выполнение критериев корректного исполнения программы? Сохранения потока данных происходит за счет использование СР и

- 43. Ограничения спекуляции. Если инструкция в спекулятивном режиме вызвало кэш промах стоит его обрабатывать или нет? Обрабатываются

- 44. Ограничения планирования инструкций условного перехода. За один такт может быть запланирована только одна инструкция условного перехода,

- 45. Альтернативный подход к ССП Переименование регистров. Вычисленные значения инструкций до стадии завершения хранятся в основном регистровом

- 47. Скачать презентацию

Специфика технологии как товара

Специфика технологии как товара Стратегические направления Стратегическое видение Миссия SWOT - анализ

Стратегические направления Стратегическое видение Миссия SWOT - анализ  Поэзия С.А. Клычкова

Поэзия С.А. Клычкова РЕФЕРАТ НА ТЕМУ: «Московский метрополитен как памятник архитектуры » . Группа РГ-08-6

РЕФЕРАТ НА ТЕМУ: «Московский метрополитен как памятник архитектуры » . Группа РГ-08-6 Контрабанда в Дальневосточном таможенном управлении

Контрабанда в Дальневосточном таможенном управлении Александр Сергеевич Пушкин (1799 - 1837)

Александр Сергеевич Пушкин (1799 - 1837) РАЗВИТИЕ ПОЗНАВАТЕЛЬНЫХ ПРОЦЕССОВ И ИГРОВОЙ ДЕЯТЕЛЬНОСТИ В ДОШКОЛЬНОМ ВОЗРАСТЕ

РАЗВИТИЕ ПОЗНАВАТЕЛЬНЫХ ПРОЦЕССОВ И ИГРОВОЙ ДЕЯТЕЛЬНОСТИ В ДОШКОЛЬНОМ ВОЗРАСТЕ Макияж тигра - презентация для начальной школы_

Макияж тигра - презентация для начальной школы_ Что такое йога

Что такое йога Презентация____

Презентация____ Рождество Христово

Рождество Христово Устойчивость оболочек

Устойчивость оболочек Проблемы материи в истории философии

Проблемы материи в истории философии Презентация "Инвестиционный банк – посредник между эмитентом и рынком" - скачать презентации по Экономике

Презентация "Инвестиционный банк – посредник между эмитентом и рынком" - скачать презентации по Экономике История

История ДИФФЕРЕНЦИАЦИЯ ПРОЦЕССА ОБУЧЕНИЯ (ПОНЯТИЯ И СУЩНОСТЬ)

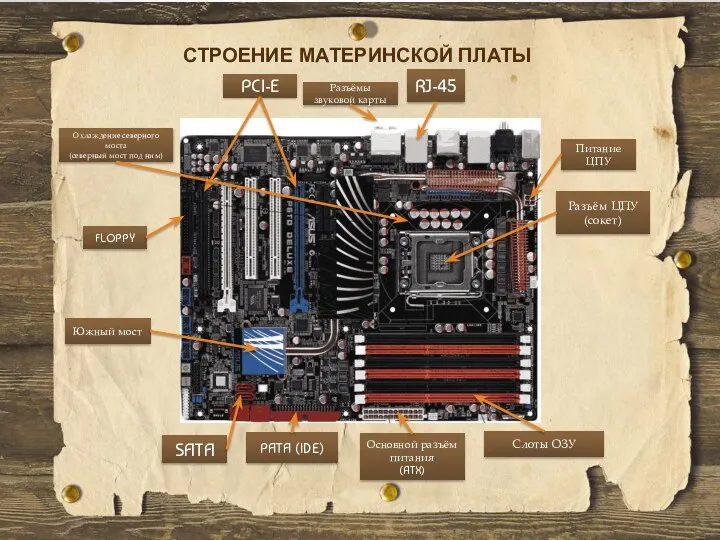

ДИФФЕРЕНЦИАЦИЯ ПРОЦЕССА ОБУЧЕНИЯ (ПОНЯТИЯ И СУЩНОСТЬ) Строение материнской платы

Строение материнской платы Разработка металлических ювелирных и декоративных изделий «Jewelry & paste»

Разработка металлических ювелирных и декоративных изделий «Jewelry & paste» DeVita Ritm base - цифровое устройство оздоровления

DeVita Ritm base - цифровое устройство оздоровления Правовые основы деятельности международных спортивных организаций и олимпийских игр

Правовые основы деятельности международных спортивных организаций и олимпийских игр Презентация Киотская конвенция

Презентация Киотская конвенция Сортоводство лесных древесных пород

Сортоводство лесных древесных пород Языки программирования

Языки программирования Коробка передач на ВАЗ-2106

Коробка передач на ВАЗ-2106 Трещины на торце вала верхнего рулевого управления. LADA 4x4

Трещины на торце вала верхнего рулевого управления. LADA 4x4 第二课 《汉语口语速成 基础 篇》 吃点什么 作者 支悠儿

第二课 《汉语口语速成 基础 篇》 吃点什么 作者 支悠儿 Мақтаншақ бұлақ

Мақтаншақ бұлақ Однофазные линейные электрические цепи синусоидального тока. Элементы цепи. Мощность. Резонанс

Однофазные линейные электрические цепи синусоидального тока. Элементы цепи. Мощность. Резонанс