Содержание

- 2. Логическая ячейка FPGA Cyclone II Рис. 2 – Логическая ячейка FPGA Cyclone II

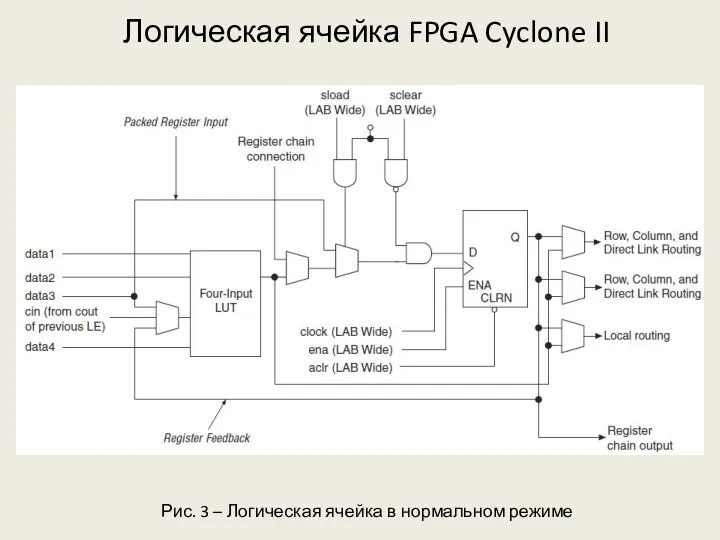

- 3. Логическая ячейка FPGA Cyclone II Рис. 3 – Логическая ячейка в нормальном режиме

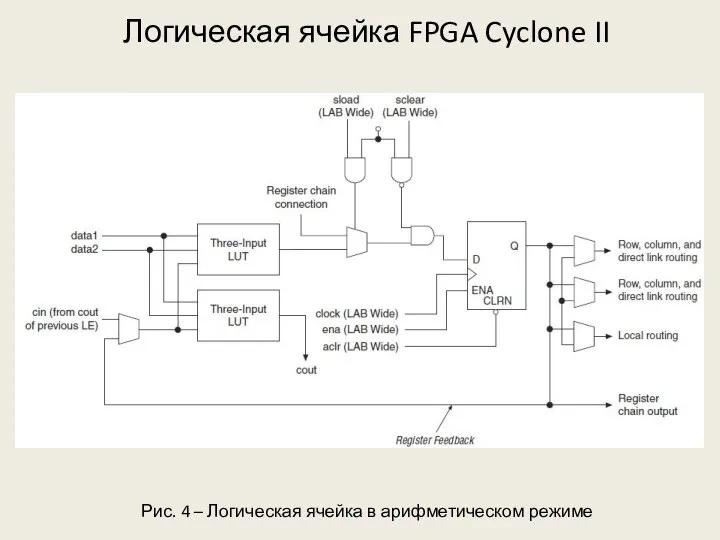

- 4. Логическая ячейка FPGA Cyclone II Рис. 4 – Логическая ячейка в арифметическом режиме

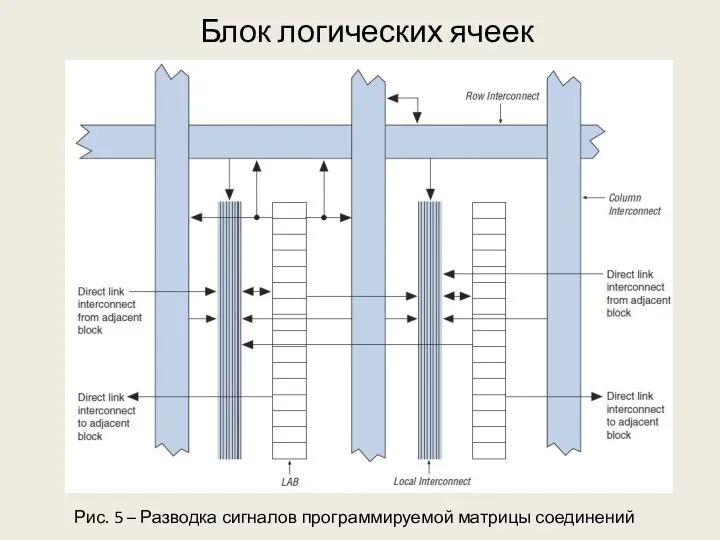

- 5. Блок логических ячеек Рис. 5 – Разводка сигналов программируемой матрицы соединений

- 6. Система синхронизации и PLL Рис.6 – Схема разводки синхросигнала по микросхеме

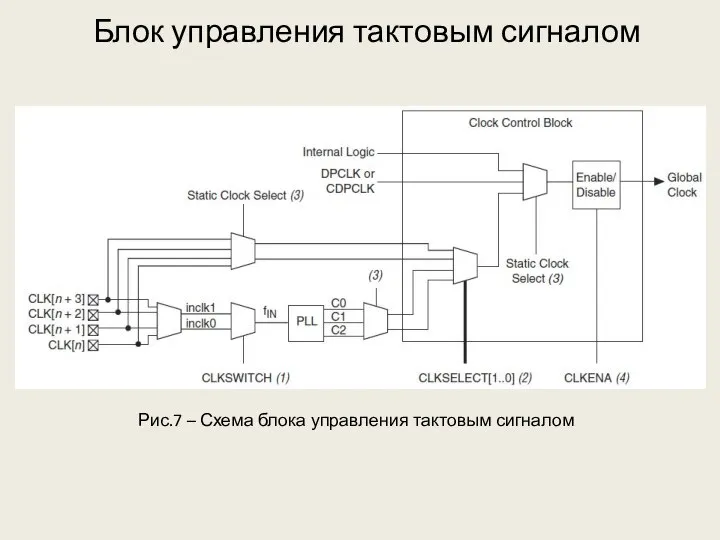

- 7. Блок управления тактовым сигналом Рис.7 – Схема блока управления тактовым сигналом

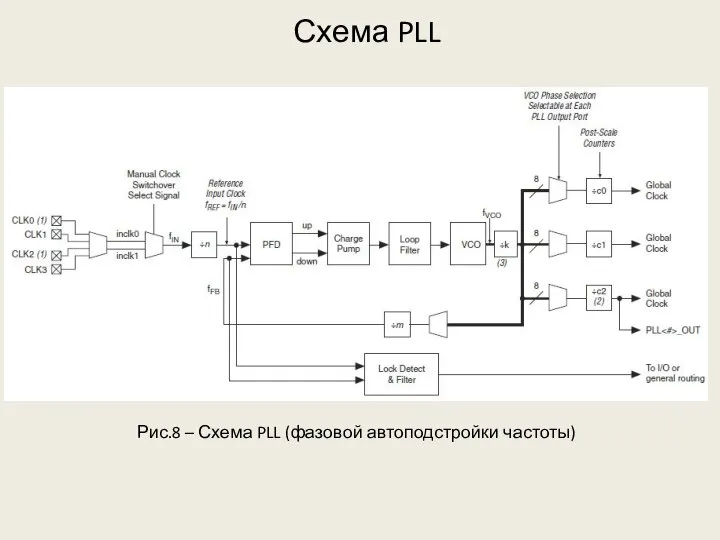

- 8. Схема PLL Рис.8 – Схема PLL (фазовой автоподстройки частоты)

- 9. Встроенные блоки памяти M4K Рис.9 – Подключение блоков памяти к внутренним сигналам

- 10. Встроенный умножитель Рис.10 – Схема встроенных умножителей

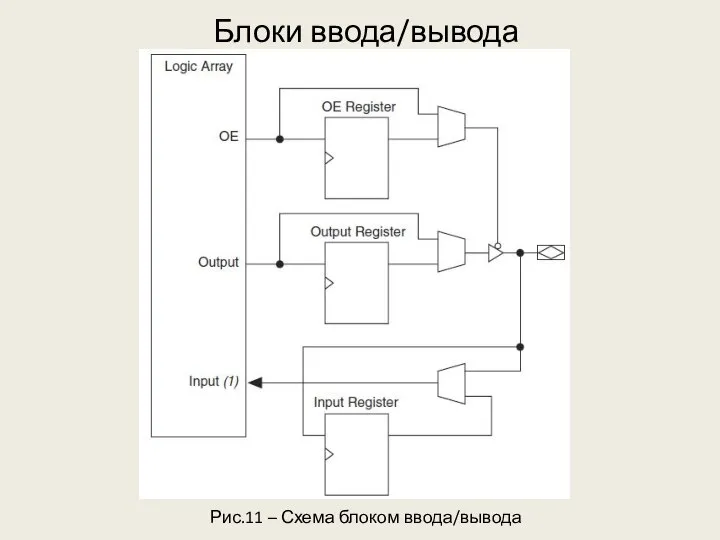

- 11. Блоки ввода/вывода Рис.11 – Схема блоком ввода/вывода

- 12. Банки блоков ввода/вывода Рис.12 – Размещение банков блоков ввода/вывода

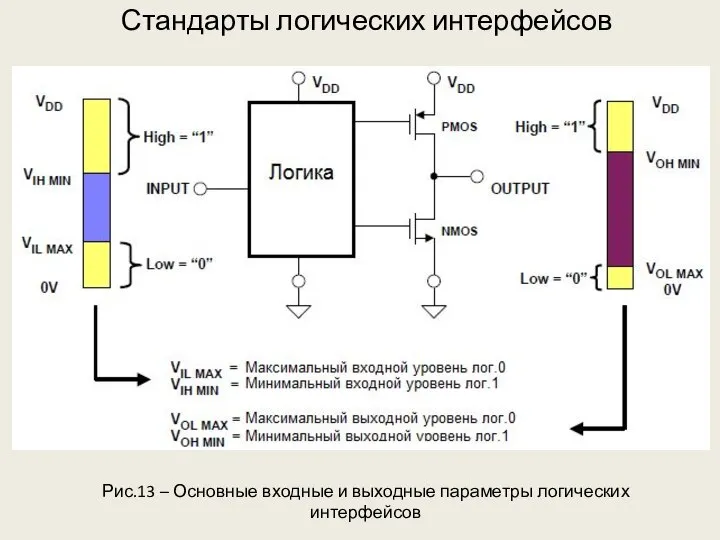

- 13. Стандарты логических интерфейсов Рис.13 – Основные входные и выходные параметры логических интерфейсов

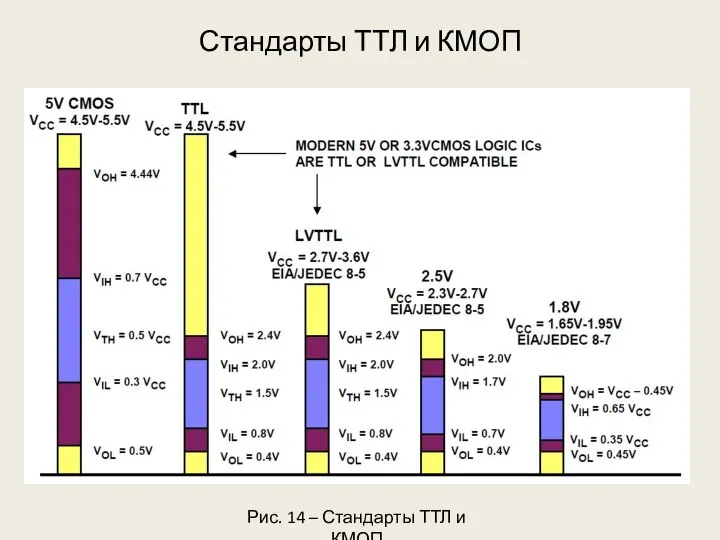

- 14. Стандарты ТТЛ и КМОП Рис. 14 – Стандарты ТТЛ и КМОП

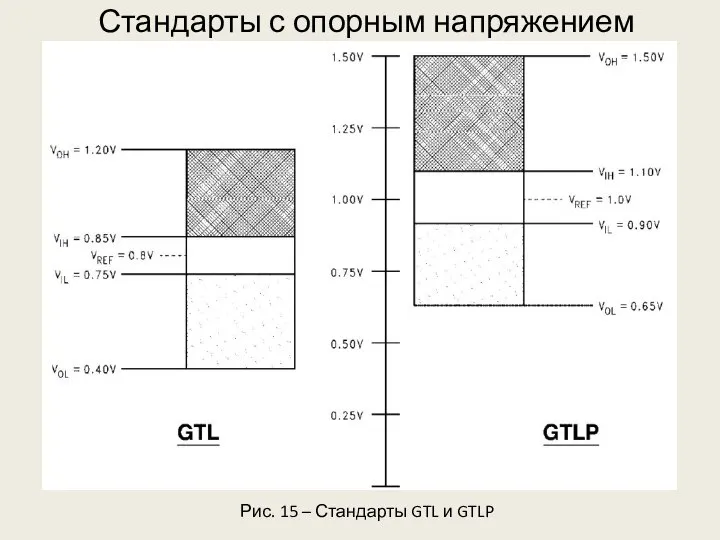

- 15. Стандарты с опорным напряжением Рис. 15 – Стандарты GTL и GTLP

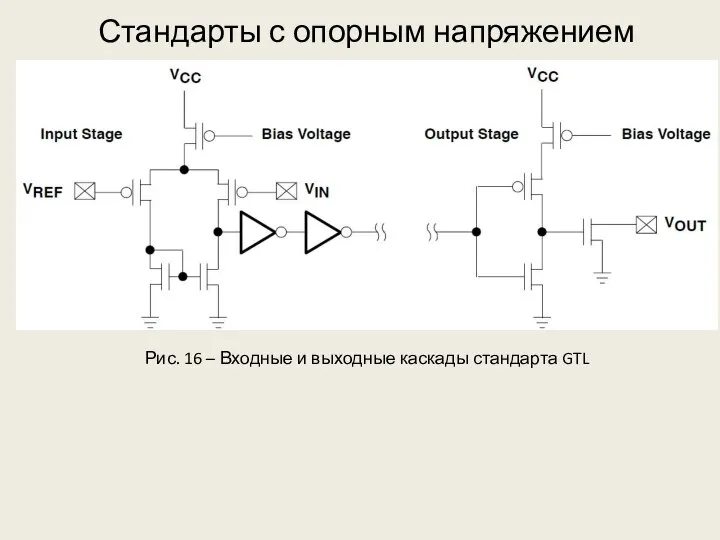

- 16. Стандарты с опорным напряжением Рис. 16 – Входные и выходные каскады стандарта GTL

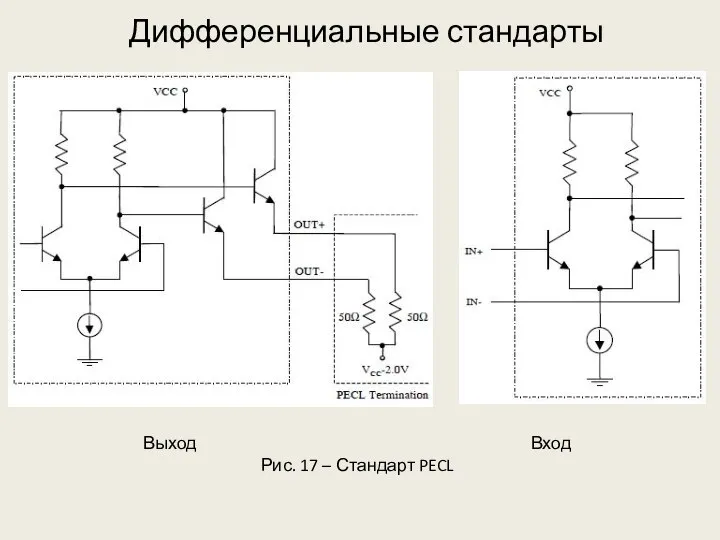

- 17. Дифференциальные стандарты Выход Вход Рис. 17 – Стандарт PECL

- 18. Дифференциальные стандарты Рис. 18 – Соединение приемника и передатчика PECL

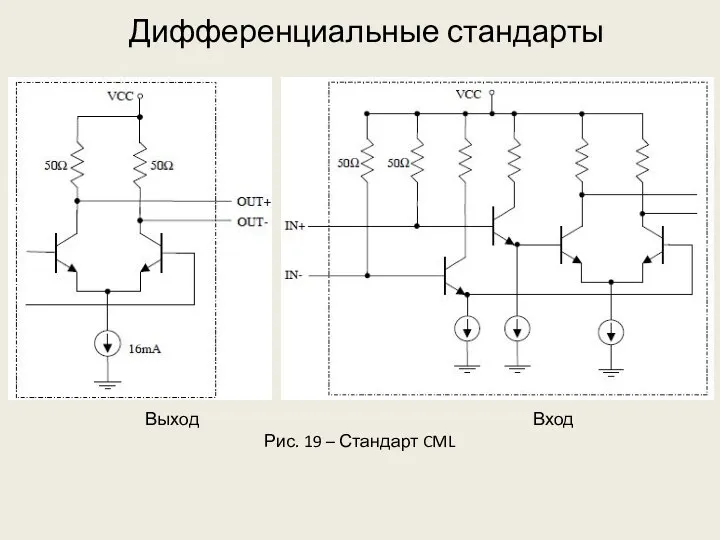

- 19. Дифференциальные стандарты Выход Вход Рис. 19 – Стандарт CML

- 21. Скачать презентацию

PR-Охота! 2010 V Международный форум по связям с общественностью и рекламе Фотоотчет

PR-Охота! 2010 V Международный форум по связям с общественностью и рекламе Фотоотчет Поршневые насосы. (Лекция 4)

Поршневые насосы. (Лекция 4) Великобритания. Лондон

Великобритания. Лондон Валерий Яковлевич Брюсов. Жизнь и творчество

Валерий Яковлевич Брюсов. Жизнь и творчество Презентация на тему "Звіт основні орієнтири 5 клас 2012" - скачать презентации по Педагогике

Презентация на тему "Звіт основні орієнтири 5 клас 2012" - скачать презентации по Педагогике Terrorist scenario - South East Asia

Terrorist scenario - South East Asia Системы связи. Телекоммуникационные сети

Системы связи. Телекоммуникационные сети Презентация Земельные ресурсы

Презентация Земельные ресурсы Презентация____

Презентация____ Гульнара Зимасова

Гульнара Зимасова «Многое из того, что усваивает ученик, забывается, но зато остается привычка определенным образом работать над материалом. Стало б

«Многое из того, что усваивает ученик, забывается, но зато остается привычка определенным образом работать над материалом. Стало б «Забери -Товар». Служба доставки товаров для интернет-магазинов по всей России

«Забери -Товар». Служба доставки товаров для интернет-магазинов по всей России Мать Тереза

Мать Тереза Презентация "К. Ф. Юон" - скачать презентации по МХК

Презентация "К. Ф. Юон" - скачать презентации по МХК Глобальная система электронной коммерции Fohow+

Глобальная система электронной коммерции Fohow+ The 10 most extravagant hats for the Royal Ascot races Royal

The 10 most extravagant hats for the Royal Ascot races Royal …Е121…Е123..Е216…Е217…Е240… Пищевые добавки- полезные, вкусные и запрещённые Московских Анастасия 9 А класс МОУ СОШ № 27 города Белово

…Е121…Е123..Е216…Е217…Е240… Пищевые добавки- полезные, вкусные и запрещённые Московских Анастасия 9 А класс МОУ СОШ № 27 города Белово Равновесие пространственной системы сил. (Лекция 3)

Равновесие пространственной системы сил. (Лекция 3) Памп-трек в г. Дубна

Памп-трек в г. Дубна Презентация Виды международных договоров

Презентация Виды международных договоров  Презентация на тему "Кодекс Классного руководителя" - скачать презентации по Педагогике

Презентация на тему "Кодекс Классного руководителя" - скачать презентации по Педагогике Коррекционно – развивающая работа, направленная на развитие дыхания и голоса Составила Корытко Н.В. учитель-логопед МБОУ «Кард

Коррекционно – развивающая работа, направленная на развитие дыхания и голоса Составила Корытко Н.В. учитель-логопед МБОУ «Кард STH group - лучшие в подборе персонала

STH group - лучшие в подборе персонала Орнаменты египтян

Орнаменты египтян Расширенные возможности многопоточного программирования. Лекция 1

Расширенные возможности многопоточного программирования. Лекция 1 Новые поступления (март)

Новые поступления (март) Мікропроцесорна техніка (лекція 6)

Мікропроцесорна техніка (лекція 6) Русский язык «Прилагательные-синонимы и прилагательные-антонимы» 3 класс Т.Г.Рамзаева

Русский язык «Прилагательные-синонимы и прилагательные-антонимы» 3 класс Т.Г.Рамзаева