Цифровая схемотехника и архитектура компьютера. Проектирование последовательностной логики. (Глава 3)

Содержание

- 2. Цифровая схемотехника и архитектура компьютера Эти слайды предназначены для преподавателей, которые читают лекции на основе учебника

- 3. Благодарности Перевод данных слайдов на русский язык был выполнен командой сотрудников университетов и компаний из России,

- 4. Глава 3 :: Темы Введение Защелки и Триггеры Проектирование синхронных логических схем Конечные автоматы Синхронизация последовательностных

- 5. Выходы последовательностной схемы зависят как от текущих, так и от прошлых значений на входах - схема

- 6. Выдают последовательность событий Имеют (краткосрочную) память Для сохранения информации используют обратную связь с выходов на входы

- 7. Состояние схемы влияет на ее будущее поведение Элементы хранят состояние схемы Бистабильная схема RS-триггер D-защелка D-триггер

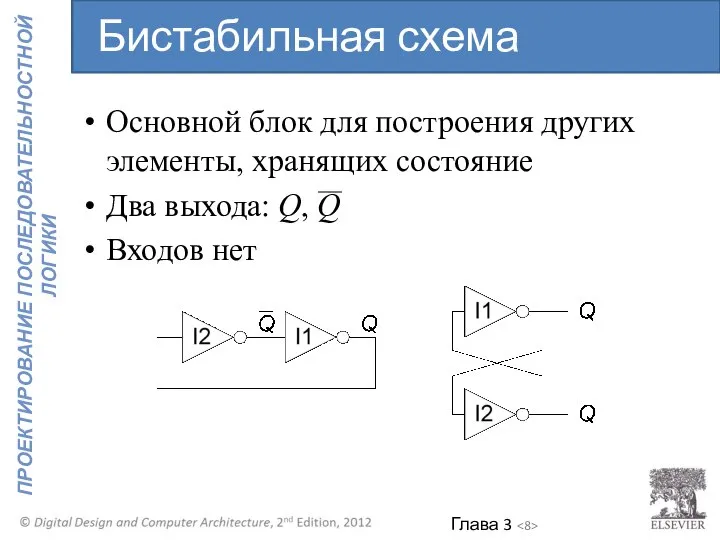

- 8. Основной блок для построения других элементы, хранящих состояние Два выхода: Q, Q Входов нет Бистабильная схема

- 9. Рассмотрим два возможных случая: Q = 0: Тогда Q = 1, Q = 0 (нет противоречия)

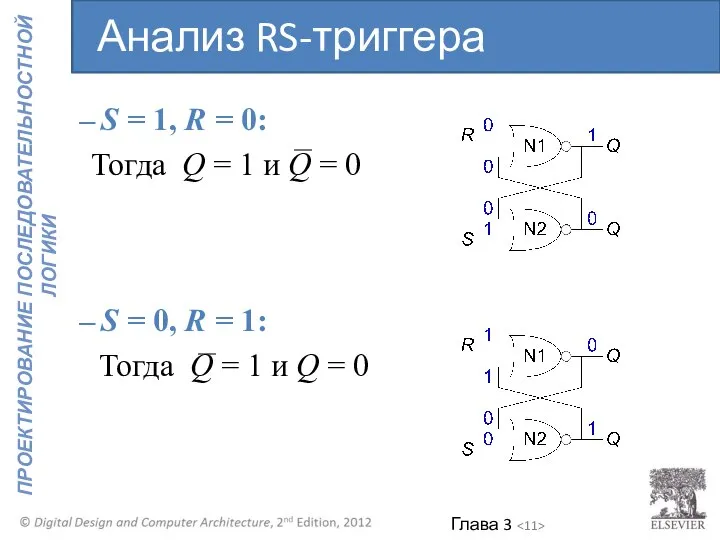

- 10. RS-триггер Рассмотрим четыре возможные случая: S = 1, R = 0 S = 0, R =

- 11. S = 1, R = 0: Тогда Q = 1 и Q = 0 S =

- 12. S = 0, R = 0: Тогда Q = Qprev S = 1, R = 1:

- 13. S = 0, R = 0: Тогда Q = Qprev Память! S = 1, R =

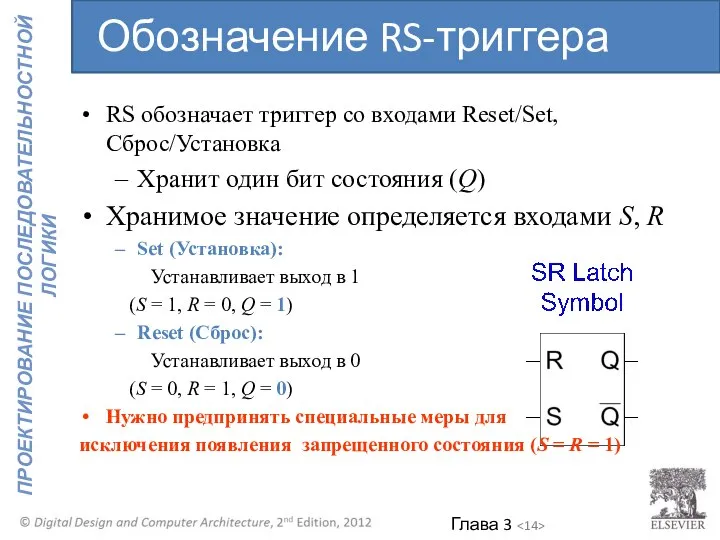

- 14. RS обозначает триггер со входами Reset/Set, Сброс/Установка Хранит один бит состояния (Q) Хранимое значение определяется входами

- 15. Два входа CLK, D CLK: определяет когда выход изменяется D (вход данных): определяет новое значение выхода

- 16. Внутренняя структура D защелки

- 17. Внутренняя структура D защелки

- 18. Входы: CLK, D Работа Фиксирует значение D по переднему фронту CLK Когда CLK изменяется от 0

- 19. Две последовательно соединенные защелки (L1 и L2), которые управляются комплементарными тактовыми сигналами Когда CLK = 0

- 20. Сравнение D-защелки и D-триггера

- 21. Сравнение D-защелки и D-триггера

- 22. Регистры

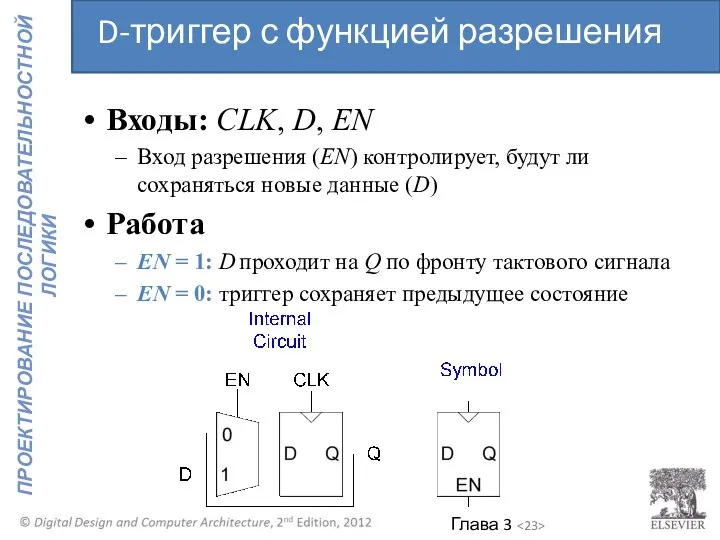

- 23. Входы: CLK, D, EN Вход разрешения (EN) контролирует, будут ли сохраняться новые данные (D) Работа EN

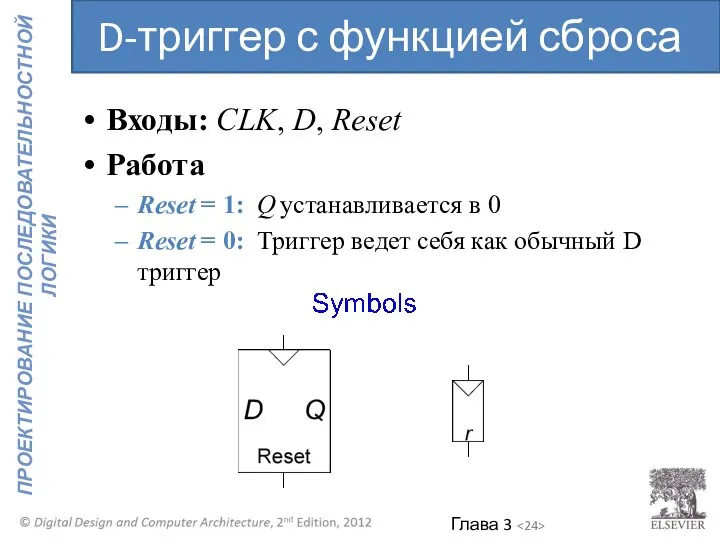

- 24. Входы: CLK, D, Reset Работа Reset = 1: Q устанавливается в 0 Reset = 0: Триггер

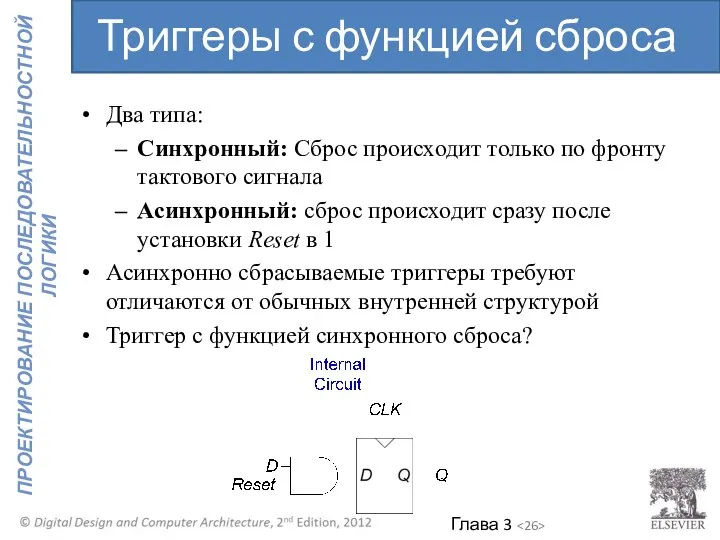

- 25. Два типа: Синхронный: Сброс происходит только по фронту тактового сигнала Асинхронный: сброс происходит сразу после установки

- 26. Два типа: Синхронный: Сброс происходит только по фронту тактового сигнала Асинхронный: сброс происходит сразу после установки

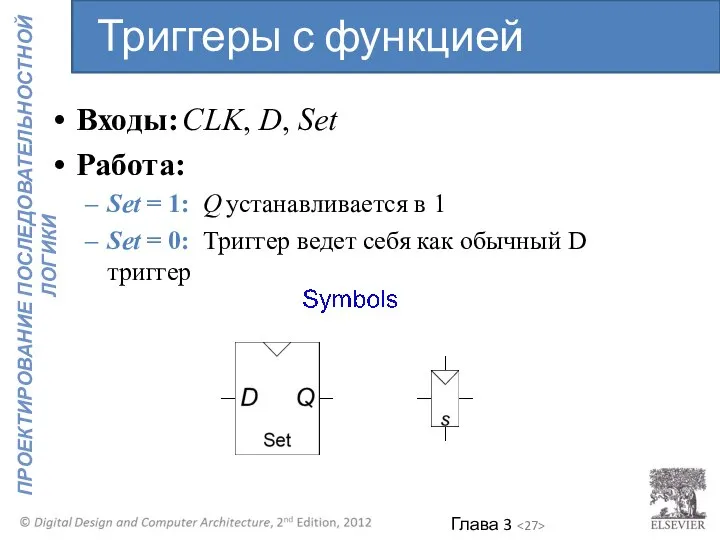

- 27. Входы: CLK, D, Set Работа: Set = 1: Q устанавливается в 1 Set = 0: Триггер

- 28. Последовательностные схемы - все схемы, которые не являются комбинационными Проблемная схема: Последовательностные цифровые схемы

- 29. Последовательностные схемы - все схемы, которые не являются комбинационными Проблемная схема: Входов нет, выходов 3 Нестабильная

- 30. Разрушение циклических путей с путем добавления регистров Регистры сохраняет состояние схемы Состояние изменяется по фронтам тактового

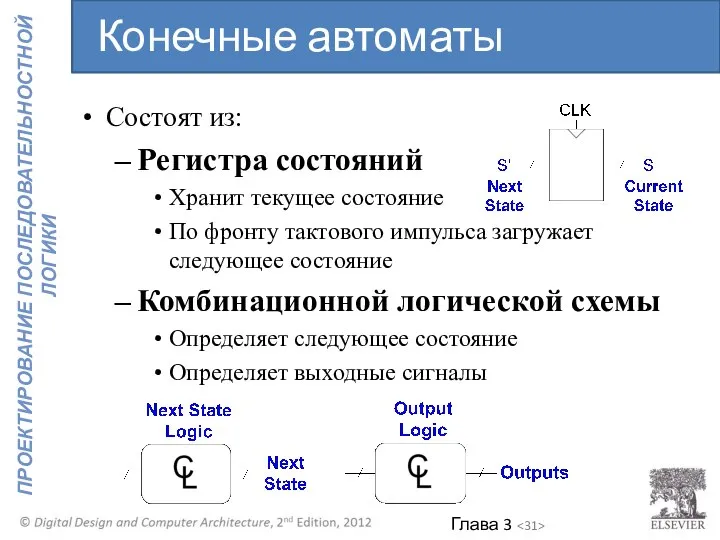

- 31. Состоят из: Регистра состояний Хранит текущее состояние По фронту тактового импульса загружает следующее состояние Комбинационной логической

- 32. Следующее состояние определяется входами и текущим состоянием Два класса конечных автоматов отличаются логикой определения выходных сигналов:

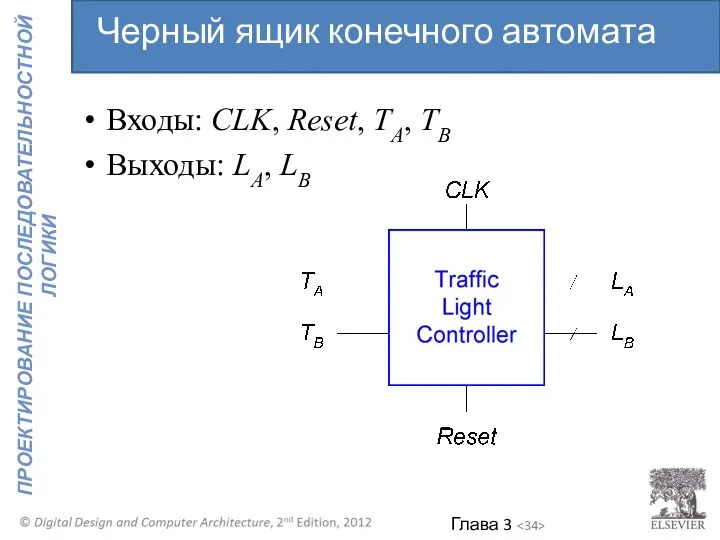

- 33. Система управления светофором Датчики движения: TA, TB (ИСТИНА, когда на улице есть студенты) Светофоры: LA, LB

- 34. Входы: CLK, Reset, TA, TB Выходы: LA, LB Черный ящик конечного автомата

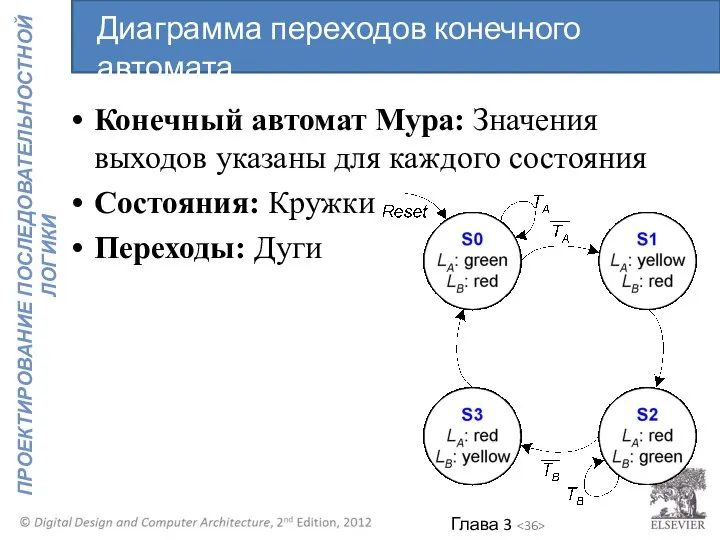

- 35. Конечный автомат Мура: Значения выходов указаны для каждого состояния Состояния: Кружки Переходы: Дуги Диаграмма переходов конечного

- 36. Конечный автомат Мура: Значения выходов указаны для каждого состояния Состояния: Кружки Переходы: Дуги Диаграмма переходов конечного

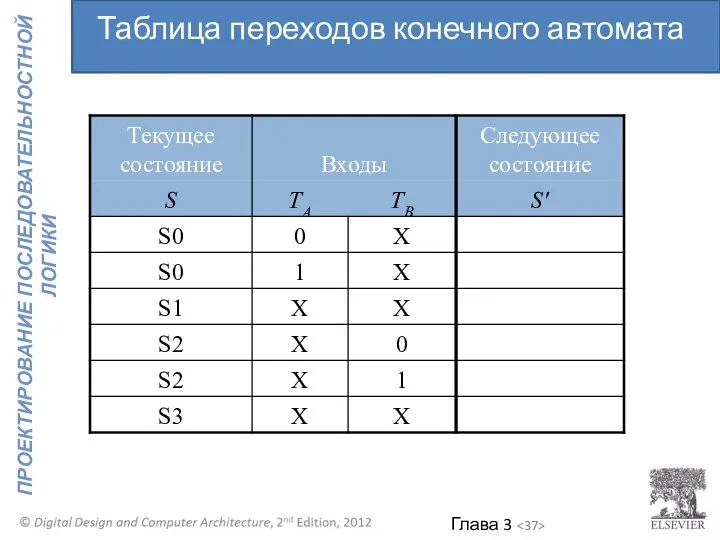

- 37. Таблица переходов конечного автомата

- 38. Таблица переходов конечного автомата

- 39. Таблица переходов конечного автомата с указанием кодирования

- 40. S'1 = S1 ⊕ S0 S'0 = S1S0TA + S1S0TB Таблица переходов конечного автомата с указанием

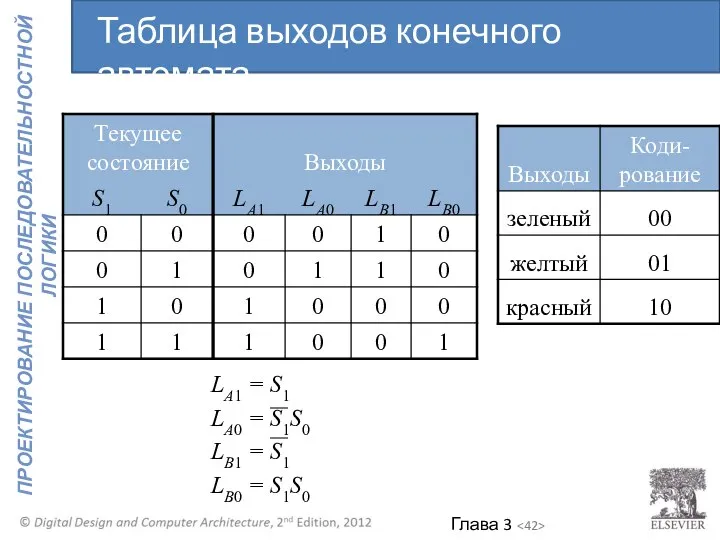

- 41. Таблица выходов конечного автомата

- 42. LA1 = S1 LA0 = S1S0 LB1 = S1 LB0 = S1S0 Таблица выходов конечного автомата

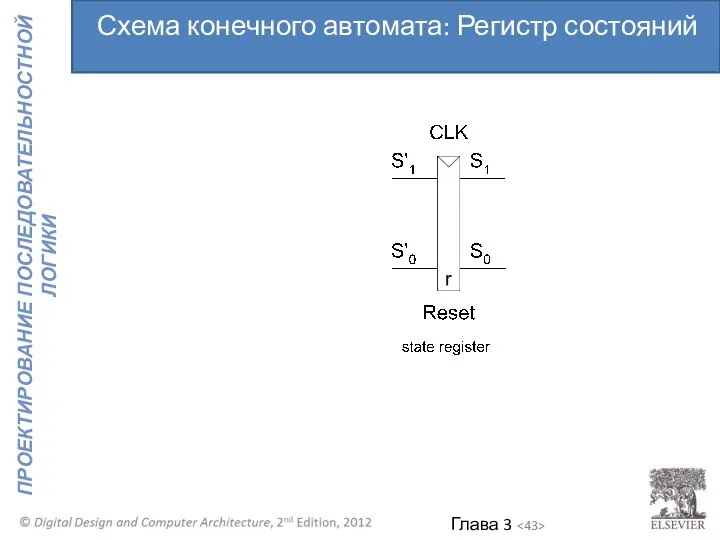

- 43. Схема конечного автомата: Регистр состояний

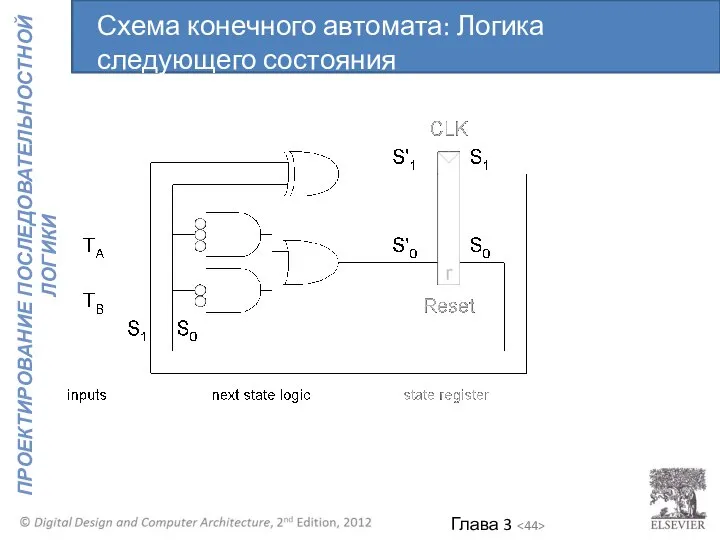

- 44. Схема конечного автомата: Логика следующего состояния

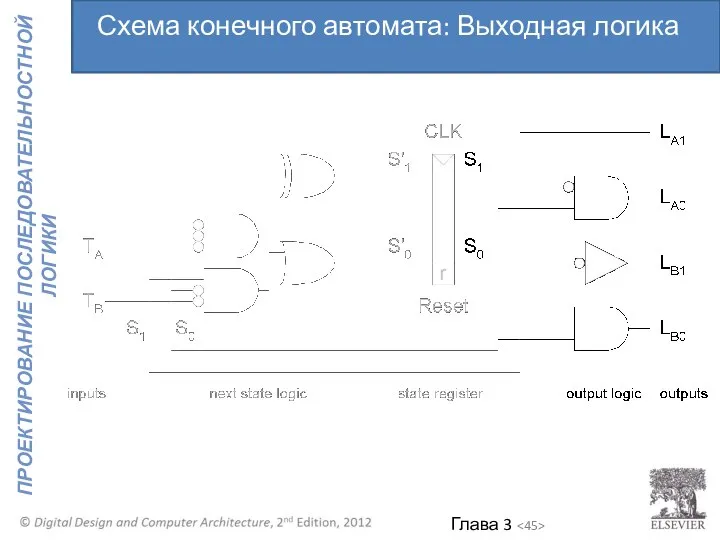

- 45. Схема конечного автомата: Выходная логика

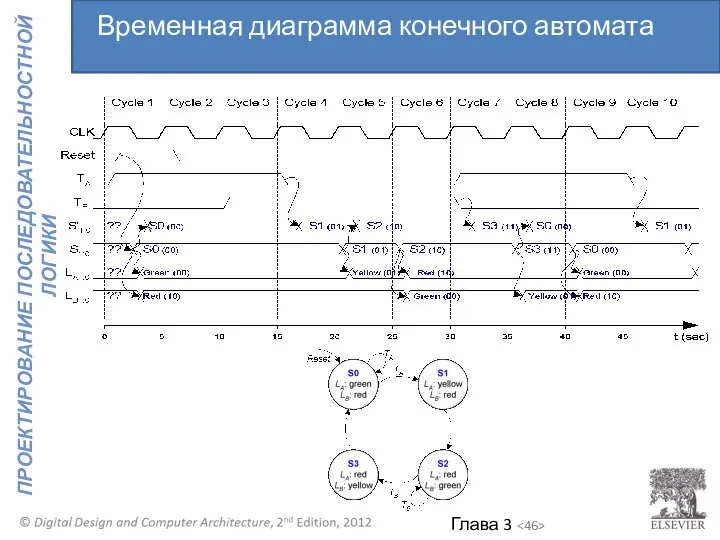

- 46. Временная диаграмма конечного автомата

- 47. Двоичное кодирование: Для четырех состояний: 00, 01, 10, 11 Прямое (One-hot) кодирование На каждое состояние один

- 48. У Алисы есть улитка, которая ползает по перфоленте, содержащей последовательность нулей и единиц. Улитка улыбается, если

- 49. Конечный автомат Мили: около дуг указаны значения входов/выходов Диаграмма переходов

- 50. Таблица переходов конечного автомата Мура

- 51. Таблица переходов конечного автомата Мура S1’ = S0A S0’ = A

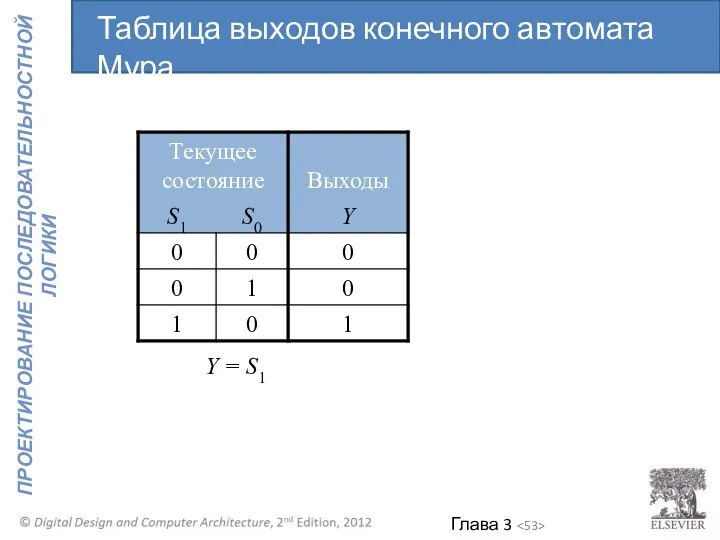

- 52. Y = S1 Таблица выходов конечного автомата Мура

- 53. Y = S1 Таблица выходов конечного автомата Мура

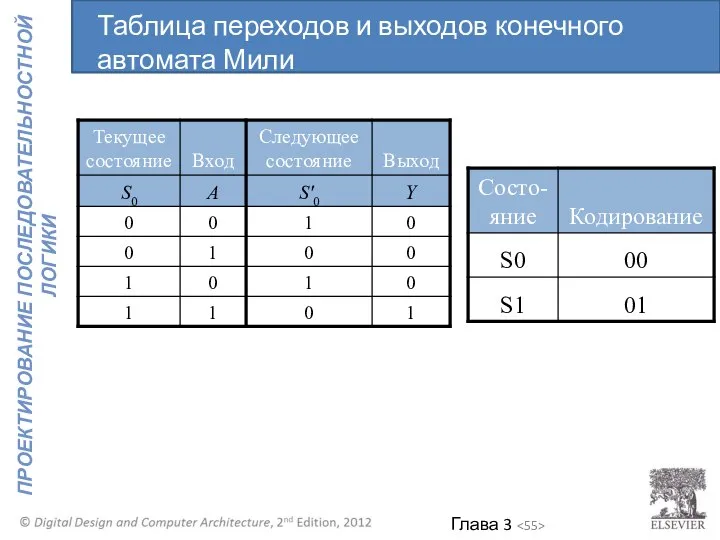

- 54. Таблица переходов и выходов конечного автомата Мили

- 55. Таблица переходов и выходов конечного автомата Мили

- 56. Схема конечного автомата Мура

- 57. Схема конечного автомата Мили

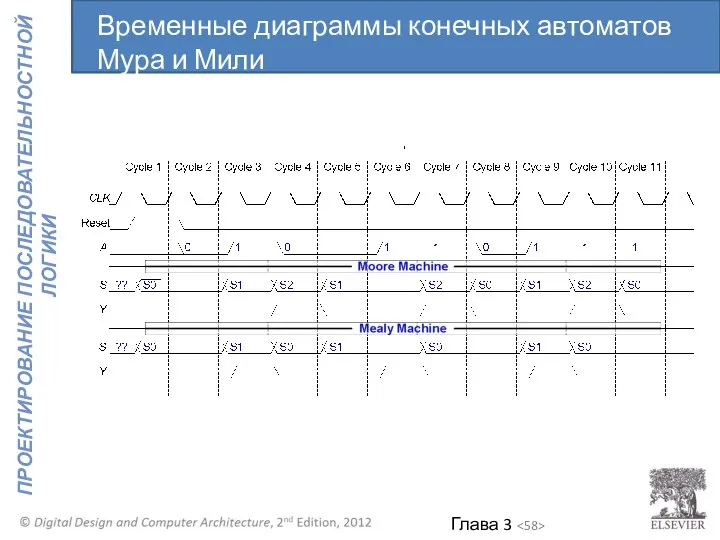

- 58. Временные диаграммы конечных автоматов Мура и Мили

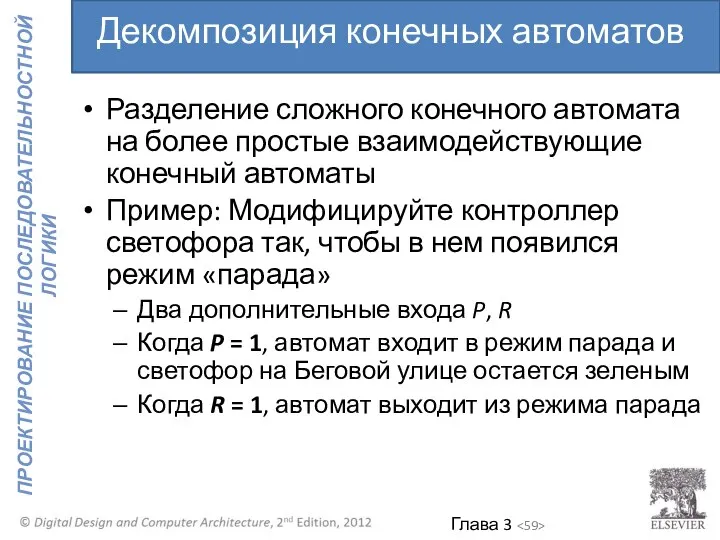

- 59. Разделение сложного конечного автомата на более простые взаимодействующие конечный автоматы Пример: Модифицируйте контроллер светофора так, чтобы

- 60. Немодульный конечный автомат Модульный конечный автомат Модифицированный конечный автомат

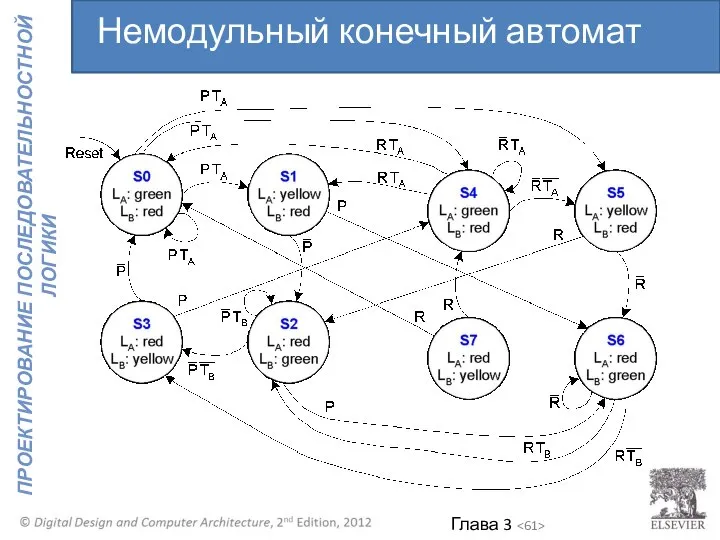

- 61. Немодульный конечный автомат

- 62. Модульный конечный автомат

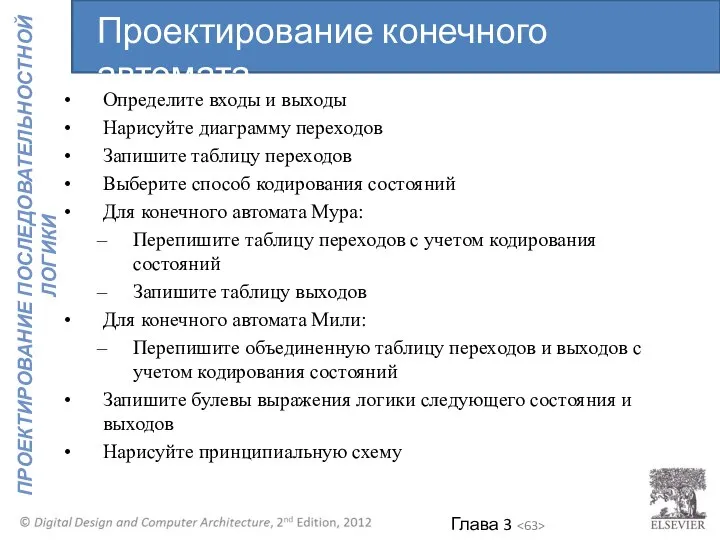

- 63. Определите входы и выходы Нарисуйте диаграмму переходов Запишите таблицу переходов Выберите способ кодирования состояний Для конечного

- 64. Триггер фиксирует сигнал D по фронту тактового сигнала Сигнал D должен быть стабильным в процессе фиксации

- 65. Время предустановки: tsetup = период времени перед фронтом тактового сигнала, в течении которого данные должны быть

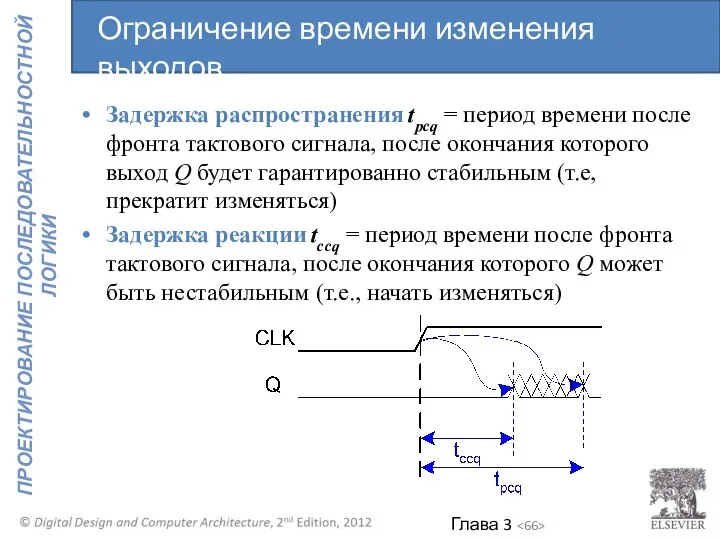

- 66. Задержка распространения tpcq = период времени после фронта тактового сигнала, после окончания которого выход Q будет

- 67. Входы синхронной последовательностной схемы должны быть стабильны в течение апертурного времени в окрестности фронта тактового сигнала

- 68. В зависимости от задержек элементов, общая задержка между регистрами лежит между максимальным и минимальным значениями Динамическая

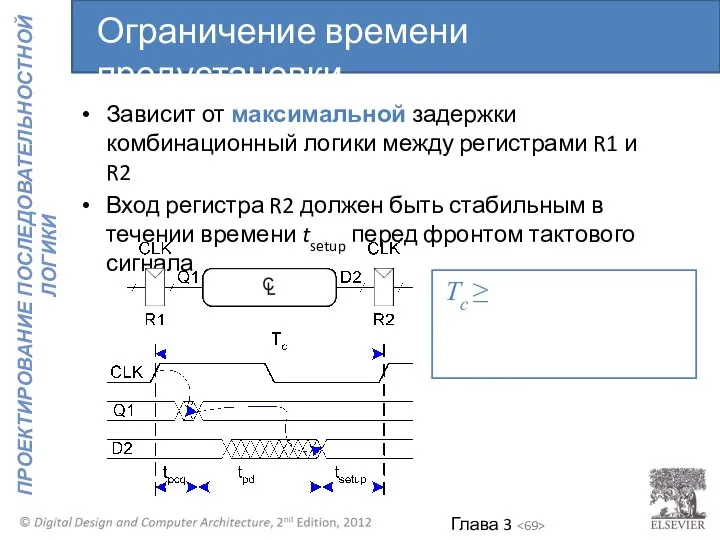

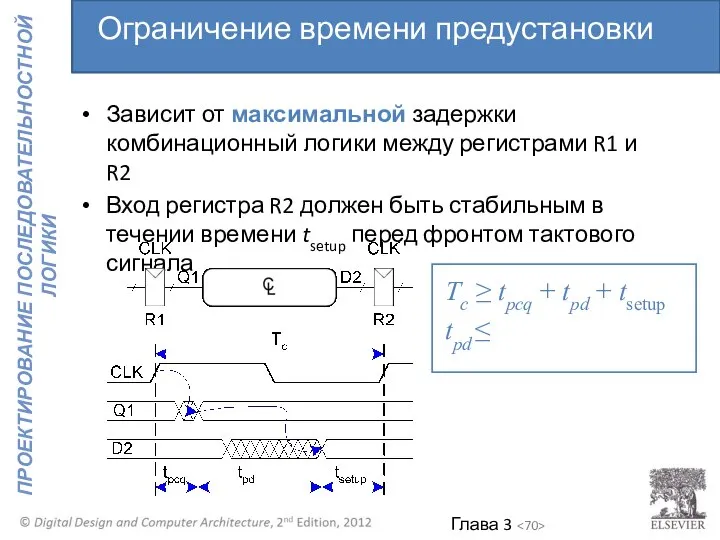

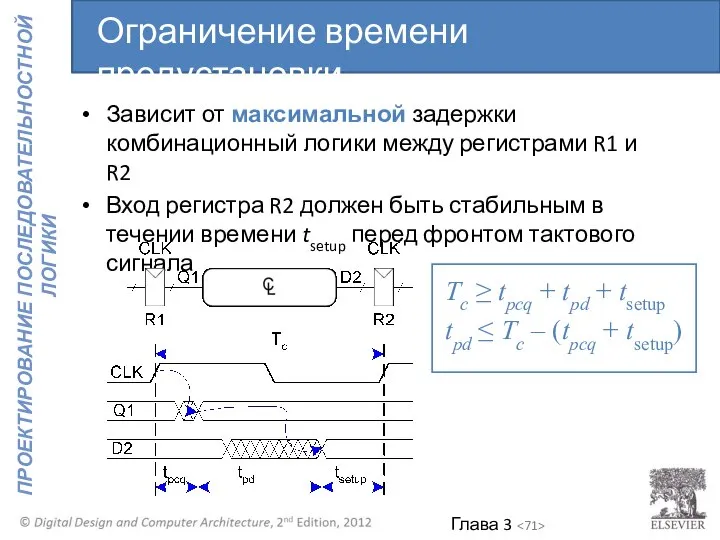

- 69. Зависит от максимальной задержки комбинационный логики между регистрами R1 и R2 Вход регистра R2 должен быть

- 70. Зависит от максимальной задержки комбинационный логики между регистрами R1 и R2 Вход регистра R2 должен быть

- 71. Зависит от максимальной задержки комбинационный логики между регистрами R1 и R2 Вход регистра R2 должен быть

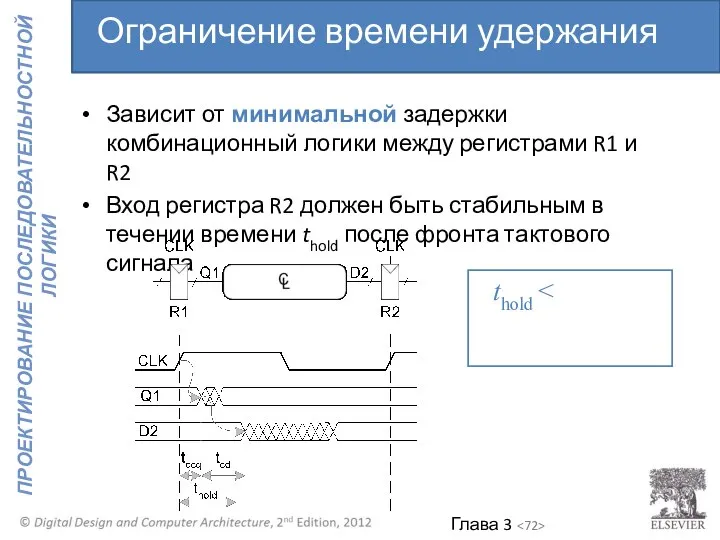

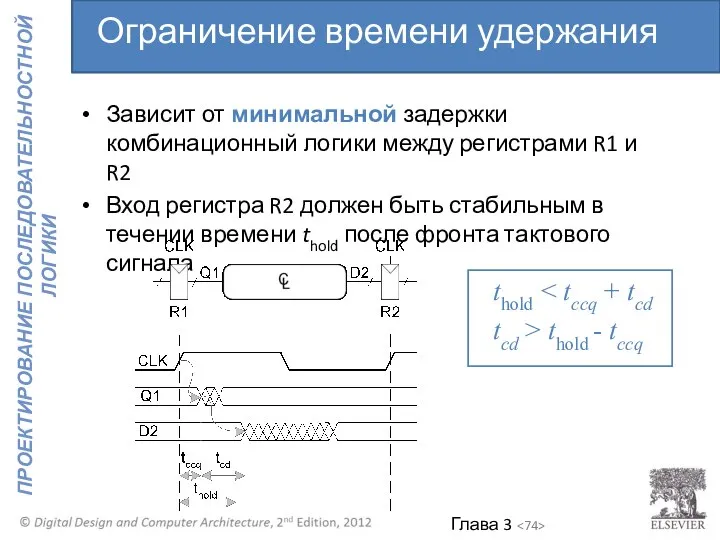

- 72. Зависит от минимальной задержки комбинационный логики между регистрами R1 и R2 Вход регистра R2 должен быть

- 73. Зависит от минимальной задержки комбинационный логики между регистрами R1 и R2 Вход регистра R2 должен быть

- 74. Зависит от минимальной задержки комбинационный логики между регистрами R1 и R2 Вход регистра R2 должен быть

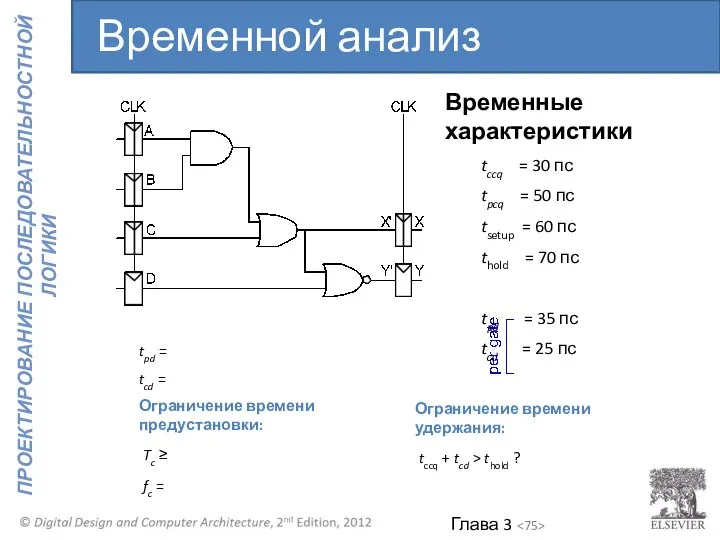

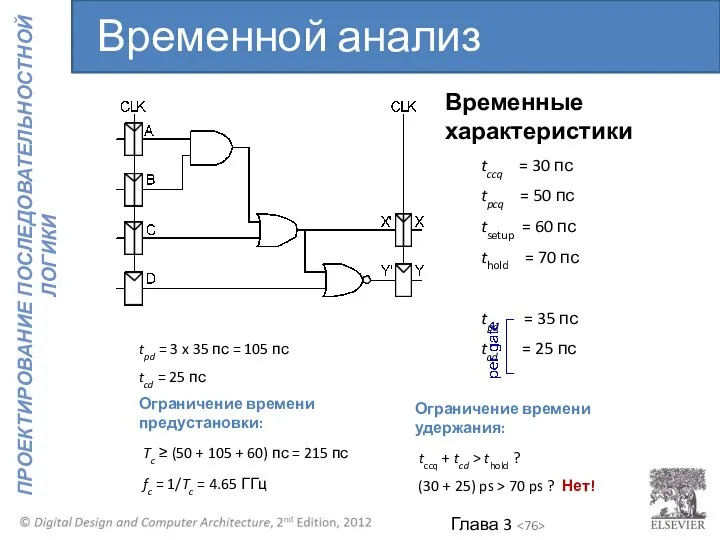

- 75. Временные характеристики tccq = 30 пс tpcq = 50 пс tsetup = 60 пс thold =

- 76. Временные характеристики tccq = 30 пс tpcq = 50 пс tsetup = 60 пс thold =

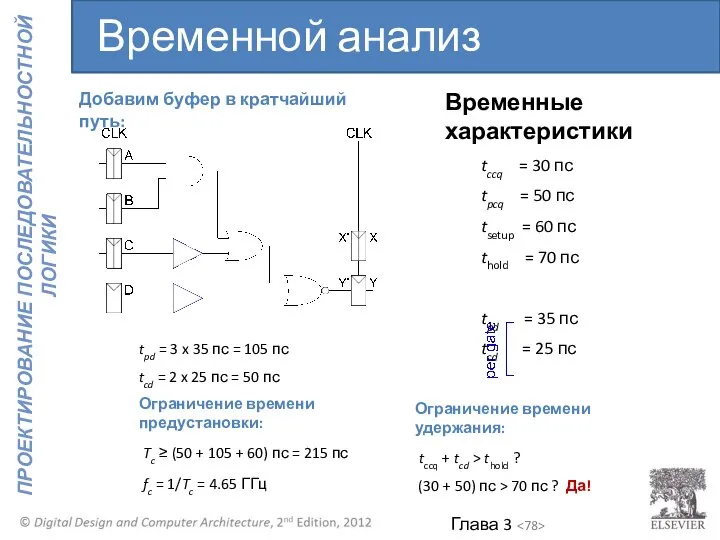

- 77. Временные характеристики tccq = 30 пс tpcq = 50 пс tsetup = 60 пс thold =

- 78. Временные характеристики tccq = 30 пс tpcq = 50 пс tsetup = 60 пс thold =

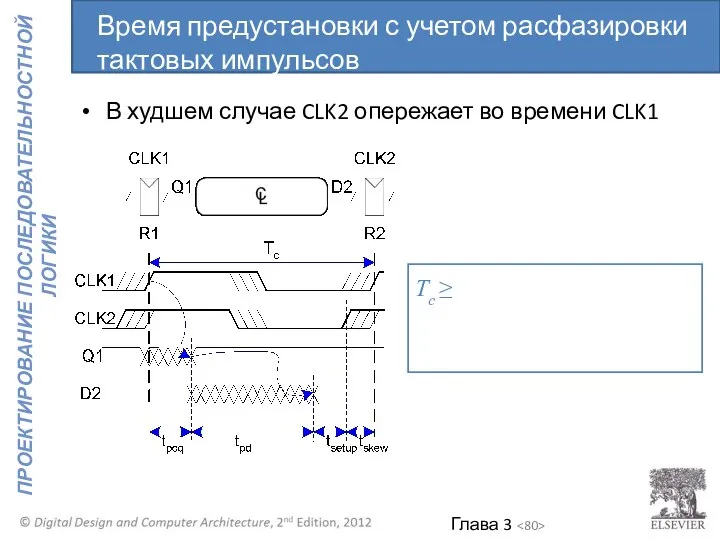

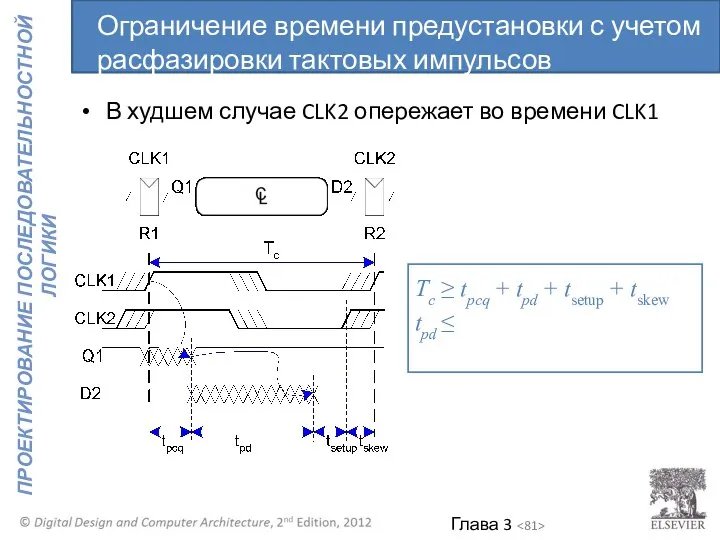

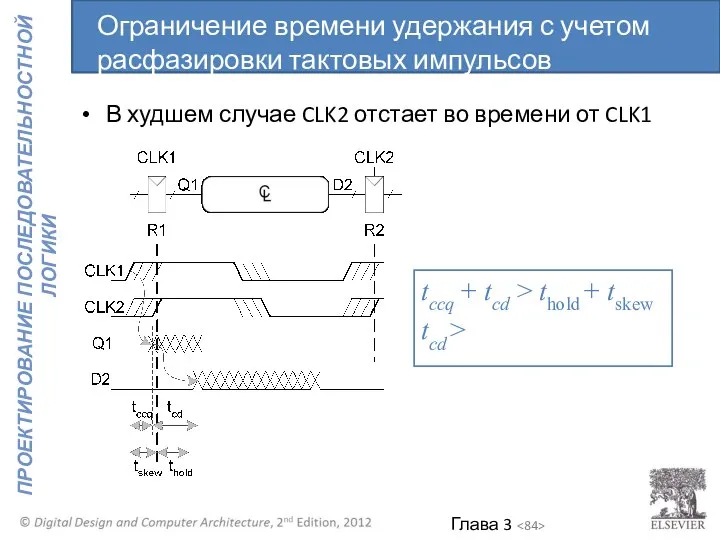

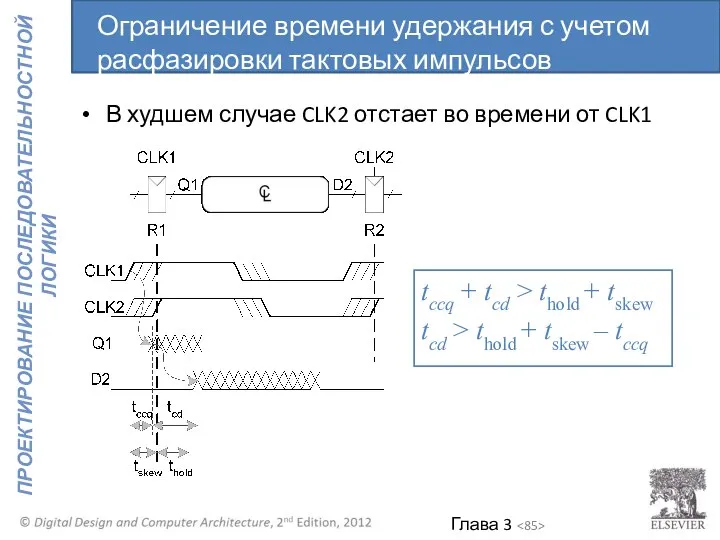

- 79. Тактовые импульсы поступают на разные регистры схемы не одновременно Расфазировка: различие во времени между фронтами тактовых

- 80. В худшем случае CLK2 опережает во времени CLK1 Tc ≥ Время предустановки с учетом расфазировки тактовых

- 81. В худшем случае CLK2 опережает во времени CLK1 Tc ≥ tpcq + tpd + tsetup +

- 82. В худшем случае CLK2 опережает во времени CLK1 Tc ≥ tpcq + tpd + tsetup +

- 83. В худшем случае CLK2 отстает во времени от CLK1 tccq + tcd > Ограничение времени удержания

- 84. В худшем случае CLK2 отстает во времени от CLK1 tccq + tcd > thold + tskew

- 85. В худшем случае CLK2 отстает во времени от CLK1 tccq + tcd > thold + tskew

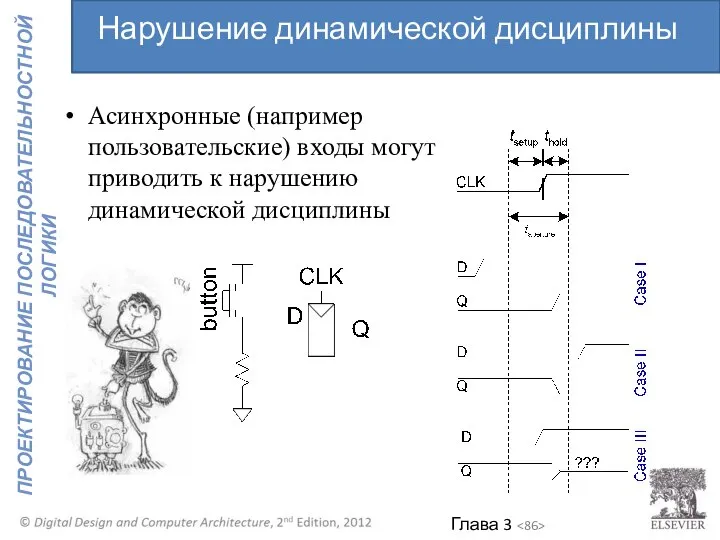

- 86. Асинхронные (например пользовательские) входы могут приводить к нарушению динамической дисциплины Нарушение динамической дисциплины

- 87. Бистабильные приборы: два стабильные состояния и метастабильное состояние между ними Триггер два стабильные состояния (0 и

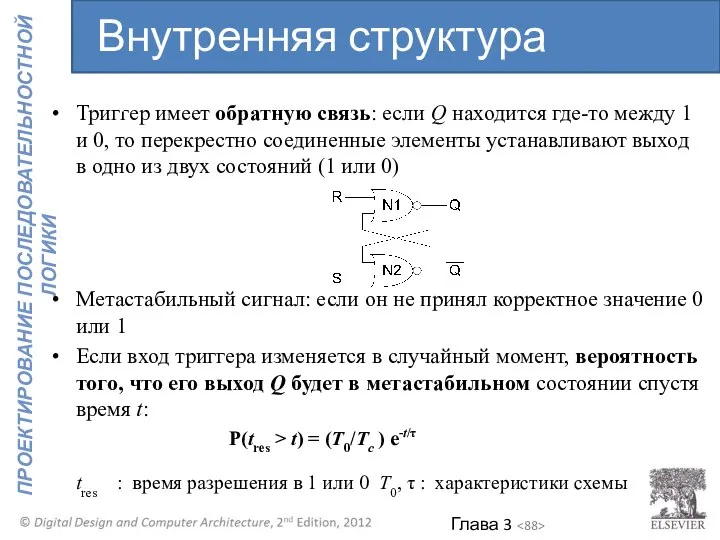

- 88. Триггер имеет обратную связь: если Q находится где-то между 1 и 0, то перекрестно соединенные элементы

- 89. Интуитивно: T0/Tc: вероятность изменения входа в плохое (апертурное) время P(tres > t) = (T0/Tc ) e-t/τ

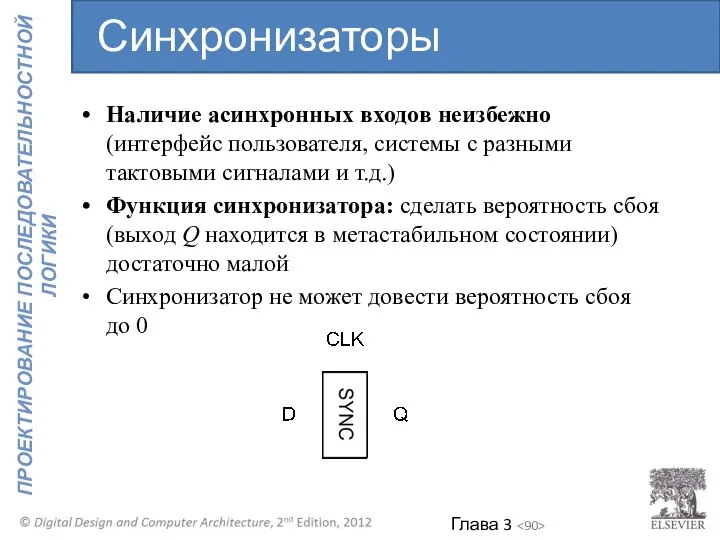

- 90. Наличие асинхронных входов неизбежно (интерфейс пользователя, системы с разными тактовыми сигналами и т.д.) Функция синхронизатора: сделать

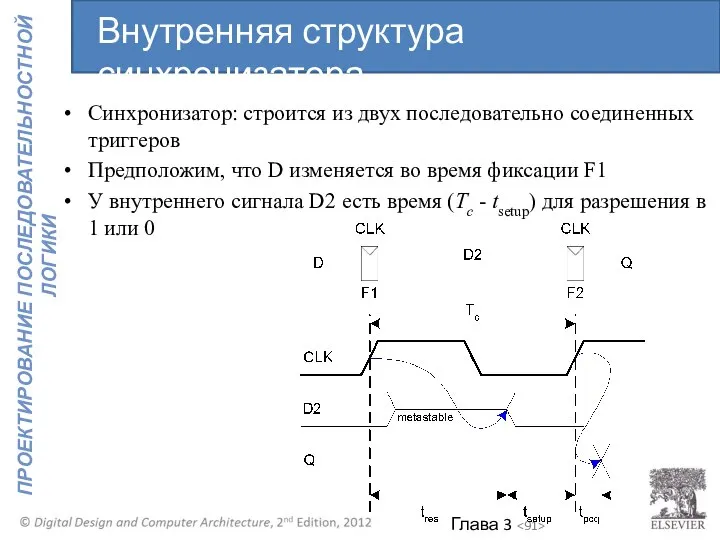

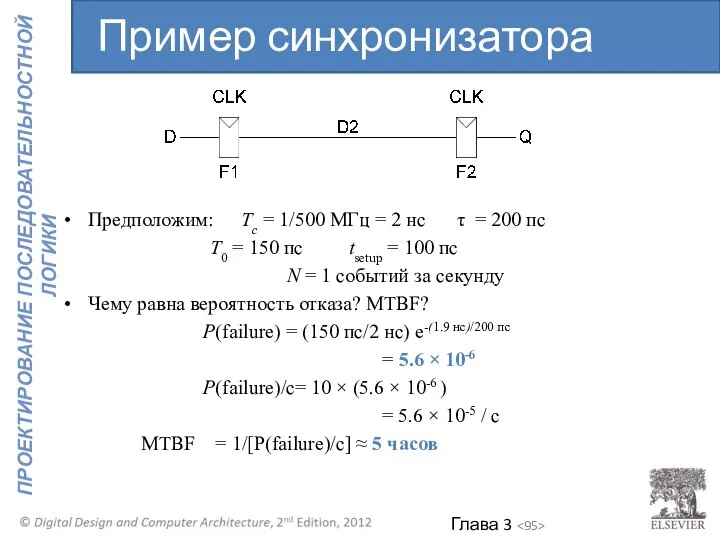

- 91. Синхронизатор: строится из двух последовательно соединенных триггеров Предположим, что D изменяется во время фиксации F1 У

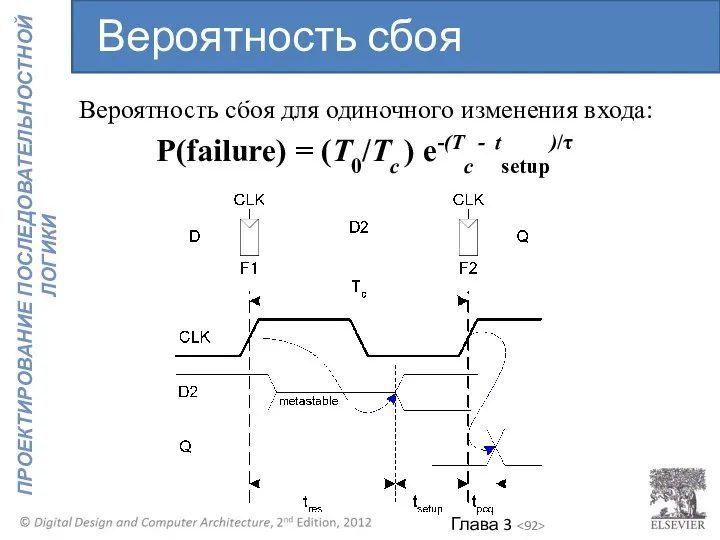

- 92. Вероятность сбоя для одиночного изменения входа: P(failure) = (T0/Tc ) e-(Tc - tsetup)/τ Вероятность сбоя синхронизатора

- 93. Если асинхронный вход изменяется один раз за секунду, то вероятность сбоя за одну секунду будет равна

- 94. Предположим: Tc = 1/500 МГц = 2 нс τ = 200 пс T0 = 150 пс

- 95. Предположим: Tc = 1/500 МГц = 2 нс τ = 200 пс T0 = 150 пс

- 96. Два типа параллелизма: Пространственный параллелизм: несколько копий аппаратных блоков в одно и то же время выполняют

- 97. Токен (Token): Набор входной информации, который обрабатывается для того, чтобы получить выходную информацию Латентность (latency): Время

- 98. Бен готовит печенье для вечеринки, посвященной введению в эксплуатацию его контроллера светофора 5 минут уходит на

- 99. Бен готовит печенье для вечеринки, посвященной введению в эксплуатацию его контроллера светофора 5 минут уходит на

- 100. Чему равна пропускная способность и задержка если Бен использует параллелизма? Пространственный параллелизм: Бен просит Алису помочь,

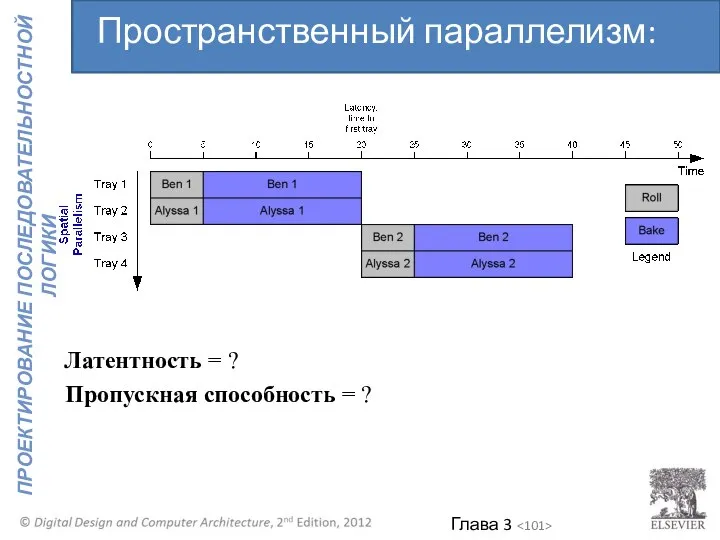

- 101. Латентность = ? Пропускная способность = ? Пространственный параллелизм:

- 102. Латентность = 5 + 15 = 20 минут = 1/3 час Пропускная способность = 2 противня/

- 103. Латентность = ? Пропускная способность = ? Временной параллелизм

- 105. Скачать презентацию

История и правила игры в футбол

История и правила игры в футбол Источники и ресурсы власти

Источники и ресурсы власти Қазақстандық модельерлер миланда

Қазақстандық модельерлер миланда Презентация "Основы восточного мировоззрения в бумагопластике" - скачать презентации по МХК

Презентация "Основы восточного мировоззрения в бумагопластике" - скачать презентации по МХК "Фантазия важнее знаний" А. Эйнштейн

"Фантазия важнее знаний" А. Эйнштейн  Раннее христианство. Гомилетика. Риторика и христианство

Раннее христианство. Гомилетика. Риторика и христианство Особенности регулирования труда женщин и лиц с семейными обязанностями

Особенности регулирования труда женщин и лиц с семейными обязанностями Де козак там і слава

Де козак там і слава Оценка деятельности предприятия на примере ООО «Магистраль»

Оценка деятельности предприятия на примере ООО «Магистраль» Профилактика болезней сердца

Профилактика болезней сердца Презентация на тему "Методика проведения учебного занятия в системе дополнительного образования" - скачать презентации по Пе

Презентация на тему "Методика проведения учебного занятия в системе дополнительного образования" - скачать презентации по Пе Биография Жака Превера

Биография Жака Превера Презентация "Маркетинговая среда" - скачать презентации по Экономике

Презентация "Маркетинговая среда" - скачать презентации по Экономике Ардуино. Микроконтроллер

Ардуино. Микроконтроллер Презентация Концепция долгосрочного социально-экономического развития Российской Федерации на период до 2020 года о таможенной де

Презентация Концепция долгосрочного социально-экономического развития Российской Федерации на период до 2020 года о таможенной де Муниципальное образовательное учреждение Глебовская средняя общеобразовательная школа Из опыта работы учителя русского языка и

Муниципальное образовательное учреждение Глебовская средняя общеобразовательная школа Из опыта работы учителя русского языка и Алгоритмы и формулы аналитической геометрии

Алгоритмы и формулы аналитической геометрии Сортировка массива (pascal)

Сортировка массива (pascal) Адаптация учащихся в предметной учебной деятельности формированием понятийного аппарата, или Как овладеть языком предмета - през

Адаптация учащихся в предметной учебной деятельности формированием понятийного аппарата, или Как овладеть языком предмета - през День инвестора Центральной и Восточной Европы (IDCEE) Интернет-технологии и инновации 25-26 октября, 2011 Киев, Украина

День инвестора Центральной и Восточной Европы (IDCEE) Интернет-технологии и инновации 25-26 октября, 2011 Киев, Украина НАЛОГООБЛОЖЕНИЕ НЕКОММЕРЧЕСКИХ ОРГАНИЗАЦИЙ СМИРНОВА ЕЛЕНА ЕВГЕНЬЕВНА – к.э.н., доцент

НАЛОГООБЛОЖЕНИЕ НЕКОММЕРЧЕСКИХ ОРГАНИЗАЦИЙ СМИРНОВА ЕЛЕНА ЕВГЕНЬЕВНА – к.э.н., доцент Учитель начальных классов: Фогель С.С. МОБУ «Лицей №5» Оренбург- 2012г.

Учитель начальных классов: Фогель С.С. МОБУ «Лицей №5» Оренбург- 2012г. Степень с натуральным показателем - презентация по Алгебре__

Степень с натуральным показателем - презентация по Алгебре__ «Наука побеждать» Автор: Кругляков Александр 3 класс

«Наука побеждать» Автор: Кругляков Александр 3 класс Посреднические договоры

Посреднические договоры Презентация на тему "Аристотель. Педагогические идеи" - скачать презентации по Педагогике

Презентация на тему "Аристотель. Педагогические идеи" - скачать презентации по Педагогике Герои легенд. Игра

Герои легенд. Игра Экономические закономерности Жуйкова Л.Д., преподаватель КГБОУ НПО «Профессиональный лицей № 67»

Экономические закономерности Жуйкова Л.Д., преподаватель КГБОУ НПО «Профессиональный лицей № 67»