Содержание

- 2. Цифровая схемотехника и архитектура компьютера Эти слайды предназначены для преподавателей, которые читают лекции на основе учебника

- 3. Благодарности Перевод данных слайдов на русский язык был выполнен командой сотрудников университетов и компаний из России,

- 4. Глава 4 : Темы Введение Комбинационная логика Структурное моделирование Последовательностная логика И снова комбинационная логика Конечные

- 5. Языки описания аппаратуры (HDL): Определяют функциональность проектируемого устройства Средства САПР синтезируют оптимизированные схему устройства, состоящую из

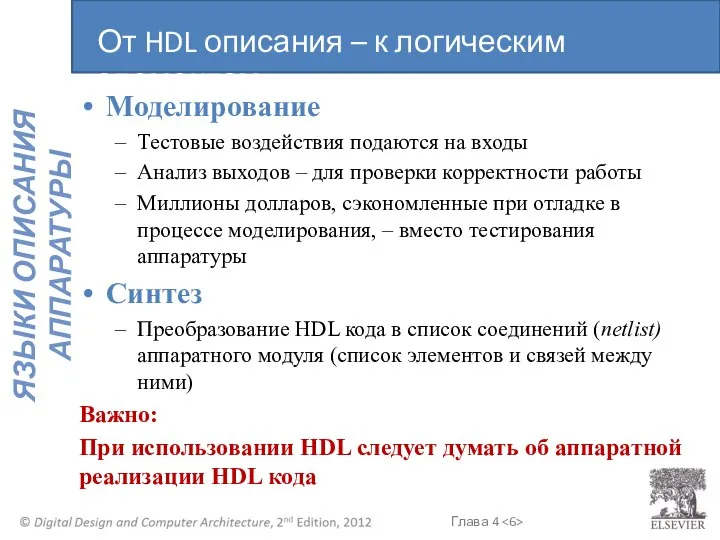

- 6. Моделирование Тестовые воздействия подаются на входы Анализ выходов – для проверки корректности работы Миллионы долларов, сэкономленные

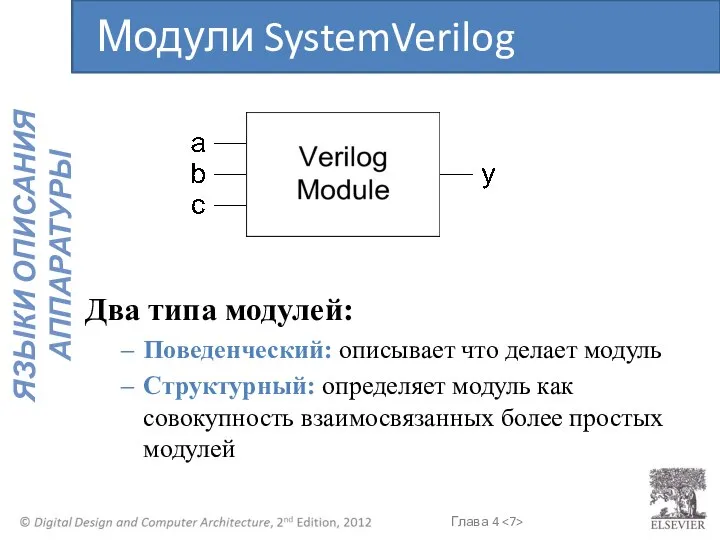

- 7. Два типа модулей: Поведенческий: описывает что делает модуль Структурный: определяет модуль как совокупность взаимосвязанных более простых

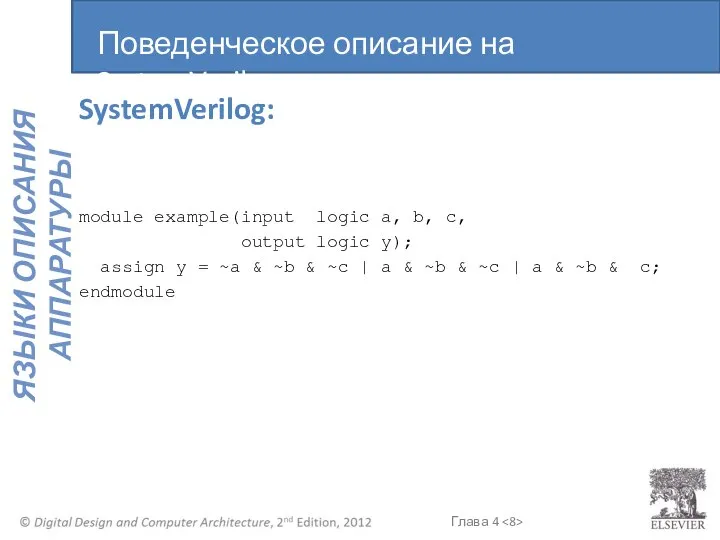

- 8. module example(input logic a, b, c, output logic y); assign y = ~a & ~b &

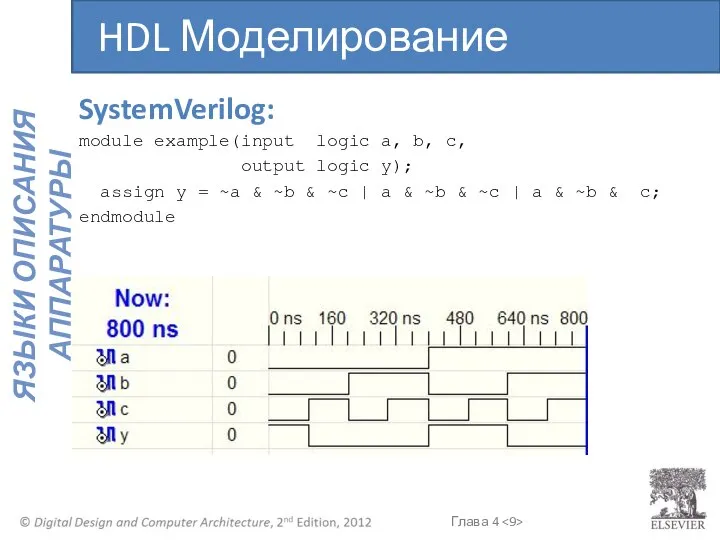

- 9. HDL Моделирование module example(input logic a, b, c, output logic y); assign y = ~a &

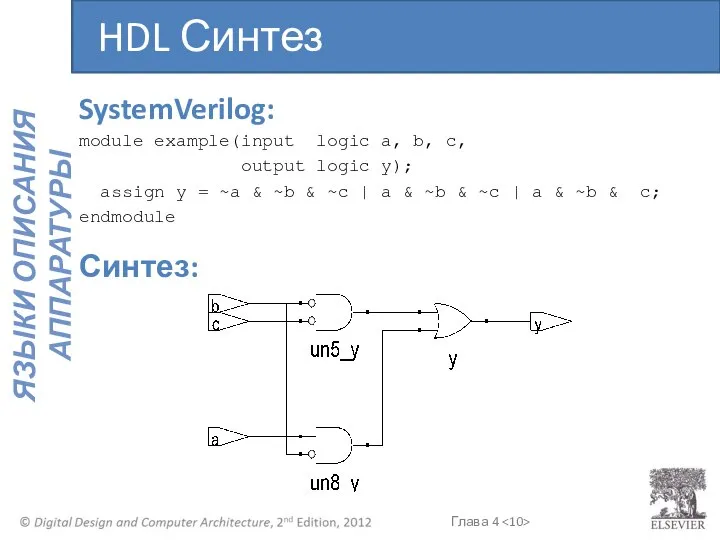

- 10. HDL Синтез module example(input logic a, b, c, output logic y); assign y = ~a &

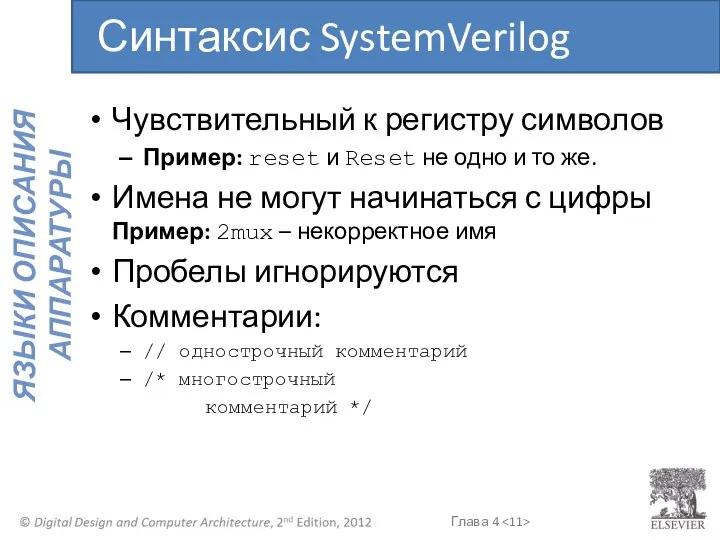

- 11. Чувствительный к регистру символов Пример: reset и Reset не одно и то же. Имена не могут

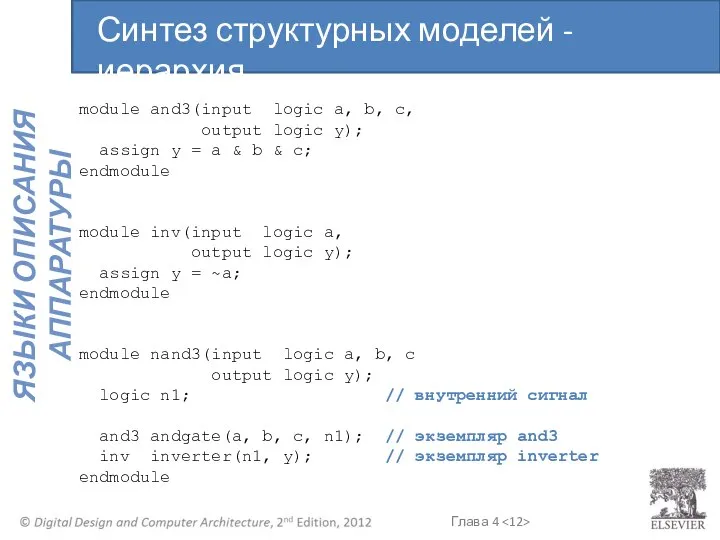

- 12. module and3(input logic a, b, c, output logic y); assign y = a & b &

- 13. module gates(input logic [3:0] a, b, output logic [3:0] y1, y2, y3, y4, y5); /* Five

- 14. module and8(input logic [7:0] a, output logic y); assign y = &a; // &a is much

- 15. module mux2(input logic [3:0] d0, d1, input logic s, output logic [3:0] y); assign y =

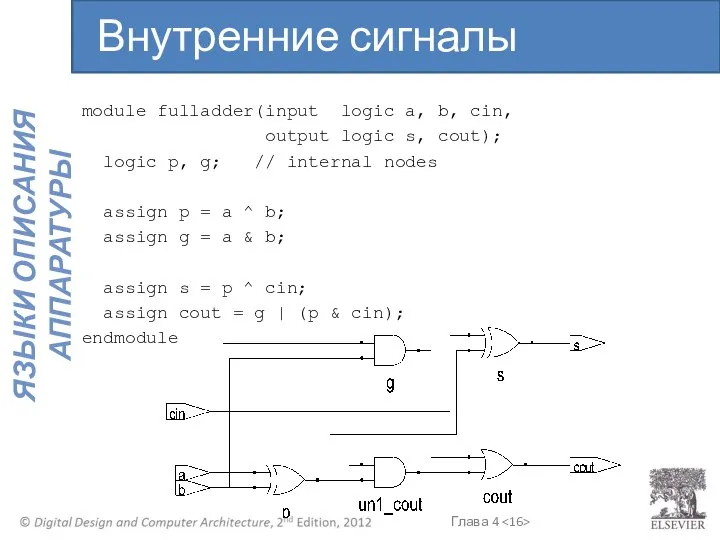

- 16. module fulladder(input logic a, b, cin, output logic s, cout); logic p, g; // internal nodes

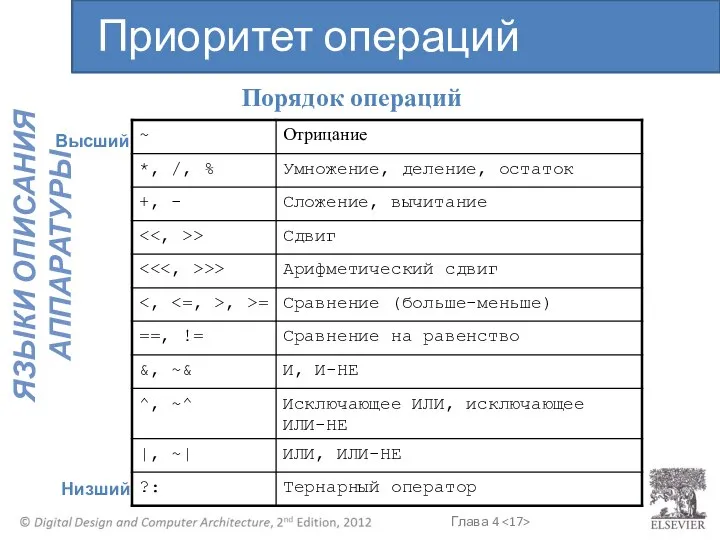

- 17. Порядок операций Высший Низший Приоритет операций

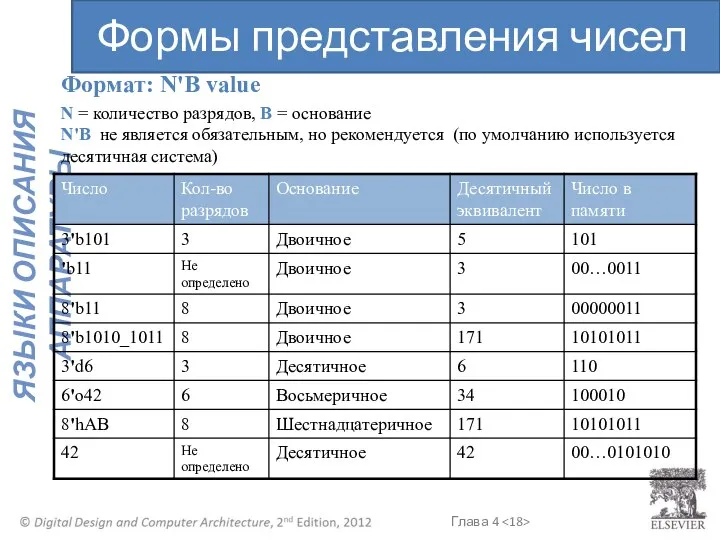

- 18. Формат: N'B value N = количество разрядов, B = основание N'B не является обязательным, но рекомендуется

- 19. assign y = {a[2:1], {3{b[0]}}, a[0], 6'b100_010}; // если y - 12-битовый сигнал, оператор выше сформирует:

- 20. module mux2_8(input logic [7:0] d0, d1, input logic s, output logic [7:0] y); mux2 lsbmux(d0[3:0], d1[3:0],

- 21. module tristate(input logic [3:0] a, input logic en, output logic [3:0] y); assign y = en

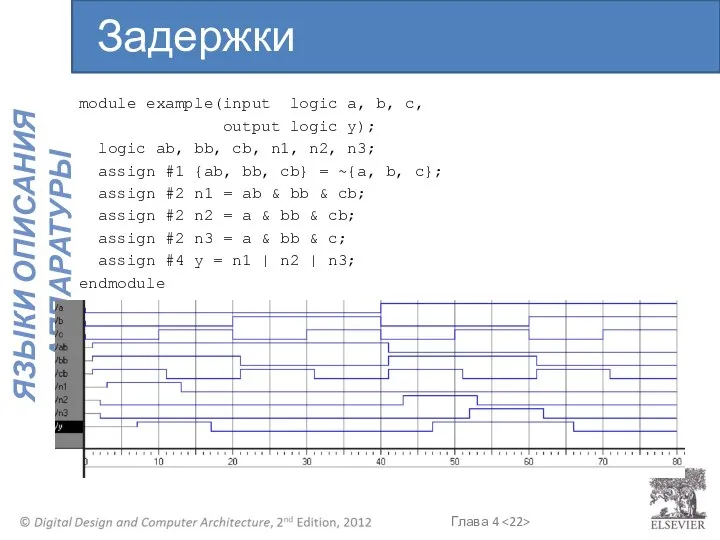

- 22. module example(input logic a, b, c, output logic y); logic ab, bb, cb, n1, n2, n3;

- 23. module example(input logic a, b, c, output logic y); logic ab, bb, cb, n1, n2, n3;

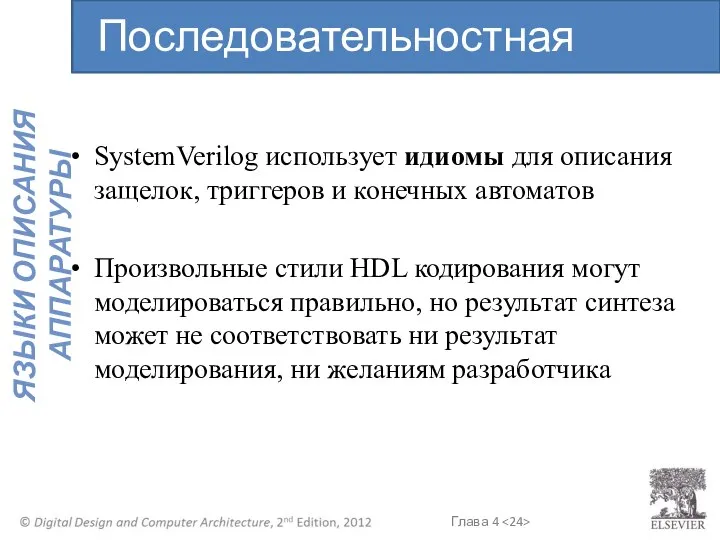

- 24. SystemVerilog использует идиомы для описания защелок, триггеров и конечных автоматов Произвольные стили HDL кодирования могут моделироваться

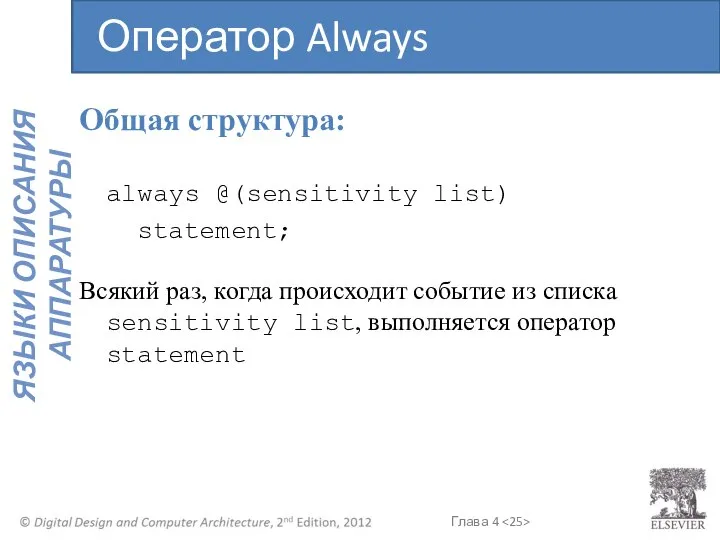

- 25. Общая структура: always @(sensitivity list) statement; Всякий раз, когда происходит событие из списка sensitivity list, выполняется

- 26. module flop(input logic clk, input logic [3:0] d, output logic [3:0] q); always_ff @(posedge clk) q

- 27. module flopr(input logic clk, input logic reset, input logic [3:0] d, output logic [3:0] q); //

- 28. module flopr(input logic clk, input logic reset, input logic [3:0] d, output logic [3:0] q); //

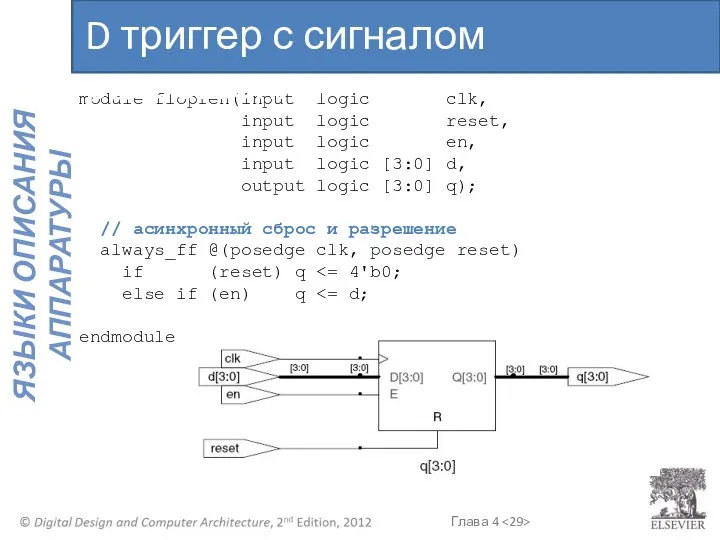

- 29. module flopren(input logic clk, input logic reset, input logic en, input logic [3:0] d, output logic

- 30. module latch(input logic clk, input logic [3:0] d, output logic [3:0] q); always_latch if (clk) q

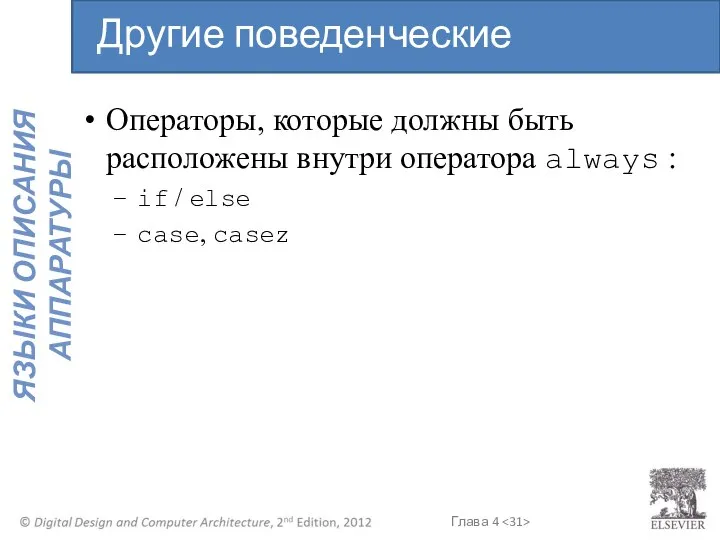

- 31. Операторы, которые должны быть расположены внутри оператора always : if / else case, casez Другие поведенческие

- 32. //комбинационная логика с использованием оператора always module gates(input logic [3:0] a, b, output logic [3:0] y1,

- 33. module sevenseg(input logic [3:0] data, output logic [6:0] segments); always_comb case (data) // abc_defg 0: segments

- 34. Оператор Case реализует комбинационную логику, только если в его ветвях перечислены все возможные входные комбинации Помните

- 35. module priority_casez(input logic [3:0] a, output logic [3:0] y); always_comb casez(a) 4'b1???: y = 4'b1000; //

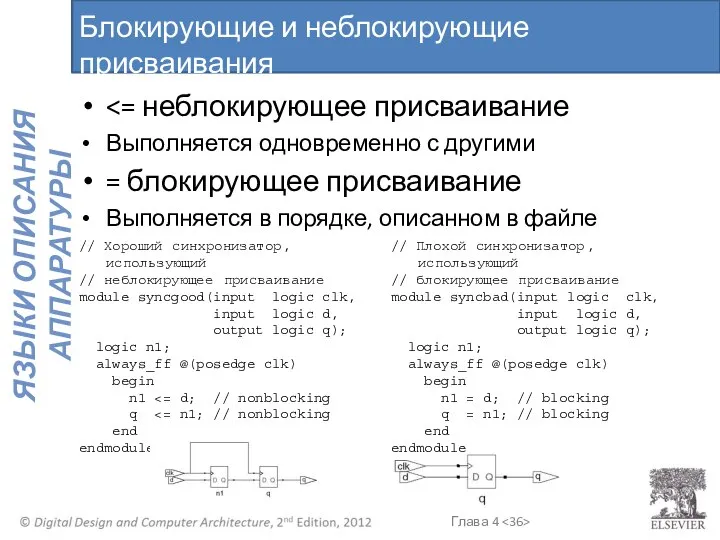

- 36. Выполняется одновременно с другими = блокирующее присваивание Выполняется в порядке, описанном в файле // Хороший синхронизатор,

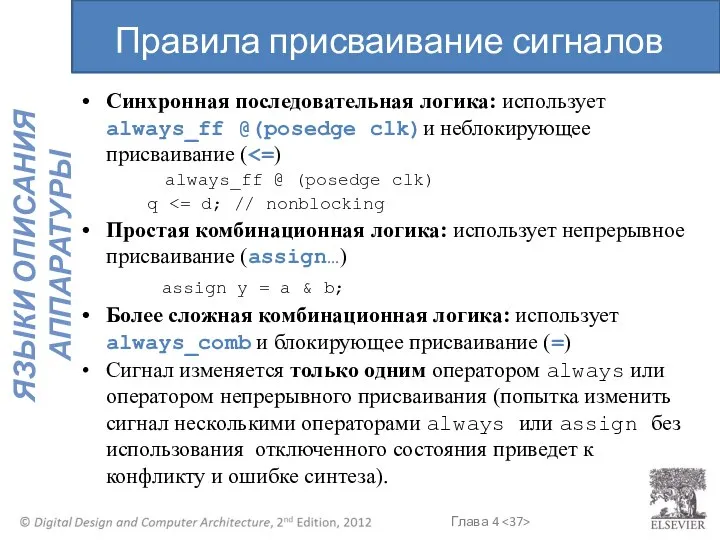

- 37. Синхронная последовательная логика: использует always_ff @(posedge clk)и неблокирующее присваивание ( always_ff @ (posedge clk) q Простая

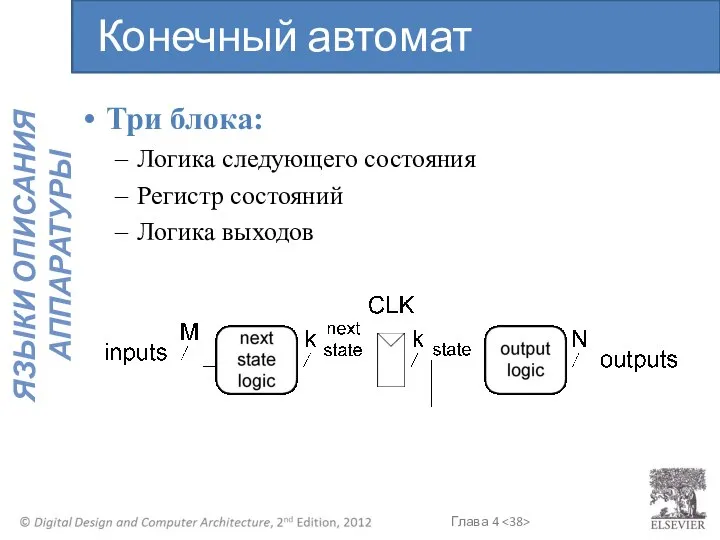

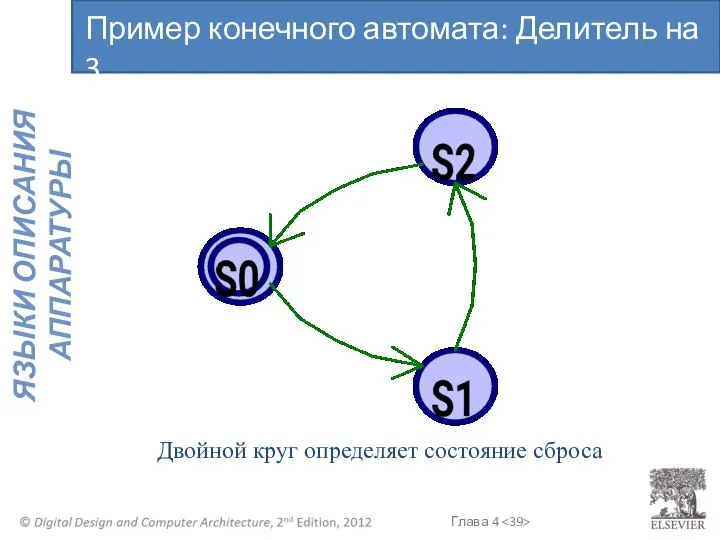

- 38. Три блока: Логика следующего состояния Регистр состояний Логика выходов Конечный автомат

- 39. Двойной круг определяет состояние сброса Пример конечного автомата: Делитель на 3

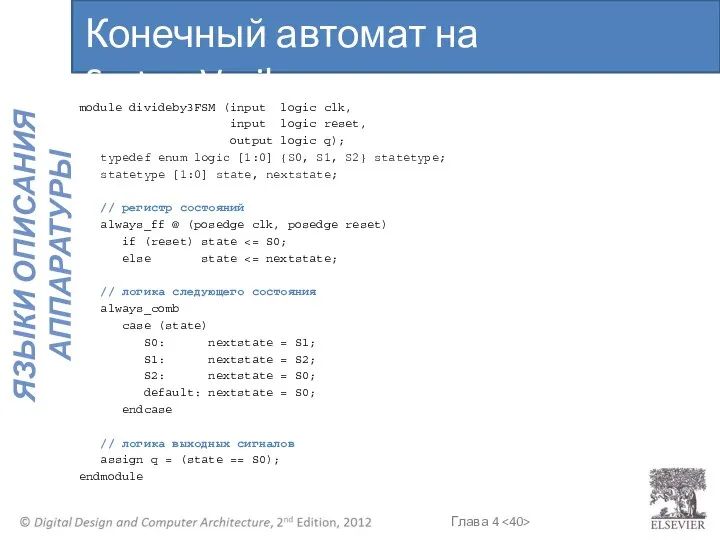

- 40. module divideby3FSM (input logic clk, input logic reset, output logic q); typedef enum logic [1:0] {S0,

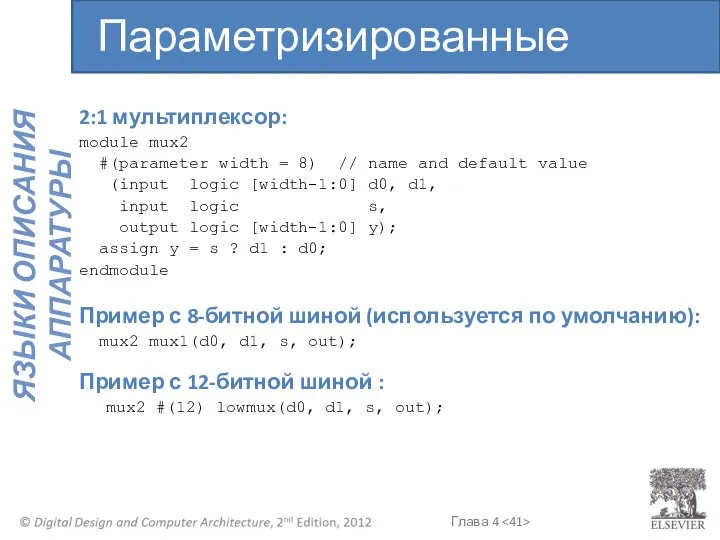

- 41. 2:1 мультиплексор: module mux2 #(parameter width = 8) // name and default value (input logic [width-1:0]

- 42. HDL модуль, который тестирует другой модуль: тестируемое устройство (DUT) Не предназначена для синтеза Типы: Простая С

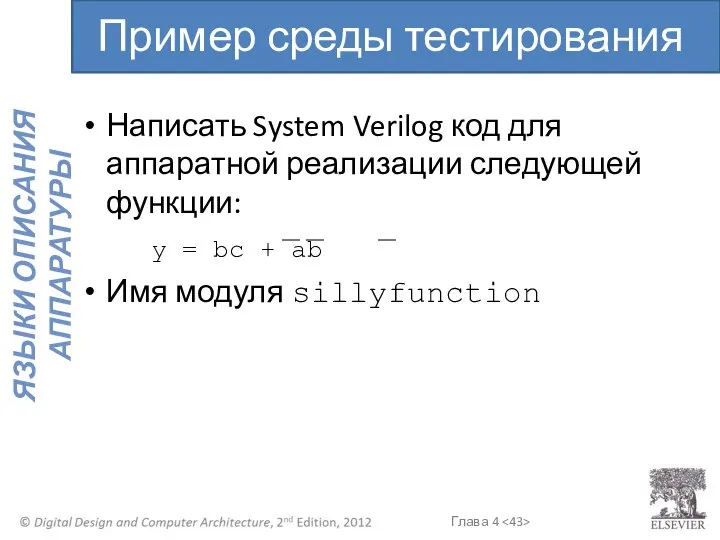

- 43. Написать System Verilog код для аппаратной реализации следующей функции: y = bc + ab Имя модуля

- 44. Написать System Verilog код для аппаратной реализации следующей функции: y = bc + ab module sillyfunction(input

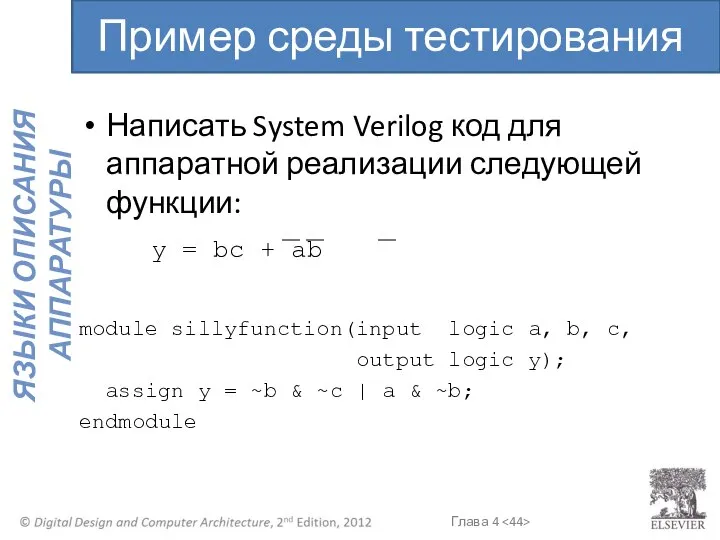

- 45. module testbench1(); logic a, b, c; logic y; // экземпляр проверяемого устройства sillyfunction dut(a, b, c,

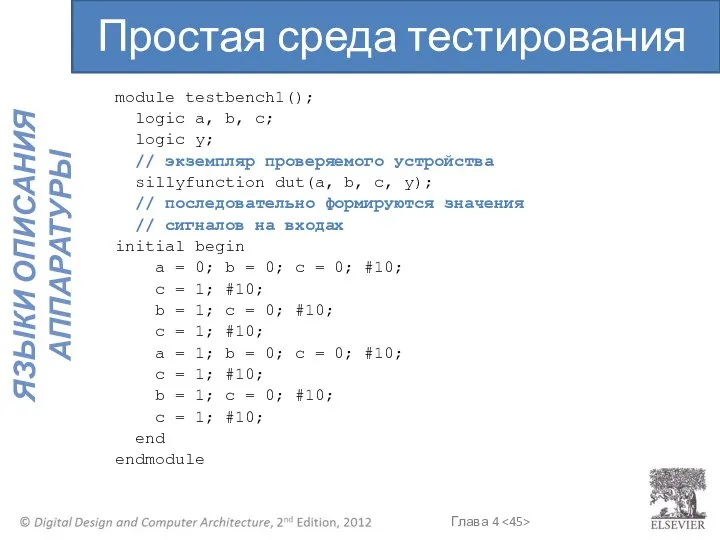

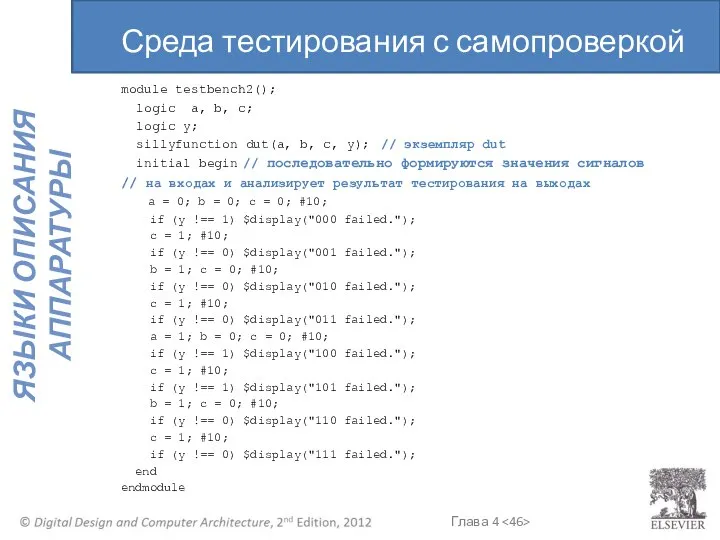

- 46. module testbench2(); logic a, b, c; logic y; sillyfunction dut(a, b, c, y); // экземпляр dut

- 47. Файл тестовых векторов: входные сигналы и ожидаемые состояния выходов Среда тестирования: Формирование тактового сигнала для изменения

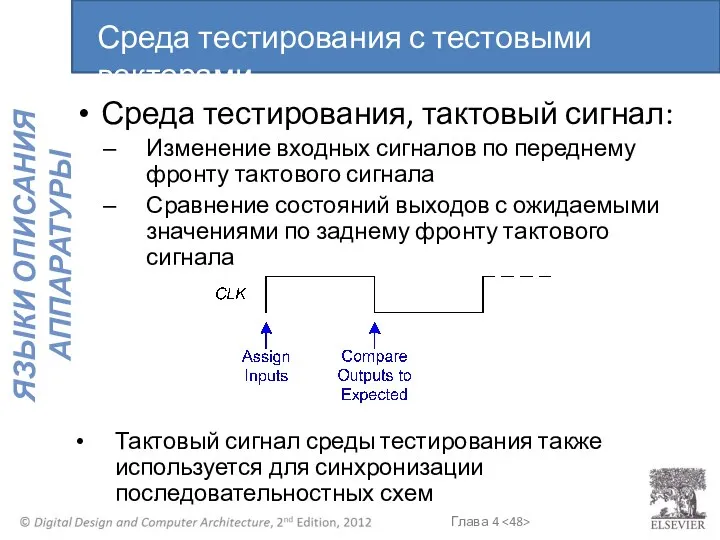

- 48. Среда тестирования, тактовый сигнал: Изменение входных сигналов по переднему фронту тактового сигнала Сравнение состояний выходов с

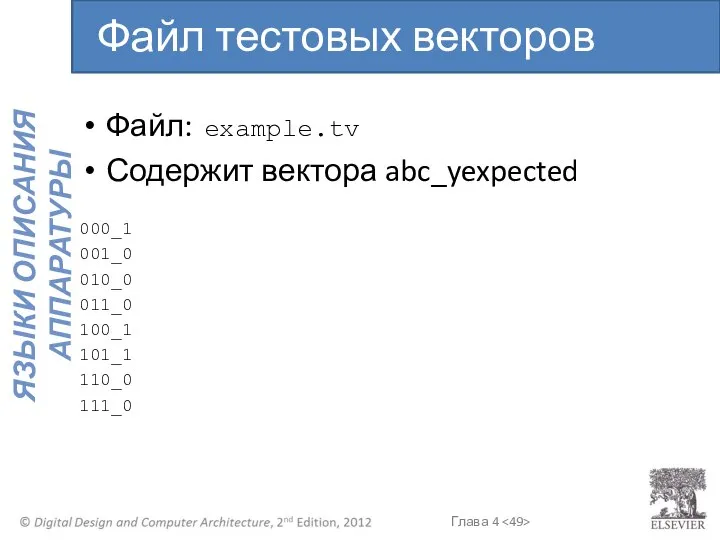

- 49. Файл: example.tv Содержит вектора abc_yexpected 000_1 001_0 010_0 011_0 100_1 101_1 110_0 111_0 Файл тестовых векторов

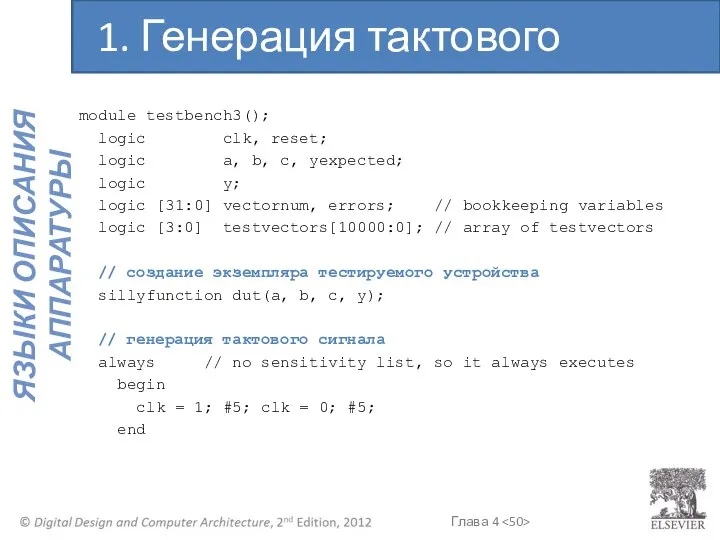

- 50. module testbench3(); logic clk, reset; logic a, b, c, yexpected; logic y; logic [31:0] vectornum, errors;

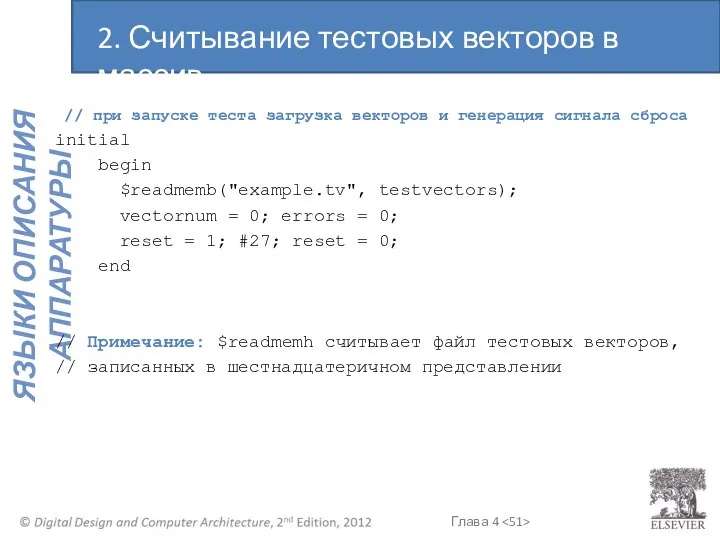

- 51. // при запуске теста загрузка векторов и генерация сигнала сброса initial begin $readmemb("example.tv", testvectors); vectornum =

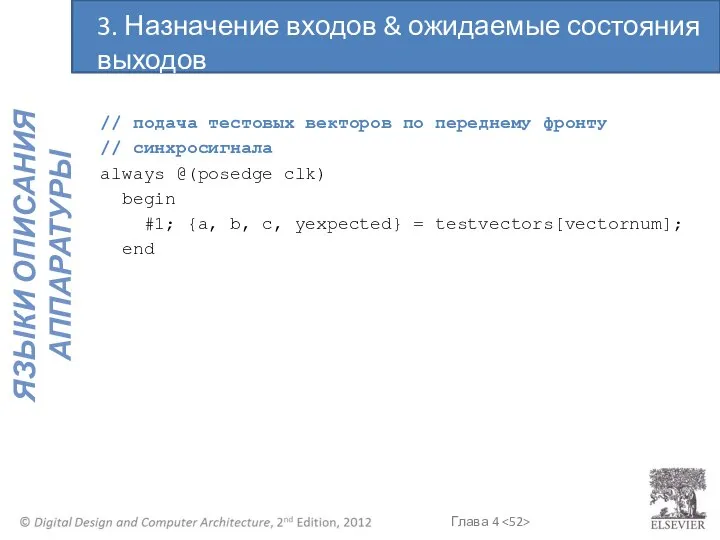

- 52. // подача тестовых векторов по переднему фронту // синхросигнала always @(posedge clk) begin #1; {a, b,

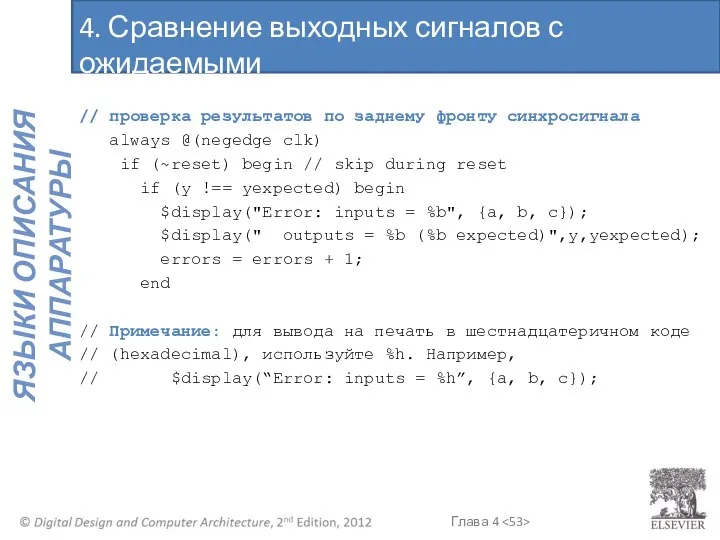

- 53. // проверка результатов по заднему фронту синхросигнала always @(negedge clk) if (~reset) begin // skip during

- 55. Скачать презентацию

![module gates(input logic [3:0] a, b, output logic [3:0] y1, y2,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-12.jpg)

![module and8(input logic [7:0] a, output logic y); assign y =](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-13.jpg)

![module mux2(input logic [3:0] d0, d1, input logic s, output logic](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-14.jpg)

![assign y = {a[2:1], {3{b[0]}}, a[0], 6'b100_010}; // если y -](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-18.jpg)

![module mux2_8(input logic [7:0] d0, d1, input logic s, output logic](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-19.jpg)

![module tristate(input logic [3:0] a, input logic en, output logic [3:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-20.jpg)

![module flop(input logic clk, input logic [3:0] d, output logic [3:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-25.jpg)

![module flopr(input logic clk, input logic reset, input logic [3:0] d,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-26.jpg)

![module flopr(input logic clk, input logic reset, input logic [3:0] d,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-27.jpg)

![module latch(input logic clk, input logic [3:0] d, output logic [3:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-29.jpg)

![//комбинационная логика с использованием оператора always module gates(input logic [3:0] a,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-31.jpg)

![module sevenseg(input logic [3:0] data, output logic [6:0] segments); always_comb case](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-32.jpg)

![module priority_casez(input logic [3:0] a, output logic [3:0] y); always_comb casez(a)](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1475016/slide-34.jpg)

Труд в изобразительном искусстве Выполнила учитель ИЗО Шаньшерова М.М. г. Белоярский ХМАО-Югра

Труд в изобразительном искусстве Выполнила учитель ИЗО Шаньшерова М.М. г. Белоярский ХМАО-Югра Лёгочные диссеминации

Лёгочные диссеминации  Бурильная колонна. КНБК. Работа бурильной колонны в скважине. Семинар 5

Бурильная колонна. КНБК. Работа бурильной колонны в скважине. Семинар 5 Происхождение и быт восточных славян

Происхождение и быт восточных славян Основы цветоведения

Основы цветоведения Паличкоподібні (циліндричні) бактерії Паличкоподібні бактерії мають форму паличок. Розрізняються різноманітністю розмірів,

Паличкоподібні (циліндричні) бактерії Паличкоподібні бактерії мають форму паличок. Розрізняються різноманітністю розмірів,  Качество товаров

Качество товаров Свойства нейтрино.

Свойства нейтрино. Русская культура конца XIII – XVI веков

Русская культура конца XIII – XVI веков Выращивание зелёного лука в различных условиях Выполнила: ученица 1 «Б» класса Атаманчук Даша Руководитель: Бояринкова Н. А.

Выращивание зелёного лука в различных условиях Выполнила: ученица 1 «Б» класса Атаманчук Даша Руководитель: Бояринкова Н. А. Искусство портрета

Искусство портрета Выполнила : Гавриленко Любовь Александровна. Вклад И.М. Сеченова в развитие мировой и отечественной физиологии.

Выполнила : Гавриленко Любовь Александровна. Вклад И.М. Сеченова в развитие мировой и отечественной физиологии.  47d45de70c3e43edaa4fce632df1ab97 (3)

47d45de70c3e43edaa4fce632df1ab97 (3) В художественном мире русской волшебной сказки Цикл «Развивающие исследовательские технологии». © Г.С. Меркин, 2009 г.

В художественном мире русской волшебной сказки Цикл «Развивающие исследовательские технологии». © Г.С. Меркин, 2009 г. «Банкир – это центральная фигура. Он держит на своих плечах весь мир.» Герберт Кэссон

«Банкир – это центральная фигура. Он держит на своих плечах весь мир.» Герберт Кэссон Евфимий Васильевич Путятин - русский адмирал

Евфимий Васильевич Путятин - русский адмирал Семинар «Воспитание личности школьника – важнейшее условие оптимизации образовательного процесса»

Семинар «Воспитание личности школьника – важнейшее условие оптимизации образовательного процесса»  Лучевая энергия Солнца и Т среды обитания животных

Лучевая энергия Солнца и Т среды обитания животных  Гемостаз

Гемостаз Банковские риски и управление ими Гурина Л.А.

Банковские риски и управление ими Гурина Л.А.  ГРАММАТИКА В СИСТЕМНОМ ПРЕДСТАВЛЕНИИ ЯЗЫКА

ГРАММАТИКА В СИСТЕМНОМ ПРЕДСТАВЛЕНИИ ЯЗЫКА Презентация Правовые и нормативные основы охраны труда

Презентация Правовые и нормативные основы охраны труда Инженерные сооружения на автомобильных дорогах

Инженерные сооружения на автомобильных дорогах Brainstorm. Project students’ activity

Brainstorm. Project students’ activity ЧЕЛОВЕК И ЕГО ДЕЯТЕЛЬНОСТЬ1

ЧЕЛОВЕК И ЕГО ДЕЯТЕЛЬНОСТЬ1 Навигатор дополнительного образования. Инструкция для родителей по регистрации на сайте

Навигатор дополнительного образования. Инструкция для родителей по регистрации на сайте «ДОБРЫХ РУК МАСТЕРСТВО». Публичное выступление – представление исследовательского проекта о произведениях декоративно-прик

«ДОБРЫХ РУК МАСТЕРСТВО». Публичное выступление – представление исследовательского проекта о произведениях декоративно-прик Михаил Юрьевич Лермонтов

Михаил Юрьевич Лермонтов