Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Faculty, Electronic Devices & Systems, 7th semester,2010 Dr. Mokhovikov Alexander Yurievich

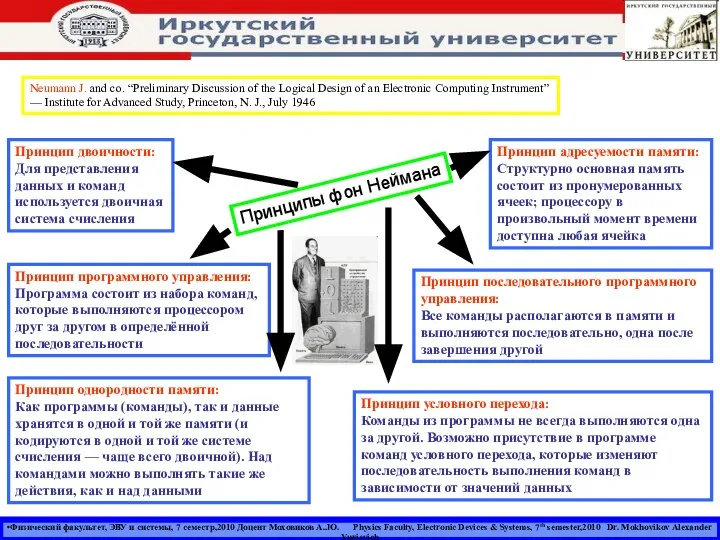

Neumann J. and co. “Preliminary Discussion of the Logical Design of an Electronic Computing Instrument”

— Institute for Advanced Study, Princeton, N. J., July 1946

Принципы фон Неймана

Принцип двоичности:

Для представления данных и команд используется двоичная система счисления

Принцип программного управления:

Программа состоит из набора команд, которые выполняются процессором друг за другом в определённой последовательности

Принцип однородности памяти:

Как программы (команды), так и данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления — чаще всего двоичной). Над командами можно выполнять такие же действия, как и над данными

Принцип адресуемости памяти:

Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка

Принцип последовательного программного управления:

Все команды располагаются в памяти и выполняются последовательно, одна после завершения другой

Принцип условного перехода:

Команды из программы не всегда выполняются одна за другой. Возможно присутствие в программе команд условного перехода, которые изменяют последовательность выполнения команд в зависимости от значений данных

Духовный смысл поста

Духовный смысл поста Якість як об’єкт управління

Якість як об’єкт управління Алгоритм Рабина - Карпа. Поиск подстрок сдвигом

Алгоритм Рабина - Карпа. Поиск подстрок сдвигом Олимпийский огонь «Сочи-2014» в цифрах и фактах

Олимпийский огонь «Сочи-2014» в цифрах и фактах Государственные органы власти РФ

Государственные органы власти РФ Анализ мирового опыта создания подземных переходов

Анализ мирового опыта создания подземных переходов Строительство 14-ти этажного жилого дома с рамно-связевым каркасом. Поселок Мурино Ленинградская область

Строительство 14-ти этажного жилого дома с рамно-связевым каркасом. Поселок Мурино Ленинградская область Особенности определения страны происхождения товаров с территории особых экономических зон Калининградской и Магаданской облас

Особенности определения страны происхождения товаров с территории особых экономических зон Калининградской и Магаданской облас Первые уроки школьной отметки.

Первые уроки школьной отметки. сент

сент Деятельность социального педагога

Деятельность социального педагога У р о к г о р о д а «Комсомольская юность моих земляков»

У р о к г о р о д а «Комсомольская юность моих земляков»  Понятие занятости населения

Понятие занятости населения Samsung Motors. История

Samsung Motors. История Определение интересов учащихся школы

Определение интересов учащихся школы Колчак Александр Васильевич

Колчак Александр Васильевич Характеристика и классификация оптических волокон и оптических кабелей

Характеристика и классификация оптических волокон и оптических кабелей Электромонтажник

Электромонтажник  Методы исследований

Методы исследований Илья Ефимович Репин

Илья Ефимович Репин Мониторинг прессы по проекту "Форма для Национальной олимпийской сборной Украины" by Andre Tan

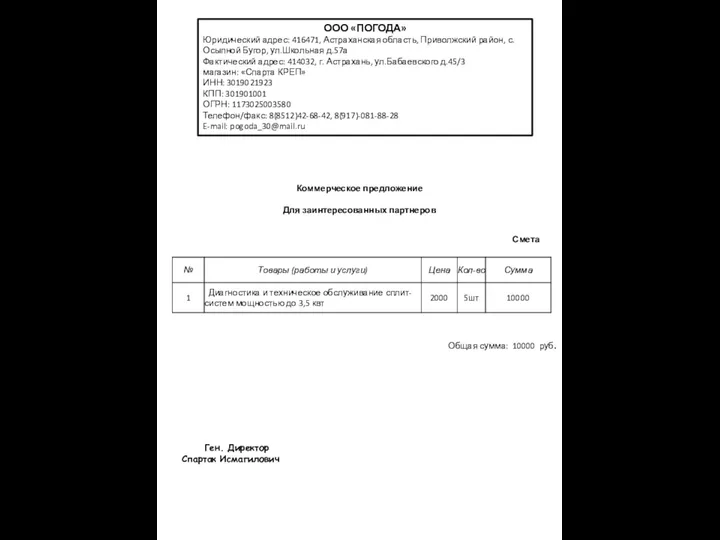

Мониторинг прессы по проекту "Форма для Национальной олимпийской сборной Украины" by Andre Tan ООО «Погода»

ООО «Погода» Иконопись Новгорода (1)

Иконопись Новгорода (1) Разминка по теме «Психология личности преступника» Выполнила А.В. Червона

Разминка по теме «Психология личности преступника» Выполнила А.В. Червона  ЛЕКЦИЯ 6-7 ТЕМА 4 Инвестиции: сущность, структура, основные модели Лектор – д.э.н., профессор Дегтярева Ирина Викторовна

ЛЕКЦИЯ 6-7 ТЕМА 4 Инвестиции: сущность, структура, основные модели Лектор – д.э.н., профессор Дегтярева Ирина Викторовна Правила проектирования и проектные нормы КМДП транзисторов

Правила проектирования и проектные нормы КМДП транзисторов Телевизионные системы наблюдения

Телевизионные системы наблюдения Масленица. Пятница

Масленица. Пятница