Содержание

Слайд 2

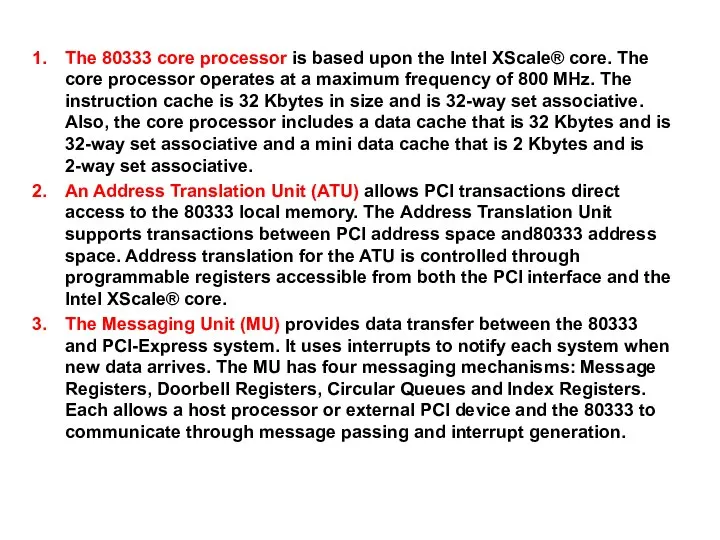

The 80333 core processor is based upon the Intel XScale® core.

The 80333 core processor is based upon the Intel XScale® core.

The core processor operates at a maximum frequency of 800 MHz. The instruction cache is 32 Kbytes in size and is 32-way set associative. Also, the core processor includes a data cache that is 32 Kbytes and is 32-way set associative and a mini data cache that is 2 Kbytes and is 2-way set associative.

An Address Translation Unit (ATU) allows PCI transactions direct access to the 80333 local memory. The Address Translation Unit supports transactions between PCI address space and80333 address space. Address translation for the ATU is controlled through programmable registers accessible from both the PCI interface and the Intel XScale® core.

The Messaging Unit (MU) provides data transfer between the 80333 and PCI-Express system. It uses interrupts to notify each system when new data arrives. The MU has four messaging mechanisms: Message Registers, Doorbell Registers, Circular Queues and Index Registers. Each allows a host processor or external PCI device and the 80333 to communicate through message passing and interrupt generation.

An Address Translation Unit (ATU) allows PCI transactions direct access to the 80333 local memory. The Address Translation Unit supports transactions between PCI address space and80333 address space. Address translation for the ATU is controlled through programmable registers accessible from both the PCI interface and the Intel XScale® core.

The Messaging Unit (MU) provides data transfer between the 80333 and PCI-Express system. It uses interrupts to notify each system when new data arrives. The MU has four messaging mechanisms: Message Registers, Doorbell Registers, Circular Queues and Index Registers. Each allows a host processor or external PCI device and the 80333 to communicate through message passing and interrupt generation.

Слайд 3

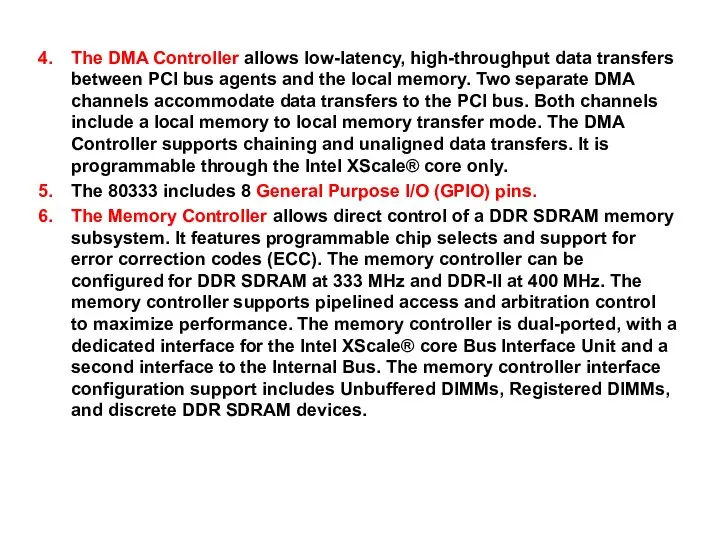

The DMA Controller allows low-latency, high-throughput data transfers between PCI bus

The DMA Controller allows low-latency, high-throughput data transfers between PCI bus

agents and the local memory. Two separate DMA channels accommodate data transfers to the PCI bus. Both channels include a local memory to local memory transfer mode. The DMA Controller supports chaining and unaligned data transfers. It is programmable through the Intel XScale® core only.

The 80333 includes 8 General Purpose I/O (GPIO) pins.

The Memory Controller allows direct control of a DDR SDRAM memory subsystem. It features programmable chip selects and support for error correction codes (ECC). The memory controller can be configured for DDR SDRAM at 333 MHz and DDR-II at 400 MHz. The memory controller supports pipelined access and arbitration control to maximize performance. The memory controller is dual-ported, with a dedicated interface for the Intel XScale® core Bus Interface Unit and a second interface to the Internal Bus. The memory controller interface configuration support includes Unbuffered DIMMs, Registered DIMMs, and discrete DDR SDRAM devices.

The 80333 includes 8 General Purpose I/O (GPIO) pins.

The Memory Controller allows direct control of a DDR SDRAM memory subsystem. It features programmable chip selects and support for error correction codes (ECC). The memory controller can be configured for DDR SDRAM at 333 MHz and DDR-II at 400 MHz. The memory controller supports pipelined access and arbitration control to maximize performance. The memory controller is dual-ported, with a dedicated interface for the Intel XScale® core Bus Interface Unit and a second interface to the Internal Bus. The memory controller interface configuration support includes Unbuffered DIMMs, Registered DIMMs, and discrete DDR SDRAM devices.

- Предыдущая

Цикл процессора Следующая -

Команды управления шины PCI

Позитивистский подход в типологии обществ

Позитивистский подход в типологии обществ … Государство, в котором граждане наиболее повинуются закону, счастливо во время мира и незыблемо во время войны.

… Государство, в котором граждане наиболее повинуются закону, счастливо во время мира и незыблемо во время войны.  Тхор Лаура Курманбиевна Тхор Лаура Курманбиевна учитель начальных классов МАОУ СОШ «Земля родная» Г. Новый Уренгой

Тхор Лаура Курманбиевна Тхор Лаура Курманбиевна учитель начальных классов МАОУ СОШ «Земля родная» Г. Новый Уренгой  Основы теории и практики ведения миротворчества. Косово - МООНГ

Основы теории и практики ведения миротворчества. Косово - МООНГ Микроконтроллеры. Интерфейсы

Микроконтроллеры. Интерфейсы стрессы у детей

стрессы у детей jQuery в JavaScript

jQuery в JavaScript Понятие функции комплексной переменной

Понятие функции комплексной переменной Великобритания: общая характеристика общественного строя, формы правления и формы государственного устройства

Великобритания: общая характеристика общественного строя, формы правления и формы государственного устройства Гребля на байдарках и каноэ

Гребля на байдарках и каноэ Презентация Гражданское право и гражданские правоотношения

Презентация Гражданское право и гражданские правоотношения - презентация

- презентация Программирование и программные среды

Программирование и программные среды The variable of political culture & socialization

The variable of political culture & socialization Mechanics subline route location introduction

Mechanics subline route location introduction Внутренний мир русской избы

Внутренний мир русской избы Организация питания в МБДОУ - презентация_

Организация питания в МБДОУ - презентация_ Законодательство в области авторского права и интеллектуальной собственности

Законодательство в области авторского права и интеллектуальной собственности Система цветного телевидения

Система цветного телевидения GF_Python_Data_Structures

GF_Python_Data_Structures Презентация на тему "Профессиональная компетентность" - скачать презентации по Педагогике

Презентация на тему "Профессиональная компетентность" - скачать презентации по Педагогике Культура России 17 века

Культура России 17 века Медиация как форма досудебного урегулирования

Медиация как форма досудебного урегулирования Застольный этикет. Игра

Застольный этикет. Игра Спорт - презентация для начальной школы_

Спорт - презентация для начальной школы_ Художественная культура Мезоамерики. 10 класс

Художественная культура Мезоамерики. 10 класс оригами может сделать каждый

оригами может сделать каждый  Первые жители нашего края

Первые жители нашего края