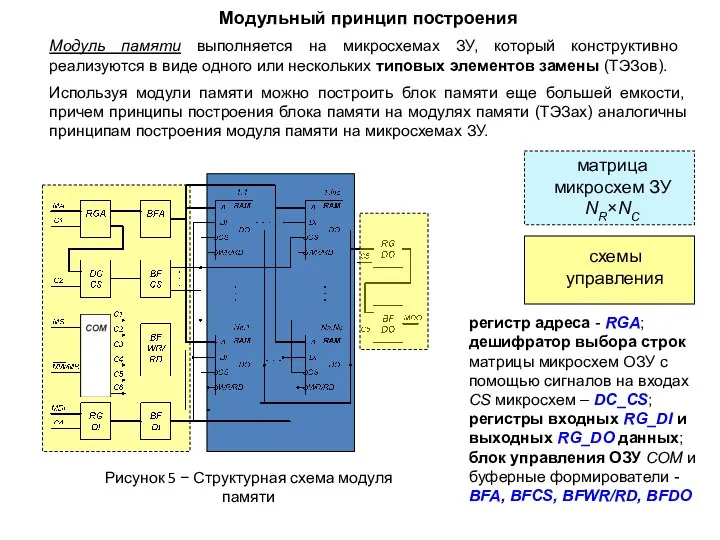

Рисунок 5 − Структурная схема модуля памяти

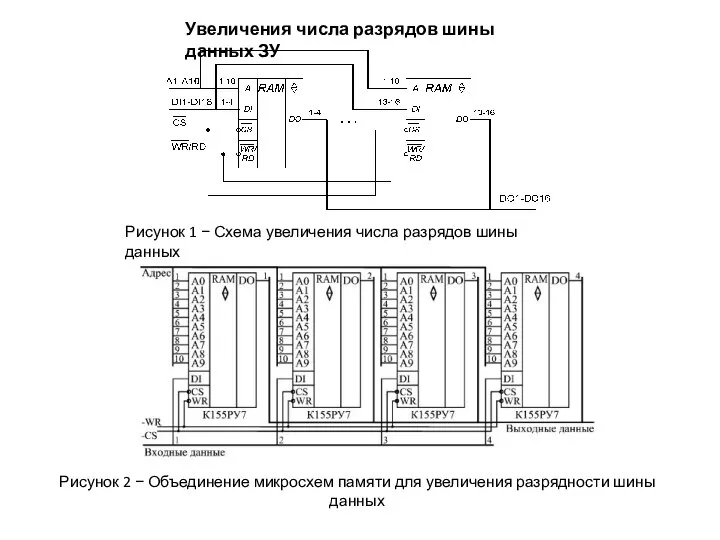

Модульный принцип построения

Модуль памяти выполняется

на микросхемах ЗУ, который конструктивно реализуются в виде одного или нескольких типовых элементов замены (ТЭЗов).

Используя модули памяти можно построить блок памяти еще большей емкости, причем принципы построения блока памяти на модулях памяти (ТЭЗах) аналогичны принципам построения модуля памяти на микросхемах ЗУ.

матрица микросхем ЗУ NR×NC

схемы управления

регистр адреса - RGA;

дешифратор выбора строк матрицы микросхем ОЗУ с помощью сигналов на входах CS микросхем – DC_CS;

регистры входных RG_DI и выходных RG_DO данных;

блок управления ОЗУ СОМ и буферные формирователи - ВFA, ВFCS, ВFWR/RD, ВFDO

Системы случайных величин

Системы случайных величин Речной туризм

Речной туризм Антигистаминные препараты

Антигистаминные препараты Скандинавская мифология

Скандинавская мифология Новогодняя сказка (для чтения) - презентация для начальной школы

Новогодняя сказка (для чтения) - презентация для начальной школы Силовые трансформаторы и автотрансформаторы

Силовые трансформаторы и автотрансформаторы Туберкулёз Лекция

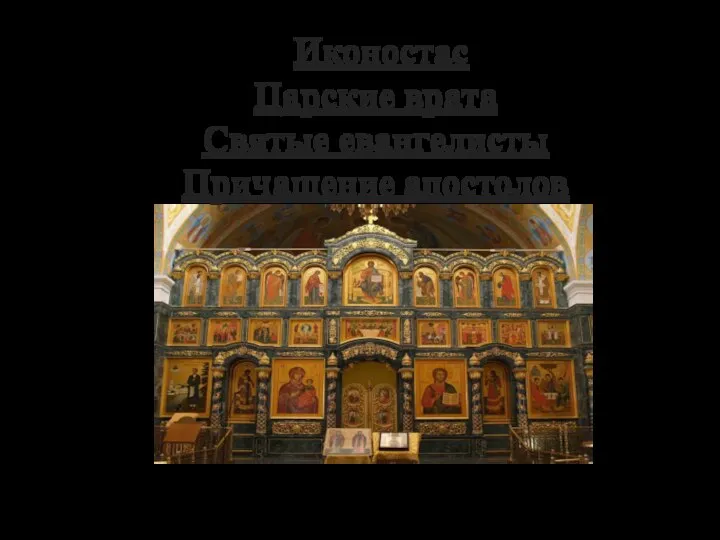

Туберкулёз Лекция Иконография

Иконография December extortion

December extortion Презентация на тему "Химия жизни. Наследственные болезни, их профилактика и лечение" - скачать презентации по Медицине

Презентация на тему "Химия жизни. Наследственные болезни, их профилактика и лечение" - скачать презентации по Медицине Вывод текста и шрифты

Вывод текста и шрифты  c Метрология, погрешность измерений

c Метрология, погрешность измерений Ислам. История возникновения

Ислам. История возникновения Презентация Законность и правопорядок

Презентация Законность и правопорядок ПОДРЯДНЫЕ ТОРГИ КАК ЭФФЕКТИВНЫЙ СПОСОБ ФОРМИРОВАНИЯ ОТНОШЕНИЙ МЕЖДУ ЗАКАЗЧИКОМ И ПОДРЯДЧИКОМ

ПОДРЯДНЫЕ ТОРГИ КАК ЭФФЕКТИВНЫЙ СПОСОБ ФОРМИРОВАНИЯ ОТНОШЕНИЙ МЕЖДУ ЗАКАЗЧИКОМ И ПОДРЯДЧИКОМ Проект реконструкции и озеленения территории МКОУ Бутурлиновская ООШ № 9 г. Бутурлиновка Воронежской области

Проект реконструкции и озеленения территории МКОУ Бутурлиновская ООШ № 9 г. Бутурлиновка Воронежской области ИССЛЕДОВАТЕЛЬСКАЯ РАБОТА Лунёва Екатерина «ВОЛШЕБНЫЕ ПРЕВРАЩЕНИЯ» МОУ ДМИТРОВСКАЯ ГИМНАЗИЯ «ЛОГОС» 2008-2009 уч.г.

ИССЛЕДОВАТЕЛЬСКАЯ РАБОТА Лунёва Екатерина «ВОЛШЕБНЫЕ ПРЕВРАЩЕНИЯ» МОУ ДМИТРОВСКАЯ ГИМНАЗИЯ «ЛОГОС» 2008-2009 уч.г. Жидачівська ЗОШ І-ІІІст. №2

Жидачівська ЗОШ І-ІІІст. №2 Слабый пол во всех видах спорта

Слабый пол во всех видах спорта Говоры и диалекты линейных казаков Кубани

Говоры и диалекты линейных казаков Кубани Патрология. Лекция II. Священномученик Ириней Лионский. Период III века

Патрология. Лекция II. Священномученик Ириней Лионский. Период III века Презентация "Символика Древнего Египта" - скачать презентации по МХК

Презентация "Символика Древнего Египта" - скачать презентации по МХК Презентация "Классификация одежды" - скачать презентации по МХК

Презентация "Классификация одежды" - скачать презентации по МХК Прикладное программное обеспечение

Прикладное программное обеспечение Физическое воспитание

Физическое воспитание Эритроциты

Эритроциты  Особенности идеала красоты и костюма в Древнем Риме

Особенности идеала красоты и костюма в Древнем Риме ОРГАНИЗАЦИЯ ДЕЛОВОГО ОБЩЕНИЯ

ОРГАНИЗАЦИЯ ДЕЛОВОГО ОБЩЕНИЯ