Содержание

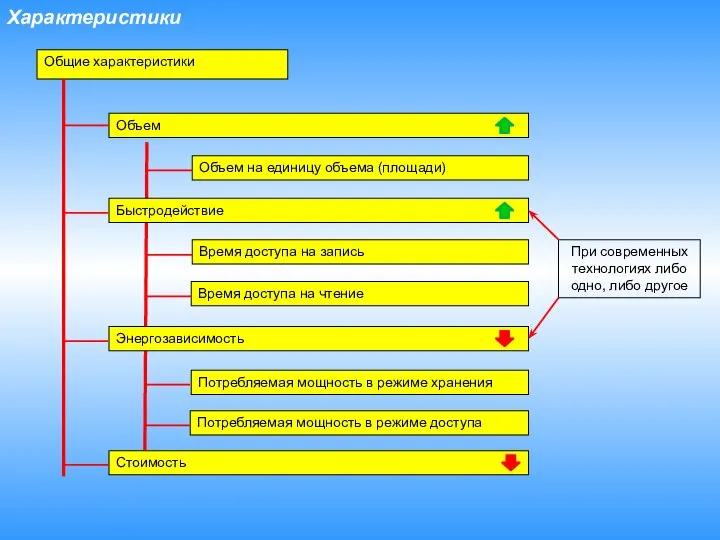

- 2. Характеристики Общие характеристики Объем Быстродействие Энергозависимость Стоимость Объем на единицу объема (площади) Время доступа на запись

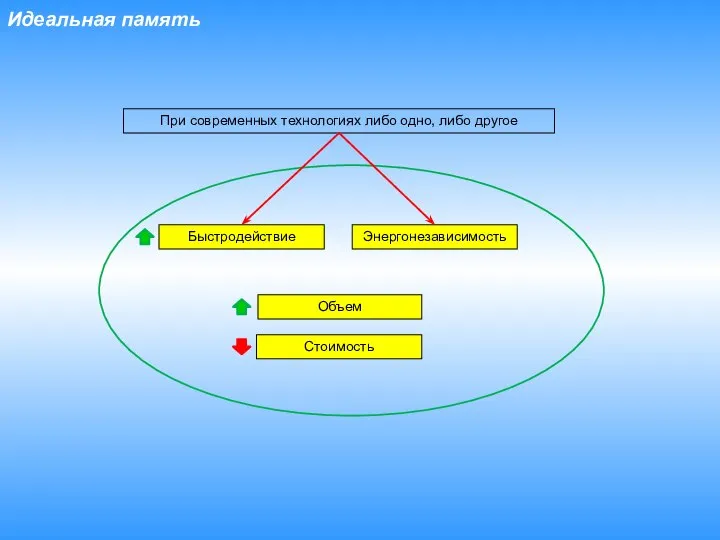

- 3. Идеальная память Объем Быстродействие Энергонезависимость Стоимость При современных технологиях либо одно, либо другое

- 4. Твердотельная память Быстродействие Энергонезависимость ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ

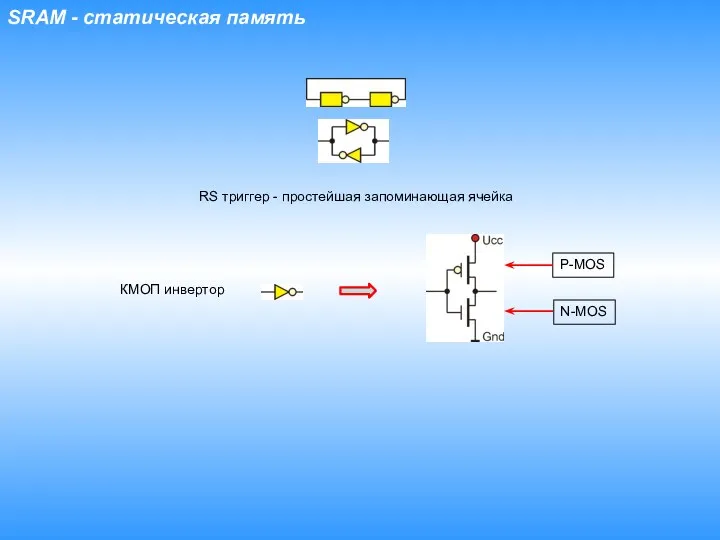

- 5. RS триггер - простейшая запоминающая ячейка КМОП инвертор SRAM - статическая память P-MOS N-MOS

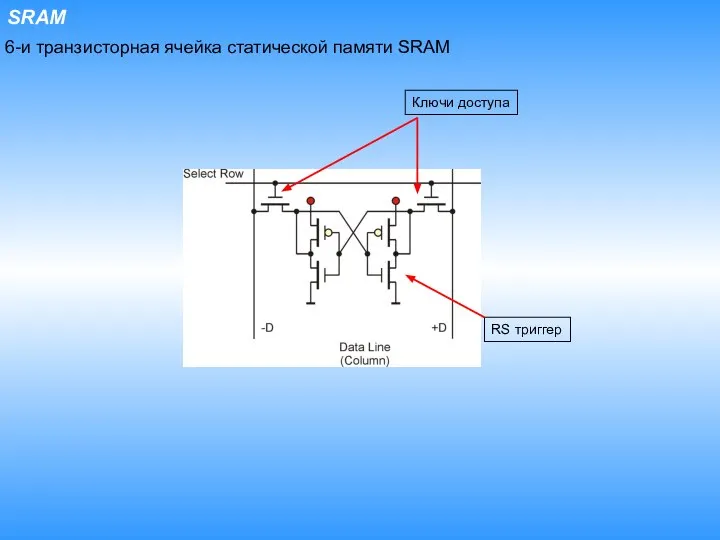

- 6. 6-и транзисторная ячейка статической памяти SRAM Ключи доступа RS триггер SRAM

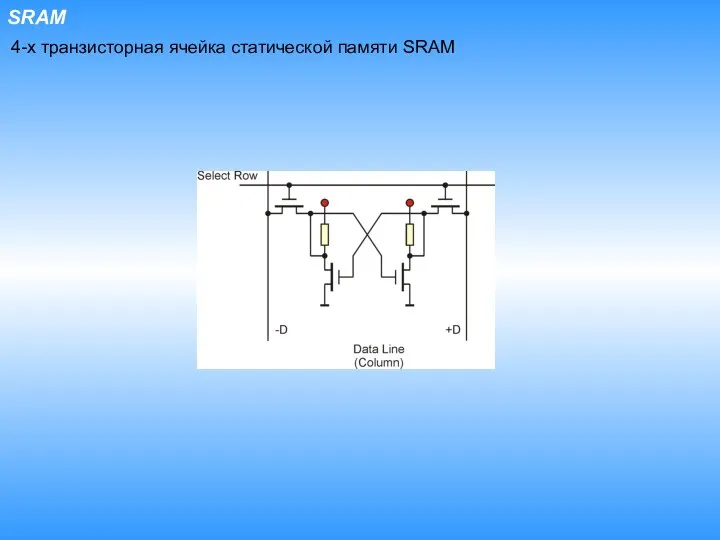

- 7. 4-х транзисторная ячейка статической памяти SRAM SRAM

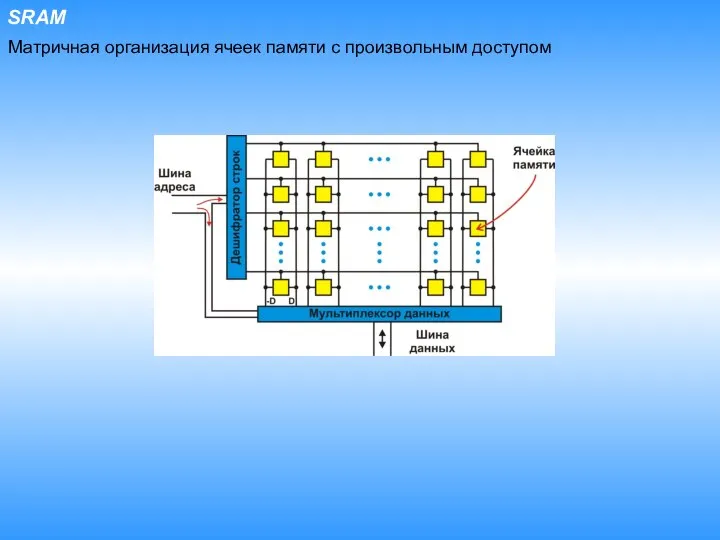

- 8. Матричная организация ячеек памяти с произвольным доступом SRAM

- 9. SRAM Асинхронная Синхронная SRAM

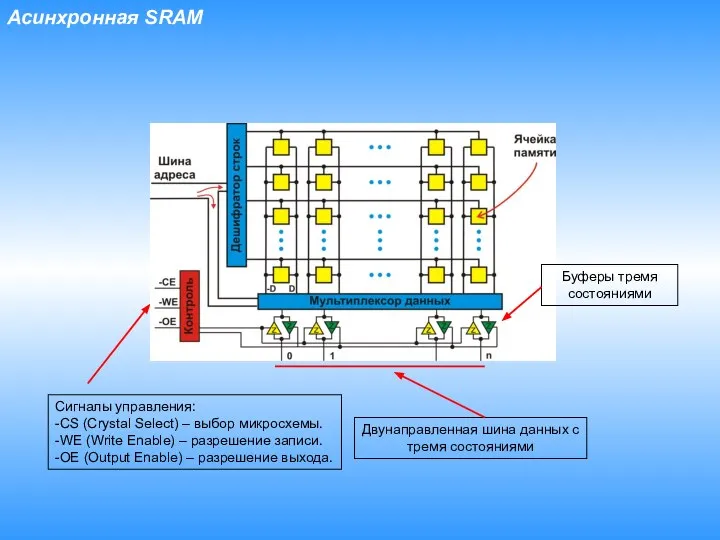

- 10. Сигналы управления: -CS (Crystal Select) – выбор микросхемы. -WE (Write Enable) – разрешение записи. -OE (Output

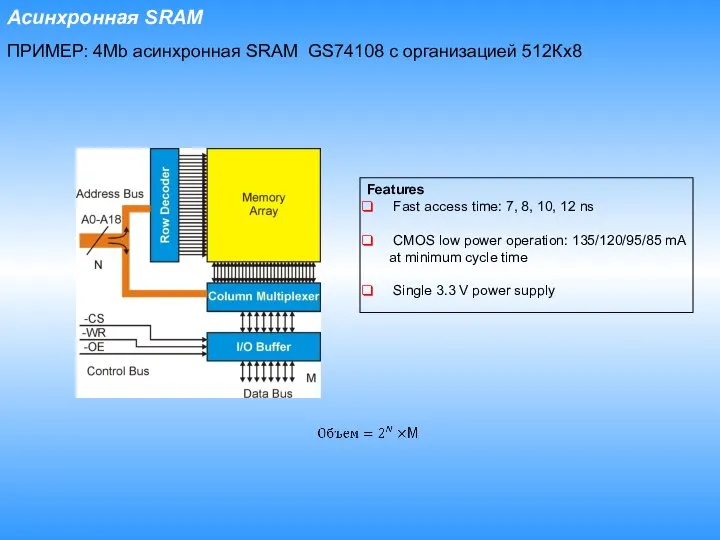

- 11. Features Fast access time: 7, 8, 10, 12 ns CMOS low power operation: 135/120/95/85 mA at

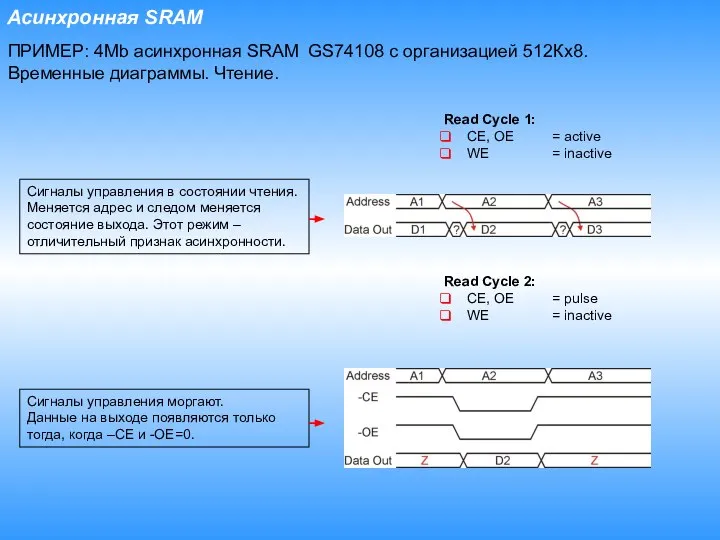

- 12. ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Чтение. Сигналы управления в состоянии чтения.

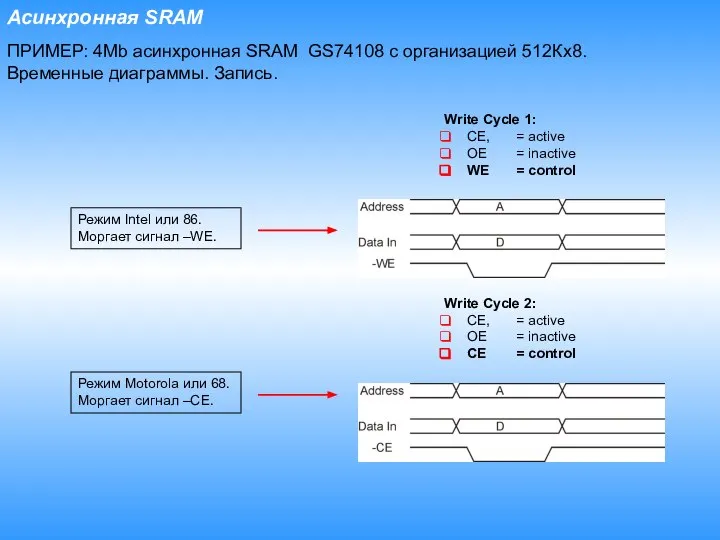

- 13. ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Запись. Режим Intel или 86. Моргает

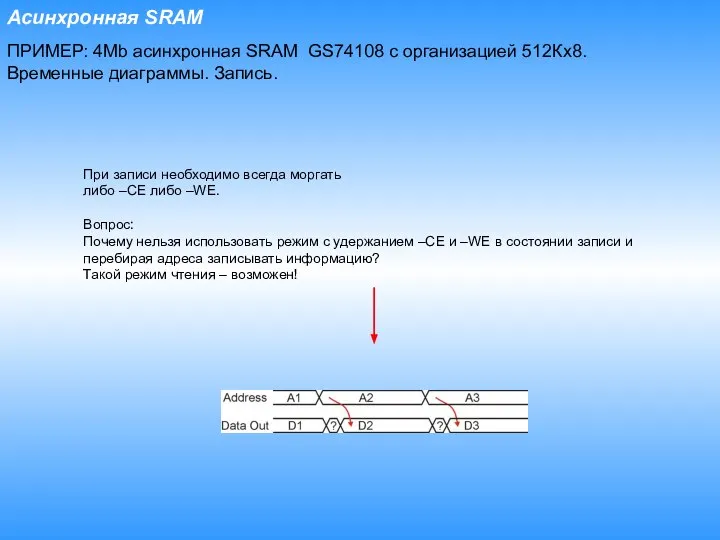

- 14. ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Запись. При записи необходимо всегда моргать

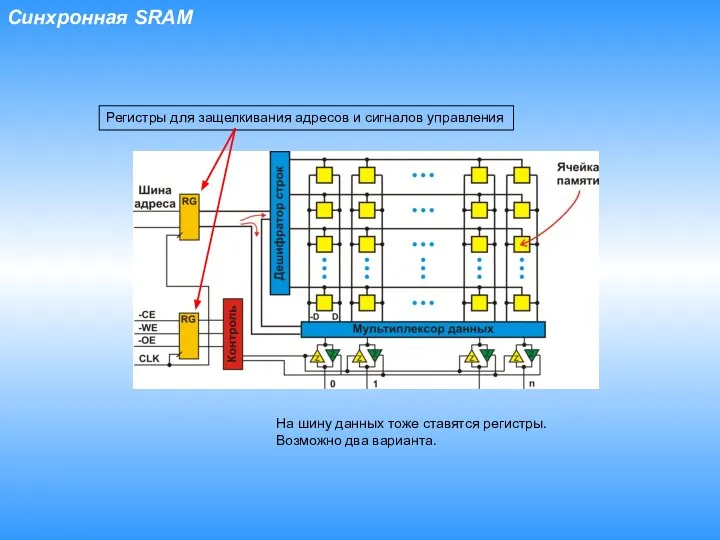

- 15. Регистры для защелкивания адресов и сигналов управления На шину данных тоже ставятся регистры. Возможно два варианта.

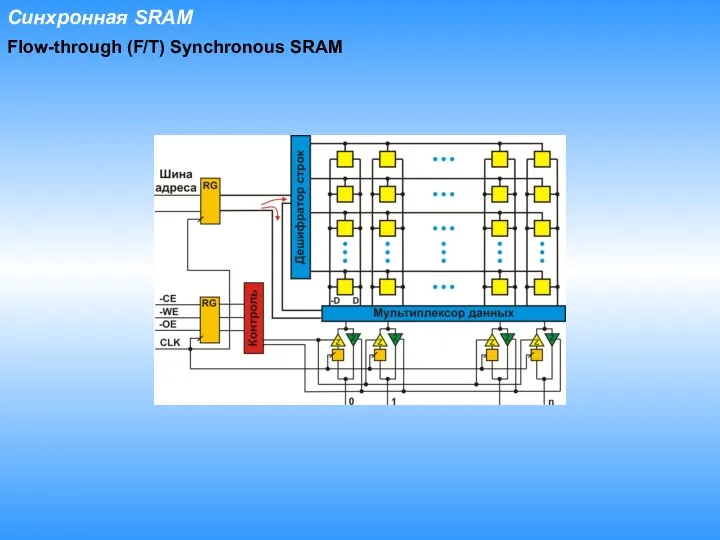

- 16. Flow-through (F/T) Synchronous SRAM Синхронная SRAM

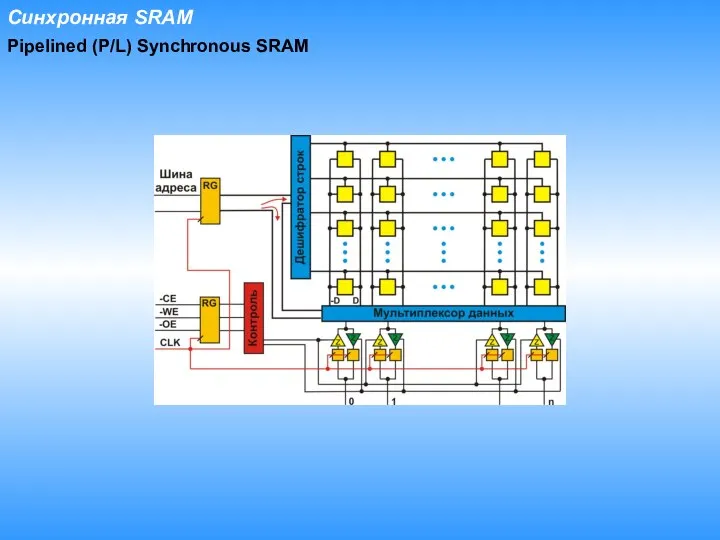

- 17. Pipelined (P/L) Synchronous SRAM Синхронная SRAM

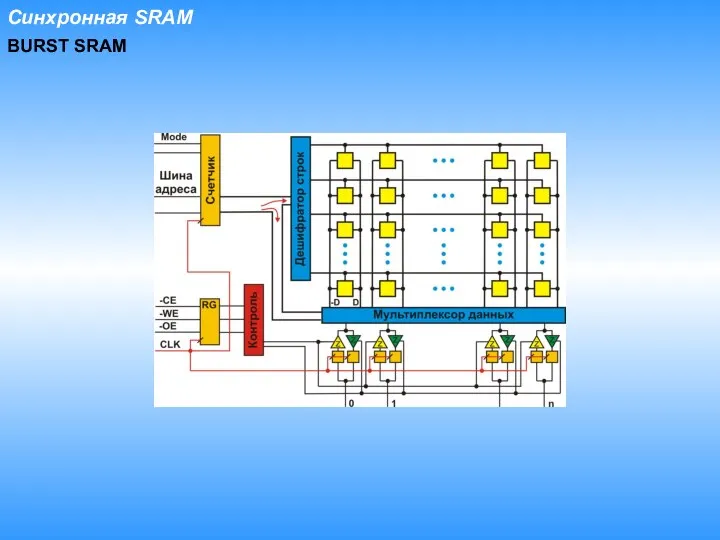

- 18. BURST SRAM Синхронная SRAM

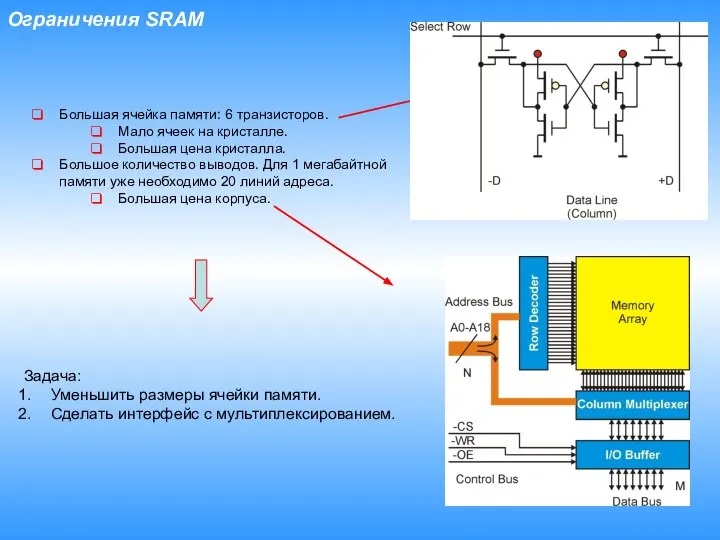

- 19. Ограничения SRAM Большая ячейка памяти: 6 транзисторов. Мало ячеек на кристалле. Большая цена кристалла. Большое количество

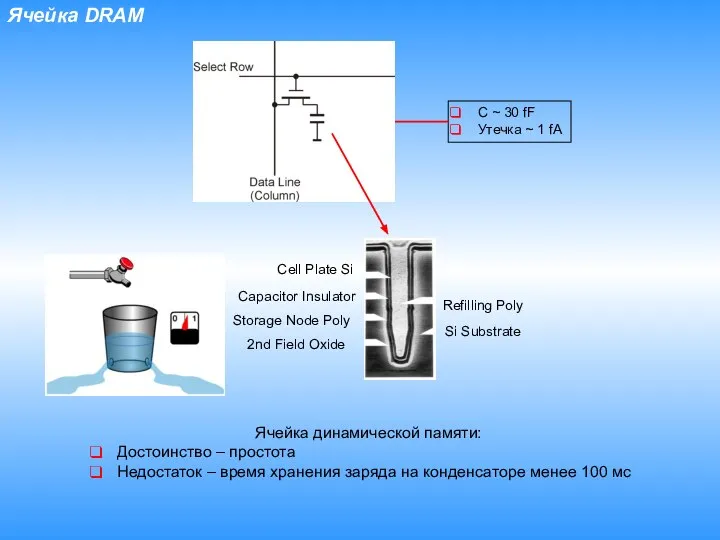

- 20. Ячейка DRAM Ячейка динамической памяти: Достоинство – простота Недостаток – время хранения заряда на конденсаторе менее

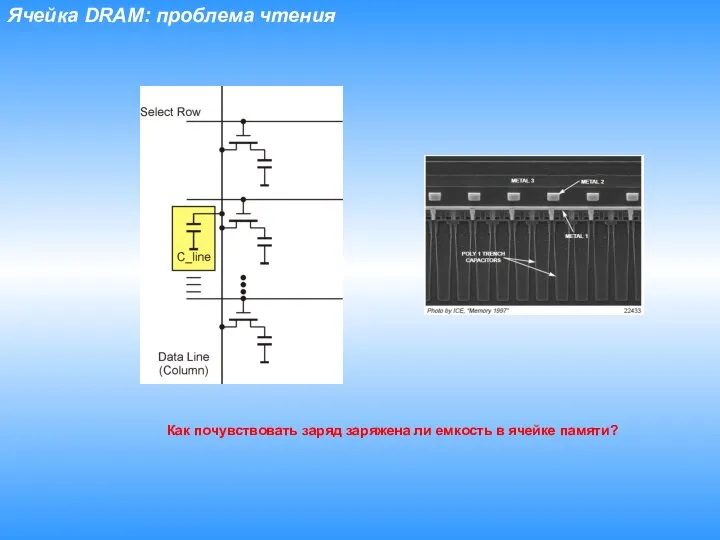

- 21. Ячейка DRAM: проблема чтения Как почувствовать заряд заряжена ли емкость в ячейке памяти?

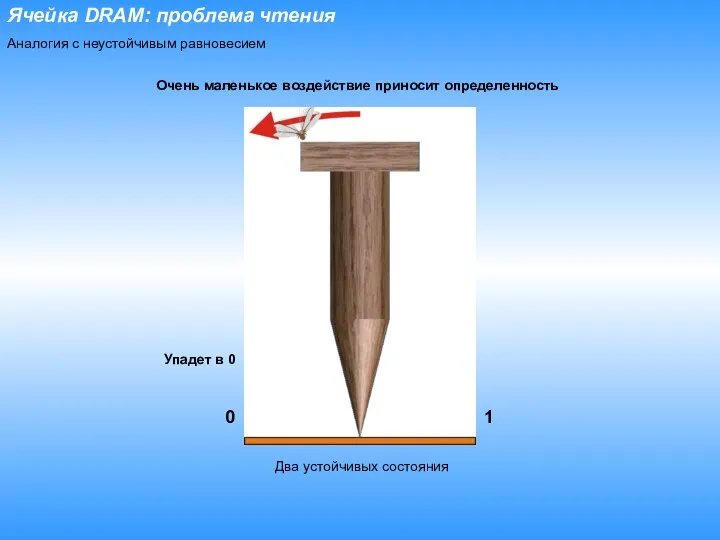

- 22. Ячейка DRAM: проблема чтения Аналогия с неустойчивым равновесием Куда упадет? 0 1 Два устойчивых состояния

- 23. Ячейка DRAM: проблема чтения Аналогия с неустойчивым равновесием Очень маленькое воздействие приносит определенность 0 1 Два

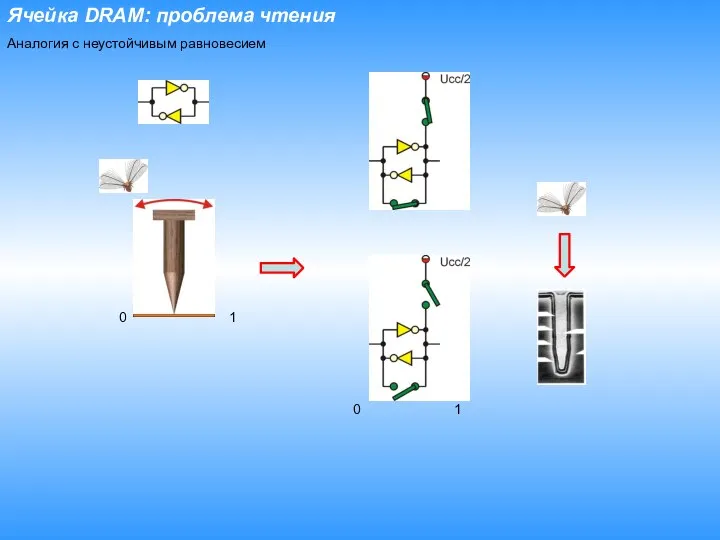

- 24. Ячейка DRAM: проблема чтения Аналогия с неустойчивым равновесием 0 1 0 1

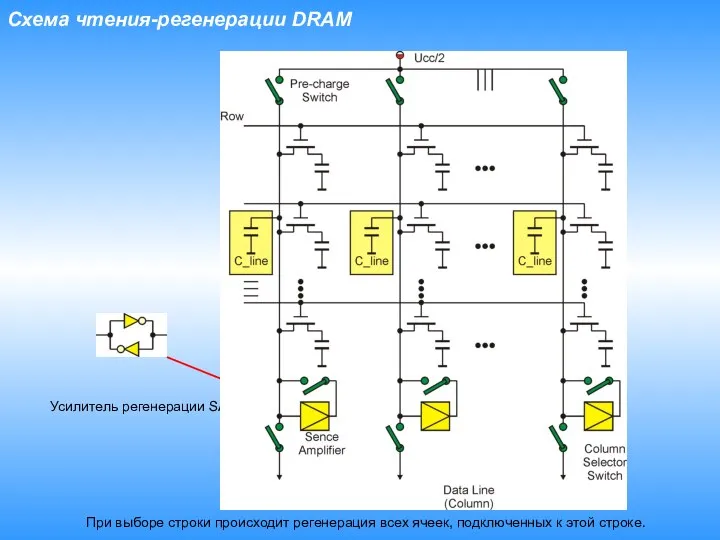

- 25. Схема чтения-регенерации DRAM Усилитель регенерации SA При выборе строки происходит регенерация всех ячеек, подключенных к этой

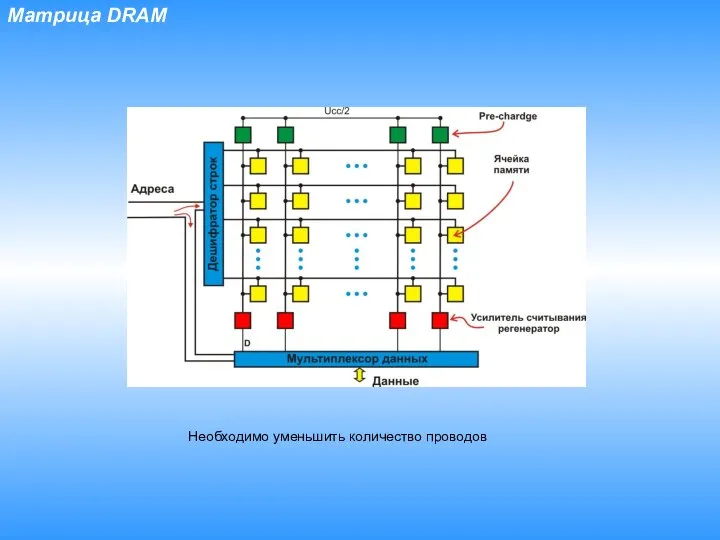

- 26. Матрица DRAM Необходимо уменьшить количество проводов

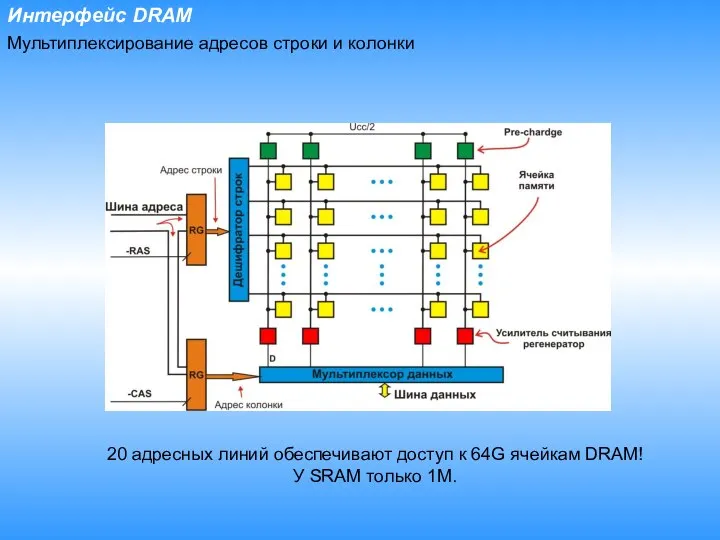

- 27. Интерфейс DRAM Мультиплексирование адресов строки и колонки 20 адресных линий обеспечивают доступ к 64G ячейкам DRAM!

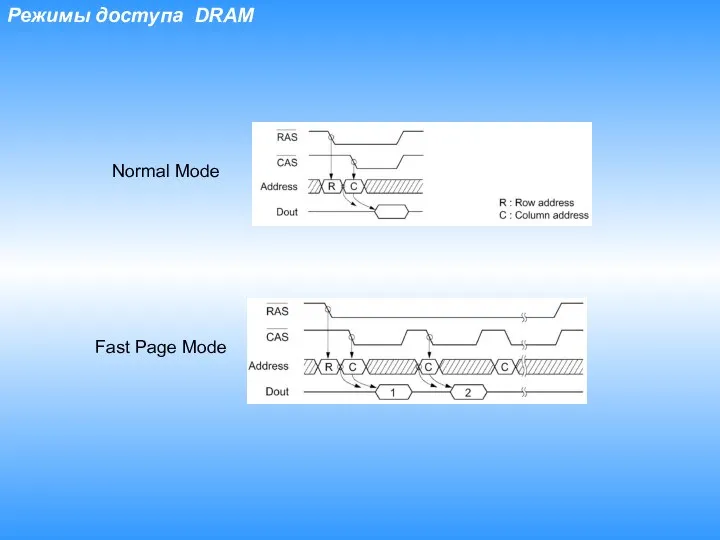

- 28. Режимы доступа DRAM Normal Mode Fast Page Mode

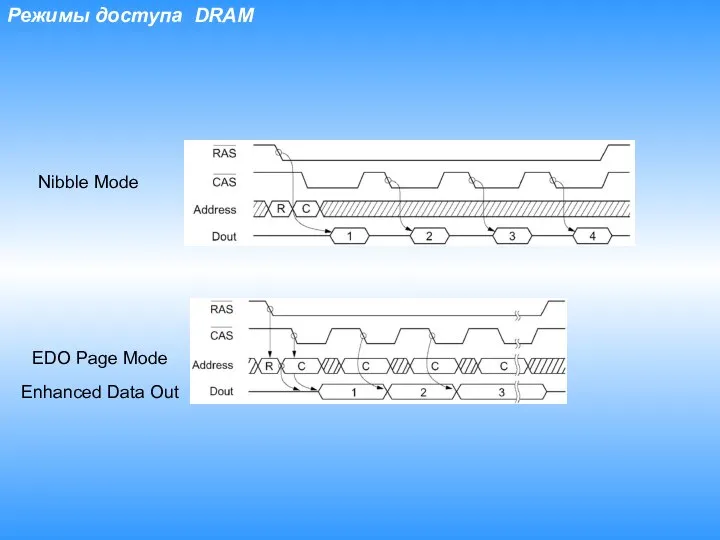

- 29. Режимы доступа DRAM Nibble Mode EDO Page Mode Enhanced Data Out

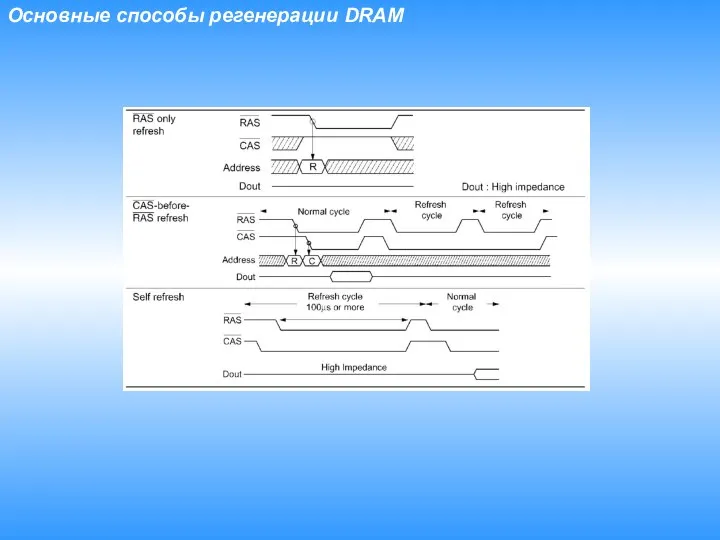

- 30. Основные способы регенерации DRAM

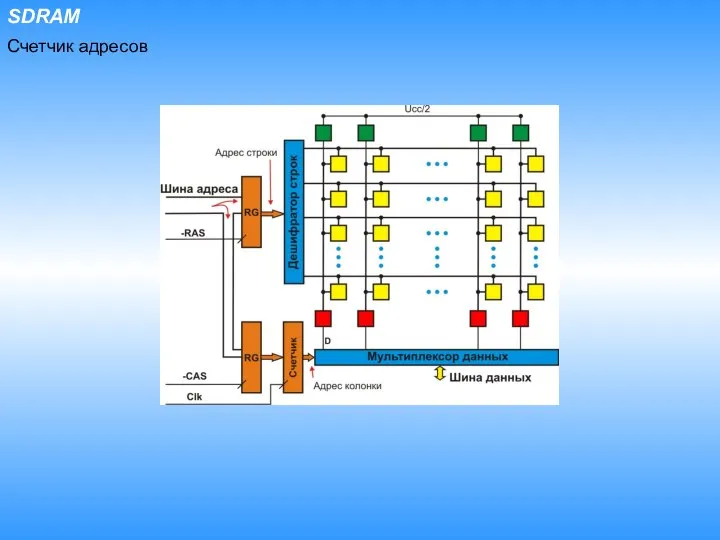

- 31. SDRAM Счетчик адресов

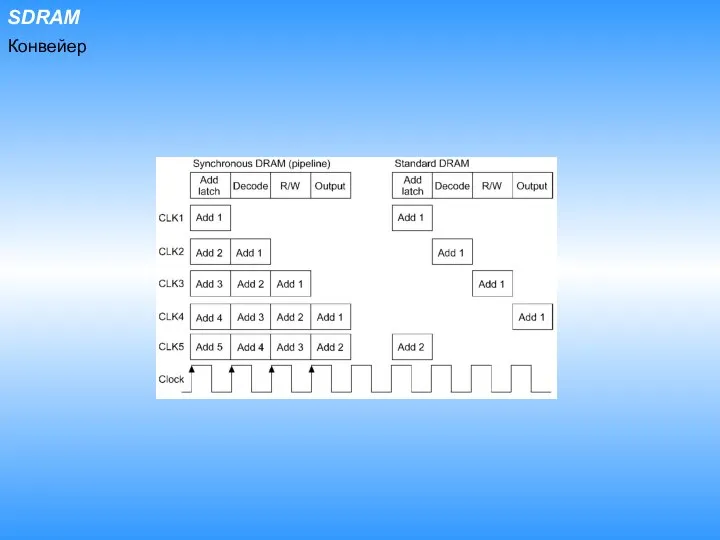

- 32. SDRAM Конвейер

- 34. Скачать презентацию

Порядок и условия исполнения наказаний, осуществляемых учреждениями УИС России. Тема № 5

Порядок и условия исполнения наказаний, осуществляемых учреждениями УИС России. Тема № 5 Journey of Hazard and Hope. Risks and Coping Strategies of Syrian Women Seeking Asylum in Austria

Journey of Hazard and Hope. Risks and Coping Strategies of Syrian Women Seeking Asylum in Austria ЭЛАСТИЧНОСТЬ СПРОСА И ПРЕДЛОЖЕНИЯ Тема 5

ЭЛАСТИЧНОСТЬ СПРОСА И ПРЕДЛОЖЕНИЯ Тема 5  Футбол. Основные правила

Футбол. Основные правила Социальные группы

Социальные группы Стадии предварительного расследования по уголовным делам. (Тема 2.2)

Стадии предварительного расследования по уголовным делам. (Тема 2.2) Таможенное дело в СССР

Таможенное дело в СССР Сопоставительный анализ современных методик преподавания иностранного языка Учитель иностранного языка МОУ «Курга

Сопоставительный анализ современных методик преподавания иностранного языка Учитель иностранного языка МОУ «Курга Система творческих заданий в преподавании элективных курсов Глаголева Татьяна Васильевна

Система творческих заданий в преподавании элективных курсов Глаголева Татьяна Васильевна ПРЕДМЕТ,МЕТОДОЛОГИЯ И ЗАДАЧИ КУРСА 1. ПРЕДМЕТ КУРСА; 2. ОБЪЕКТ ИЗУЧЕНИЯ; 3. МЕТОДОЛОГИЧЕСКИЕ И МЕТОДИЧЕСКИЕ ОСНОВЫ; 4.ЗАДАЧИ КУРСА.

ПРЕДМЕТ,МЕТОДОЛОГИЯ И ЗАДАЧИ КУРСА 1. ПРЕДМЕТ КУРСА; 2. ОБЪЕКТ ИЗУЧЕНИЯ; 3. МЕТОДОЛОГИЧЕСКИЕ И МЕТОДИЧЕСКИЕ ОСНОВЫ; 4.ЗАДАЧИ КУРСА. Алгоритмы и программы. Решение олимпиадных задач

Алгоритмы и программы. Решение олимпиадных задач Адресные ссылки в Microsoft Excel

Адресные ссылки в Microsoft Excel Культура во второй половине 19 в.

Культура во второй половине 19 в.  Тема 13. Власть и влияние

Тема 13. Власть и влияние  Презентация на тему "Мастер-класс по педагогическим технологиям " - скачать презентации по Педагогике

Презентация на тему "Мастер-класс по педагогическим технологиям " - скачать презентации по Педагогике Прямая в системе H, V, W (Лекция 2)

Прямая в системе H, V, W (Лекция 2) Сетевой график

Сетевой график Строки как одномерные массивы данных типа char (терминальные строки)

Строки как одномерные массивы данных типа char (терминальные строки) С Новым 2014-м годом! С годом спорта!

С Новым 2014-м годом! С годом спорта! Город – Герой Сталинград (17 июля 1942 - 2 февраля 1943)

Город – Герой Сталинград (17 июля 1942 - 2 февраля 1943) Главный генератор ГП311Б

Главный генератор ГП311Б Пищеварение в 12-перстной кишке, тонком и толстом кишечнике

Пищеварение в 12-перстной кишке, тонком и толстом кишечнике Принцип единственной обязанности. Адаптер. Принцип разделения интерфейсов

Принцип единственной обязанности. Адаптер. Принцип разделения интерфейсов Логистическая цепочка создания стоимости Исаева Катерина Казакова Катя ДС - 07

Логистическая цепочка создания стоимости Исаева Катерина Казакова Катя ДС - 07  Презентация Новая школа научных управлений

Презентация Новая школа научных управлений Мои лучшие, друзья!!!

Мои лучшие, друзья!!! Атлетическая гимнастика как средство физического развития детей среднего школьного возраста

Атлетическая гимнастика как средство физического развития детей среднего школьного возраста Презентация Оценка результативности поведения персонала

Презентация Оценка результативности поведения персонала