Содержание

- 2. Необходимость Тестирование ИС необходимо из-за несовершенства производственного процесса. Схемы могут иметь физические дефекты, называемые отказами, которые

- 3. Цели и задачи Цель тестирования – выявление отказов и идентификация неисправных микросхем Тестирование – важная задача,

- 4. Способ обнаружения неисправностей Существует единственный способ обнаружения неисправностей: На первичные входы (входные выводы микросхемы) поднимаются известные

- 5. Категории неисправностей Логические – неисправности, влияющие на логику работы схемы (выходные логические функции принимают значения отличные

- 6. Типы логических неисправностей Константные неисправности с залипанием в единице или в нуле (stuck-at-0, stuck-at-1) Константные неисправности

- 7. Константные неисправности с залипанием в 1 или в 0 Неисправности, когда на входе или на выходе

- 8. Константные неисправности с залипанием в открытом состоянии Неисправности, приводящие к установке на выходе схемы среднего значения

- 9. Константные неисправности типа обрыв Неисправности, приводящие к слабому изменению состояния схемы, в момент изменения внешних состояний

- 10. Неисправности типа замыкание Приводят к передаче на ветвь сигналов, соответствующих другим логическим переменным Возникают в результате

- 11. Моделирование неисправностей Используется модель константной неисправности: Простота Описывает влияние физической неисправности на входные/выходные сигналы

- 12. Модель 2х-входового вентиля И

- 13. Количество неисправностей Для k сигнальных линий существует 2k различных комбинаций одиночных неисправностей Для каждой сигнальной линии

- 14. Множественные неисправности Число комбинаций ошибок может быть очень велико Анализ множественных неисправностей – задача весьма сложная,

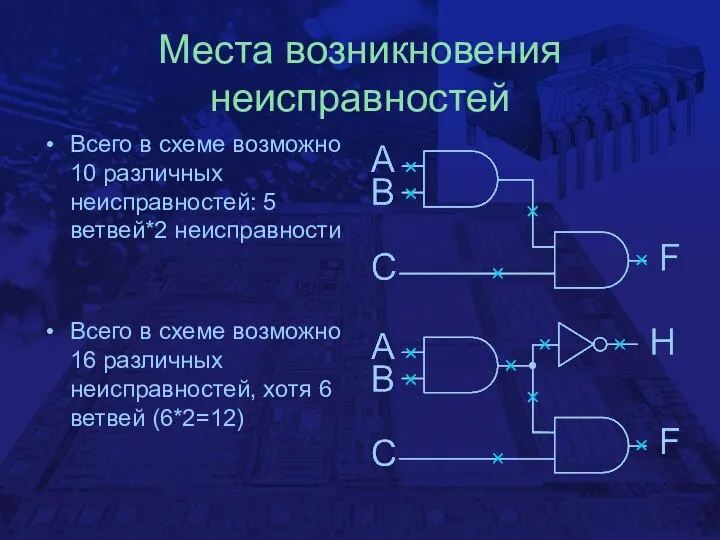

- 15. Места возникновения неисправностей Всего в схеме возможно 10 различных неисправностей: 5 ветвей*2 неисправности Всего в схеме

- 16. Тестирование ИС Входные комбинации, используемые для обнаружения неисправностей называются тестовыми векторами Набор тестовых векторов, обеспечивающий проверку

- 17. Методы поиска неисправностей Табличный (по таблице истинности). Подходит только для простых схем. Алгебраический (по выходной функции).

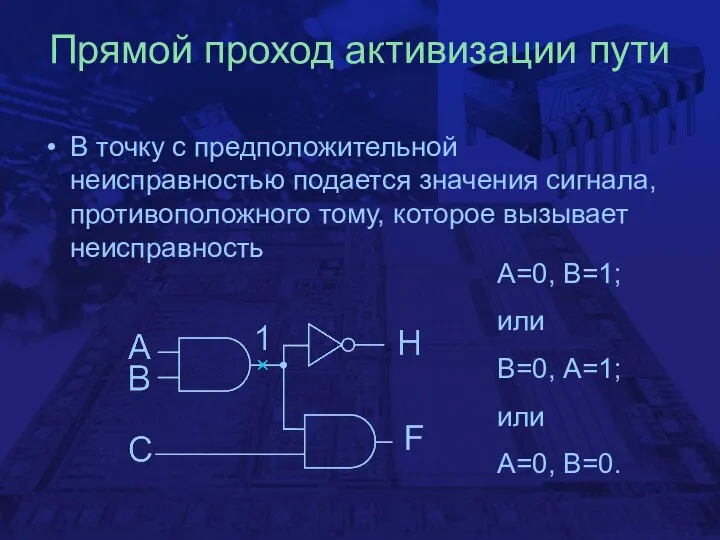

- 18. Прямой проход активизации пути В точку с предположительной неисправностью подается значения сигнала, противоположного тому, которое вызывает

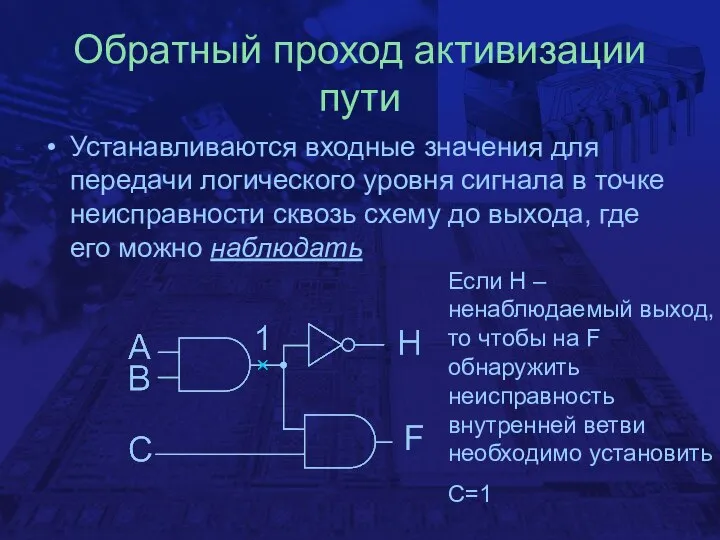

- 19. Обратный проход активизации пути Устанавливаются входные значения для передачи логического уровня сигнала в точке неисправности сквозь

- 20. Упрощение поиска неисправностей Для упрощения поиска неисправностей вводится обозначение сигнала D показывает, что сигнал =1, если

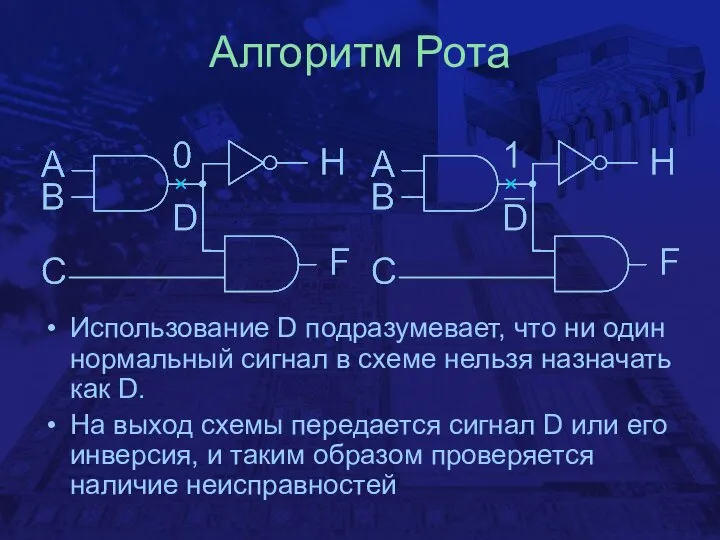

- 21. Алгоритм Рота Использование D подразумевает, что ни один нормальный сигнал в схеме нельзя назначать как D.

- 22. Поиск неисправностей по D-алгоритму Каждый вентиль на пути до первичного выхода должен быть активизирован Если схема

- 23. Эквивалентные неисправности Эквивалентные неисправности – это неисправности, которые детектируются одними и теми же тестовыми воздействиями (тестовыми

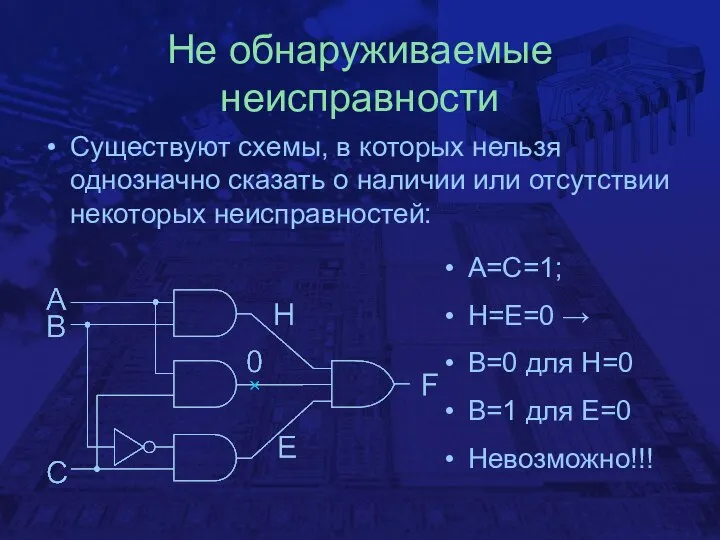

- 24. Не обнаруживаемые неисправности Существуют схемы, в которых нельзя однозначно сказать о наличии или отсутствии некоторых неисправностей:

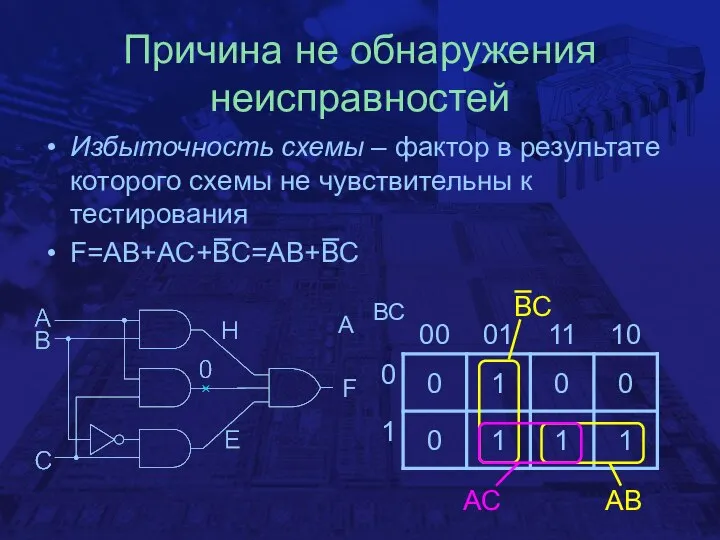

- 25. Причина не обнаружения неисправностей Избыточность схемы – фактор в результате которого схемы не чувствительны к тестирования

- 26. Тестирование последовательных схем Для тестирования последовательных схем необходимо: Установить схему в известное состояние После подачи сигналов

- 27. Метод сканирования пути Используется для обнаружения переменных состояний Режимы работы схемы: Нормальный режим – схема работает

- 28. Модель Мура для тестирования по методу сканирования пути

- 29. Проверка работоспособности последовательных схем Тестирование триггеров Тестирование комбинационной логики следующего состояния Тестирование комбинационной логики текущего состояния

- 30. Тестирование триггеров Осуществляется через тестирование регистра сдвига Mode_select=1 Через мультиплексор триггеры подключаются последовательно и выстраиваются в

- 31. Тестирование комбинационной логики следующего состояния Для тестирования комбинационной логики следующего состояния необходим доступ ко входам и

- 32. Тестирование комбинационной логики текущего состояния Задается тестовая последовательность на триггеры в режиме тестирования и затем проверяется

- 33. Встроенное самотестирование Используются внутренние генераторы последовательностей, а весь алгоритм тестирования соответствует методу сканирования пути

- 35. Скачать презентацию

Объемные изображения в скульптуре

Объемные изображения в скульптуре Урок русского языка. Тема: правописание безударных гласных, проверяемых ударением. (закрепл

Урок русского языка. Тема: правописание безударных гласных, проверяемых ударением. (закрепл Презентация на тему "Развитие фонематического слуха" - скачать презентации по Педагогике

Презентация на тему "Развитие фонематического слуха" - скачать презентации по Педагогике Презентация на тему "Развитие представлений о нравственности в обществе" - скачать презентации по Педагогике

Презентация на тему "Развитие представлений о нравственности в обществе" - скачать презентации по Педагогике Презентация "Портрет. Великие портретисты" - скачать презентации по МХК

Презентация "Портрет. Великие портретисты" - скачать презентации по МХК Система смазки двигателя внутреннего сгорания

Система смазки двигателя внутреннего сгорания Основные функции предпринимательства

Основные функции предпринимательства Лингвострановедение и его место в преподавании РКИ. Определение. Задачи. Методы

Лингвострановедение и его место в преподавании РКИ. Определение. Задачи. Методы Особенности физиологии плода

Особенности физиологии плода Судебно-медицинская экспертиза огнестрельных повреждений/ Огнестрельное оружие

Судебно-медицинская экспертиза огнестрельных повреждений/ Огнестрельное оружие П 11

П 11 Профилактика инфекционных заболеваний

Профилактика инфекционных заболеваний Фрикционные передачи

Фрикционные передачи Юпитер

Юпитер Творчество, творческая деятельность. Креативность

Творчество, творческая деятельность. Креативность Телемедицина 2019

Телемедицина 2019 Тема письменной экзаменационной работы «ОБУВНЫЕ КОЖЕВЕННЫЕ ТОВАРЫ»

Тема письменной экзаменационной работы «ОБУВНЫЕ КОЖЕВЕННЫЕ ТОВАРЫ»  Изучение массивов. (Лабораторная работа 7)

Изучение массивов. (Лабораторная работа 7) Современные культуроведческие подходы к обучению ИЯ

Современные культуроведческие подходы к обучению ИЯ Бағдарлау – мотивациялық кезең. “Тез тауып, бөгелмей айт” ойыны

Бағдарлау – мотивациялық кезең. “Тез тауып, бөгелмей айт” ойыны Презентация "Экономические школы" - скачать презентации по Экономике

Презентация "Экономические школы" - скачать презентации по Экономике Приложение: косвенный доступ к параметрам FC и FB

Приложение: косвенный доступ к параметрам FC и FB Разработка системы автоматизированного проектирования для расчета и построения цилиндрического редуктора

Разработка системы автоматизированного проектирования для расчета и построения цилиндрического редуктора Добротность открытых оптических резонаторов

Добротность открытых оптических резонаторов Олимпийские игры в Древней Греции

Олимпийские игры в Древней Греции Строительство школы нового поколения в г. Мичуринске

Строительство школы нового поколения в г. Мичуринске Готов ли ваш ребенок к школе? Практические рекомендации для родителей

Готов ли ваш ребенок к школе? Практические рекомендации для родителей Использование ресурсов Интернет в работе учителя

Использование ресурсов Интернет в работе учителя