Содержание

- 2. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 3. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 4. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 5. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 6. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 7. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 8. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 9. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 10. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 11. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 12. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 13. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 14. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 15. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 16. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 17. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 18. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 19. Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics Faculty, Electronic Devices & Systems,

- 21. Скачать презентацию

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Переключение задач.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

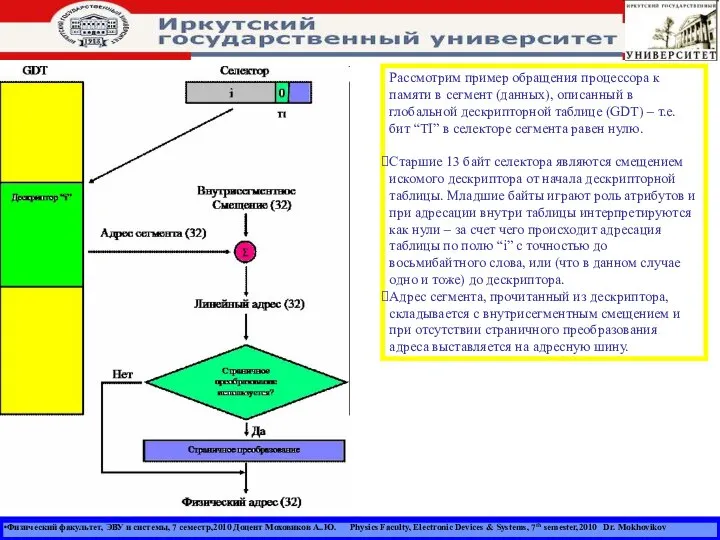

Рассмотрим пример обращения процессора к памяти в сегмент (данных), описанный в глобальной дескрипторной таблице (GDT) – т.е. бит “TI” в селекторе сегмента равен нулю.

Старшие 13 байт селектора являются смещением искомого дескриптора от начала дескрипторной таблицы. Младшие байты играют роль атрибутов и при адресации внутри таблицы интерпретируются как нули – за счет чего происходит адресация таблицы по полю “i” с точностью до восьмибайтного слова, или (что в данном случае одно и тоже) до дескриптора.

Адрес сегмента, прочитанный из дескриптора, складывается с внутрисегментным смещением и при отсутствии страничного преобразования адреса выставляется на адресную шину.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

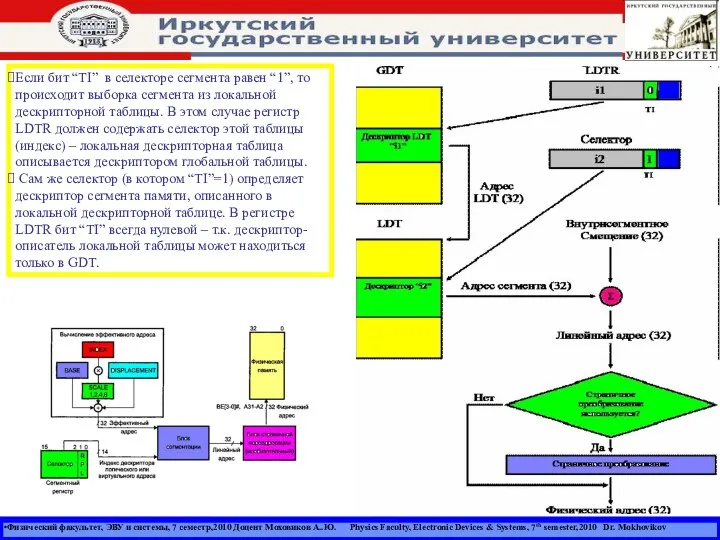

Если бит “TI” в селекторе сегмента равен “1”, то происходит выборка сегмента из локальной дескрипторной таблицы. В этом случае регистр LDTR должен содержать селектор этой таблицы (индекс) – локальная дескрипторная таблица описывается дескриптором глобальной таблицы.

Сам же селектор (в котором “TI”=1) определяет дескриптор сегмента памяти, описанного в локальной дескрипторной таблице. В регистре LDTR бит “TI” всегда нулевой – т.к. дескриптор-описатель локальной таблицы может находиться только в GDT.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Сегмент состояния задачи

TSS

Ну очень наглядно!!

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Уже лучше!!!

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

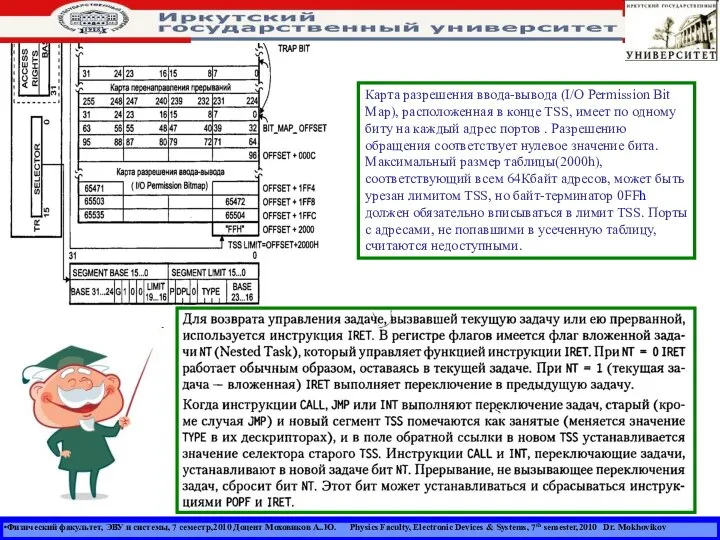

Карта разрешения ввода-вывода (I/O Permission Bit Map), расположенная в конце TSS, имеет по одному биту на каждый адрес портов . Разрешению обращения соответствует нулевое значение бита. Максимальный размер таблицы(2000h), соответствующий всем 64Кбайт адресов, может быть урезан лимитом TSS, но байт-терминатор 0FFh должен обязательно вписываться в лимит TSS. Порты с адресами, не попавшими в усеченную таблицу, считаются недоступными.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Страничное управление памятью

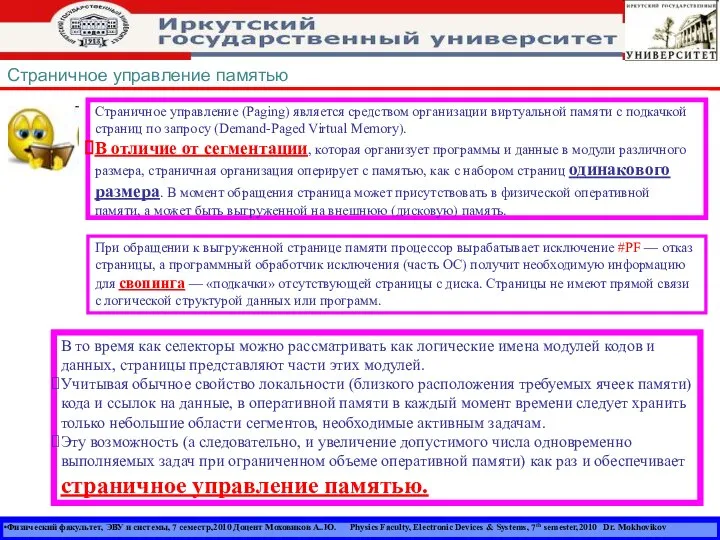

Страничное управление (Paging) является средством организации виртуальной памяти с подкачкой страниц по запросу (Demand-Paged Virtual Memory).

В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация оперирует с памятью, как с набором страниц одинакового размера. В момент обращения страница может присутствовать в физической оперативной памяти, а может быть выгруженной на внешнюю (дисковую) память.

При обращении к выгруженной странице памяти процессор вырабатывает исключение #PF — отказ страницы, а программный обработчик исключения (часть ОС) получит необходимую информацию для свопинга — «подкачки» отсутствующей страницы с диска. Страницы не имеют прямой связи с логической структурой данных или программ.

В то время как селекторы можно рассматривать как логические имена модулей кодов и данных, страницы представляют части этих модулей.

Учитывая обычное свойство локальности (близкого расположения требуемых ячеек памяти) кода и ссылок на данные, в оперативной памяти в каждый момент времени следует хранить только небольшие области сегментов, необходимые активным задачам.

Эту возможность (а следовательно, и увеличение допустимого числа одновременно выполняемых задач при ограниченном объеме оперативной памяти) как раз и обеспечивает страничное управление памятью.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

!

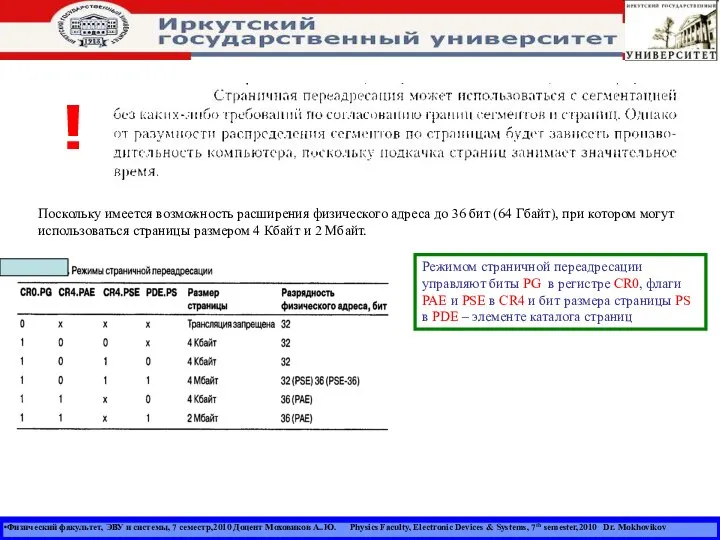

Поскольку имеется возможность расширения физического адреса до 36 бит (64 Гбайт), при котором могут использоваться страницы размером 4 Кбайт и 2 Мбайт.

Режимом страничной переадресации управляют биты PG в регистре CR0, флаги PAE и PSE в СR4 и бит размера страницы PS в PDE – элементе каталога страниц

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

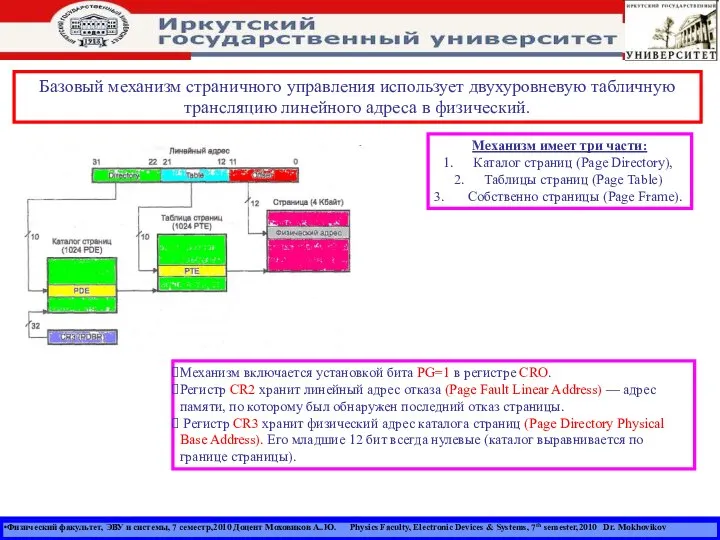

Базовый механизм страничного управления использует двухуровневую табличную трансляцию линейного адреса в физический.

Механизм имеет три части:

Каталог страниц (Page Directory),

Таблицы страниц (Page Table)

Собственно страницы (Page Frame).

Механизм включается установкой бита PG=1 в регистре CRO.

Регистр CR2 хранит линейный адрес отказа (Page Fault Linear Address) — адрес памяти, по которому был обнаружен последний отказ страницы.

Регистр CR3 хранит физический адрес каталога страниц (Page Directory Physical Base Address). Его младшие 12 бит всегда нулевые (каталог выравнивается по границе страницы).

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

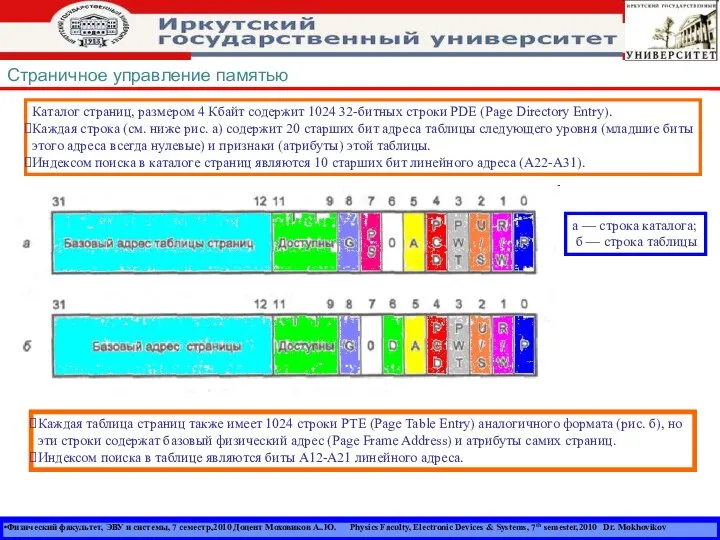

а — строка каталога;

б — строка таблицы

Каталог страниц, размером 4 Кбайт содержит 1024 32-битных строки РDЕ (Page Directory Entry).

Каждая строка (см. ниже рис. а) содержит 20 старших бит адреса таблицы следующего уровня (младшие биты этого адреса всегда нулевые) и признаки (атрибуты) этой таблицы.

Индексом поиска в каталоге страниц являются 10 старших бит линейного адреса (А22-А31).

Страничное управление памятью

Каждая таблица страниц также имеет 1024 строки РТЕ (Page Table Entry) аналогичного формата (рис. б), но эти строки содержат базовый физический адрес (Page Frame Address) и атрибуты самих страниц.

Индексом поиска в таблице являются биты А12-А21 линейного адреса.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

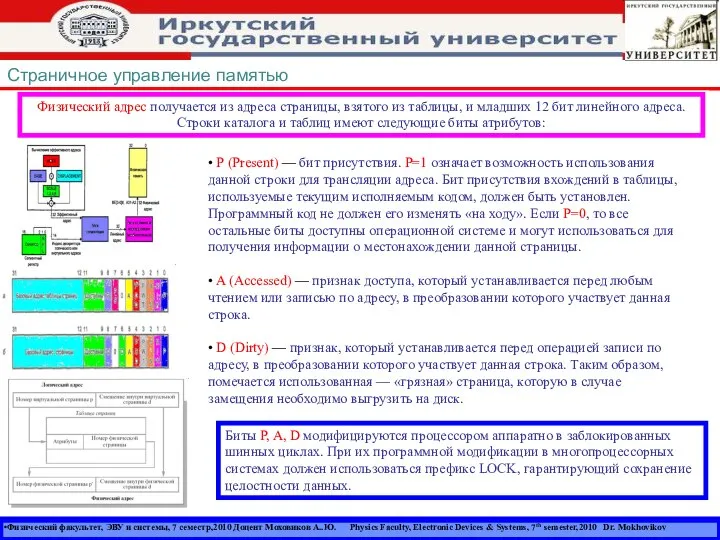

Страничное управление памятью

Физический адрес получается из адреса страницы, взятого из таблицы, и младших 12 бит линейного адреса. Строки каталога и таблиц имеют следующие биты атрибутов:

• Р (Present) — бит присутствия. Р=1 означает возможность использования данной строки для трансляции адреса. Бит присутствия вхождений в таблицы, используемые текущим исполняемым кодом, должен быть установлен. Программный код не должен его изменять «на ходу». Если Р=0, то все остальные биты доступны операционной системе и могут использоваться для получения информации о местонахождении данной страницы.

• A (Accessed) — признак доступа, который устанавливается перед любым чтением или записью по адресу, в преобразовании которого участвует данная строка.

• D (Dirty) — признак, который устанавливается перед операцией записи по адресу, в преобразовании которого участвует данная строка. Таким образом, помечается использованная — «грязная» страница, которую в случае замещения необходимо выгрузить на диск.

Биты Р, А, D модифицируются процессором аппаратно в заблокированных шинных циклах. При их программной модификации в многопроцессорных системах должен использоваться префикс LOCK, гарантирующий сохранение целостности данных.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Страничное управление памятью

Поле OS Reserved программно используется по усмотрению ОС и может хранить, например, информацию о «возрасте» страницы, необходимую для реализации замещения по алгоритму LRU (Least Recently Used — наиболее долго не использовавшаяся страница замещается первой).

Бит PWT (Page Write Through) определяет политику записи при кэшировании, а бит PCD (Page Cache Disable) запрещает кэширование памяти для обслуживаемых страниц или таблиц.

Бит PS (Page Size) задает размер страницы. При PS=0 страница имеет размер 4 Кбайт, PS=1 используется в расширениях РАЕ и PSE.

Бит G (Global), появившийся в Р6, определяет глобальность страницы. Он анализируется только в строке, указывающей на страницу физической памяти (в РТЕ для страниц в 4 Кбайт, в PDE — для страниц 2 Мбайт или 4 Мбайт). Этот бит, управляемый только программно, позволяет пометить страницы глобального использования (например, ядра ОС). При установленном бите PGE в регистре CR4 строки с указателями на глобальные таблицы не будут аннулироваться в TLB при загрузке CR3 или переключении задач, что снижает издержки обслуживания виртуальной памяти.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Страничное управление памятью

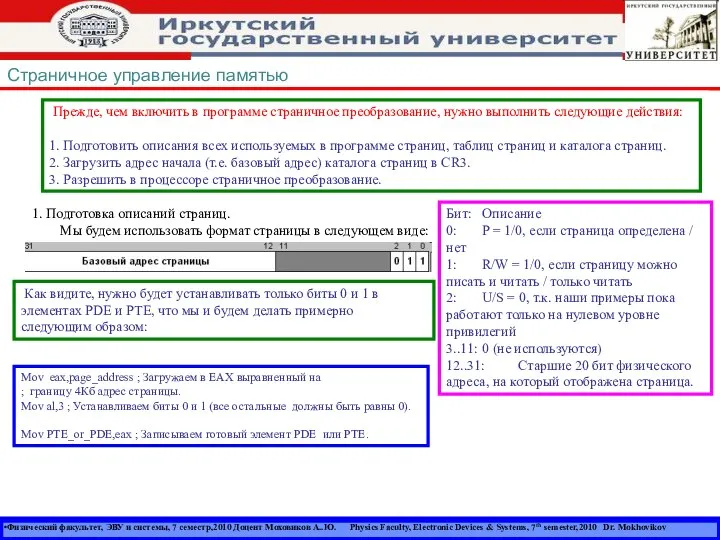

Прежде, чем включить в программе страничное преобразование, нужно выполнить следующие действия:

1. Подготовить описания всех используемых в программе страниц, таблиц страниц и каталога страниц.

2. Загрузить адрес начала (т.е. базовый адрес) каталога страниц в CR3.

3. Разрешить в процессоре страничное преобразование.

1. Подготовка описаний страниц.

Мы будем использовать формат страницы в следующем виде:

Бит: Описание

0: P = 1/0, если страница определена / нет

1: R/W = 1/0, если страницу можно писать и читать / только читать

2: U/S = 0, т.к. наши примеры пока работают только на нулевом уровне привилегий

3..11: 0 (не используются)

12..31: Старшие 20 бит физического адреса, на который отображена страница.

Как видите, нужно будет устанавливать только биты 0 и 1 в элементах PDE и PTE, что мы и будем делать примерно следующим образом:

Mov eax,page_address ; Загружаем в EAX выравненный на ; границу 4Кб адрес страницы.

Mov al,3 ; Устанавливаем биты 0 и 1 (все остальные должны быть равны 0).

Mov PTE_or_PDE,eax ; Записываем готовый элемент PDE или PTE.

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

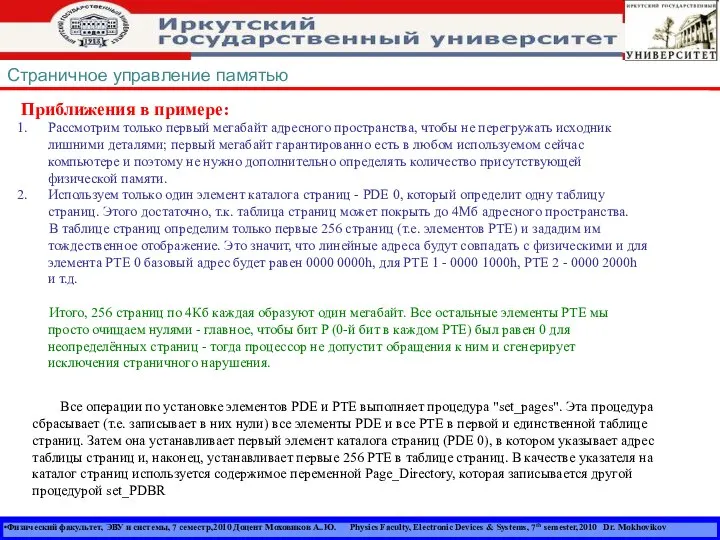

Страничное управление памятью

Приближения в примере:

Рассмотрим только первый мегабайт адресного пространства, чтобы не перегружать исходник лишними деталями; первый мегабайт гарантированно есть в любом используемом сейчас компьютере и поэтому не нужно дополнительно определять количество присутствующей физической памяти.

Используем только один элемент каталога страниц - PDE 0, который определит одну таблицу страниц. Этого достаточно, т.к. таблица страниц может покрыть до 4Мб адресного пространства.

В таблице страниц определим только первые 256 страниц (т.е. элементов PTE) и зададим им тождественное отображение. Это значит, что линейные адреса будут совпадать с физическими и для элемента PTE 0 базовый адрес будет равен 0000 0000h, для PTE 1 - 0000 1000h, PTE 2 - 0000 2000h и т.д.

Итого, 256 страниц по 4Кб каждая образуют один мегабайт. Все остальные элементы PTE мы просто очищаем нулями - главное, чтобы бит P (0-й бит в каждом PTE) был равен 0 для неопределённых страниц - тогда процессор не допустит обращения к ним и сгенерирует исключения страничного нарушения.

Все операции по установке элементов PDE и PTE выполняет процедура "set_pages". Эта процедура сбрасывает (т.е. записывает в них нули) все элементы PDE и все PTE в первой и единственной таблице страниц. Затем она устанавливает первый элемент каталога страниц (PDE 0), в котором указывает адрес таблицы страниц и, наконец, устанавливает первые 256 PTE в таблице страниц. В качестве указателя на каталог страниц используется содержимое переменной Page_Directory, которая записывается другой процедурой set_PDBR

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

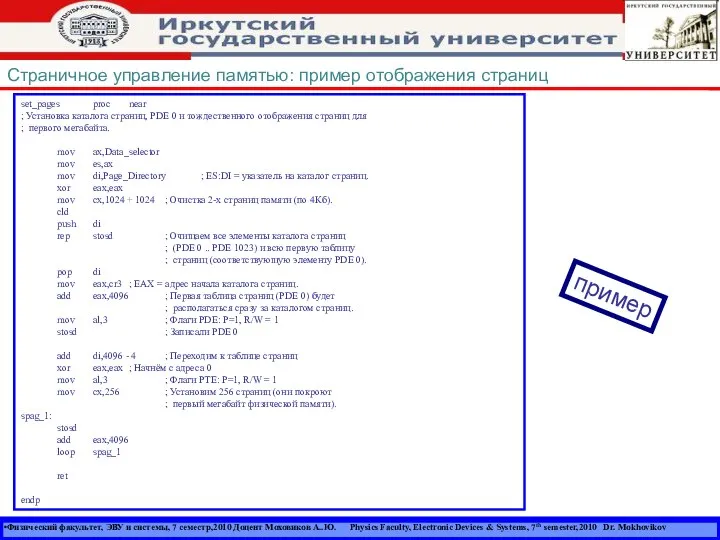

Страничное управление памятью: пример отображения страниц

set_pages proc near

; Установка каталога страниц, PDE 0 и тождественного отображения страниц для

; первого мегабайта.

mov ax,Data_selector

mov es,ax

mov di,Page_Directory ; ES:DI = указатель на каталог страниц.

xor eax,eax

mov cx,1024 + 1024 ; Очистка 2-х страниц памяти (по 4Кб).

cld

push di

rep stosd ; Очищаем все элементы каталога страниц

; (PDE 0 .. PDE 1023) и всю первую таблицу

; страниц (соответствующую элементу PDE 0).

pop di

mov eax,cr3 ; EAX = адрес начала каталога страниц.

add eax,4096 ; Первая таблица страниц (PDE 0) будет

; располагаться сразу за каталогом страниц.

mov al,3 ; Флаги PDE: P=1, R/W = 1

stosd ; Записали PDE 0

add di,4096 - 4 ; Переходим к таблице страниц

xor eax,eax ; Начнём с адреса 0

mov al,3 ; Флаги PTE: P=1, R/W = 1

mov cx,256 ; Установим 256 страниц (они покроют

; первый мегабайт физической памяти).

spag_1:

stosd

add eax,4096

loop spag_1

ret

endp

пример

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

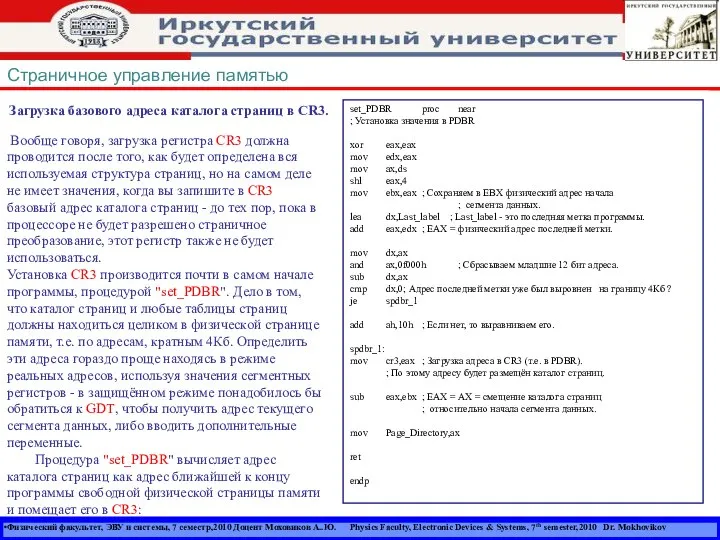

Страничное управление памятью

Загрузка базового адреса каталога страниц в CR3.

Вообще говоря, загрузка регистра CR3 должна проводится после того, как будет определена вся используемая структура страниц, но на самом деле не имеет значения, когда вы запишите в CR3 базовый адрес каталога страниц - до тех пор, пока в процессоре не будет разрешено страничное преобразование, этот регистр также не будет использоваться.

Установка CR3 производится почти в самом начале программы, процедурой "set_PDBR". Дело в том, что каталог страниц и любые таблицы страниц должны находиться целиком в физической странице памяти, т.е. по адресам, кратным 4Кб. Определить эти адреса гораздо проще находясь в режиме реальных адресов, используя значения сегментных регистров - в защищённом режиме понадобилось бы обратиться к GDT, чтобы получить адрес текущего сегмента данных, либо вводить дополнительные переменные.

Процедура "set_PDBR" вычисляет адрес каталога страниц как адрес ближайшей к концу программы свободной физической страницы памяти и помещает его в CR3:

set_PDBR proc near

; Установка значения в PDBR

xor eax,eax

mov edx,eax

mov ax,ds

shl eax,4

mov ebx,eax ; Сохраняем в EBX физический адрес начала

; сегмента данных.

lea dx,Last_label ; Last_label - это последняя метка программы.

add eax,edx ; EAX = физический адрес последней метки.

mov dx,ax

and ax,0f000h ; Сбрасываем младшие 12 бит адреса.

sub dx,ax

cmp dx,0; Адрес последней метки уже был выровнен на границу 4Кб ?

je spdbr_1

add ah,10h ; Если нет, то выравниваем его.

spdbr_1:

mov cr3,eax ; Загрузка адреса в CR3 (т.е. в PDBR).

; По этому адресу будет размещён каталог страниц.

sub eax,ebx ; EAX = AX = смещение каталога страниц

; относительно начала сегмента данных.

mov Page_Directory,ax

ret

endp

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

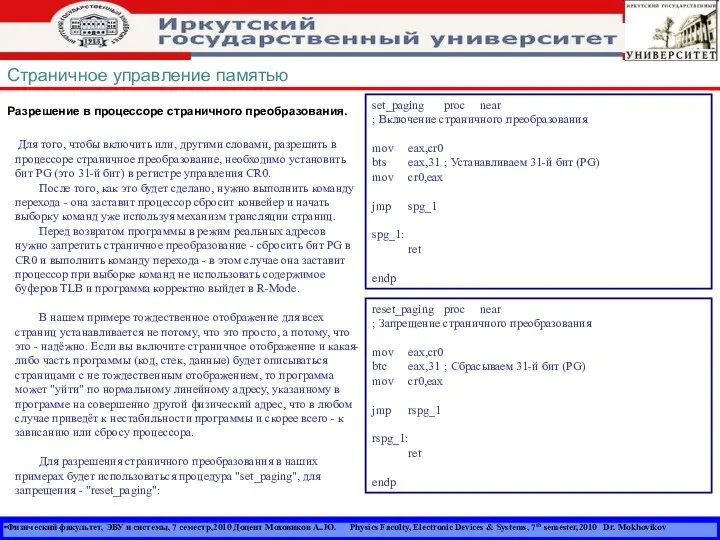

Страничное управление памятью

Разрешение в процессоре страничного преобразования.

Для того, чтобы включить или, другими словами, разрешить в процессоре страничное преобразование, необходимо установить бит PG (это 31-й бит) в регистре управления CR0.

После того, как это будет сделано, нужно выполнить команду перехода - она заставит процессор сбросит конвейер и начать выборку команд уже используя механизм трансляции страниц.

Перед возвратом программы в режим реальных адресов нужно запретить страничное преобразование - сбросить бит PG в CR0 и выполнить команду перехода - в этом случае она заставит процессор при выборке команд не использовать содержимое буферов TLB и программа корректно выйдет в R-Mode.

В нашем примере тождественное отображение для всех страниц устанавливается не потому, что это просто, а потому, что это - надёжно. Если вы включите страничное отображение и какая-либо часть программы (код, стек, данные) будет описываться страницами с не тождественным отображением, то программа может "уйти" по нормальному линейному адресу, указанному в программе на совершенно другой физический адрес, что в любом случае приведёт к нестабильности программы и скорее всего - к зависанию или сбросу процессора.

Для разрешения страничного преобразования в наших примерах будет использоваться процедура "set_paging", для запрещения - "reset_paging":

set_paging proc near

; Включение страничного преобразования

mov eax,cr0

bts eax,31 ; Устанавливаем 31-й бит (PG)

mov cr0,eax

jmp spg_1

spg_1:

ret

endp

reset_paging proc near

; Запрещение страничного преобразования

mov eax,cr0

btc eax,31 ; Сбрасываем 31-й бит (PG)

mov cr0,eax

jmp rspg_1

rspg_1:

ret

endp

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Используемые Интернет-ресурсы:

http://sasm.narod.ru/docs/pm/pm_mem/chap_6.htm

http://sasm.narod.ru/docs/pm/pm_mem/chap_7.htm

http://citforum.ru/operating_systems/sos/glava_7.shtml

http://x86.migera.ru/text/glava_2.html

http://www.intuit.ru/department/os/osintro/10/

http://www.moodle.ipm.kstu.ru/mod/resource/view.php?id=57

Анализ данных

Анализ данных  Процессоры от 1-го поколения до последнего

Процессоры от 1-го поколения до последнего 4. Java OOP. 6. Inner Classes

4. Java OOP. 6. Inner Classes Разработка метода и программного модуля управления шестизвенным манипулятором на основе геометрического подхода

Разработка метода и программного модуля управления шестизвенным манипулятором на основе геометрического подхода Sports in Russia

Sports in Russia «В ногу» со временем! Компания «SMART photographer». Инстамат

«В ногу» со временем! Компания «SMART photographer». Инстамат Презентация Экспертиза рыбных консервов

Презентация Экспертиза рыбных консервов Информационная модель ЛДП

Информационная модель ЛДП Анемия

Анемия Программирование алгоритмов обработки сложных данных

Программирование алгоритмов обработки сложных данных Гарантии законности и правопорядка в современном обществе Работу подготовили студентки 2 курса ФТД гр.1309 Михайлова Анастасия и Х

Гарантии законности и правопорядка в современном обществе Работу подготовили студентки 2 курса ФТД гр.1309 Михайлова Анастасия и Х Система отраслевого или корпоративного нормирования

Система отраслевого или корпоративного нормирования Русские прялки

Русские прялки Буквы Зз - Сс - презентация для начальной школы

Буквы Зз - Сс - презентация для начальной школы «Решение задач с помощью пропорций» - презентация по Алгебре

«Решение задач с помощью пропорций» - презентация по Алгебре Базисные условия поставки товаров – это общепризнанные международные торговые обычаи, соответствующие содержанию и характер

Базисные условия поставки товаров – это общепризнанные международные торговые обычаи, соответствующие содержанию и характер Анализ результатов ГИА по истории и методические рекомендации для учителей

Анализ результатов ГИА по истории и методические рекомендации для учителей Физиологические основы оптимизации спортивной тренировки

Физиологические основы оптимизации спортивной тренировки Интеллектуальная собственность Объекты патентного права (технические решения). Лекция 8

Интеллектуальная собственность Объекты патентного права (технические решения). Лекция 8 Виникнення козацтва

Виникнення козацтва Классический деловой стиль

Классический деловой стиль Модуль 5 Биполярное расстройство и тревожное/паническое расстройство

Модуль 5 Биполярное расстройство и тревожное/паническое расстройство  Органы государственной власти РФ: президент

Органы государственной власти РФ: президент  Домашняя утварь в крестьянском доме

Домашняя утварь в крестьянском доме Способы передачи данных

Способы передачи данных Высшее образование в России 2

Высшее образование в России 2  Придумать или найти

Придумать или найти Страхование рисков

Страхование рисков