Физический факультет, ЭВУ и системы, 7 семестр,2010 Доцент Моховиков А..Ю. Physics

Faculty, Electronic Devices & Systems, 7th semester,2010 Dr. Mokhovikov

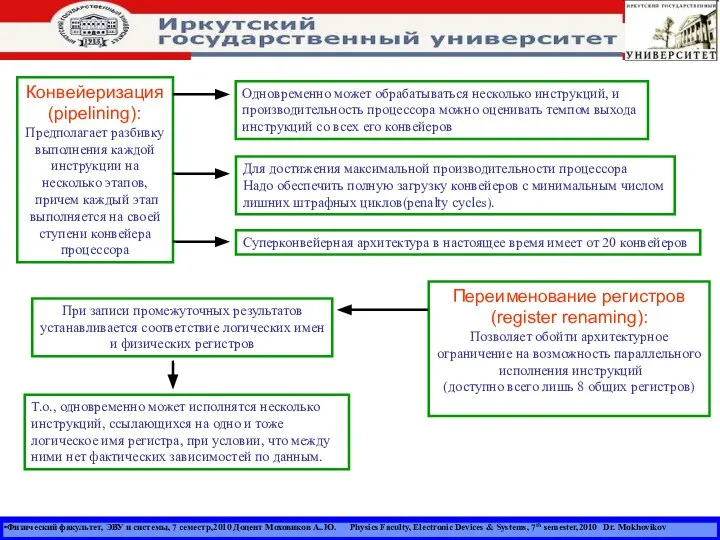

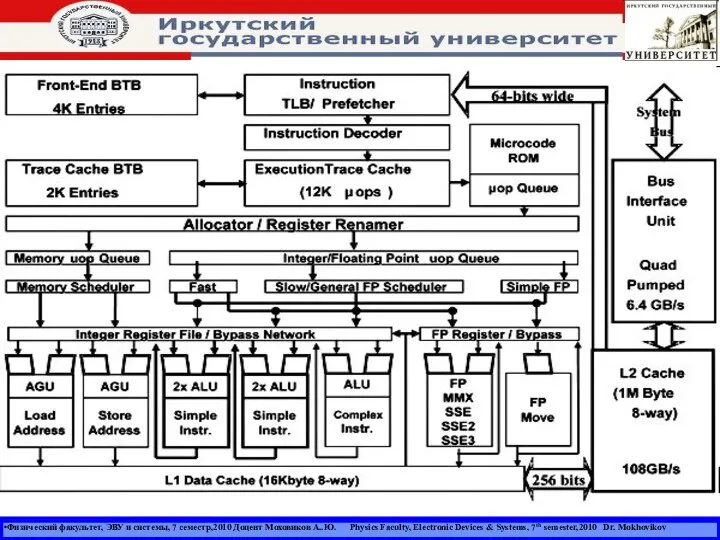

Конвейеризация

(pipelining):

Предполагает разбивку выполнения каждой инструкции на несколько этапов,

причем каждый этап выполняется на своей ступени конвейера процессора

Одновременно может обрабатываться несколько инструкций, и

производительность процессора можно оценивать темпом выхода

инструкций со всех его конвейеров

Для достижения максимальной производительности процессора

Надо обеспечить полную загрузку конвейеров с минимальным числом

лишних штрафных циклов(penalty cycles).

Суперконвейерная архитектура в настоящее время имеет от 20 конвейеров

Переименование регистров

(register renaming):

Позволяет обойти архитектурное

ограничение на возможность параллельного

исполнения инструкций

(доступно всего лишь 8 общих регистров)

При записи промежуточных результатов

устанавливается соответствие логических имен

и физических регистров

Т.о., одновременно может исполнятся несколько

инструкций, ссылающихся на одно и тоже

логическое имя регистра, при условии, что между

ними нет фактических зависимостей по данным.

Значение имущественное правоотношения

Значение имущественное правоотношения Три закона Кеплера

Три закона Кеплера Истоки русского театра

Истоки русского театра Уроки национальных культур на территории Кировградского городского округа

Уроки национальных культур на территории Кировградского городского округа Асмус Кристина

Асмус Кристина Теория вероятностей и математическая статистика

Теория вероятностей и математическая статистика Потребительская корзина в странах мира.

Потребительская корзина в странах мира. кросcворд Таможенное дело

кросcворд Таможенное дело Проектирование цифровой системы телевещания поселка

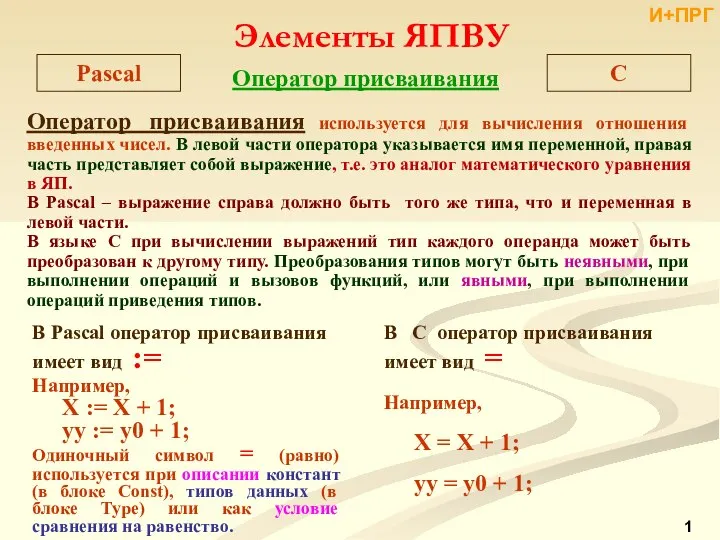

Проектирование цифровой системы телевещания поселка Операторы ЯП- присваивание,условный, комментарий

Операторы ЯП- присваивание,условный, комментарий  Методична розробка Використання опорних схем і конспектів на уроках української мови Учитель вищої категорії Мігуш Т.А.

Методична розробка Використання опорних схем і конспектів на уроках української мови Учитель вищої категорії Мігуш Т.А. Царь Давид

Царь Давид Политическая культура

Политическая культура Информационные технологии Диаграммы Диаграммы вариантов использования (прецедентов)

Информационные технологии Диаграммы Диаграммы вариантов использования (прецедентов) ИЛЛЮСТРИРОВАННЫЙ СЛОВАРЬ АРХИТЕКТУРНЫХ ТЕРМИНОВ Выполнил учитель высшей категории Богатырева Наталья Витальевна

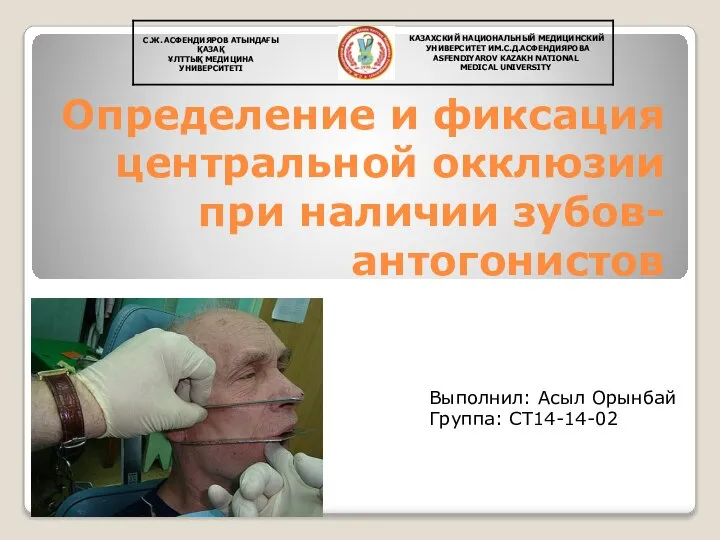

ИЛЛЮСТРИРОВАННЫЙ СЛОВАРЬ АРХИТЕКТУРНЫХ ТЕРМИНОВ Выполнил учитель высшей категории Богатырева Наталья Витальевна Определение и фиксация центральной окклюзии при наличии зубов-антогонистов

Определение и фиксация центральной окклюзии при наличии зубов-антогонистов  Серебряный век русской культуры

Серебряный век русской культуры Критические нагрузки, расчетное сопротивление грунта

Критические нагрузки, расчетное сопротивление грунта Философия культуры А. Тойнби

Философия культуры А. Тойнби Haskell тіліндегі деректердің күрделі құрылымын өңдеу. Зертханалық жұмыс №6

Haskell тіліндегі деректердің күрделі құрылымын өңдеу. Зертханалық жұмыс №6 Легенды и мифы Китая

Легенды и мифы Китая «Транс-Онего». Ежегодный международный зимний многодневный кайт-марафон, протяженностью 350 км, по акватории Онежского озера

«Транс-Онего». Ежегодный международный зимний многодневный кайт-марафон, протяженностью 350 км, по акватории Онежского озера ТАЙМ-менеджмент Управление временем Базовый курс Семинар на тему общего менеджмента

ТАЙМ-менеджмент Управление временем Базовый курс Семинар на тему общего менеджмента La cocina española

La cocina española Развитие силовых способностей учащихся на уроках физической культуры средствами легкоатлетических упражнений. (8 класс)

Развитие силовых способностей учащихся на уроках физической культуры средствами легкоатлетических упражнений. (8 класс) Современные методы управления

Современные методы управления Семинарная работа студента группы 15-1016 отделения очного обучения МУХАМЕТЗЯНОВОЙ РАЛИНЫ ИЛЬДАРОВНЫ

Семинарная работа студента группы 15-1016 отделения очного обучения МУХАМЕТЗЯНОВОЙ РАЛИНЫ ИЛЬДАРОВНЫ Короткі відомості про життя і творчість Івана Карпенка–Карого, театр корифеїв. Трагікомедія «Сто тисяч»

Короткі відомості про життя і творчість Івана Карпенка–Карого, театр корифеїв. Трагікомедія «Сто тисяч»