Содержание

- 2. Организация функционирования ЭВМ с магистральной архитектурой Комплект интегральных схем, из которых состоит ЭВМ, называется микропроцессорным комплектом

- 3. Организация функционирования ЭВМ с магистральной архитектурой Все устройства ЭВМ делятся на центральные и периферийные. Центральные устройства

- 4. Организация функционирования ЭВМ с магистральной архитектурой В центральных устройствах основным узлом, связывающим микропроцессорный комплект в единое

- 5. Организация функционирования ЭВМ с магистральной архитектурой Количество проводников в шине называется разрядностью (шириной) шины. Для ША

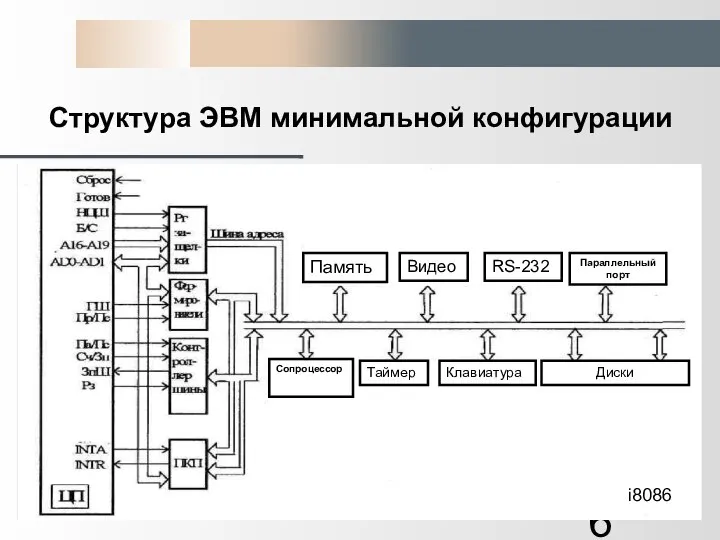

- 6. Структура ЭВМ минимальной конфигурации i8086 Память Видео RS-232 Параллельный порт Сопроцессор Таймер Клавиатура Диски

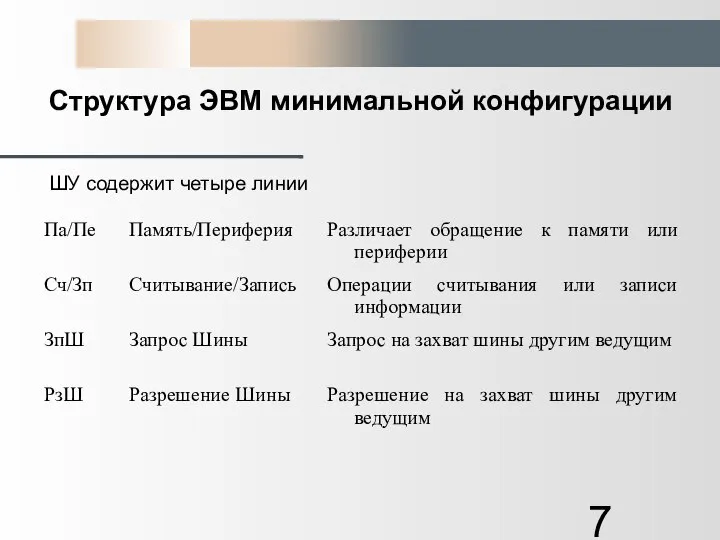

- 7. Структура ЭВМ минимальной конфигурации ШУ содержит четыре линии

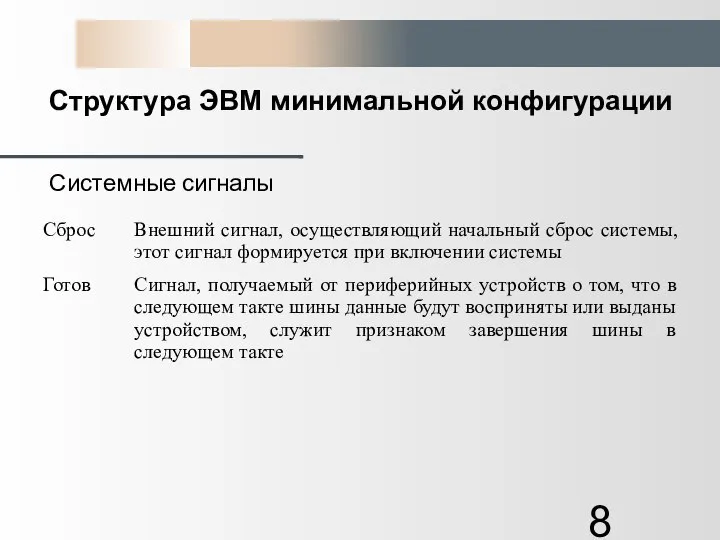

- 8. Структура ЭВМ минимальной конфигурации Системные сигналы

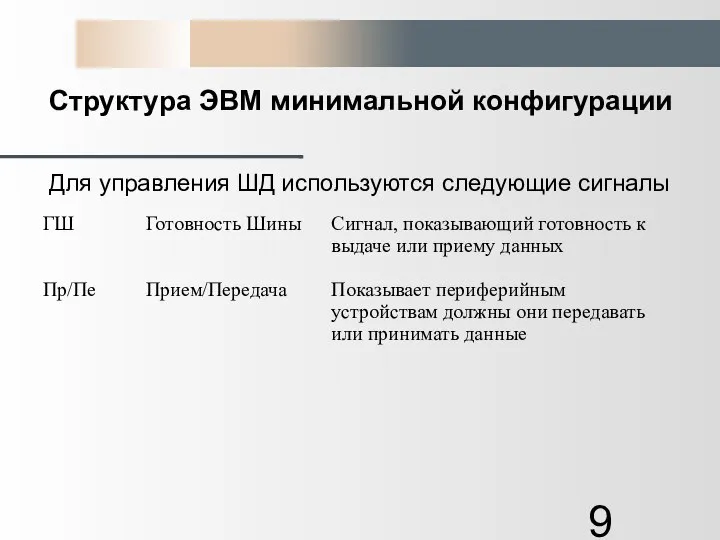

- 9. Структура ЭВМ минимальной конфигурации Для управления ШД используются следующие сигналы

- 10. Структура ЭВМ минимальной конфигурации Для управления ША используются следующие сигналы Сигнал INTR - запрос на разрешения

- 11. Цикл работы и стандарты системной шины СШ синхронизирована сигналами тактового генератора процессора. Цикл шины состоит из

- 12. Цикл работы и стандарты системной шины В конце такта регистры защёлки фиксируют адрес и он снимается

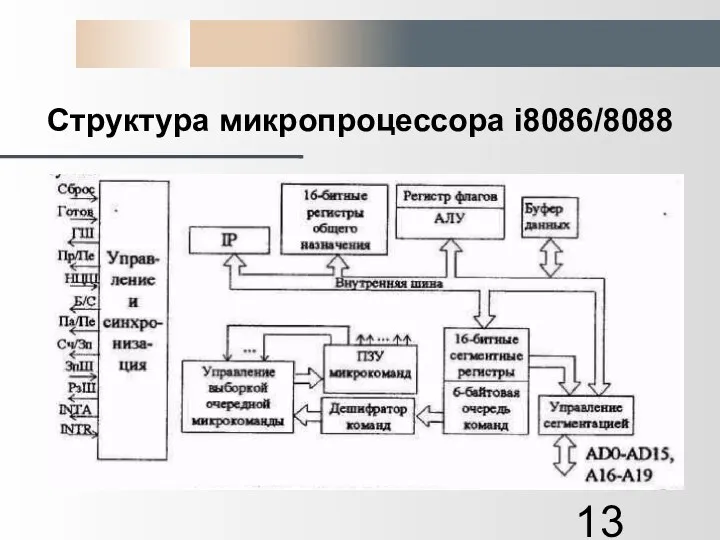

- 13. Структура микропроцессора i8086/8088

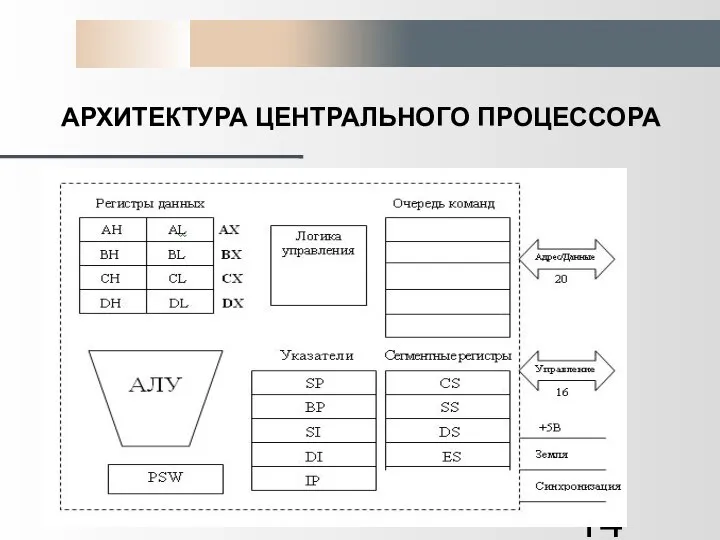

- 14. АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

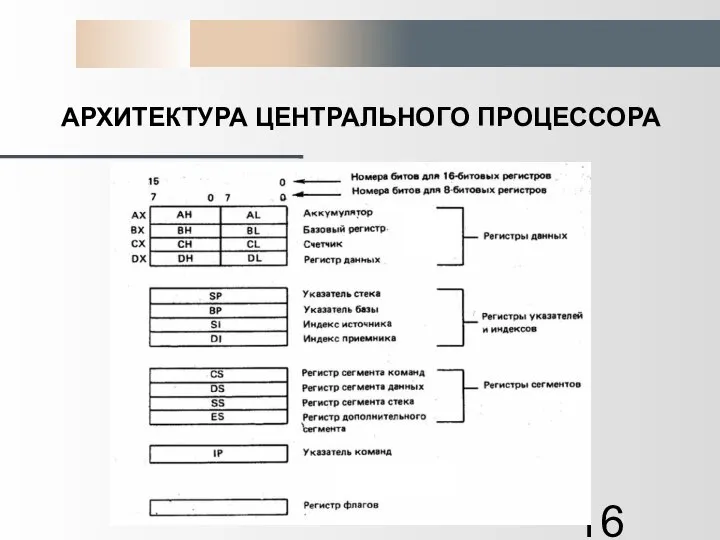

- 15. АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА Внутри микропроцессора информация содержится в группе 16-битовых элементов, называемых регистрами. Всего он имеет

- 16. АРХИТЕКТУРА ЦЕНТРАЛЬНОГО ПРОЦЕССОРА

- 17. Регистры данных В зависимости от того, чем Вы оперируете: 16-битовыми словами или 8-битовыми байтами, регистры данных

- 18. Регистры данных Регистр АХ, аккумулятор (accumulator), используется при умножении и делении слов, в операциях ввода-вывода и

- 19. Регистры данных Регистр ВХ, базовый регистр (base register), часто используется при адресации данных в памяти. Регистр

- 20. Регистры сегментов Регистр сегмента команд CS (code segment) указывает на сегмент, содержащий текущую исполняемую программу. Для

- 21. Регистры сегментов Регистр сегмента данных DS (data segment) указывает на текущий сегмент данных, обычно содержащий используемые

- 22. Регистры указателей и индексов Для вычисления адреса команды в сегменте команд микропроцессор извлекает номер блока памяти

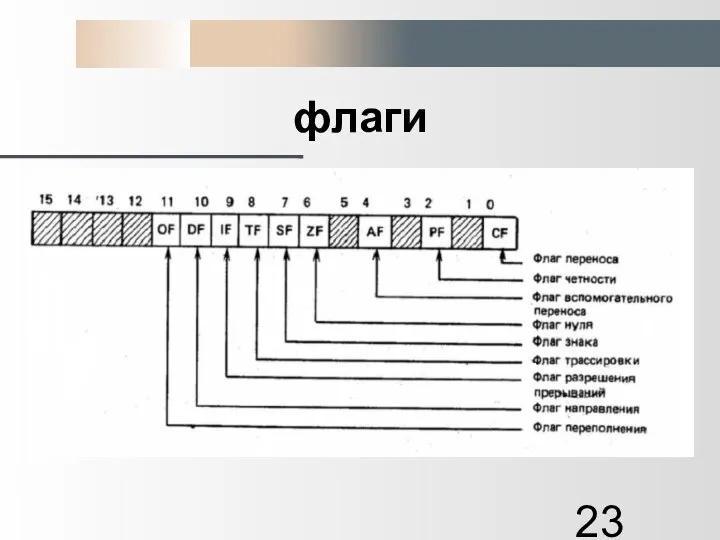

- 23. флаги

- 24. флаги В 16-битовом регистре флагов фиксируется информация о текущем состоянии дел, которая может помочь программе принять

- 25. флаги 1. Бит 0, флаг переноса CF (carry flag), равен 1, если произошел перенос единицы при

- 26. флаги 2. Бит 2, флаг четности PF (parity flag), равен 1, если в результате операции получено

- 27. флаги 3. Бит 4, вспомогательный флаг переноса AF (auxiliary carry flag), аналогичен флагу CF, только контролирует

- 28. флаги 5. Бит 7, флаг знака SF (sign flag), имеет значение только при операциях над числами

- 29. флаги 6. Бит 8, флаг трассировки TF (trap flag), разрешает микропроцессору исполнять программу "по шагам" и

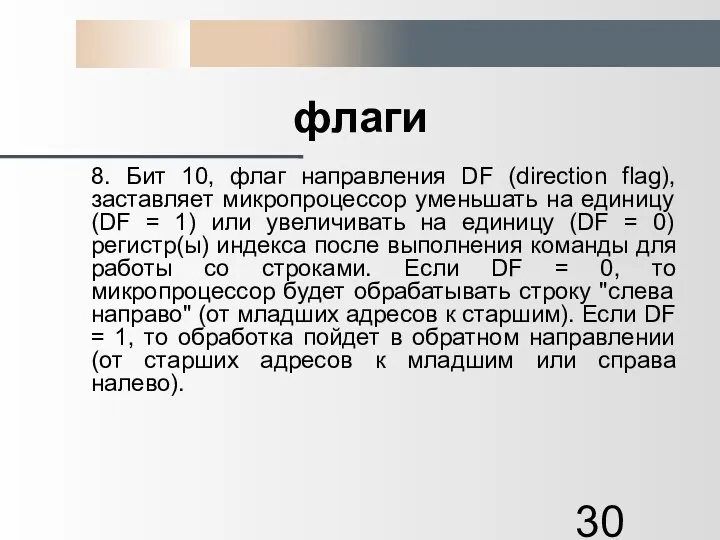

- 30. флаги 8. Бит 10, флаг направления DF (direction flag), заставляет микропроцессор уменьшать на единицу (DF =

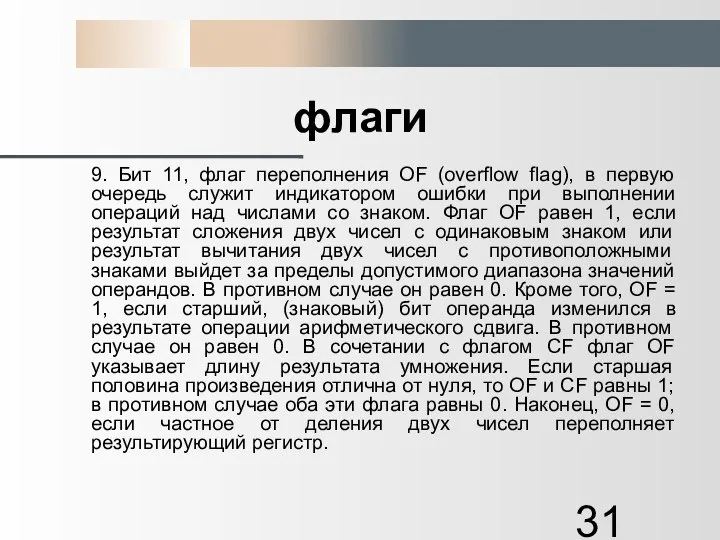

- 31. флаги 9. Бит 11, флаг переполнения OF (overflow flag), в первую очередь служит индикатором ошибки при

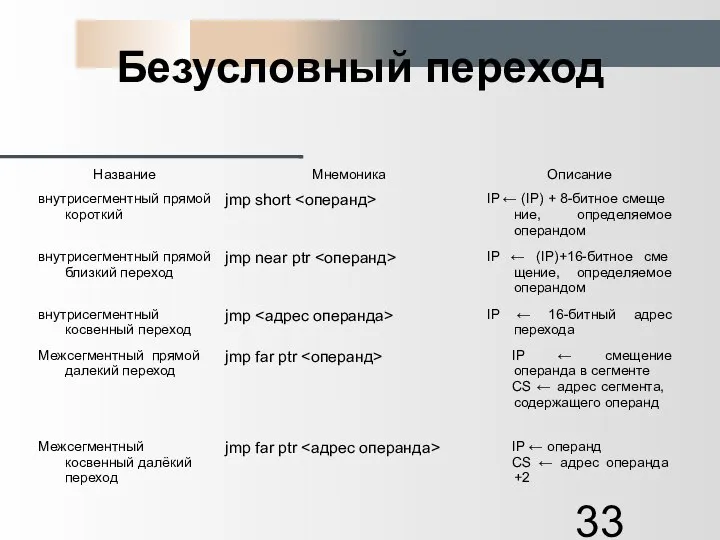

- 32. Безусловный переход jmp [ ptr ] операнд. - тип перехода short (короткий) – смещение 127 байтов

- 33. Безусловный переход

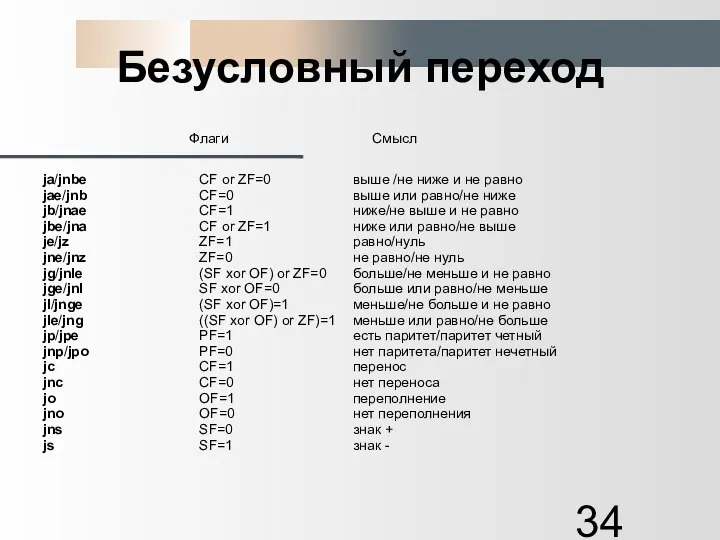

- 34. Безусловный переход

- 35. Циклы loop[ ] Инструкция loop использует содержимое регистра СХ как счетчик повторений цикла. Команда loop уменьшает

- 36. Пример Дан массив из десяти слов, содержащих целые числа. Требуется найти максимальное значение в массиве.

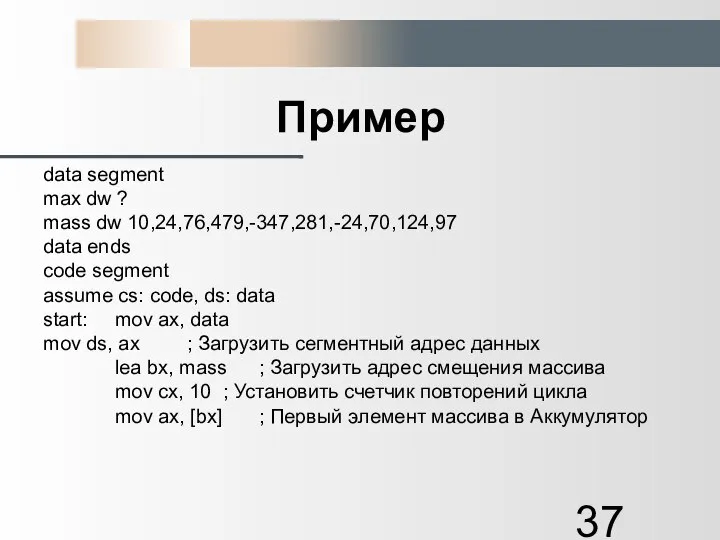

- 37. Пример data segment max dw ? mass dw 10,24,76,479,-347,281,-24,70,124,97 data ends code segment assume cs: code,

- 39. Скачать презентацию

![Безусловный переход jmp [ ptr ] операнд. - тип перехода short](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1193285/slide-31.jpg)

![Циклы loop[ ] Инструкция loop использует содержимое регистра СХ как счетчик](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1193285/slide-34.jpg)

О технологической возможности реализации микроэлектронных проектов сети дизайн-центров университетов РФ

О технологической возможности реализации микроэлектронных проектов сети дизайн-центров университетов РФ Введение в Matlab Лекция 1

Введение в Matlab Лекция 1  Объёмные геометрические фигуры Математика, 1 класс

Объёмные геометрические фигуры Математика, 1 класс Разработка модульного мульти-интерфейсного устройства управления распределенными системами

Разработка модульного мульти-интерфейсного устройства управления распределенными системами Программирование на языке С++. Работа со строками. Функции библиотеки algorithm

Программирование на языке С++. Работа со строками. Функции библиотеки algorithm Презентация "Программирование. Паскаль." - скачать презентации по Информатике

Презентация "Программирование. Паскаль." - скачать презентации по Информатике Сравнительный анализ (ПланФикс, Мегаплан, Модуль 1C:PM Управление проектами для 1С:ERP)

Сравнительный анализ (ПланФикс, Мегаплан, Модуль 1C:PM Управление проектами для 1С:ERP) Кодирование текстовой информации

Кодирование текстовой информации Презентация "Линейные алгоритмы" - скачать презентации по Информатике

Презентация "Линейные алгоритмы" - скачать презентации по Информатике Алгоритм

Алгоритм Вводная часть по целям и задачам обучения. Конфигурация ПК и его содержание. Программы личной организации труда

Вводная часть по целям и задачам обучения. Конфигурация ПК и его содержание. Программы личной организации труда ТЕМА 5 Протоколы передачи данных

ТЕМА 5 Протоколы передачи данных  Презентация "ОСНОВЫ АЛГОРИТМИЗАЦИИ" - скачать презентации по Информатике

Презентация "ОСНОВЫ АЛГОРИТМИЗАЦИИ" - скачать презентации по Информатике Засоби масової інформації

Засоби масової інформації Введение в СУБД ORACLE. Администрирование баз данных. Лекция 1

Введение в СУБД ORACLE. Администрирование баз данных. Лекция 1 Startup project. Активний тембр-блок з п’яти смуговим еквалайзером VirtusSound

Startup project. Активний тембр-блок з п’яти смуговим еквалайзером VirtusSound Формирование изображения на экране монитора

Формирование изображения на экране монитора Информатика Саушская средняя школа Разработка Габдрахмановой З. К.

Информатика Саушская средняя школа Разработка Габдрахмановой З. К. Измерение информации. Алфавитный и содержательный подходы

Измерение информации. Алфавитный и содержательный подходы Информатика Учебник для 6 класса Л. Босова Выполнил: Фролов. А. 231группа

Информатика Учебник для 6 класса Л. Босова Выполнил: Фролов. А. 231группа  Планирование и проектирование организаций

Планирование и проектирование организаций Основні команди мови SQL

Основні команди мови SQL Линейные программы. Лекция 4

Линейные программы. Лекция 4 Презентация "ШТУРМ" - скачать презентации по Информатике

Презентация "ШТУРМ" - скачать презентации по Информатике HTML-верстка

HTML-верстка Интернет как глобальная информационная система

Интернет как глобальная информационная система Микропроцессор

Микропроцессор  ПО ПК. Системное ПО

ПО ПК. Системное ПО