Содержание

- 2. Микросхемы малой степени интеграции

- 3. Управление сложностью в микроэлектронике

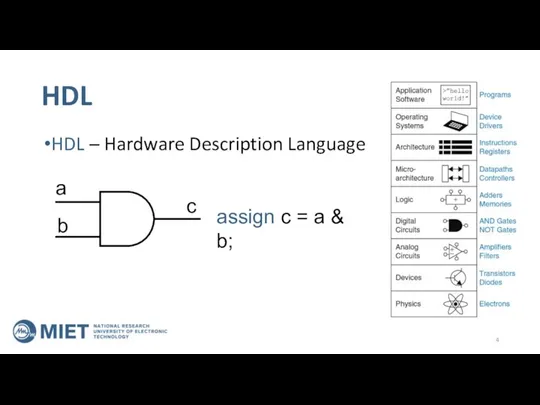

- 4. HDL HDL – Hardware Description Language a b c assign c = a & b;

- 5. HDL. Маршрут проектирования

- 6. HDL. Выбор Verilog VHDL

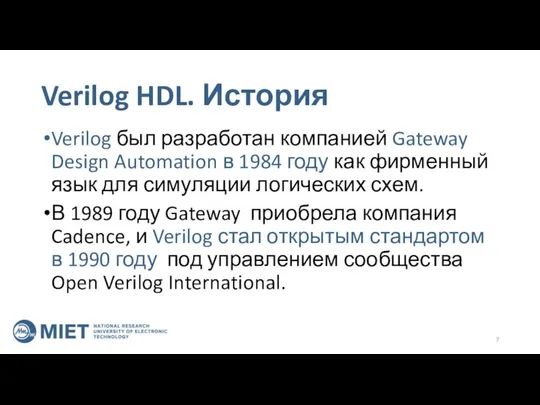

- 7. Verilog HDL. История Verilog был разработан компанией Gateway Design Automation в 1984 году как фирменный язык

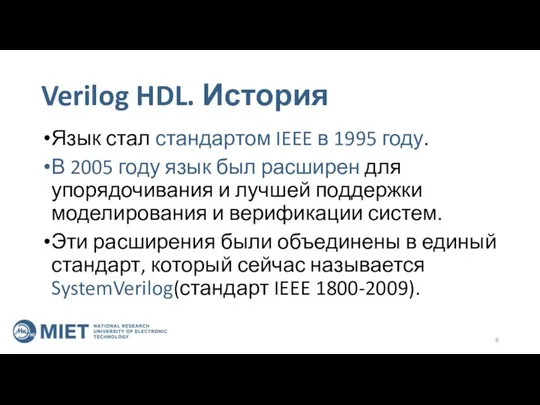

- 8. Verilog HDL. История Язык стал стандартом IEEE в 1995 году. В 2005 году язык был расширен

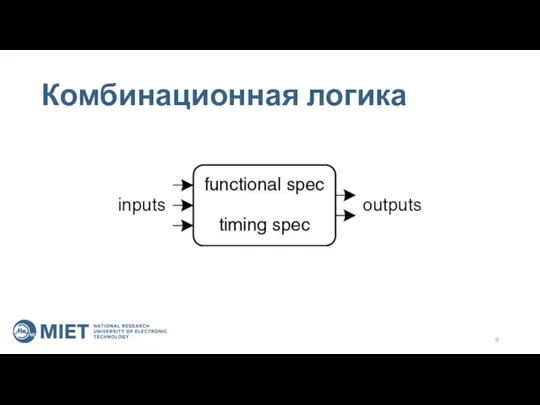

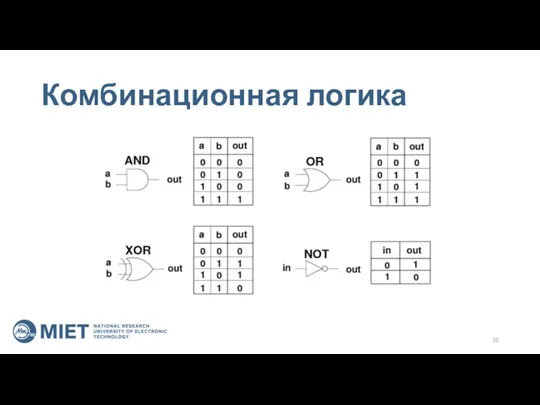

- 9. Комбинационная логика

- 10. Комбинационная логика

- 11. Verilog HDL module endmodule

- 12. Verilog HDL module top endmodule top

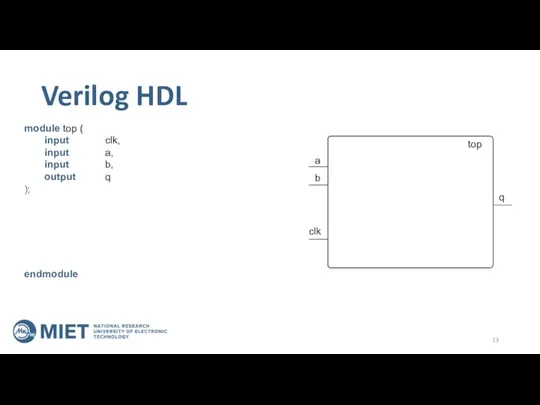

- 13. Verilog HDL module top ( input clk, input a, input b, output q ); endmodule top

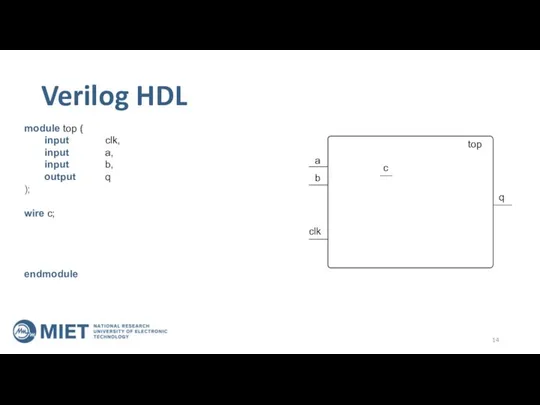

- 14. Verilog HDL top a b clk q module top ( input clk, input a, input b,

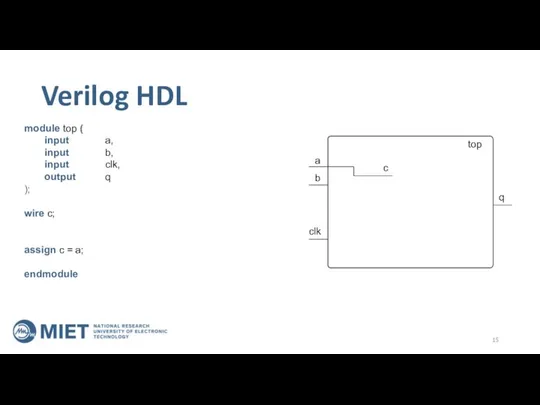

- 15. Verilog HDL top a b clk q module top ( input a, input b, input clk,

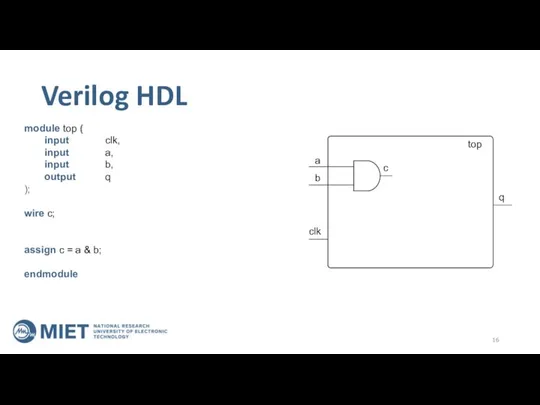

- 16. Verilog HDL module top ( input clk, input a, input b, output q ); wire c;

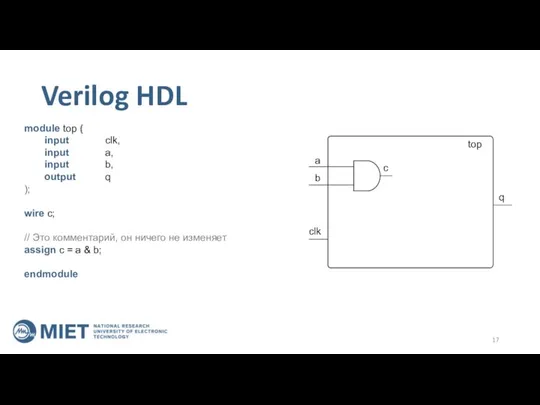

- 17. Verilog HDL module top ( input clk, input a, input b, output q ); wire c;

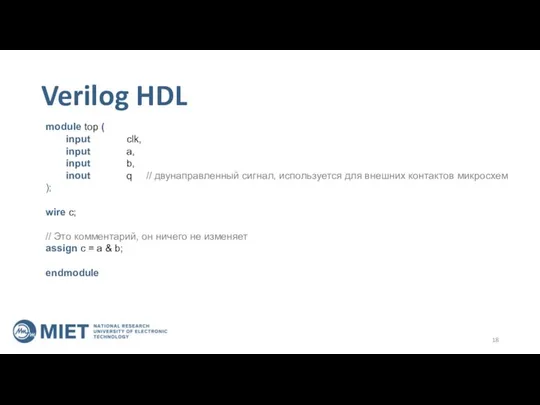

- 18. Verilog HDL module top ( input clk, input a, input b, inout q // двунаправленный сигнал,

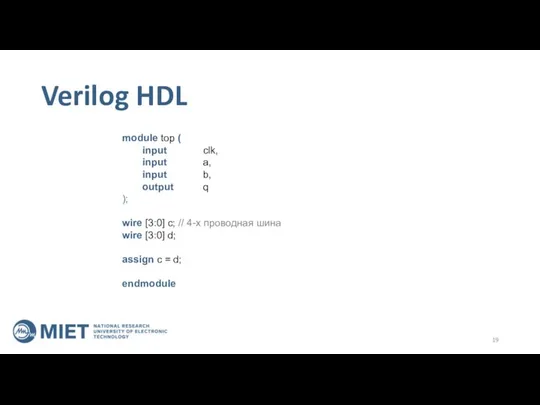

- 19. Verilog HDL module top ( input clk, input a, input b, output q ); wire [3:0]

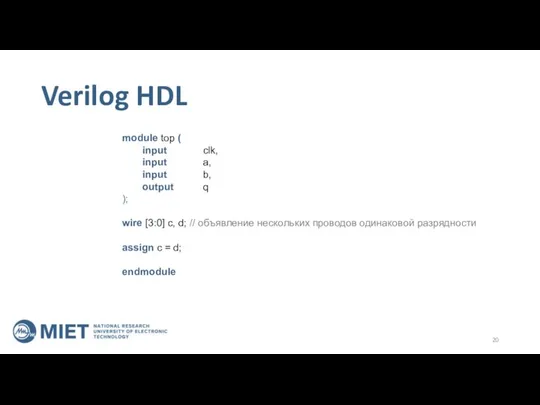

- 20. Verilog HDL module top ( input clk, input a, input b, output q ); wire [3:0]

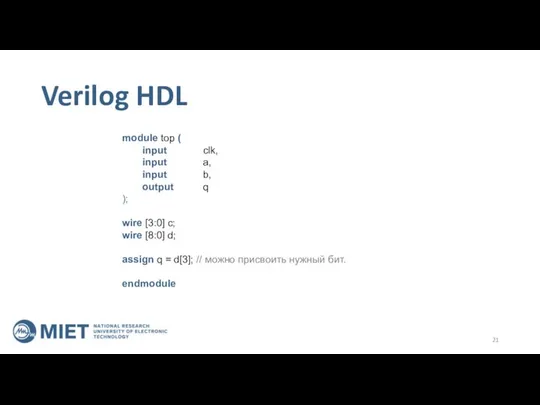

- 21. Verilog HDL module top ( input clk, input a, input b, output q ); wire [3:0]

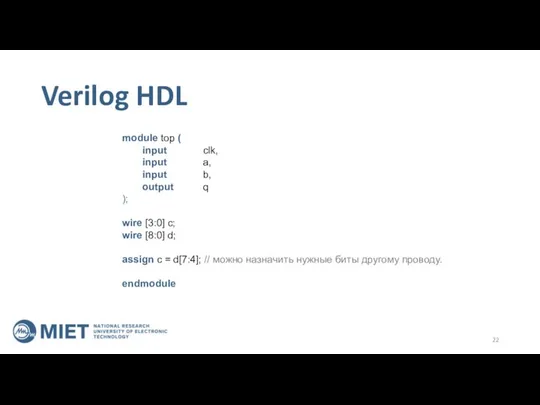

- 22. Verilog HDL module top ( input clk, input a, input b, output q ); wire [3:0]

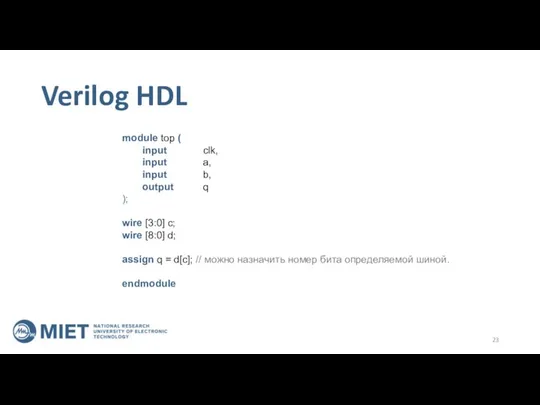

- 23. Verilog HDL module top ( input clk, input a, input b, output q ); wire [3:0]

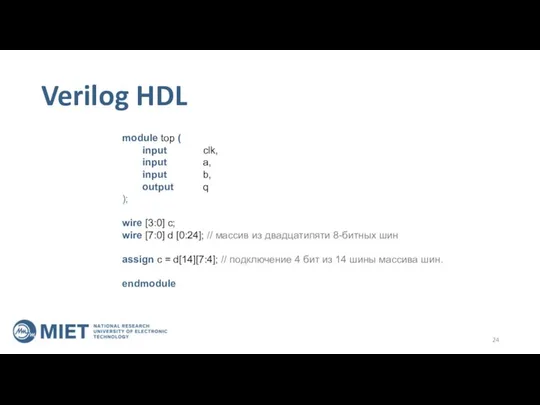

- 24. Verilog HDL module top ( input clk, input a, input b, output q ); wire [3:0]

- 25. Verilog HDL module top ( input clk, input [8:0] a, // входные и выходные порты модуля

- 26. Формат описания чисел Verilog HDL wire [10:0] a = 7; //32-х битное десятичное число, которое будет

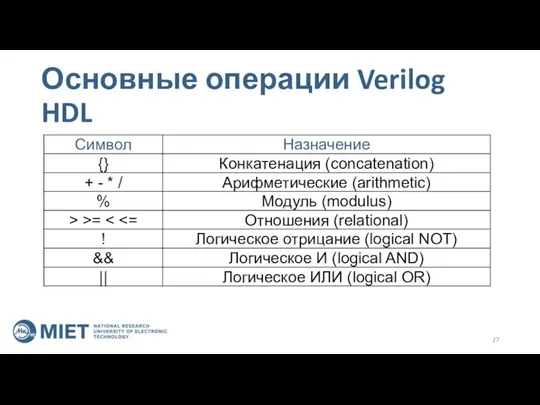

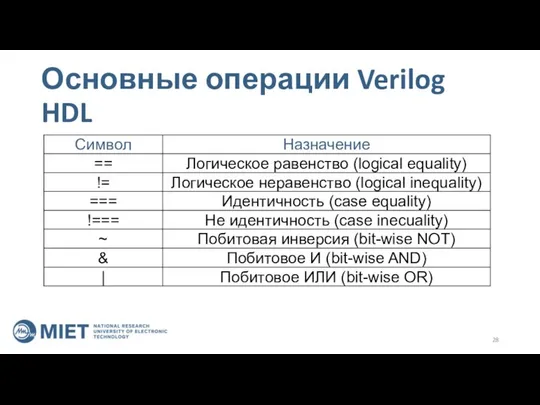

- 27. Основные операции Verilog HDL

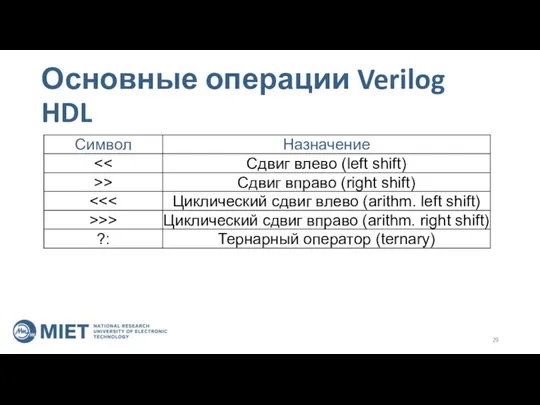

- 28. Основные операции Verilog HDL

- 29. Основные операции Verilog HDL

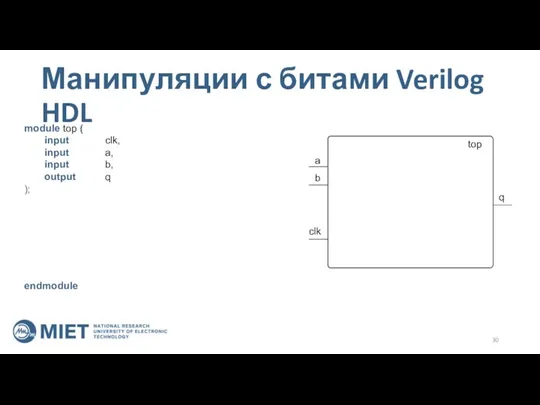

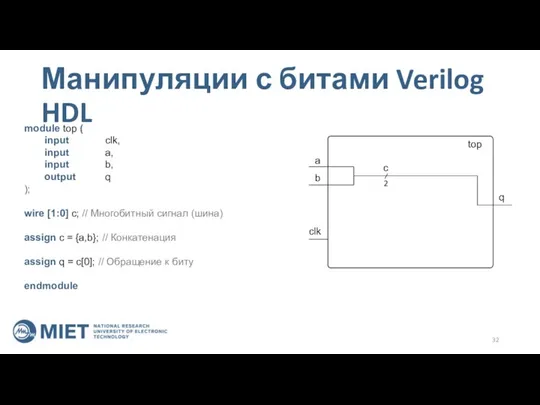

- 30. Манипуляции с битами Verilog HDL module top ( input clk, input a, input b, output q

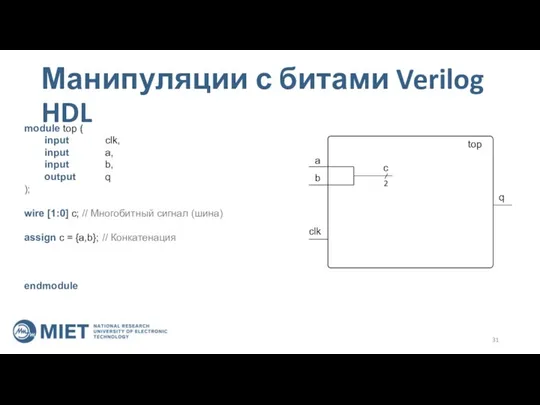

- 31. Манипуляции с битами Verilog HDL top a b clk q module top ( input clk, input

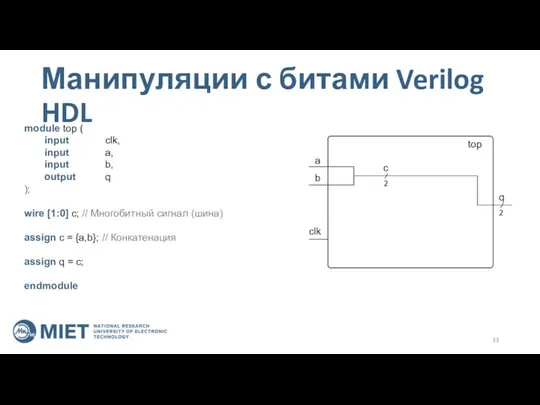

- 32. Манипуляции с битами Verilog HDL top a b clk q module top ( input clk, input

- 33. Манипуляции с битами Verilog HDL top a b clk q module top ( input clk, input

- 34. Verilog HDL. Сложение и вычитание module simple_add_sub ( input [7:0] operandA, operandB //два входных 8-ми битных

- 35. Verilog HDL. Логические и арифметические сдвиги module simple_add_sub ( input [7:0] operandA, operandB //два входных 8-ми

- 36. Verilog HDL. Битовые логические операции module simple_add_sub ( input [7:0] operandA, operandB //два входных 8-ми битных

- 37. Verilog HDL. Булевые логические операции module simple_add_sub ( input [7:0] operandA, operandB //два входных 8-ми битных

- 38. Verilog HDL. Операции свертки module simple_add_sub ( input [7:0] operandA, output out_reduction_and, out_reduction_or, out_redution_xor ); //Операции

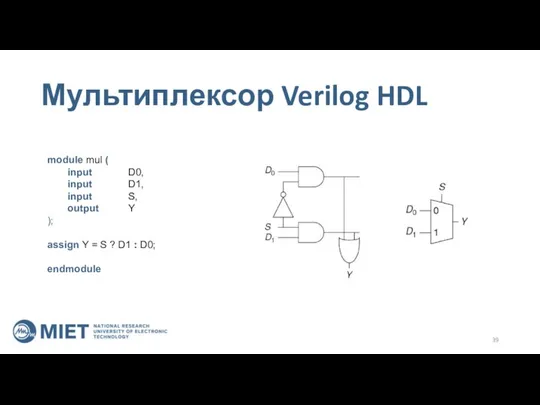

- 39. Мультиплексор Verilog HDL module mul ( input D0, input D1, input S, output Y ); assign

- 40. Verilog HDL. Операции сравнения module simple_add_sub ( input [7:0] operandA, operandB output out_eq, out_ne, out_gt, out_lt,

- 41. Verilog HDL. Тип reg module top ( input clk, input [8:0] a, input b, output [3:0]

- 42. Verilog HDL. Тип reg module top ( input clk, input [8:0] a, input b, output reg

- 43. Verilog HDL. Блок always module top ( input clk, input [8:0] a, input b, output reg

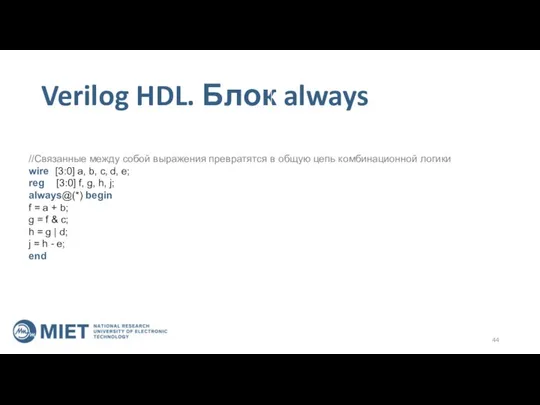

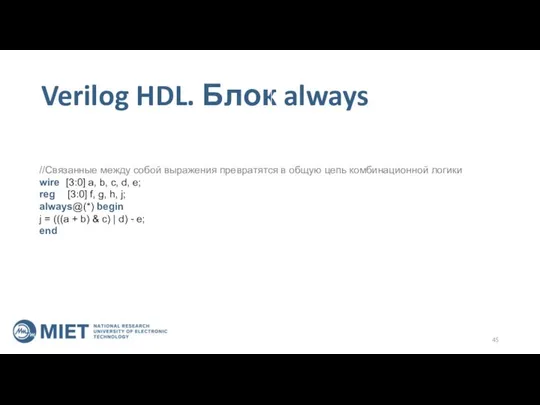

- 44. Verilog HDL. Блок always //Связанные между собой выражения превратятся в общую цепь комбинационной логики wire [3:0]

- 45. Verilog HDL. Блок always //Связанные между собой выражения превратятся в общую цепь комбинационной логики wire [3:0]

- 46. Verilog HDL. If-else //можно описывать мультиплексоры с помощью if-else а не тернарного оператора reg [3:0] c;

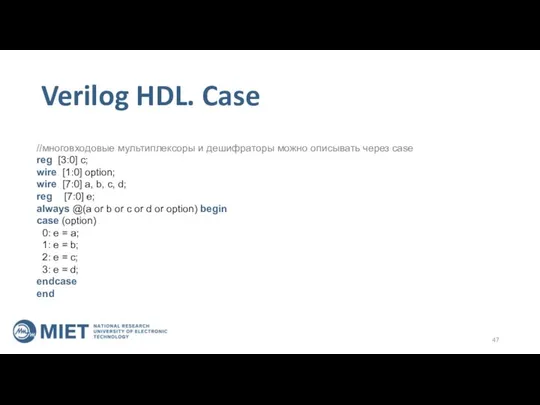

- 47. Verilog HDL. Case //многовходовые мультиплексоры и дешифраторы можно описывать через case reg [3:0] c; wire [1:0]

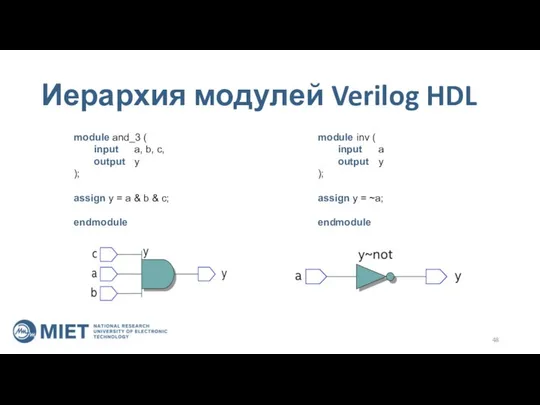

- 48. Иерархия модулей Verilog HDL module inv ( input a output y ); assign y = ~a;

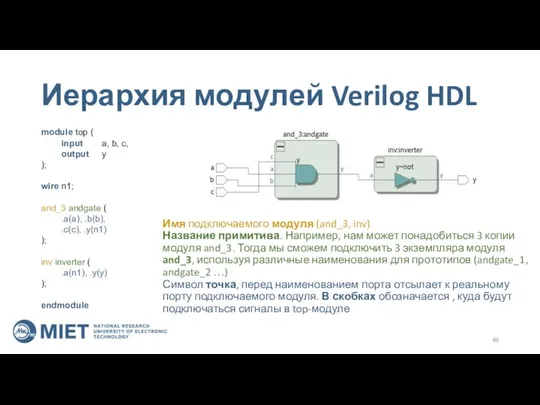

- 49. Иерархия модулей Verilog HDL module top ( input a, b, c, output y ); wire n1;

- 50. Упражнение с логическими элементами Altera Cyclone IV EP4CE6 FPGA Вывод результатов логических операций над входными воздействиями

- 51. Упражнение с логическими элементами module top ( … input [3:0] key_sw, output [3:0] led, … );

- 52. Упражнение с логическими элементами Присвойте led[2] результат операции И (AND). Присвойте led[3] результат операции исключающего ИЛИ

- 53. Упражнение с логическими элементами

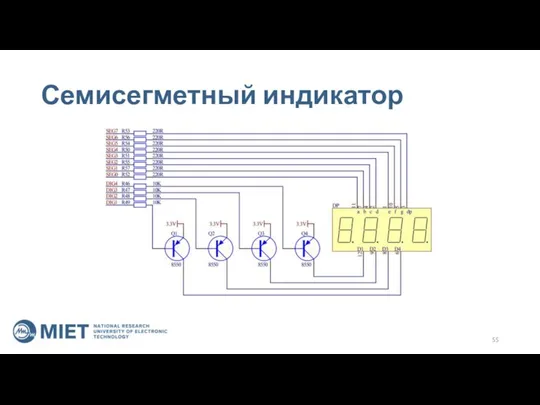

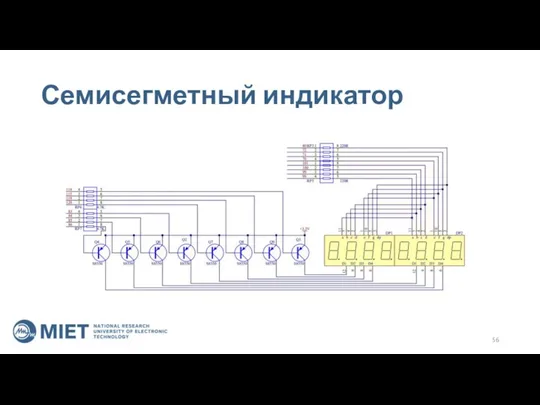

- 54. Семисегметный индикатор

- 55. Семисегметный индикатор

- 56. Семисегметный индикатор

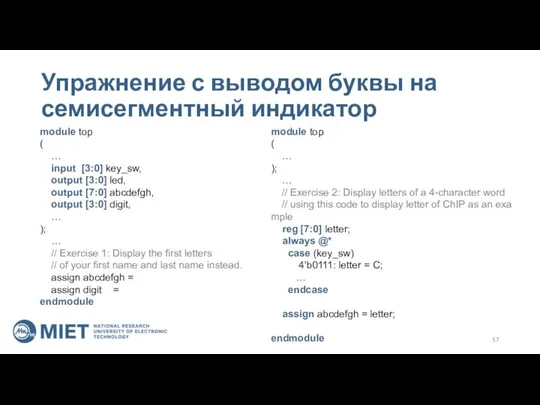

- 57. Упражнение с выводом буквы на семисегментный индикатор module top ( … input [3:0] key_sw, output [3:0]

- 58. Упражнение с выводом буквы на семисегментный индикатор Выведите первые буквы своего имени и фамилии на семисегментный

- 59. Упражнение с выводом буквы на семисегментный индикатор

- 61. Скачать презентацию

![Verilog HDL module top ( input clk, input [8:0] a, //](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-24.jpg)

![Формат описания чисел Verilog HDL wire [10:0] a = 7; //32-х](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-25.jpg)

![Verilog HDL. Сложение и вычитание module simple_add_sub ( input [7:0] operandA,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-33.jpg)

![Verilog HDL. Логические и арифметические сдвиги module simple_add_sub ( input [7:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-34.jpg)

![Verilog HDL. Битовые логические операции module simple_add_sub ( input [7:0] operandA,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-35.jpg)

![Verilog HDL. Булевые логические операции module simple_add_sub ( input [7:0] operandA,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-36.jpg)

![Verilog HDL. Операции свертки module simple_add_sub ( input [7:0] operandA, output](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-37.jpg)

![Verilog HDL. Операции сравнения module simple_add_sub ( input [7:0] operandA, operandB](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-39.jpg)

![Verilog HDL. Тип reg module top ( input clk, input [8:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-40.jpg)

![Verilog HDL. Тип reg module top ( input clk, input [8:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-41.jpg)

![Verilog HDL. Блок always module top ( input clk, input [8:0]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-42.jpg)

![Упражнение с логическими элементами module top ( … input [3:0] key_sw,](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-50.jpg)

![Упражнение с логическими элементами Присвойте led[2] результат операции И (AND). Присвойте](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/731687/slide-51.jpg)

Общая справка о компании Movavi

Общая справка о компании Movavi Дистанційне навчання

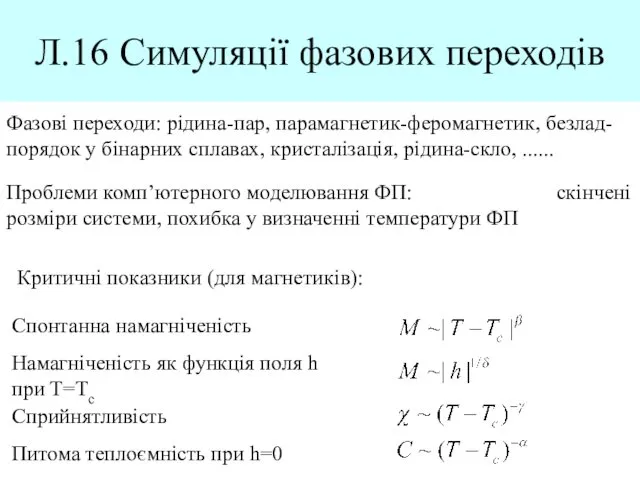

Дистанційне навчання Симуляції фазових переходів

Симуляції фазових переходів Герцель Любовь Николаевна- учитель информатики, математики. Герцель Любовь Николаевна- учитель информатики, математики. Зато

Герцель Любовь Николаевна- учитель информатики, математики. Герцель Любовь Николаевна- учитель информатики, математики. Зато Ваш личный кинотеатр Landing.ua

Ваш личный кинотеатр Landing.ua My Eyes On You. Игра

My Eyes On You. Игра Базовые типы данных и ввод-вывод. Лабораторная работа №1

Базовые типы данных и ввод-вывод. Лабораторная работа №1 Урок информатика

Урок информатика Аппаратное и программное обеспечение ЭВМ и сетей

Аппаратное и программное обеспечение ЭВМ и сетей Застосування бази даних магазину «Меблі»

Застосування бази даних магазину «Меблі» Сайт Ремонт компьютеров

Сайт Ремонт компьютеров Достижения в компьютерной технике

Достижения в компьютерной технике Операции и вычисления арифметических выражений в MS EXCEL (Тема 5)

Операции и вычисления арифметических выражений в MS EXCEL (Тема 5) Государственная (итоговая) аттестация по информатике и ИКТ. (9 класс)

Государственная (итоговая) аттестация по информатике и ИКТ. (9 класс) Word 2007. Спецкурс

Word 2007. Спецкурс Компьютерные модели различных процессов

Компьютерные модели различных процессов Начало и окончание операционного дня оператора связи

Начало и окончание операционного дня оператора связи Технология обработки звуковой информации (часть 1)

Технология обработки звуковой информации (часть 1) Программирование в компьютерных сетях

Программирование в компьютерных сетях Аттестационная работа. Разработка факультативного курса на тему Программирование на языке высокого уровня Python

Аттестационная работа. Разработка факультативного курса на тему Программирование на языке высокого уровня Python Графические и табличные информационные модели 8 класс

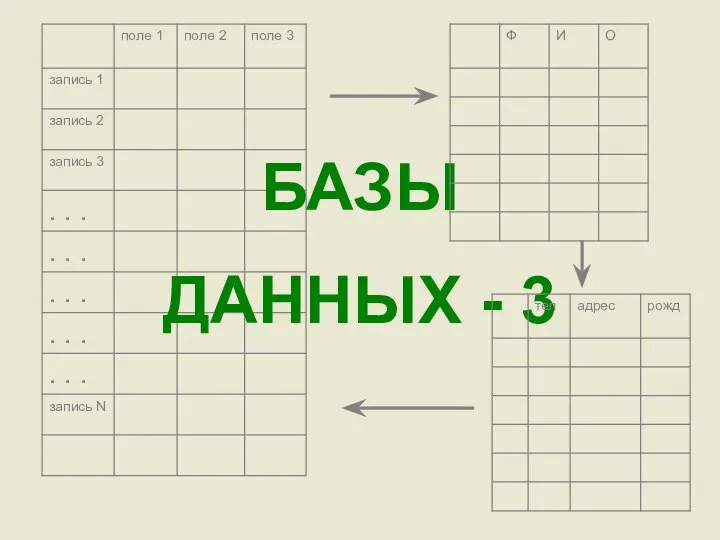

Графические и табличные информационные модели 8 класс Базы данных-3

Базы данных-3 пн

пн СrossFaer

СrossFaer Тема 7. Синхронизация и взаимодействие процессов и потоков

Тема 7. Синхронизация и взаимодействие процессов и потоков Основные части вычислительной системы

Основные части вычислительной системы Памятка по проверке документов из Росреестра

Памятка по проверке документов из Росреестра Основы HTML. Разработка Web-сайта

Основы HTML. Разработка Web-сайта