Содержание

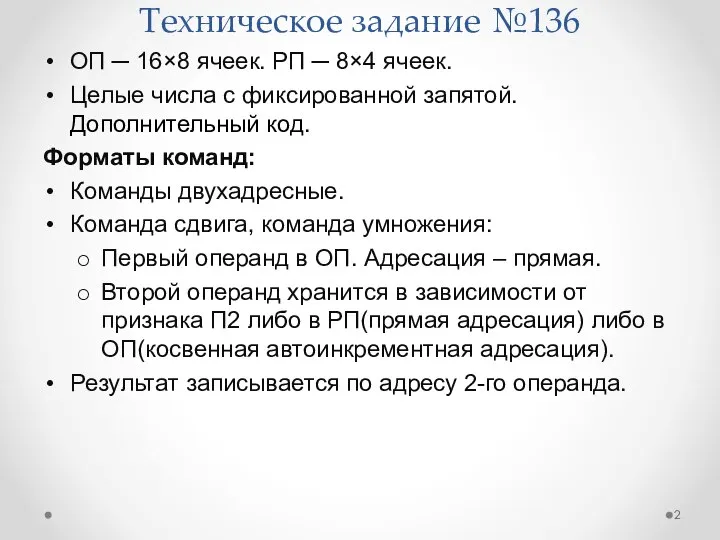

- 2. Техническое задание №136 ОП ─ 16×8 ячеек. РП ─ 8×4 ячеек. Целые числа с фиксированной запятой.

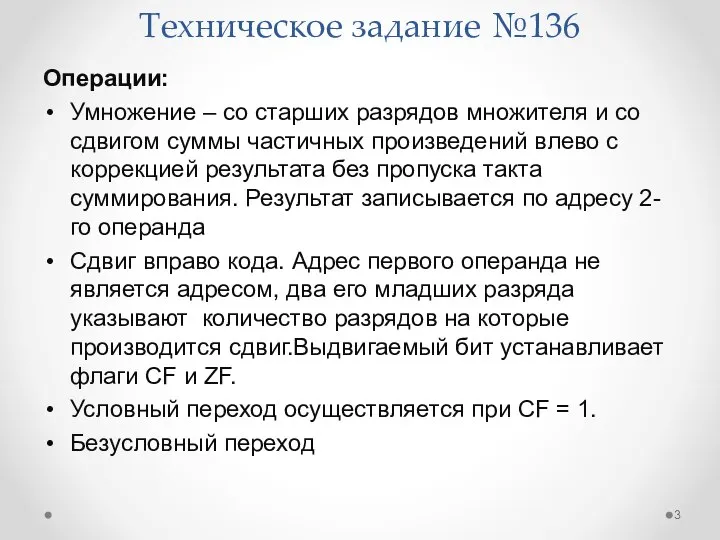

- 3. Техническое задание №136 Операции: Умножение – со старших разрядов множителя и со сдвигом суммы частичных произведений

- 4. Способы адресации и форматы команд Умножение/Сдвиг Условный переход/Безусловный переход

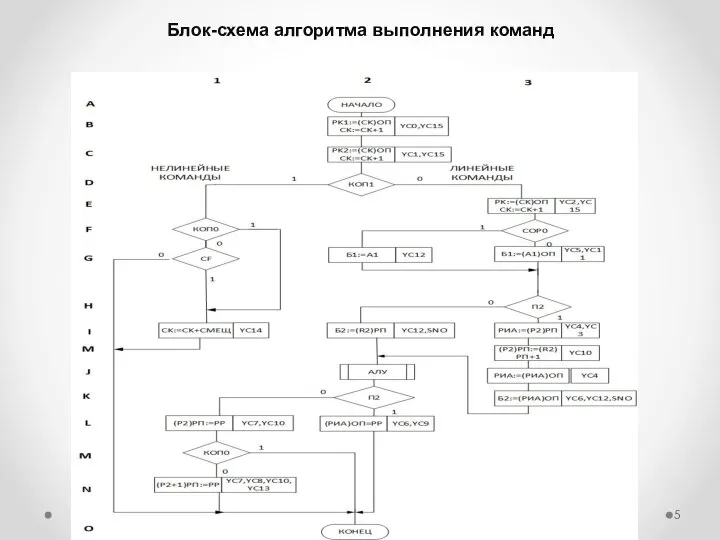

- 5. Блок-схема алгоритма выполнения команд

- 6. Функциональная схема блока управления командами

- 7. Функциональная схема блока операций

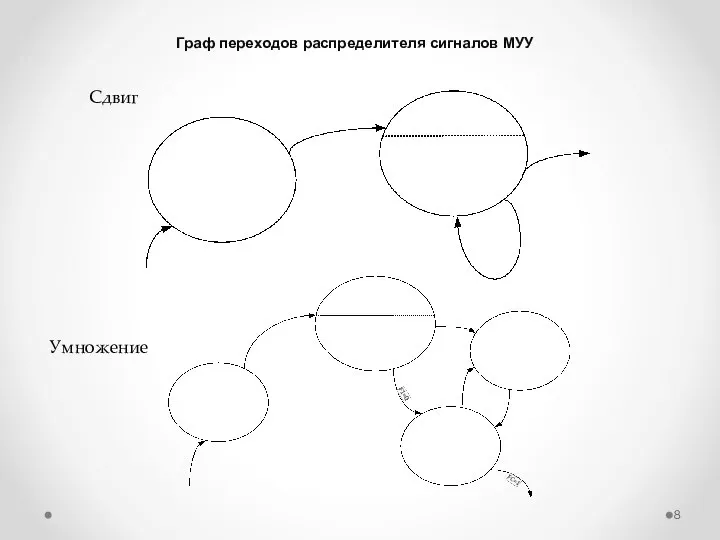

- 8. Граф переходов распределителя сигналов МУУ Сдвиг Умножение

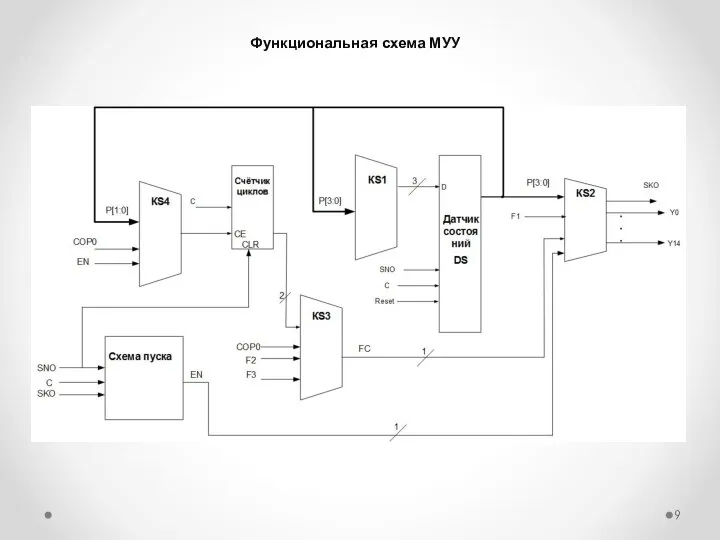

- 9. Функциональная схема МУУ

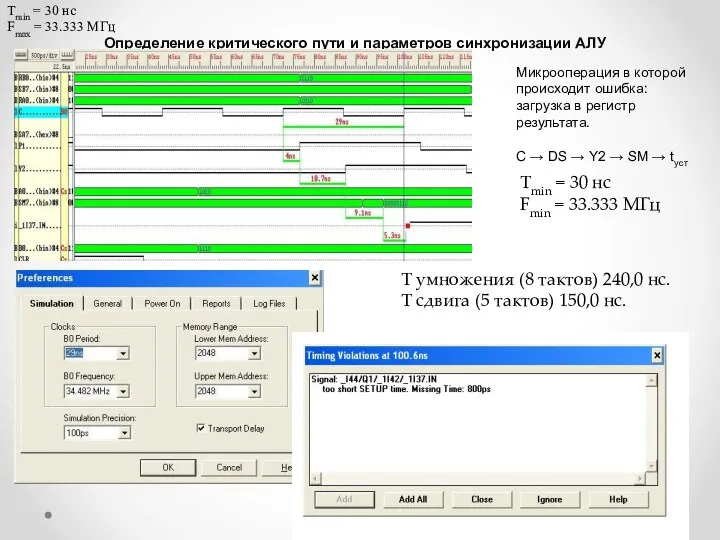

- 10. Определение критического пути и параметров синхронизации АЛУ Микрооперация в которой происходит ошибка: загрузка в регистр результата.

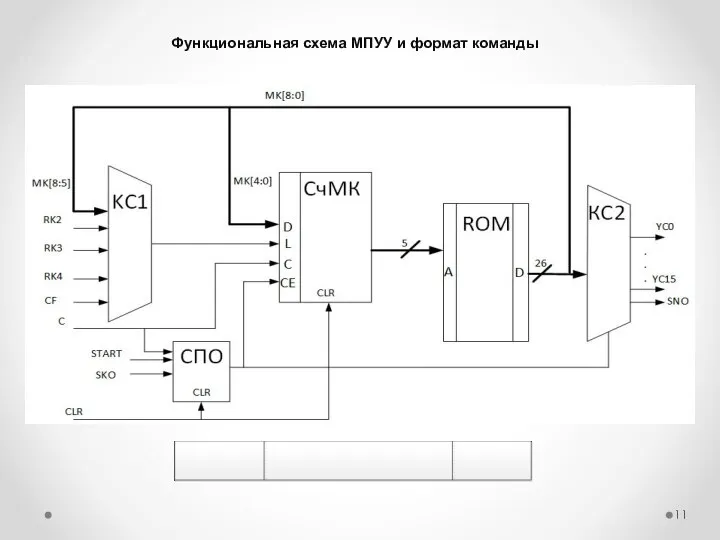

- 11. Функциональная схема МПУУ и формат команды

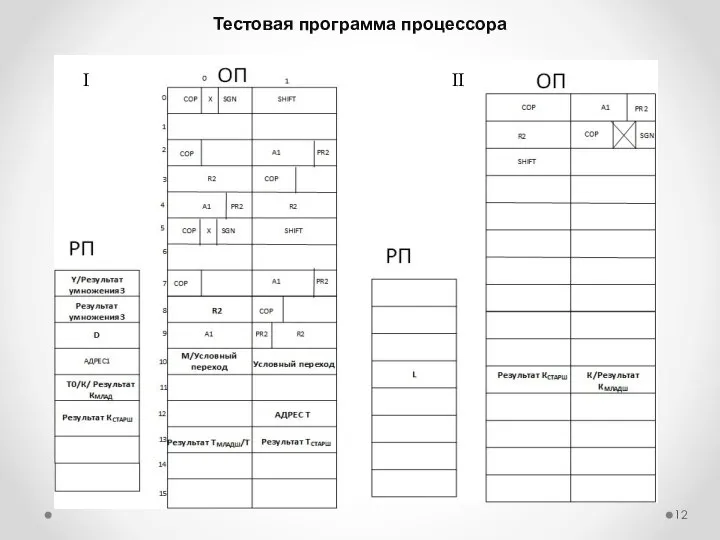

- 12. Тестовая программа процессора I II

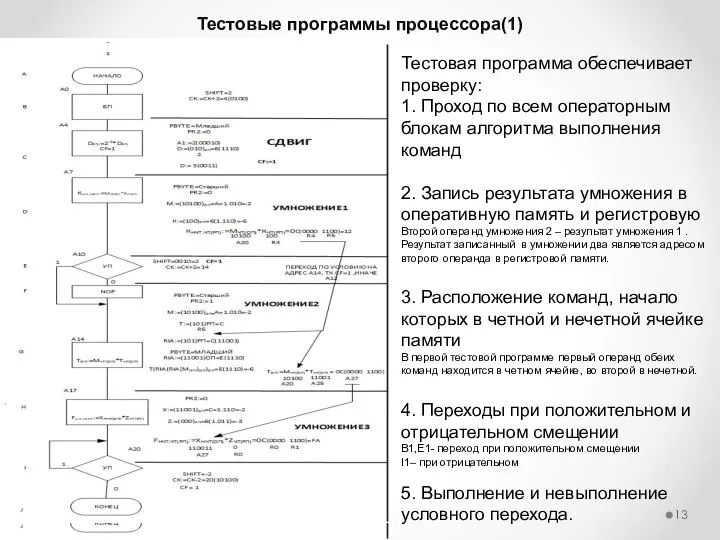

- 13. Тестовые программы процессора(1) Тестовая программа обеспечивает проверку: 1. Проход по всем операторным блокам алгоритма выполнения команд

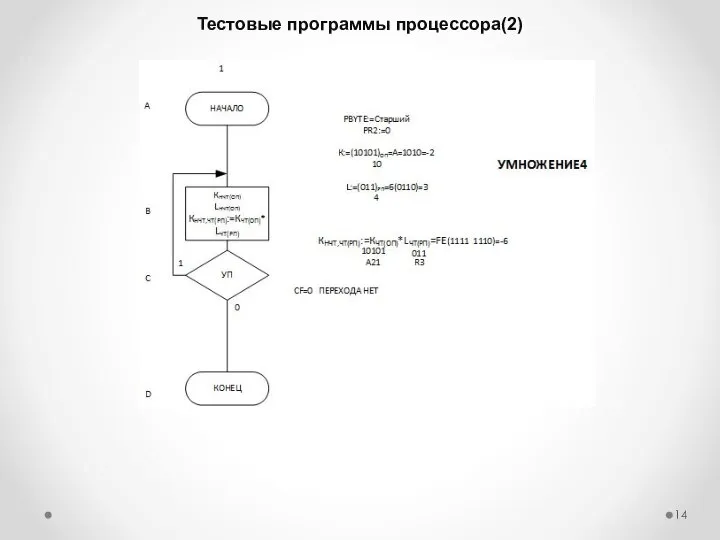

- 14. Тестовые программы процессора(2)

- 16. Скачать презентацию

Создание интерактивных тренажёров для учащихся начальных классов

Создание интерактивных тренажёров для учащихся начальных классов Команды AutoCAD Выдавить, Вращать, Лофт, Сдвиг

Команды AutoCAD Выдавить, Вращать, Лофт, Сдвиг Подпрограммы в Паскаль

Подпрограммы в Паскаль Некоторые алгоритмы для массивов. Методы сортировки. Операции над матрицами

Некоторые алгоритмы для массивов. Методы сортировки. Операции над матрицами Презентация по информатике Палитры цветов в системах цветопередачи RGB, CMYK и HSB

Презентация по информатике Палитры цветов в системах цветопередачи RGB, CMYK и HSB  Презентация "Сканер" - скачать презентации по Информатике

Презентация "Сканер" - скачать презентации по Информатике Информационные ресурсы и базы данных для написания магистерской диссертации

Информационные ресурсы и базы данных для написания магистерской диссертации Аспектно - ориентированное программирование

Аспектно - ориентированное программирование Обзор методов оптимизации

Обзор методов оптимизации Инструкция по обновлению навигационного ПО

Инструкция по обновлению навигационного ПО Основы классификации сетей. Локальные и глобальные сети. Элементы Интернет

Основы классификации сетей. Локальные и глобальные сети. Элементы Интернет Современные мультимедиатехнологии в связях с общественностью. Базовые понятия

Современные мультимедиатехнологии в связях с общественностью. Базовые понятия Создание интерактивных тестов в программе MyTestX

Создание интерактивных тестов в программе MyTestX Программирование под API web-сервисов

Программирование под API web-сервисов Математические основы информатики

Математические основы информатики Киберпреступность

Киберпреступность Проектирование и внедрение инфраструктуры лесов и доменов Active Directory Domain Services

Проектирование и внедрение инфраструктуры лесов и доменов Active Directory Domain Services Требования. Основные понятия

Требования. Основные понятия Морской бой. Конкурс интерактивных презентаций Интерактивная мозаика-2017

Морской бой. Конкурс интерактивных презентаций Интерактивная мозаика-2017 Алгоритмы и способы их описания

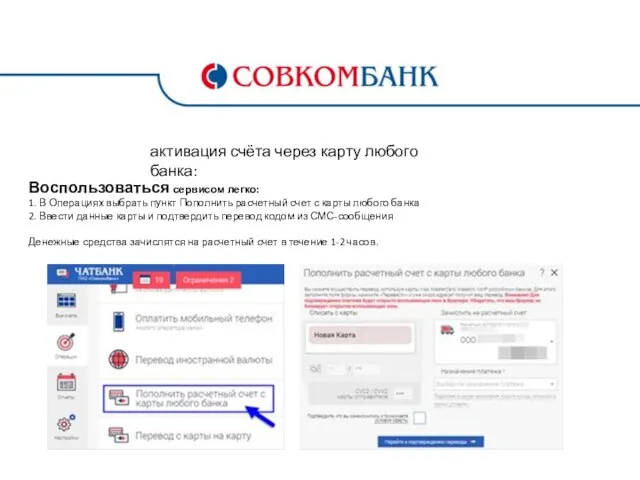

Алгоритмы и способы их описания Активация счета через карту любого банка

Активация счета через карту любого банка Локальные вычислительные сети и их виды. Локальные вычислительные сети и их виды. Основные требования, предъявляемые к локал

Локальные вычислительные сети и их виды. Локальные вычислительные сети и их виды. Основные требования, предъявляемые к локал Учимся с Марусей

Учимся с Марусей Презентация "Положительное и отрицательное влияние сети Интернет" - скачать презентации по Информатике

Презентация "Положительное и отрицательное влияние сети Интернет" - скачать презентации по Информатике Защита Инстаграм аккаунта

Защита Инстаграм аккаунта Презентация "Система счисления" - скачать презентации по Информатике

Презентация "Система счисления" - скачать презентации по Информатике Человек и компьютер Подготовила: Тихомирова Т.Е. 2009 год

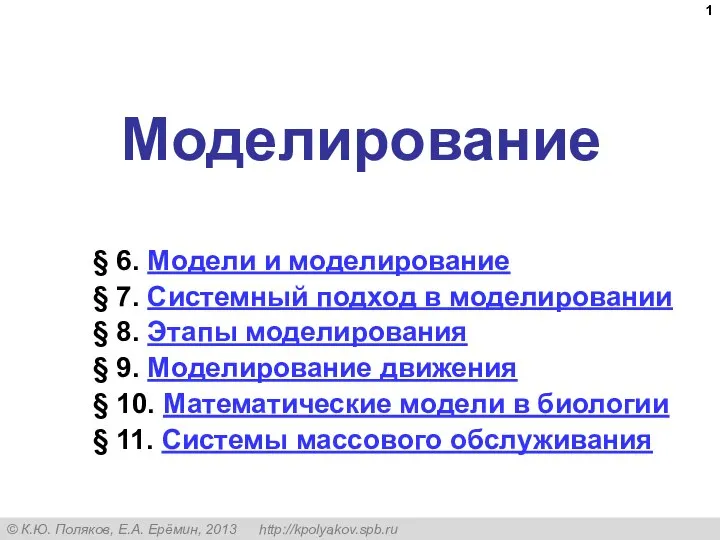

Человек и компьютер Подготовила: Тихомирова Т.Е. 2009 год 11-2_Modelirovanie

11-2_Modelirovanie