Содержание

- 2. Универсальный синхронный/асинхронный приемо-передатчик Все без исключения микроконтроллеры семейства Mega имеют в своем составе от одного до

- 3. Модули USART в микроконтроллерах семейства Mega

- 4. Модули USART в микроконтроллерах семейства Mega Модули USART, реализованные в микроконтроллерах семейства, могут обнаруживать следующие внештатные

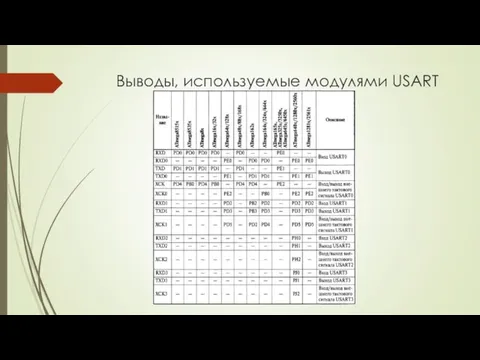

- 5. Выводы, используемые модулями USART

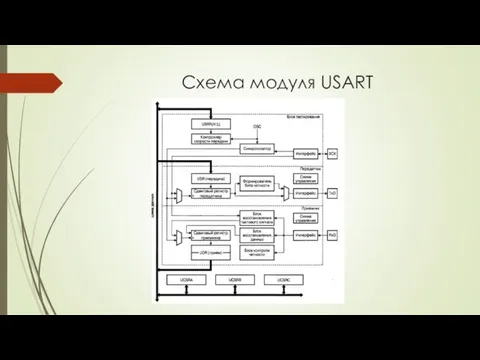

- 6. Схема модуля USART

- 7. Размещение регистров данных модулей USART

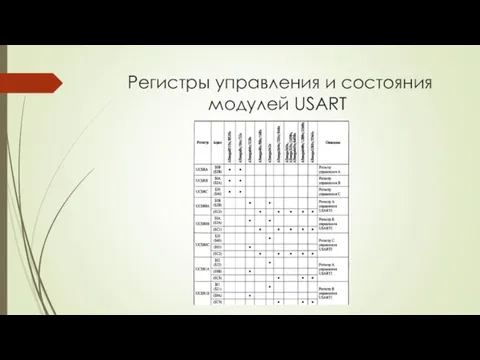

- 8. Регистры управления и состояния модулей USART

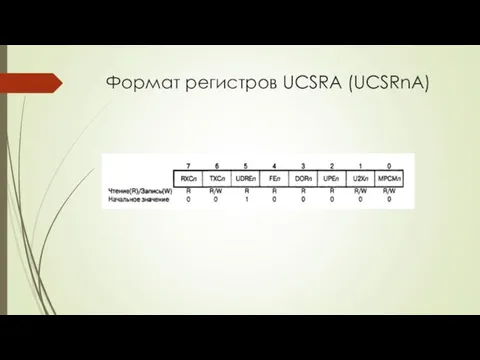

- 9. Формат регистров UCSRA (UCSRnA)

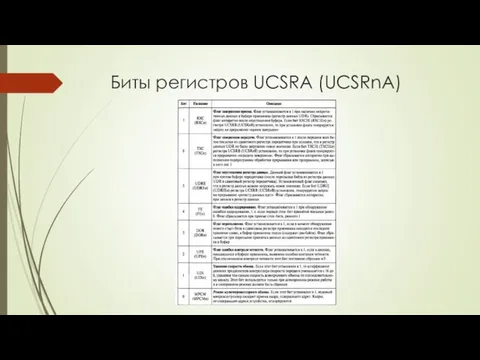

- 10. Биты регистров UCSRA (UCSRnA)

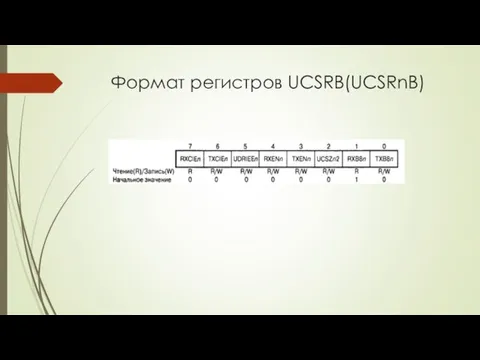

- 11. Формат регистров UCSRB(UCSRnB)

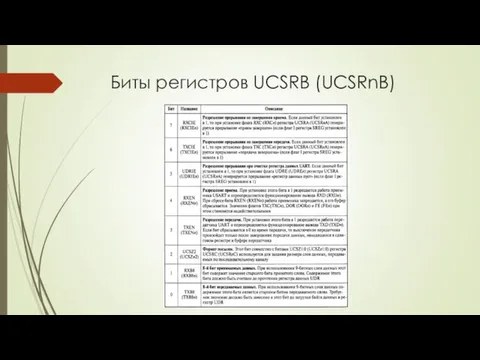

- 12. Биты регистров UCSRB (UCSRnB)

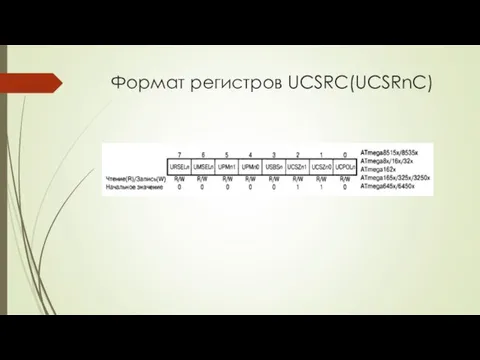

- 13. Формат регистров UCSRC(UCSRnC)

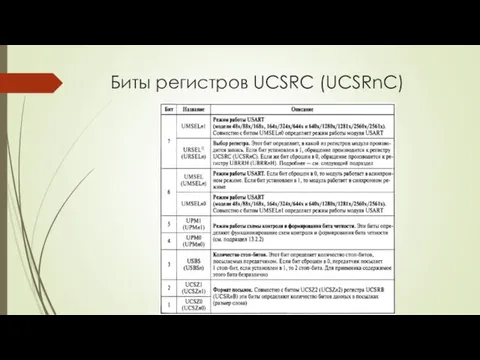

- 14. Биты регистров UCSRC (UCSRnC)

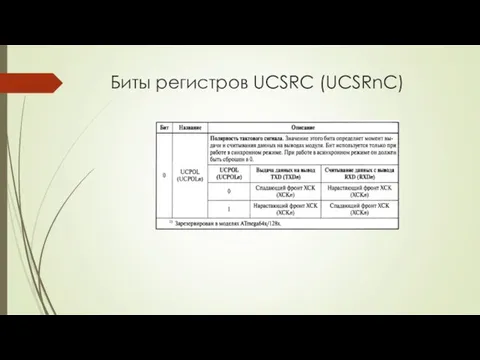

- 15. Биты регистров UCSRC (UCSRnC)

- 16. Скорость приема/передачи В асинхронном режиме, а также в синхронном режиме при работе в качестве ведущего скорость

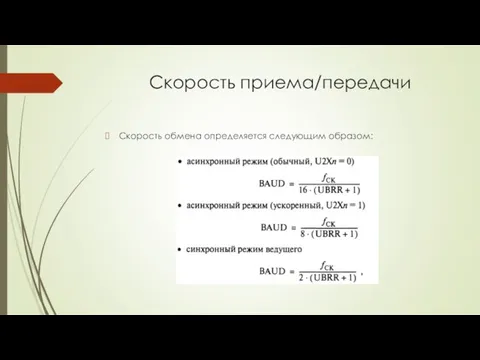

- 17. Скорость приема/передачи Скорость обмена определяется следующим образом:

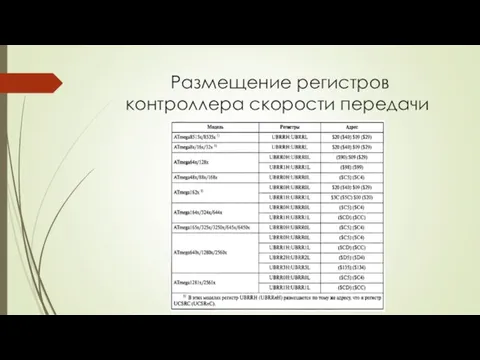

- 18. Размещение регистров контроллера скорости передачи

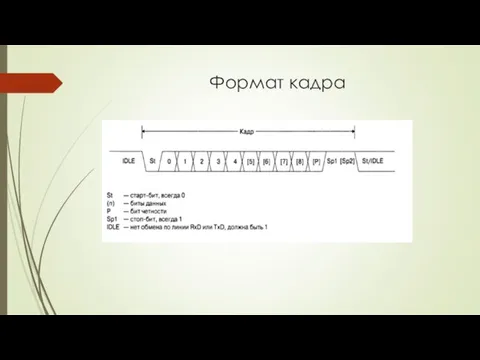

- 19. Формат кадра Под кадром в данном случае понимается совокупность одного слова данных и сопутствующей информации Кадр

- 20. Формат кадра

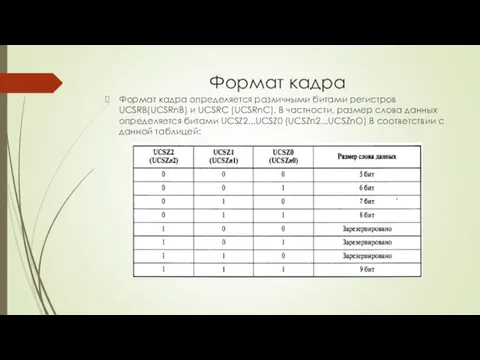

- 21. Формат кадра Формат кадра определяется различными битами регистров UCSRB(UCSRnB) и UCSRC (UCSRnC). В частности, размер слова

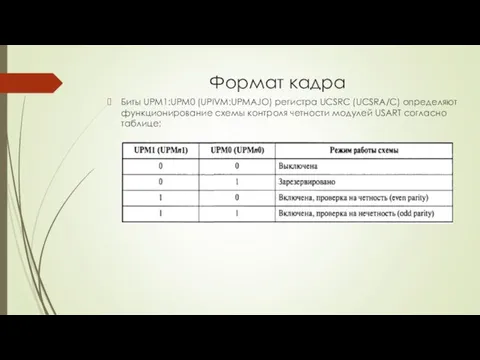

- 22. Формат кадра Биты UPM1:UPM0 (UPIVM:UPMAJO) регистра UCSRC (UCSRA/C) определяют функционирование схемы контроля четности модулей USART согласно

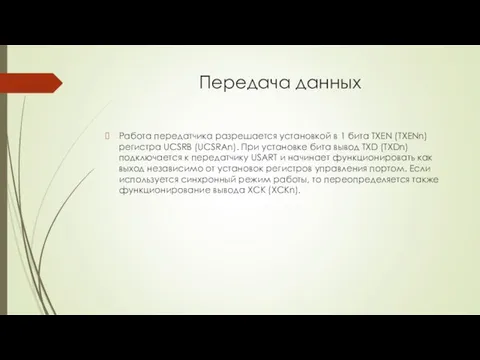

- 23. Передача данных Работа передатчика разрешается установкой в 1 бита TXEN (TXENn)регистра UCSRB (UCSRAn). При установке бита

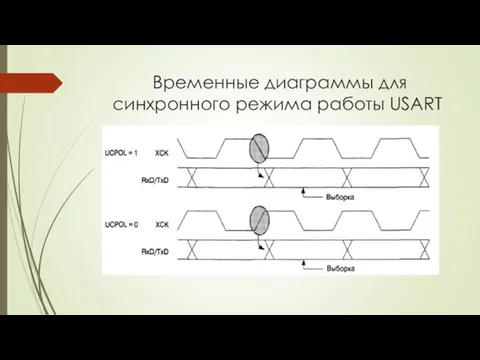

- 24. Временные диаграммы для синхронного режима работы USART

- 26. Скачать презентацию

ВКР: Офисный центр в г. Воронеж

ВКР: Офисный центр в г. Воронеж Азарова

Азарова Государственная поддержка малых форм хозяйствования в агропромышленном комплексе

Государственная поддержка малых форм хозяйствования в агропромышленном комплексе Теория железобетона

Теория железобетона Инженер строитель Такие разные здания

Инженер строитель Такие разные здания Prilagatelnye_v_zagadkakh

Prilagatelnye_v_zagadkakh Жюль Верн

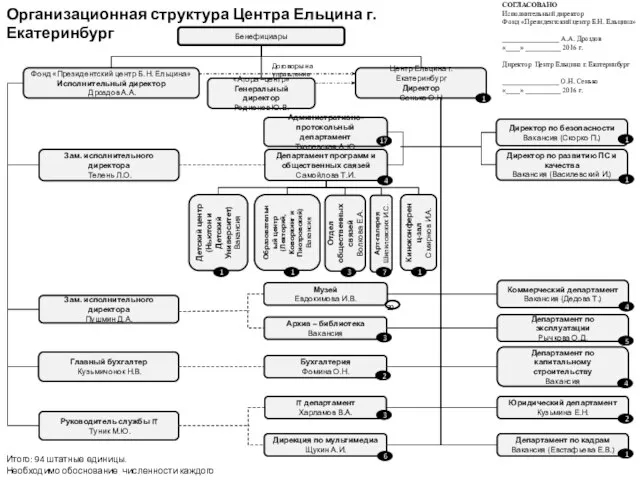

Жюль Верн Организационная структура центра Б.Н. Ельцина г. Екатеринбург

Организационная структура центра Б.Н. Ельцина г. Екатеринбург Троицын день

Троицын день 20180109_orlovskaya_oblast-80_let

20180109_orlovskaya_oblast-80_let 20180925_prilozhenie_no1

20180925_prilozhenie_no1 Тепловые МУН. Лекция 8

Тепловые МУН. Лекция 8 Презентация

Презентация 20150126_medved

20150126_medved Приспособленность

Приспособленность Ресурсосберегающая технология сбора, подготовки и закачивания пластовой воды в нефтегазовой промышленности

Ресурсосберегающая технология сбора, подготовки и закачивания пластовой воды в нефтегазовой промышленности Абай.pptx

Абай.pptx Types of accommodation

Types of accommodation Распределение денежных средств

Распределение денежных средств Конструктивные элементы судна и их назначение

Конструктивные элементы судна и их назначение Адаптация математической модели последовательного каскада

Адаптация математической модели последовательного каскада Технология штукатурных работ. Часть 1

Технология штукатурных работ. Часть 1 Умный дом

Умный дом Секреты дружного класса. Настольная книга классного руководителя

Секреты дружного класса. Настольная книга классного руководителя Откровение Правды Божией в Рим 1,16-17

Откровение Правды Божией в Рим 1,16-17 Больше, меньше. Сравнение чисел

Больше, меньше. Сравнение чисел sentyabrya_2011_g

sentyabrya_2011_g Cадоводство. Растения, распространённые в Крыму

Cадоводство. Растения, распространённые в Крыму