Содержание

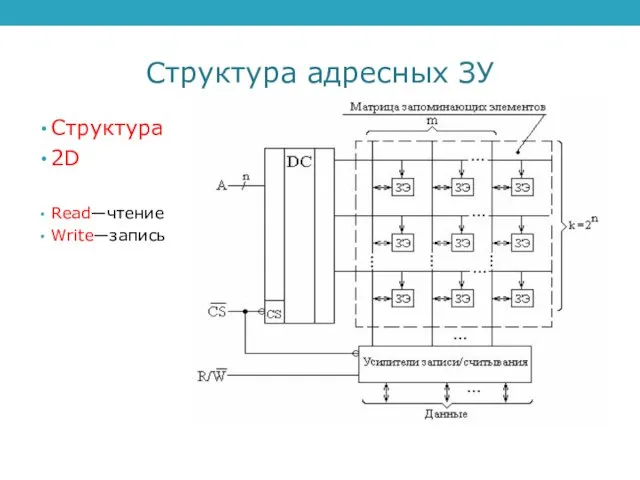

- 2. Структура адресных ЗУ Структура 2D Read—чтение Write—запись

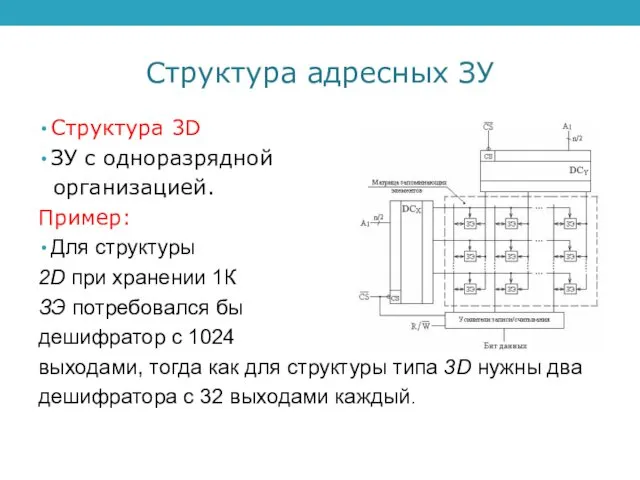

- 3. Структура адресных ЗУ Структура 3D ЗУ с одноразрядной организацией. Пример: Для структуры 2D при хранении 1К

- 4. Структура адресных ЗУ Структура 3D

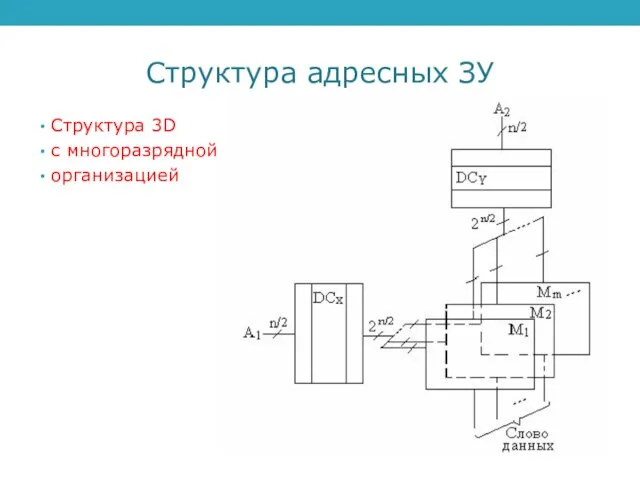

- 5. Структура адресных ЗУ Структура 3D с многоразрядной организацией

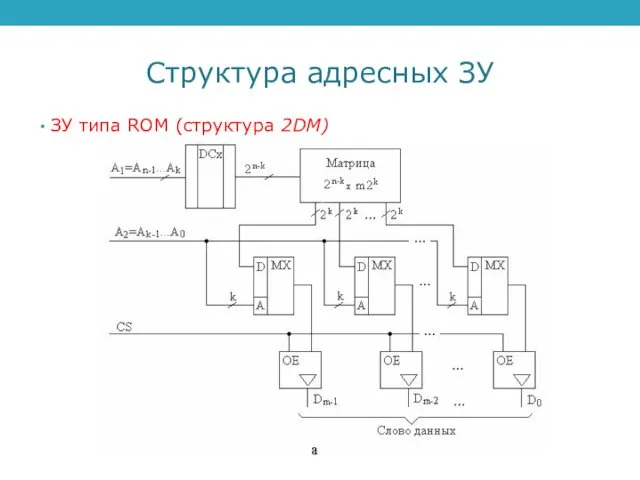

- 6. Структура адресных ЗУ ЗУ типа ROM (структура 2DM)

- 7. Структура адресных ЗУ ЗУ типа RАM (структура 2DM)

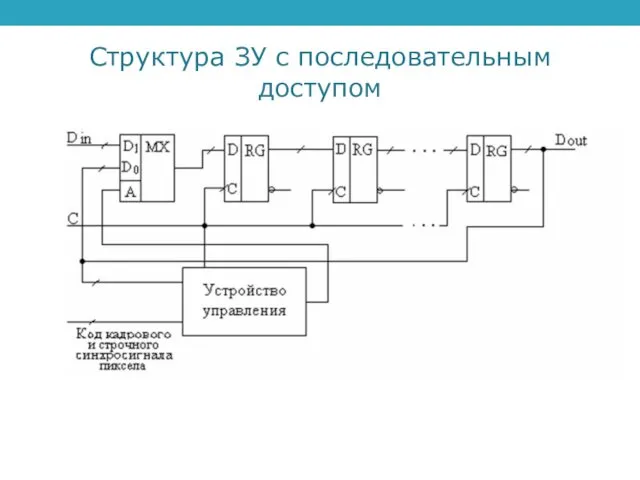

- 8. Структура ЗУ с последовательным доступом

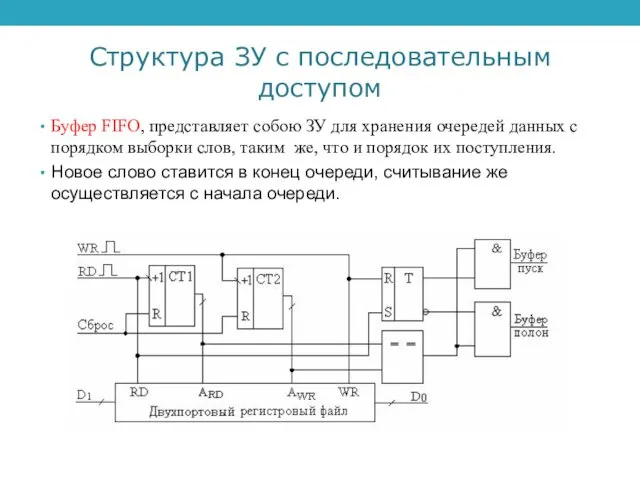

- 9. Структура ЗУ с последовательным доступом Буфер FIFO, представляет собою ЗУ для хранения очередей данных с порядком

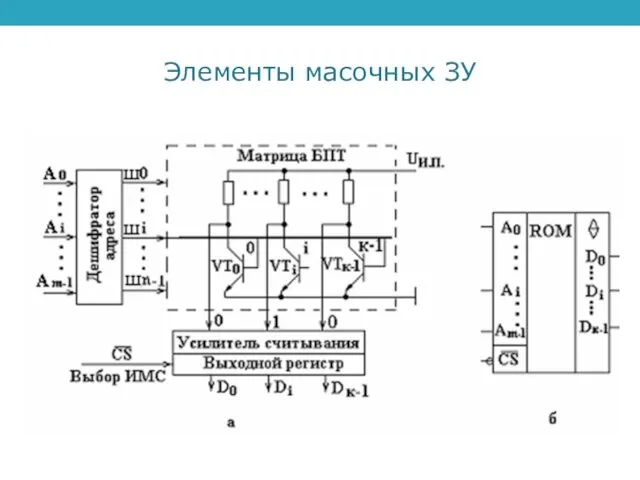

- 10. Элементы масочных ЗУ

- 11. Элементы масочных ЗУ Матрицы ПЗУМ на МОП-транзисторах

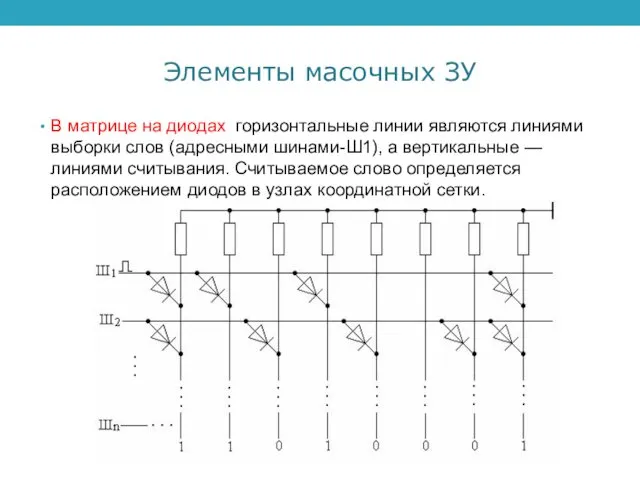

- 12. Элементы масочных ЗУ В матрице на диодах горизонтальные линии являются линиями выборки слов (адресными шинами-Ш1), а

- 13. Элементы программируемых ПЗУ ППЗУ на основе многоэмиттерных транзисторов

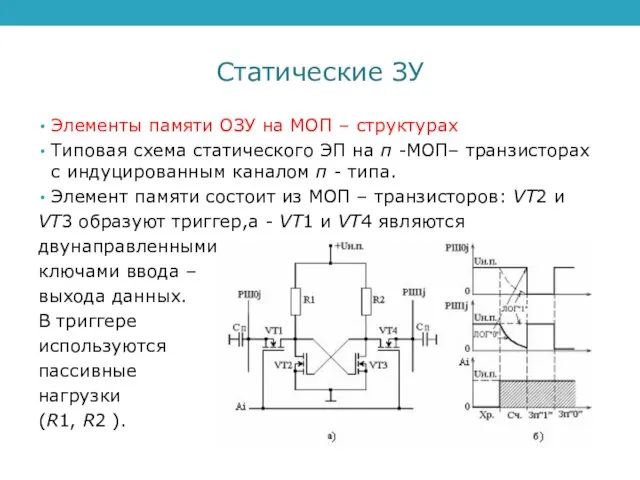

- 14. Статические ЗУ Элементы памяти ОЗУ на МОП – структурах Типовая схема статического ЭП на п -МОП–

- 15. Статические ЗУ Принципиальная схема запоминающего элемента статического ОЗУ, выполненного по КМОП технологии. (Вместо резисторов в БИС

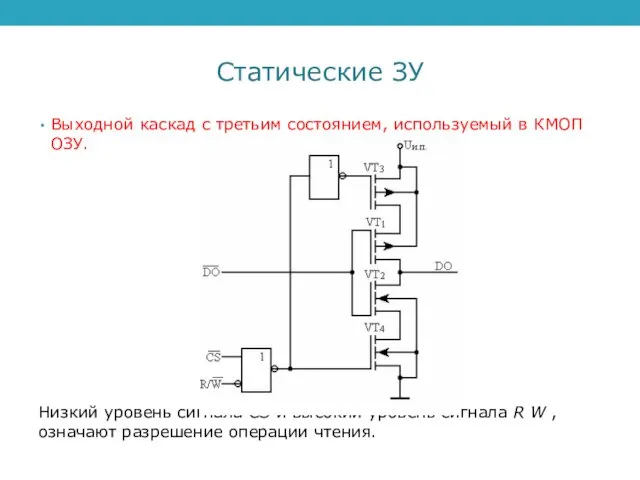

- 16. Статические ЗУ Выходной каскад с третьим состоянием, используемый в КМОП ОЗУ. Низкий уровень сигнала CS и

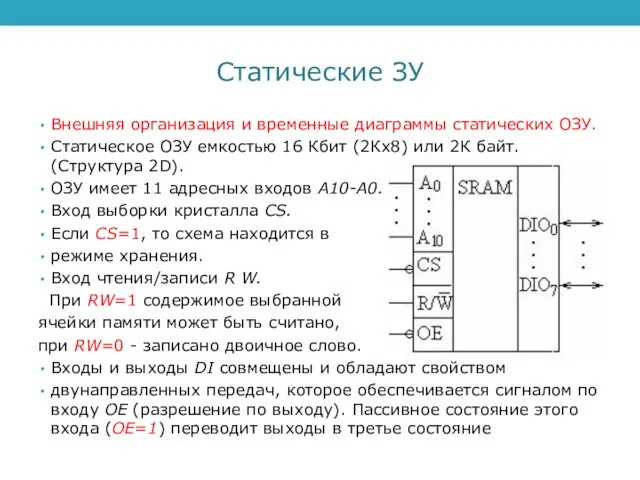

- 17. Статические ЗУ Внешняя организация и временные диаграммы статических ОЗУ. Статическое ОЗУ емкостью 16 Кбит (2Кх8) или

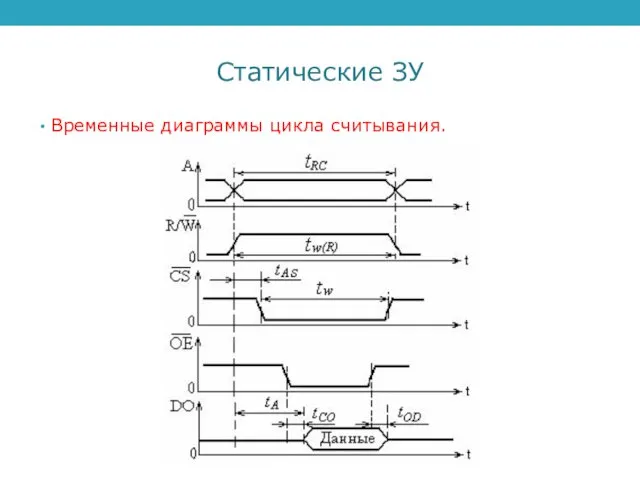

- 18. Статические ЗУ Временные диаграммы цикла считывания.

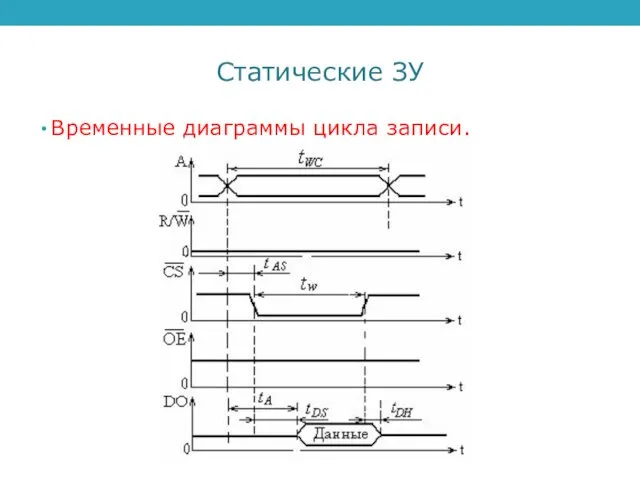

- 19. Статические ЗУ Временные диаграммы цикла записи.

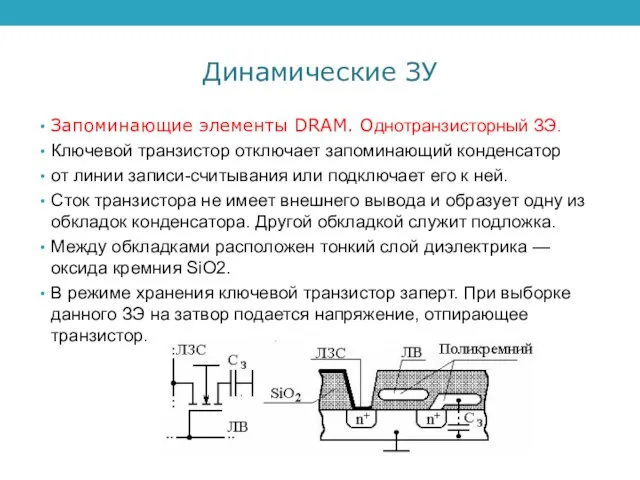

- 20. Динамические ЗУ Запоминающие элементы DRAM. Однотранзисторный ЗЭ. Ключевой транзистор отключает запоминающий конденсатор от линии записи-считывания или

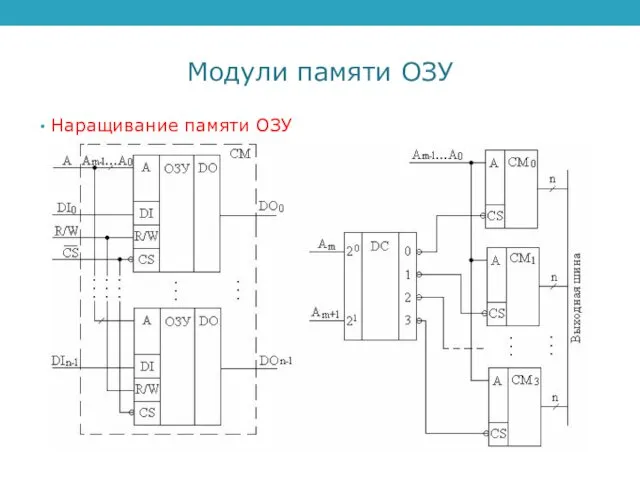

- 21. Модули памяти ОЗУ Наращивание памяти ОЗУ

- 23. Скачать презентацию

Особенности применения САПР для решения задач проектирования электронной аппаратуры

Особенности применения САПР для решения задач проектирования электронной аппаратуры Автоматизированное рабочее место (АРМ)

Автоматизированное рабочее место (АРМ) Деревянные дома

Деревянные дома Порядок действий по закреплению подвижного состава на железнодорожном транспорте в случае усиления ветра

Порядок действий по закреплению подвижного состава на железнодорожном транспорте в случае усиления ветра Новые ФСО 2022

Новые ФСО 2022 20160705_gorkiy_m._pesnya_o_sokole

20160705_gorkiy_m._pesnya_o_sokole Аттестационаая работа. Программа внеурочной деятельности Я-исследователь

Аттестационаая работа. Программа внеурочной деятельности Я-исследователь 20131125_sotrudnichestvo_kl.rukovodit._so_shkolnym_bibliotekarem

20131125_sotrudnichestvo_kl.rukovodit._so_shkolnym_bibliotekarem Гормональное расписание организма

Гормональное расписание организма Droga Krzyżowa

Droga Krzyżowa Углеродные наноматериалы в наноэлектронике. Часть 1

Углеродные наноматериалы в наноэлектронике. Часть 1 шаблон

шаблон Мои увлечения

Мои увлечения Обеспечение жильем детей-сирот

Обеспечение жильем детей-сирот Ремонт ювелирных изделий

Ремонт ювелирных изделий Последовательное и параллельное соединение проводников

Последовательное и параллельное соединение проводников Nasibullin_VKR_10_06

Nasibullin_VKR_10_06 Оснастка для изготовления композитов

Оснастка для изготовления композитов От резца до лазера. Технологические процессы обработки материалов

От резца до лазера. Технологические процессы обработки материалов Особое производство

Особое производство Look Back

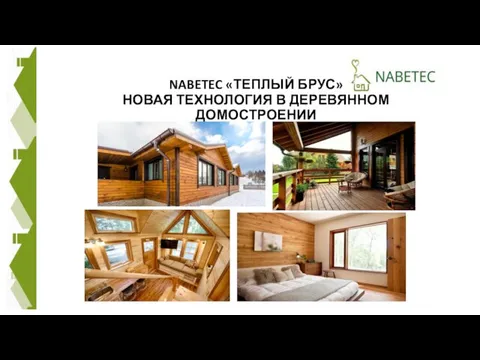

Look Back Nabetec теплый брус. Новая технология в деревянном домостроении

Nabetec теплый брус. Новая технология в деревянном домостроении Студенческий сенат

Студенческий сенат ВУДУ

ВУДУ Содержание автомобильных дорог: санация трещин; ямочный ремонт; нормативные документы в содержании а/д общего пользования

Содержание автомобильных дорог: санация трещин; ямочный ремонт; нормативные документы в содержании а/д общего пользования TEKhNOLOGIYa_ORNAMENT_V_POLOSE

TEKhNOLOGIYa_ORNAMENT_V_POLOSE Графические модели

Графические модели Программа Летний Интенсив

Программа Летний Интенсив