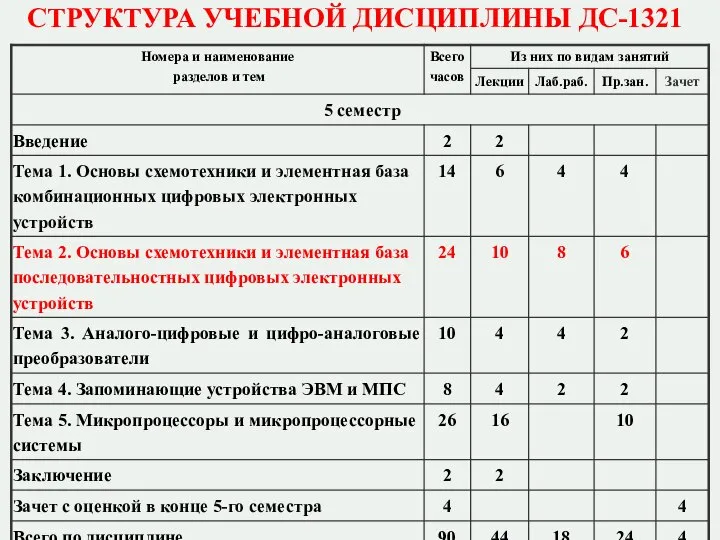

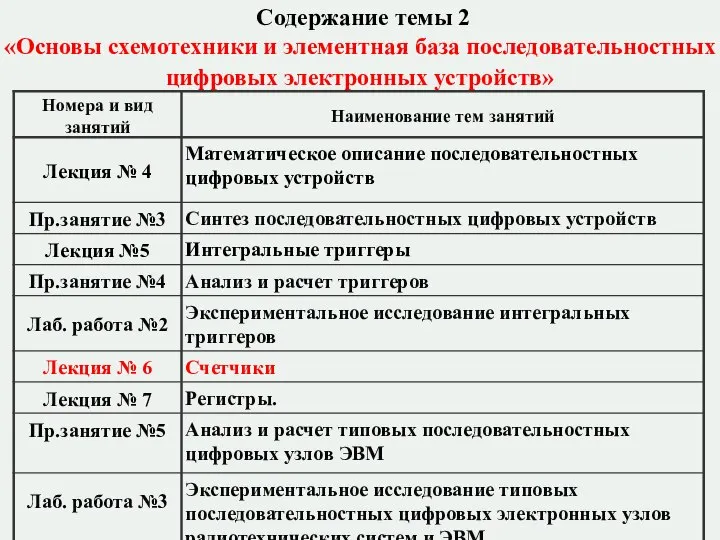

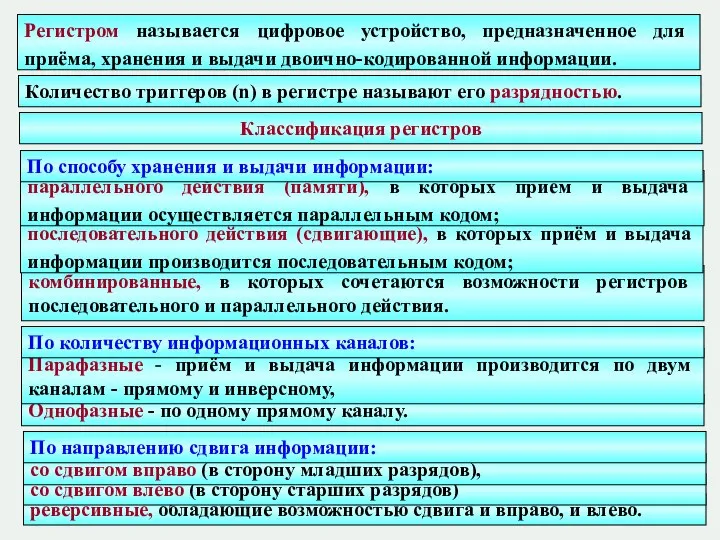

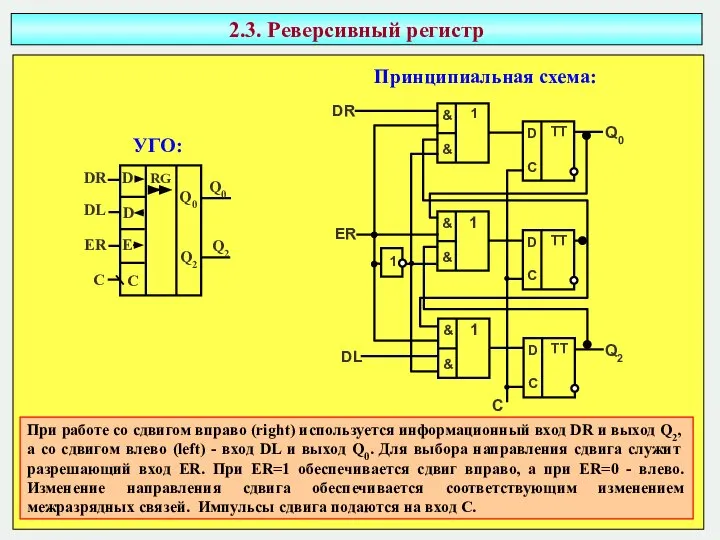

реверсивные, обладающие возможностью сдвига и вправо, и влево.

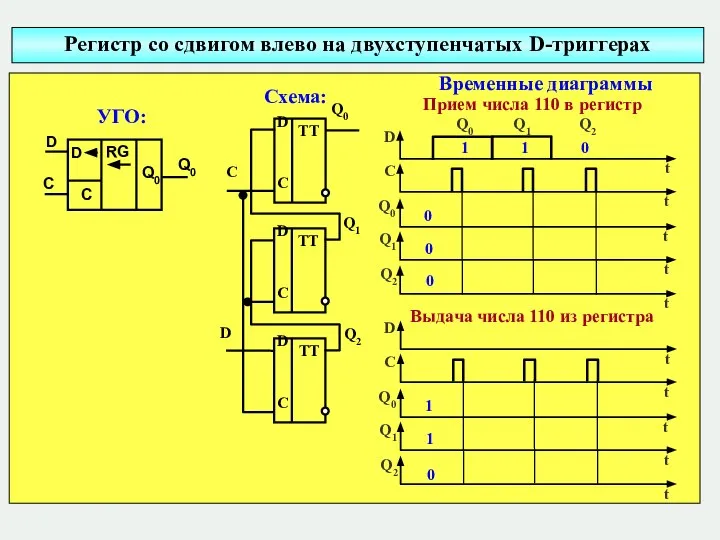

со сдвигом влево

(в сторону старших разрядов)

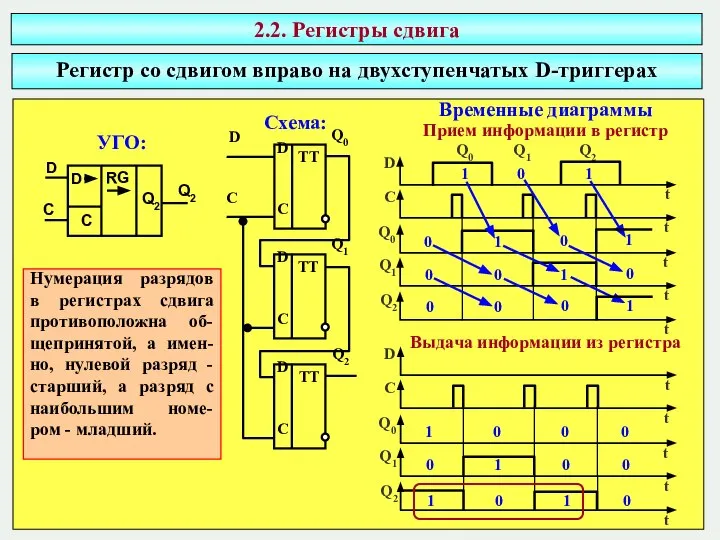

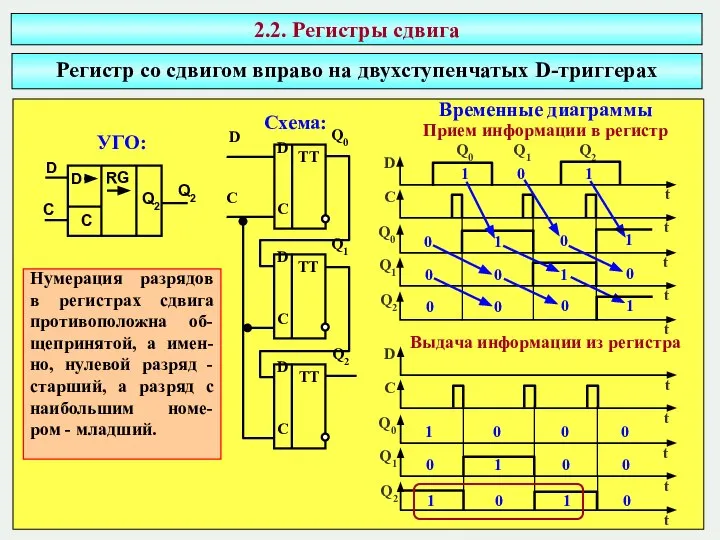

со сдвигом вправо (в сторону младших разрядов),

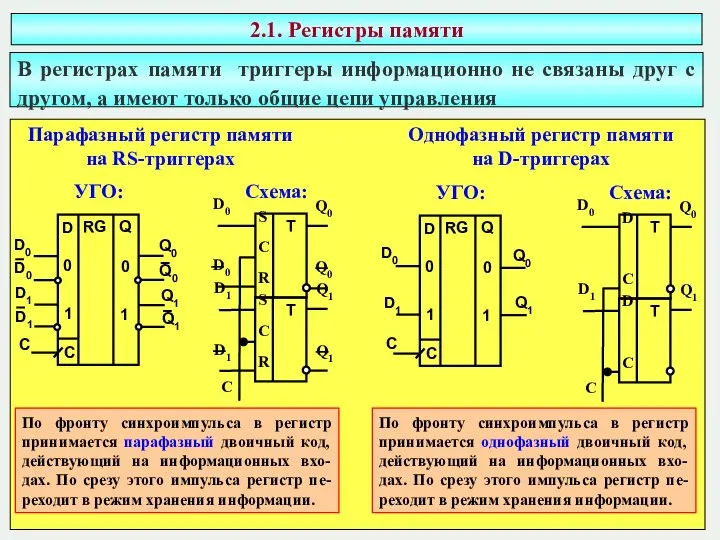

Однофазные - по одному прямому каналу.

Парафазные - приём и выдача информации производится по двум каналам - прямому и инверсному,

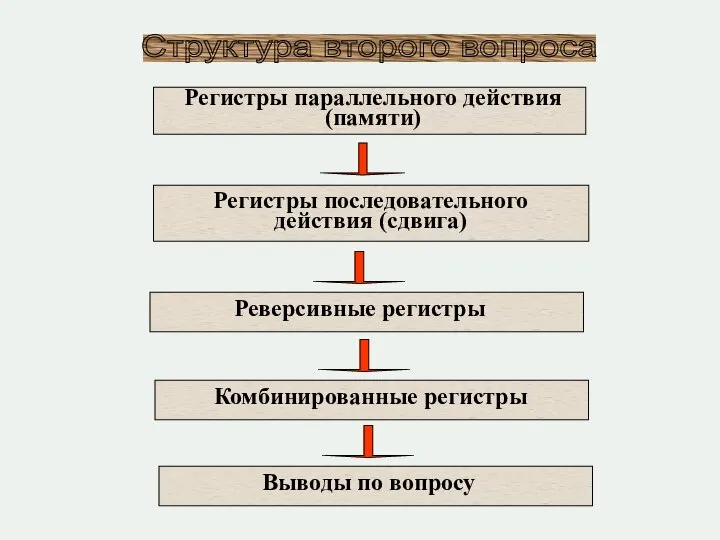

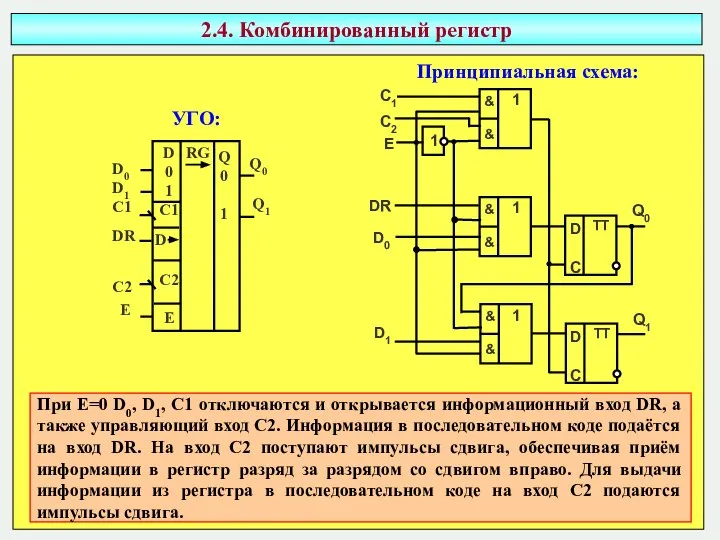

комбинированные, в которых сочетаются возможности регистров последовательного и параллельного действия.

последовательного действия (сдвигающие), в которых приём и выдача информации производится последовательным кодом;

параллельного действия (памяти), в которых приём и выдача информации осуществляется параллельным кодом;

По способу хранения и выдачи информации:

Регистром называется цифровое устройство, предназначенное для приёма, хранения и выдачи двоично-кодированной информации.

Количество триггеров (n) в регистре называют его разрядностью.

Классификация регистров

По количеству информационных каналов:

По направлению сдвига информации:

![Цифровые устройства и микропроцессоры [Электронный ресурс] : Учебное пособие/ Жидков Е.Н.](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/727933/slide-7.jpg)

Технологические разработки ООО”Нефтегазгеофизика” и их использование при строительстве и эксплуатации нефтегазовых скважин

Технологические разработки ООО”Нефтегазгеофизика” и их использование при строительстве и эксплуатации нефтегазовых скважин Теорема Эйлера и малая теорема Ферма. Методы решения сравнений

Теорема Эйлера и малая теорема Ферма. Методы решения сравнений Структура и содержание электронного паспорта социально значимого объекта МОУ лицей МОК№2 г. Джанкой

Структура и содержание электронного паспорта социально значимого объекта МОУ лицей МОК№2 г. Джанкой Котоматограф или Синемяу

Котоматограф или Синемяу Модуль: Тур

Модуль: Тур Нагрев и охлаждение электрических аппаратов. Виды потерь в деталях электрических аппаратов

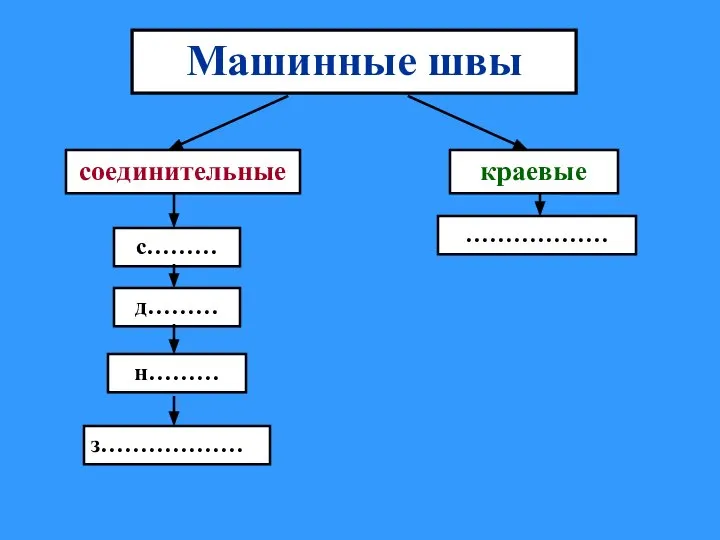

Нагрев и охлаждение электрических аппаратов. Виды потерь в деталях электрических аппаратов Машинные швы

Машинные швы Merged_document

Merged_document Nadzieja

Nadzieja 20150122_otechestvennaya_voyna_1812_goda

20150122_otechestvennaya_voyna_1812_goda Всемирное наследие

Всемирное наследие Условия изучения дисциплины Conditions for studying the discipline:

Условия изучения дисциплины Conditions for studying the discipline: родословная Кунцевич Галина

родословная Кунцевич Галина Аппаратные средства вычислительной техники

Аппаратные средства вычислительной техники Горнопроходческие работы при строительстве стволов

Горнопроходческие работы при строительстве стволов Подборка примеров общественно-административных зданий

Подборка примеров общественно-административных зданий Бисероплетение Вышитый смайлик

Бисероплетение Вышитый смайлик Stagioni nel cinema

Stagioni nel cinema Совершенствование организации перевозок опасных грузов автотранспортом в условиях заданного предприятия

Совершенствование организации перевозок опасных грузов автотранспортом в условиях заданного предприятия Лучистое отопление

Лучистое отопление Вокзал будущего

Вокзал будущего Презентація_Слісаренко (1)

Презентація_Слісаренко (1) АО Южморгеология. Описание района работ

АО Южморгеология. Описание района работ Чердачный наблюдатель. Фильм о коте Кузе

Чердачный наблюдатель. Фильм о коте Кузе Устав ООО Инновационный центр пожарной безопасности

Устав ООО Инновационный центр пожарной безопасности Общий вид столярной мастерской

Общий вид столярной мастерской Васильев день, или Старый Новый год

Васильев день, или Старый Новый год Прошедшее время

Прошедшее время