Содержание

- 2. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Определение интерфейса Интерфейс – это понятие,

- 3. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Характеристики интерфейса Интерфейс характеризуется следующими параметрами:

- 4. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Интерфейсы передачи данных Наиболее распространённые интерфейсы

- 5. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 UART (1) UART – универсальный асинхронный

- 6. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 UART (2) По структуре это обычный

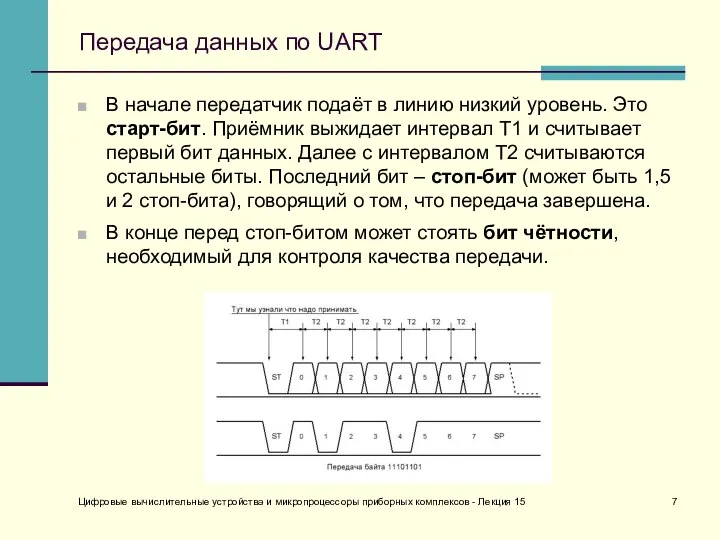

- 7. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Передача данных по UART В начале

- 8. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 SPI SPI - последовательный синхронный стандарт

- 9. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Сигналы, используемые в SPI В SPI

- 10. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 CPOL и CPHA В дополнение к

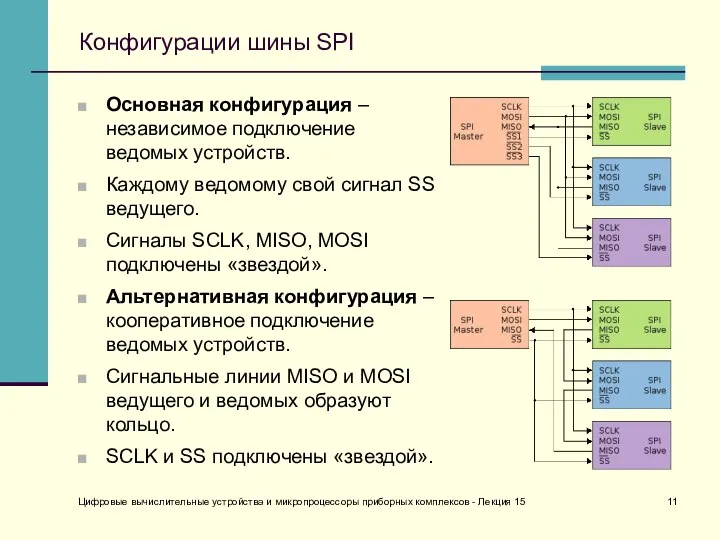

- 11. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Конфигурации шины SPI Основная конфигурация –

- 12. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Достоинства и недостатки SPI Достоинства: передача

- 13. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Применение шины SPI Основная конфигурация шины

- 14. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 I2C I2C – последовательная шина данных

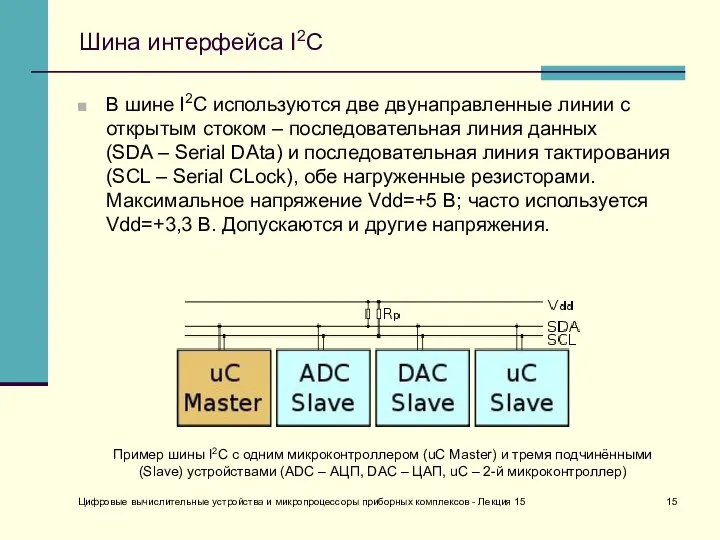

- 15. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Шина интерфейса I2C В шине I2C

- 16. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Адресация в шине I2C (1) Каждое

- 17. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Адресация в шине I2C (2) Первые

- 18. Цифровые вычислительные устройства и микропроцессоры приборных комплексов - Лекция 15 Принцип работы I2C (1) Процедура обмена

- 20. Скачать презентацию

Физические механизмы перекрытия изоляционных конструкций

Физические механизмы перекрытия изоляционных конструкций Общество как форма жизнедеятельности людей

Общество как форма жизнедеятельности людей интеллигентность

интеллигентность Компания Ebang

Компания Ebang Ювілей Самохвала Михайла. Фотоальбом

Ювілей Самохвала Михайла. Фотоальбом Псалмы 32-36, святорусский текст

Псалмы 32-36, святорусский текст Вторая жизнь капроновых колготок

Вторая жизнь капроновых колготок Технологии ремонта и отделки жилых помещений

Технологии ремонта и отделки жилых помещений Односторонняя контактная сварка, оборудование и режимы сварки

Односторонняя контактная сварка, оборудование и режимы сварки Мастер-класс Печатание листьями

Мастер-класс Печатание листьями Тепловые двигатели и нагнетатели. Паротурбинные установки (часть 1)

Тепловые двигатели и нагнетатели. Паротурбинные установки (часть 1) МР Анатомия головного мозга МРТ

МР Анатомия головного мозга МРТ Брейн-ринг

Брейн-ринг Презентация к семинару

Презентация к семинару Химическая технология

Химическая технология Работа глаз и видимые спектры

Работа глаз и видимые спектры Поздравление учителей к 8 марта

Поздравление учителей к 8 марта Портфолио. Васенина Мария Николаевна

Портфолио. Васенина Мария Николаевна Понятие о нефтяной залежи. Часть 1

Понятие о нефтяной залежи. Часть 1 Петер Ветш. Концепция земляных домов

Петер Ветш. Концепция земляных домов Что такое лес

Что такое лес Software and Hardware for control of NPP electric- and heat-engineering equipment

Software and Hardware for control of NPP electric- and heat-engineering equipment Покормите птиц зимой

Покормите птиц зимой Интерактивные задания для мультимедийной доски

Интерактивные задания для мультимедийной доски Формирование сквозных металлизированных отверстий в арсенид-галлиевых СВЧ МИС

Формирование сквозных металлизированных отверстий в арсенид-галлиевых СВЧ МИС Новая презентация-1

Новая презентация-1 Заголовок слайда, подзаголовок слайда

Заголовок слайда, подзаголовок слайда Какое Рождество без ангела?

Какое Рождество без ангела?