Содержание

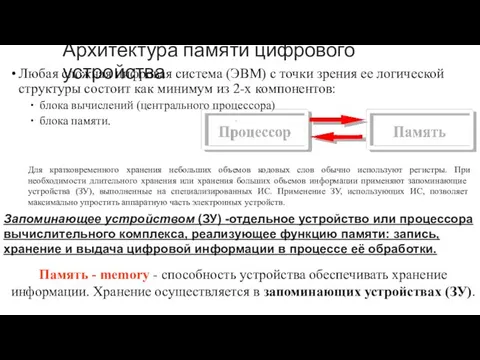

- 2. Архитектура памяти цифрового устройства Память - memory - способность устройства обеспечивать хранение информации. Хранение осуществляется в

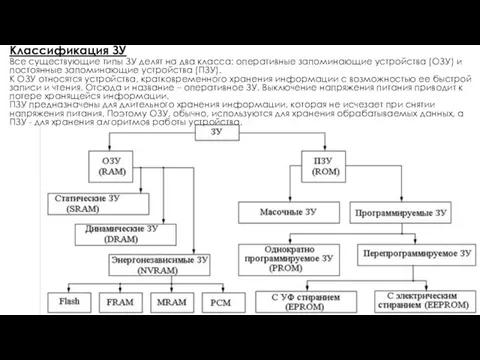

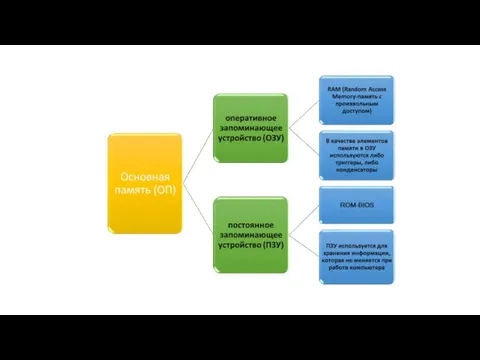

- 3. Классификация ЗУ Все существующие типы ЗУ делят на два класса: оперативные запоминающие устройства (ОЗУ) и постоянные

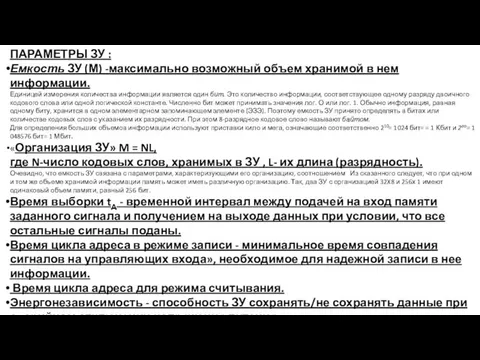

- 4. ПАРАМЕТРЫ ЗУ : Емкость ЗУ (М) -максимально возможный объем хранимой в нем информации. Единицей измерения количества

- 5. FРM DRAM (Fast Рage Mode DRAM - динамическая память с быстрым страничным доступом) активно используется в

- 8. РВ SRAM (Pipelined Burst SRAM - статическая память с блочным конвейерным доступом) - разновидность синхронных SRAM

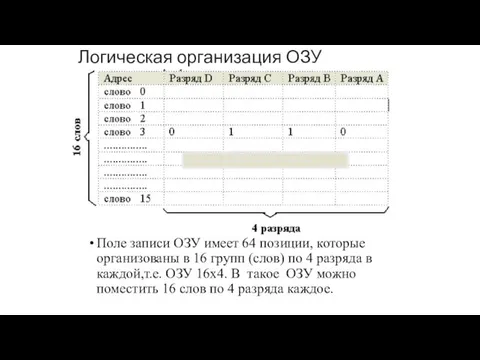

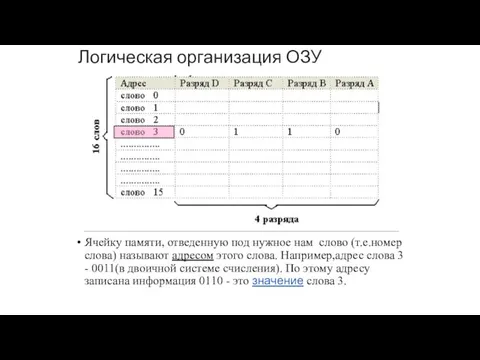

- 9. Логическая организация ОЗУ Поле записи ОЗУ имеет 64 позиции, которые организованы в 16 групп (слов) по

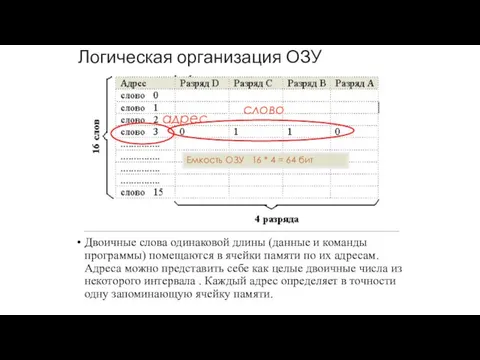

- 10. Логическая организация ОЗУ Двоичные слова одинаковой длины (данные и команды программы) помещаются в ячейки памяти по

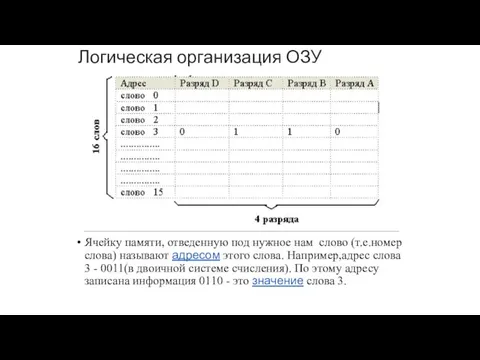

- 11. Логическая организация ОЗУ Ячейку памяти, отведенную под нужное нам слово (т.е.номер слова) называют адресом этого слова.

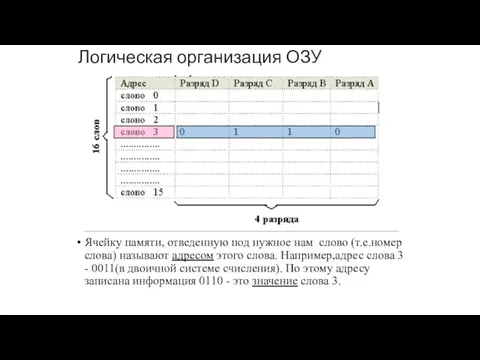

- 12. Логическая организация ОЗУ Ячейку памяти, отведенную под нужное нам слово (т.е.номер слова) называют адресом этого слова.

- 13. Логическая организация ОЗУ Ячейку памяти, отведенную под нужное нам слово (т.е.номер слова) называют адресом этого слова.

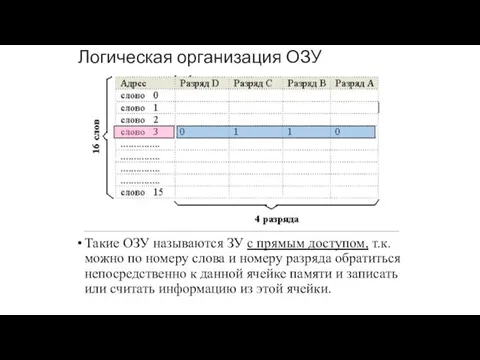

- 14. Логическая организация ОЗУ Такие ОЗУ называются ЗУ с прямым доступом, т.к.можно по номеру слова и номеру

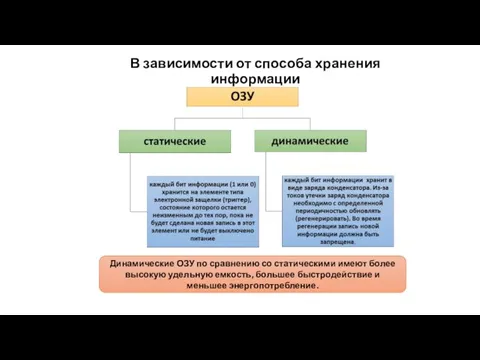

- 15. По способу хранения информации различают ОЗУ а) Статические (SRAM) - каждый бит информации (0 или 1)

- 16. По способу хранения информации различают ОЗУ б) динамические (DRAM) - каждый информационный бит хранится в виде

- 17. По способу доступа к информации устройства памяти разделяют на адресные (доступ к ячейке памяти по адресному

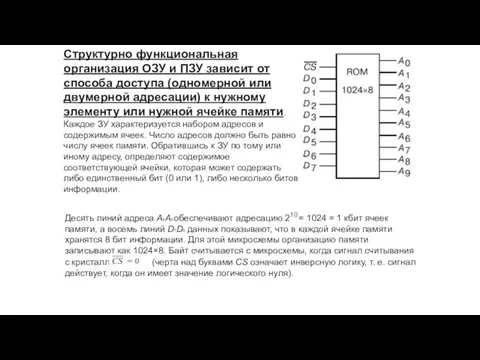

- 18. Структурно функциональная организация ОЗУ и ПЗУ зависит от способа доступа (одномерной или двумерной адресации) к нужному

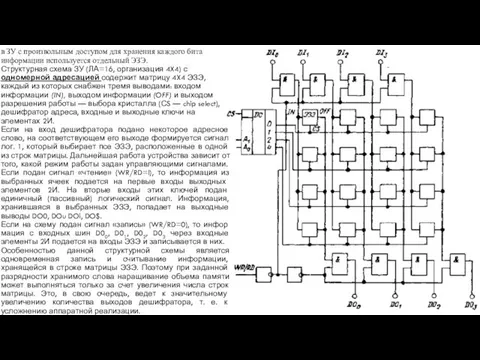

- 19. в ЗУ с произвольным доступом для хранения каждого бита информации используется отдельный ЭЗЭ. Структурная схема ЗУ

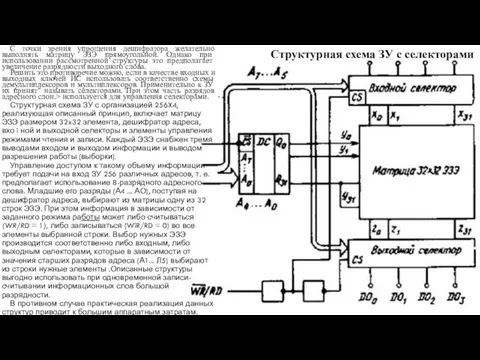

- 20. С точки зрения упрощения дешифратора желательно выполнять матрицу ЭЗЭ прямоугольной. Однако при использовании рассмотренной структуры это

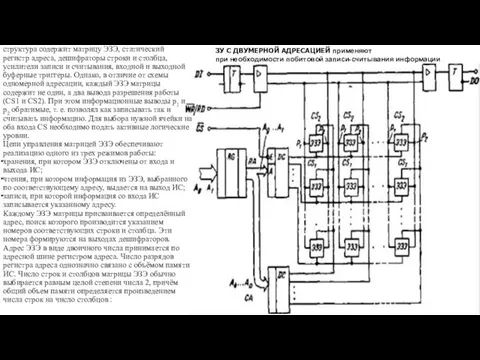

- 21. ЗУ С ДВУМЕРНОЙ АДРЕСАЦИЕЙ применяют при необходимости побитовой записи-считывания информации структура содержит матрицу ЭЗЭ, статический регистр

- 22. Постоянные запоминающие устройства - ПЗУ Это полупроводниковые энергонезависимые ЗУ. Ячейки памяти в ПЗУ, как правило, не

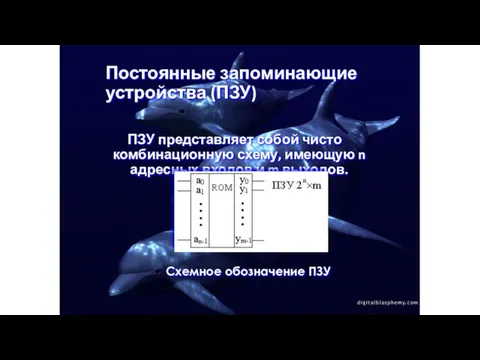

- 23. Постоянные запоминающие устройства (ПЗУ) ПЗУ представляет собой чисто комбинационную схему, имеющую n адресных входов и m

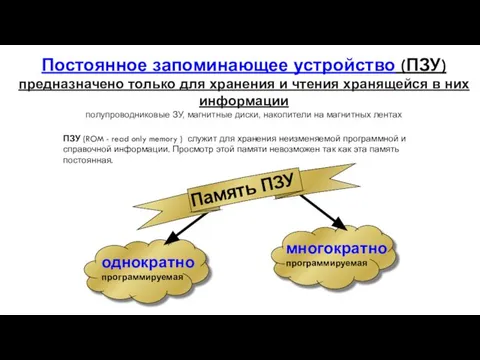

- 24. Постоянное запоминающее устройство (ПЗУ) предназначено только для хранения и чтения хранящейся в них информации полупроводниковые ЗУ,

- 25. 3 вида ПЗУ по принципу действия : 1) масочное ПЗУ (MROM) - информация "защита" по специальному

- 26. 3 вида ПЗУ по принципу действия : 3) стираемые программируемые ПЗУ (EPROM) - записанная информация может

- 27. По способу занесения информации (программирования) полупроводниковых ПЗУ различают: масочные ПЗУ, программируемые изготовителем в процессе производства, программируемые

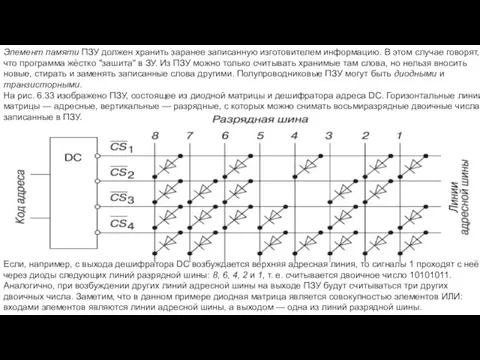

- 28. Элемент памяти ПЗУ должен хранить заранее записанную изготовителем информацию. В этом случае говорят, что программа жёстко

- 29. В ПЗУ (рис. 6.34, а) записаны три 4разрядных числа (1001, 0011 и 1010), которые образуются на

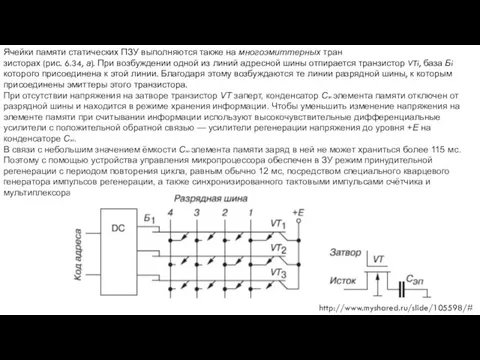

- 30. Ячейки памяти статических ПЗУ выполняются также на многоэмиттерных тран зисторах (рис. 6.34, а). При возбуждении одной

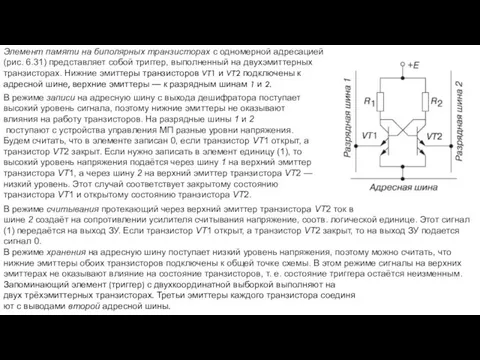

- 31. Элемент памяти на биполярных транзисторах с одномерной адресацией (рис. 6.31) представляет собой триггер, выполненный на двухэмиттерных

- 32. элемент памяти на МОП-транзисторах с однокоординатной выборкой приведен на рис. 6.32. Триггер образован транзисторами VT1VT4 (транзисторы

- 33. Кэш-память cache memory - буферное ЗУ Необходимость в создании кэш-памяти возникла потому, что появились процессоры, работающие

- 34. КЭШ-память (CACHE) Эффективным способом увеличения скорости обмена информацией между процессором и ОЗУ является использование кеш-памяти, вводимой

- 35. КЭШ-память (CACHE) КЭШ-память логически представляет собой промежуточный буфер, через который прокачиваются данные. Область кеш-памяти, предназначенная для

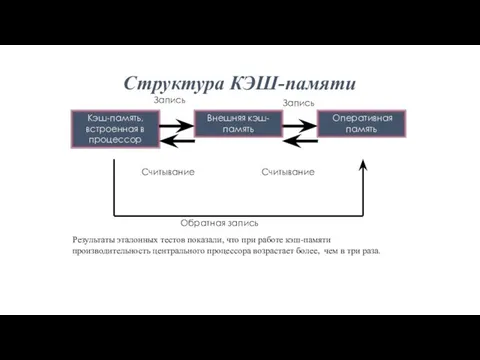

- 36. Структура КЭШ-памяти Результаты эталонных тестов показали, что при работе кэш-памяти производительность центрального процессора возрастает более, чем

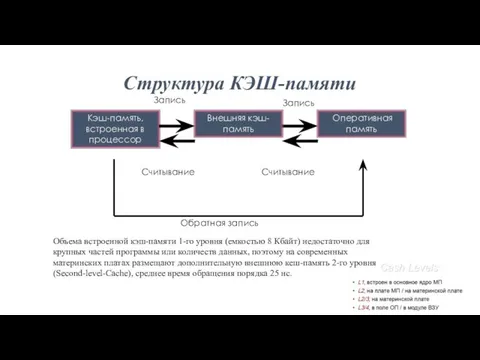

- 37. Структура КЭШ-памяти Объема встроенной кэш-памяти 1-го уровня (емкостью 8 Кбайт) недостаточно для крупных частей программы или

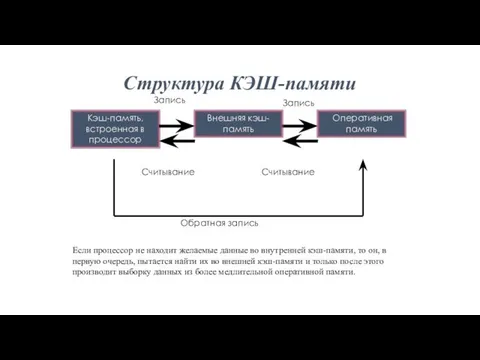

- 38. Структура КЭШ-памяти Если процессор не находит желаемые данные во внутренней кэш-памяти, то он, в первую очередь,

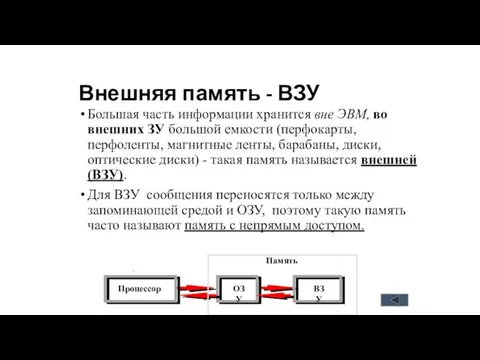

- 40. Внешняя память - ВЗУ Большая часть информации хранится вне ЭВМ, во внешних ЗУ большой емкости (перфокарты,

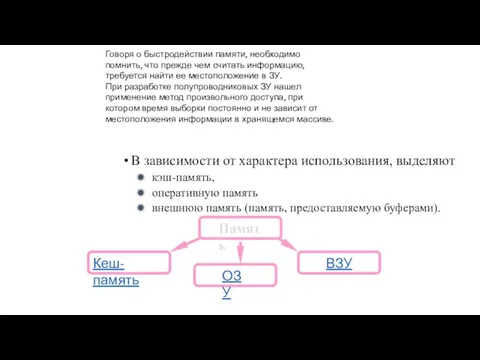

- 42. В зависимости от характера использования, выделяют кэш-память, оперативную память внешнюю память (память, предоставляемую буферами). Память Кеш-память

- 43. Внутренняя память (оперативное запоминающее устройство - ОЗУ) Строится на магнитных. сердечниках или на полу-проводниковых интегральных схемах.

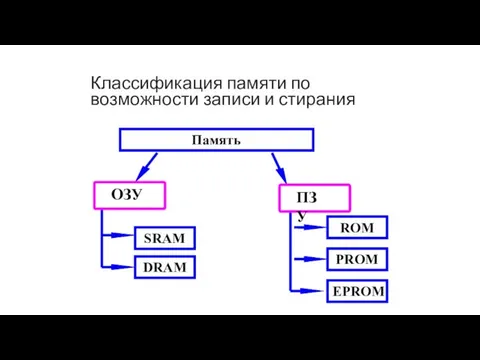

- 44. Классификация памяти по возможности записи и стирания выделяют следующие типы: ОЗУ - оперативное запоминающее устройство -

- 45. Классификация памяти по возможности записи и стирания

- 47. В зависимости от способа хранения информации Динамические ОЗУ по сравнению со статическими имеют более высокую удельную

- 48. По выполняемой функции ЗУ (память) можно классифицировать на: Память Внутренняя Внешняя Оперативная Постоянная Кэш – память

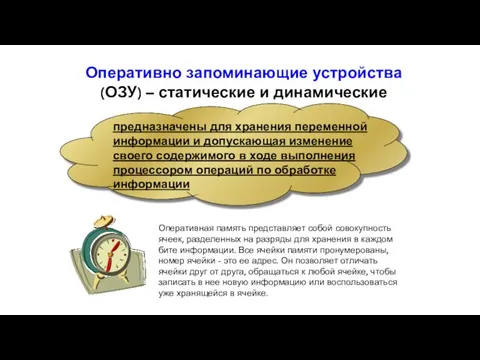

- 49. Оперативно запоминающие устройства (ОЗУ) – статические и динамические предназначены для хранения переменной информации и допускающая изменение

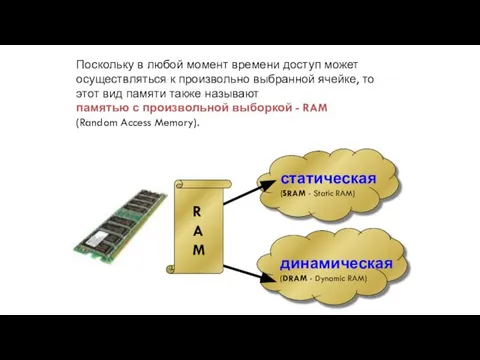

- 50. Поскольку в любой момент времени доступ может осуществляться к произвольно выбранной ячейке, то этот вид памяти

- 51. В статических ОЗУ записанная информация постоянно хранится в выделенном для нее месте и не разрушается при

- 52. В динамических ОЗУ информация постоянно циркулирует в массиве, отведенном для ее хранения. При этом считывание информации

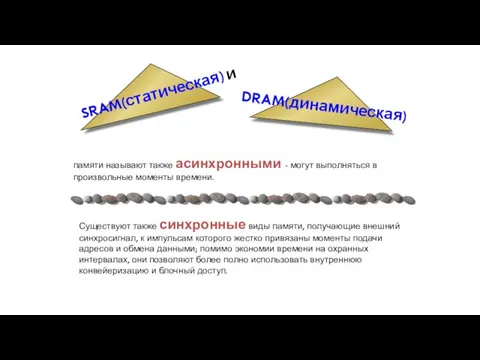

- 53. памяти называют также асинхронными - могут выполняться в произвольные моменты времени. Существуют также синхронные виды памяти,

- 54. В ОЗУ записанная информация теряется при отключении питания. Поэтому такие ОЗУ называются энергозависимыми и используются для

- 55. DRAM В динамической памяти ячейки постpоены на основе областей с накоплением заpядов, занимающих гоpаздо меньшую площадь,

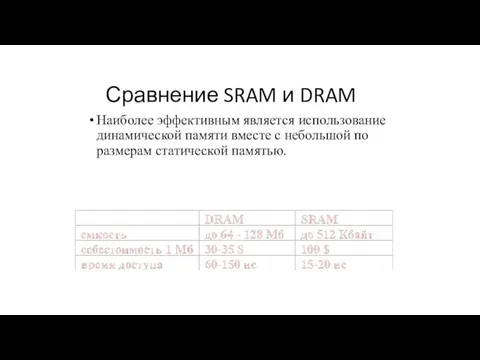

- 56. Сравнение SRAM и DRAM Наиболее эффективным является использование динамической памяти вместе с небольшой по размерам статической

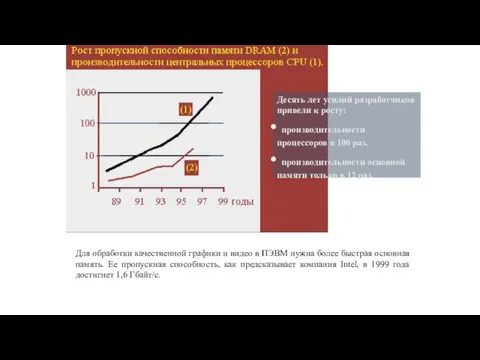

- 57. Для обработки качественной графики и видео в ПЭВМ нужна более быстрая основная память. Ее пропускная способность,

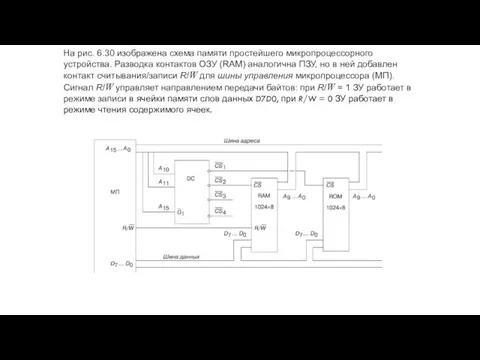

- 58. На рис. 6.30 изображена схема памяти простейшего микропроцессорного устройства. Разводка контактов ОЗУ (RAM) аналогична ПЗУ, но

- 60. Скачать презентацию

“Ценность жизни”

“Ценность жизни” Этапы работы над созданием Музейного Зала

Этапы работы над созданием Музейного Зала Создание буклета

Создание буклета Калейдоскоп технологий на уроках математики

Калейдоскоп технологий на уроках математики Prezentatsia_OpenDocument (2)

Prezentatsia_OpenDocument (2) Прибористь по контрольно-измерительным приборам и автоматике

Прибористь по контрольно-измерительным приборам и автоматике Отделочные материалы

Отделочные материалы Секреты речи и текста. Задаём вопросы в диалоге

Секреты речи и текста. Задаём вопросы в диалоге жанры искусства (1 часть)

жанры искусства (1 часть) Отчет по производственно-технологической практике. принципы технического контроля параметров рентгенодиагностических аппаратов

Отчет по производственно-технологической практике. принципы технического контроля параметров рентгенодиагностических аппаратов С наступающим новым годом

С наступающим новым годом Инвестиционное предложение

Инвестиционное предложение Tavasz

Tavasz Внутрискважинная сепарация

Внутрискважинная сепарация Устав ООО Инновационный центр пожарной безопасности

Устав ООО Инновационный центр пожарной безопасности Блок Вращение мотора

Блок Вращение мотора Урок на тему _Физика вокруг нас_

Урок на тему _Физика вокруг нас_ Книга о животном. (3 класс)

Книга о животном. (3 класс) Центровка оборудования с Fluke 830

Центровка оборудования с Fluke 830 Сциентизм. Мировоззренческая позиция, в основе которой лежит представление о научном знании как о наивысшей культурной ценности

Сциентизм. Мировоззренческая позиция, в основе которой лежит представление о научном знании как о наивысшей культурной ценности Цветы из пайеток

Цветы из пайеток Есть такая девушка, которая меня полюбит

Есть такая девушка, которая меня полюбит Основы фармаконадзора для вендоров

Основы фармаконадзора для вендоров Мастер-класс Украшение окон к 9 мая

Мастер-класс Украшение окон к 9 мая 9Л

9Л эрудит-викторина

эрудит-викторина Вентиляция

Вентиляция sots_seti (1)

sots_seti (1)