Содержание

- 2. Архитектура ПК Архитектурой принято называть совокупность всех программно доступных аппаратных средств процессора. Понятие архитектуры является комплексным

- 3. В основе любого устройства лежат базовые принципы, на основе которых в дальнейшем строится система Набор этих

- 4. Широкое распространение получили персональные компьютеры производства компании Apple Computer и компании IBM (International Business Machines).

- 5. Компания Apple производит широко известные компьютеры Macintosh Особенности все основные узлы компьютера размещены на одной плате

- 6. IBM-совместимые компьютеры строятся на базе принципа открытой архитектуры: компьютер составлен из отдельных узлов (блоков), пользователю предоставляются

- 7. Компьютеры, не совместимые с IBM PC Например, компьютер Power PC с процессором производства корпорации Motorola

- 8. Общие архитектурные свойства и принципы Эти свойства и принципы присущи всем современным машинам фон-неймановской архитектуры. Принцип

- 9. Общие архитектурные свойства и принципы Линейное пространство памяти ОП организована как совокупность ячеек памяти (байтов), которым

- 10. Структурная схема компьютера Оперативная память Устройство управления АЛУ Регистровая память КЭШ-память (Level 1) Процессор ВИДЕО АУДИО

- 11. Материнская плата Основной элемент компьютера – материнская (системная) плата вместе с микропроцессором Предназначена для обеспечения бесперебойной

- 12. Материнская плата Основные компоненты материнской платы Постоянное запоминающее устройство – ПЗУ Оперативное запоминающее устройство – ОЗУ

- 13. Постоянное запоминающее устройство – ПЗУ Память только для чтения Не предусмотрено изменение содержимого пользователем. После отключения

- 14. Энергонезависимая память (CMOS-память) Хранится информация об устройствах системы и их параметрах (дисковая подсистема); необходимая при каждом

- 15. Системные шины Шина (bus) – общий канал связи, соединяющий отдельные части компьютера (пучок проводов) Перенос информации

- 16. Системные шины Передаваемую информацию можно условно разделить на 3 вида: Данные – обрабатываемые числовые значения. Адреса

- 17. Шина управления Микропроцессор выставляет на шине управления команды управления узлами системы и получает ответные сигналы состояния

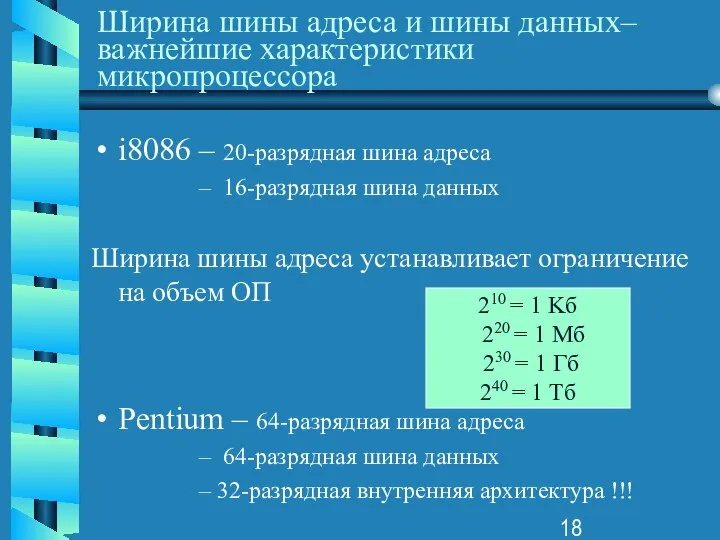

- 18. Ширина шины адреса и шины данных– важнейшие характеристики микропроцессора i8086 – 20-разрядная шина адреса 16-разрядная шина

- 19. Внутренняя шина Три шины вместе (шина адреса, шина данных, шина управления) составляют процессорную (внутреннюю) шину Шина

- 20. Системная шина Микропроцессор напрямую работает только с несколькими устройствами, а от остальных отделен специальными микросхемами-буферами (для

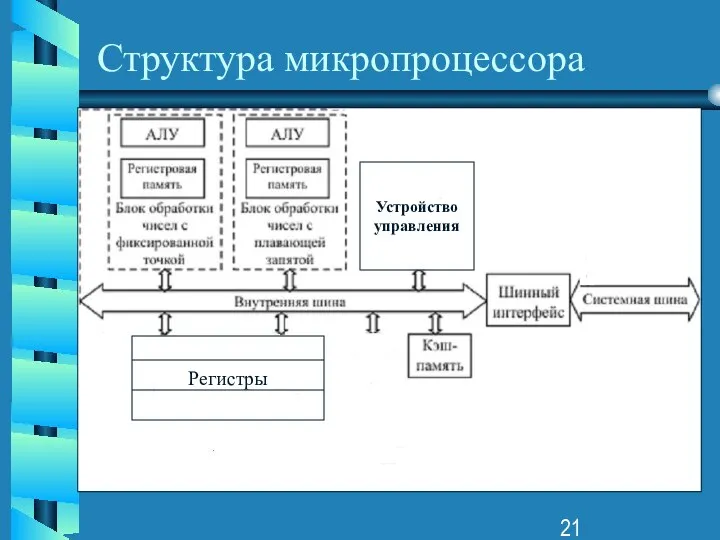

- 21. Структура микропроцессора Устройство управления Регистры

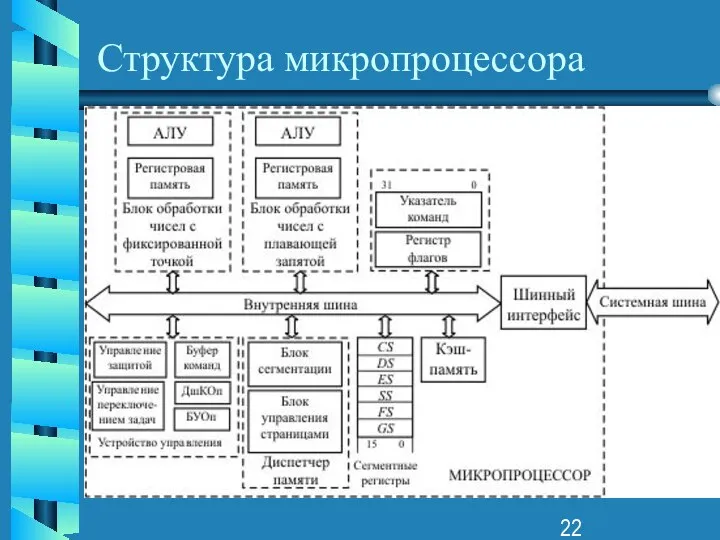

- 22. Структура микропроцессора

- 23. Тактовая частота Управление процессором осуществляется с помощью сигналов – тактовых импульсов, которые выдаются через фиксированные интервалы

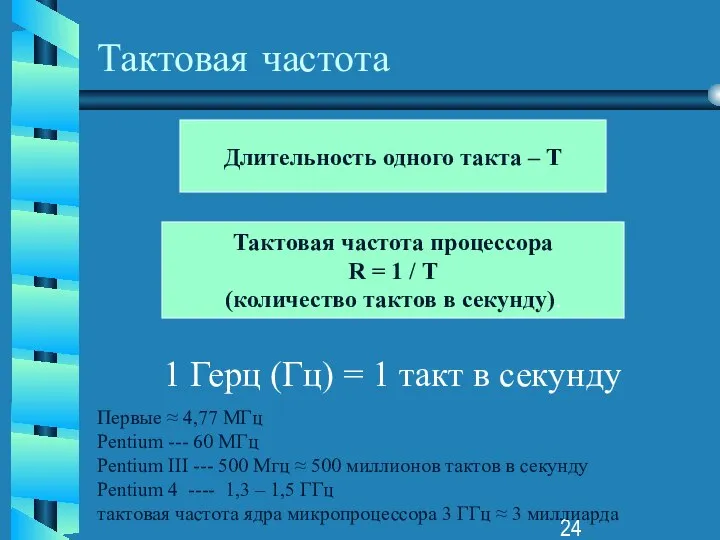

- 24. Тактовая частота Тактовая частота процессора R = 1 / T (количество тактов в секунду). Длительность одного

- 25. Тактовая частота Решает задачу синхронизации функционирования всех компонентов системы (их действия должны быть «увязаны» между собой,

- 26. Мультипроцессорные системы Система, содержащая несколько (много) процессоров, называется многопроцессорной (мультипроцессорной) Процессоры выполняют параллельно несколько задач (несколько

- 27. Мультикомпьютерные системы Мультикомпьютерные = многомашинные системы - соединенные группы компьютеров Каждому компьютеру доступна только своя память

- 28. Элементная база процессора Процессор состоит из очень большого набора элементов, собранных определенным образом. Каждый элемент –

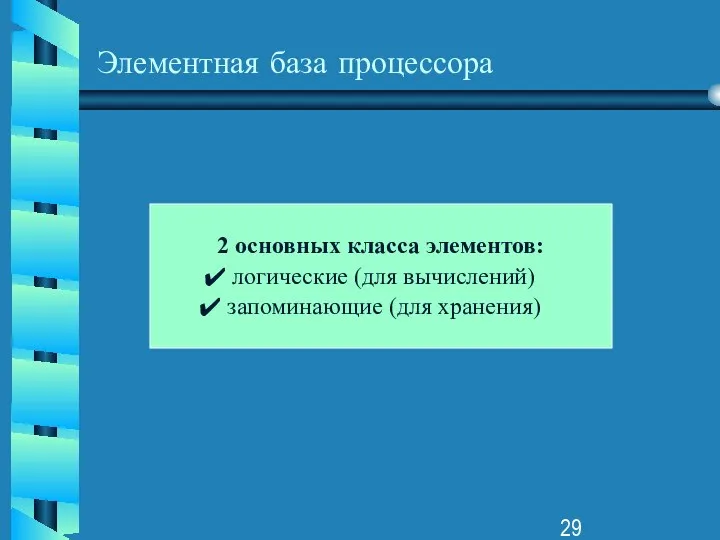

- 29. Элементная база процессора 2 основных класса элементов: логические (для вычислений) запоминающие (для хранения)

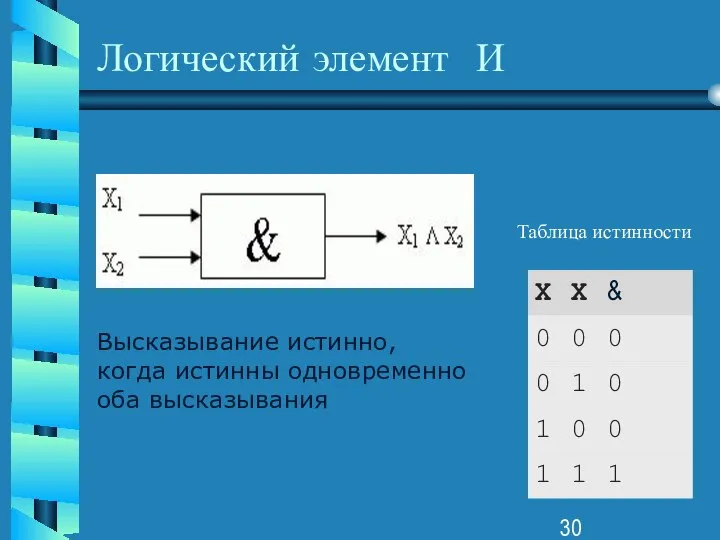

- 30. Логический элемент И Высказывание истинно, когда истинны одновременно оба высказывания Таблица истинности

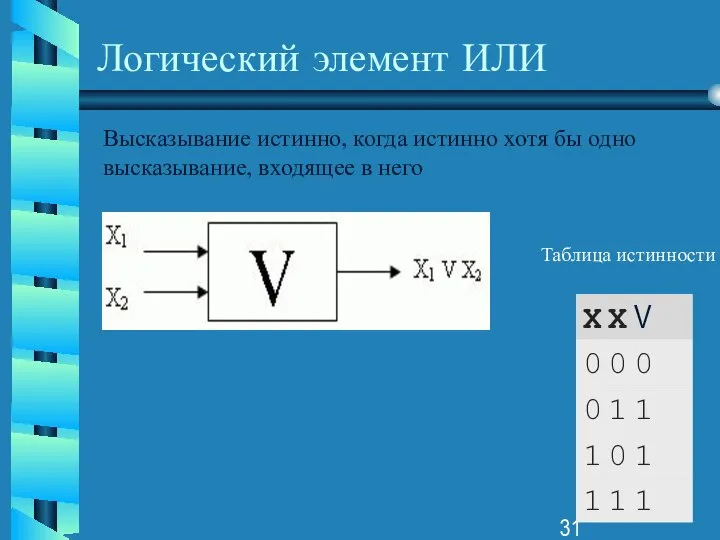

- 31. Логический элемент ИЛИ Высказывание истинно, когда истинно хотя бы одно высказывание, входящее в него Таблица истинности

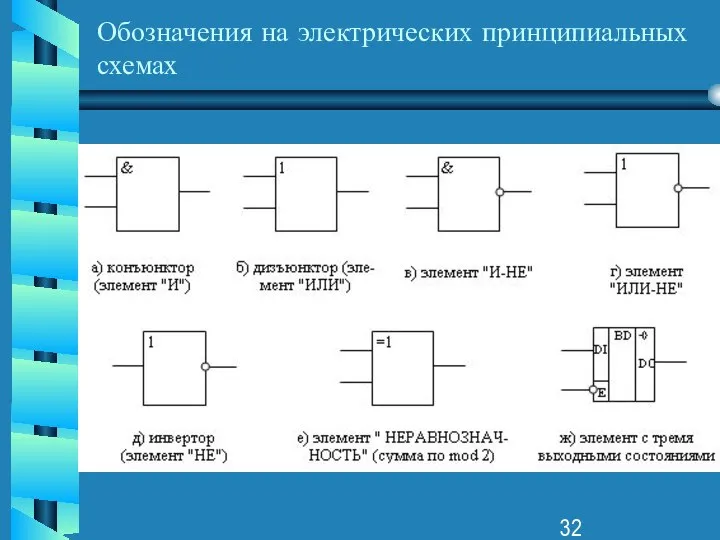

- 32. Обозначения на электрических принципиальных схемах

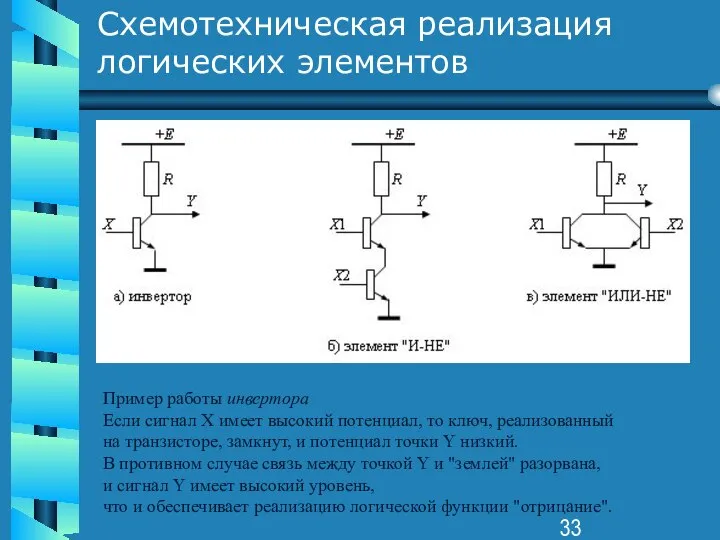

- 33. Схемотехническая реализация логических элементов Пример работы инвертора Если сигнал X имеет высокий потенциал, то ключ, реализованный

- 34. Запоминающие элементы Базовый запоминающий элемент в электротехнике – ТРИГГЕР Триггер используется для хранения одного бита информации

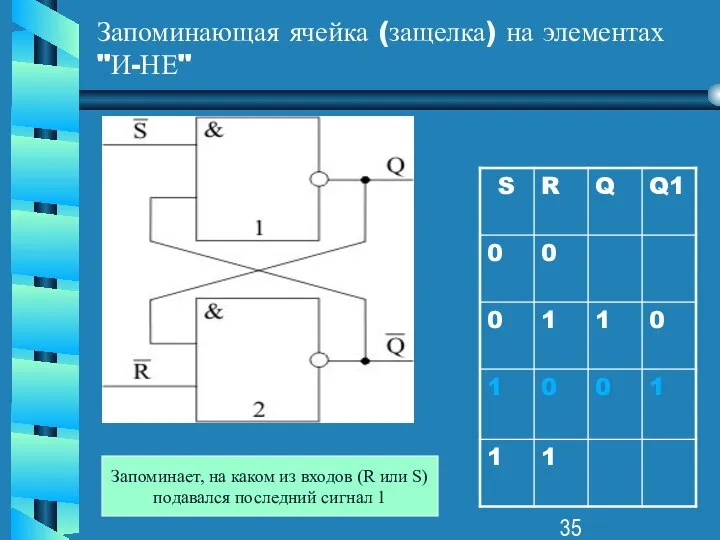

- 35. Запоминающая ячейка (защелка) на элементах "И-НЕ" Запоминает, на каком из входов (R или S) подавался последний

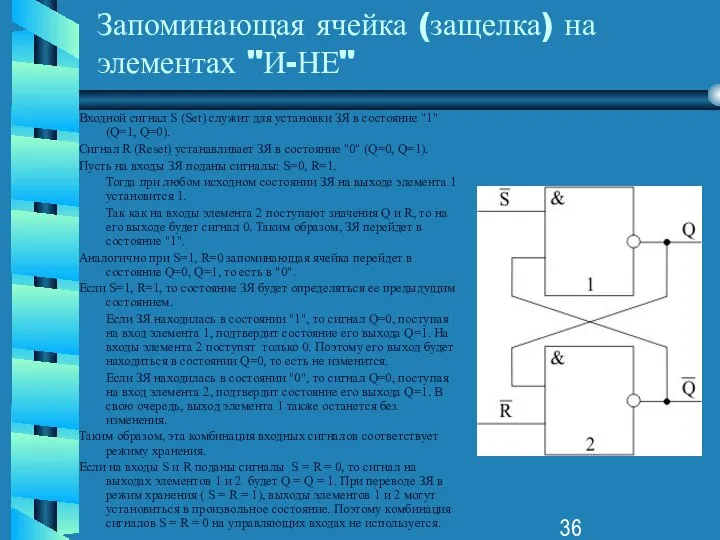

- 36. Запоминающая ячейка (защелка) на элементах "И-НЕ" Входной сигнал S (Set) служит для установки ЗЯ в состояние

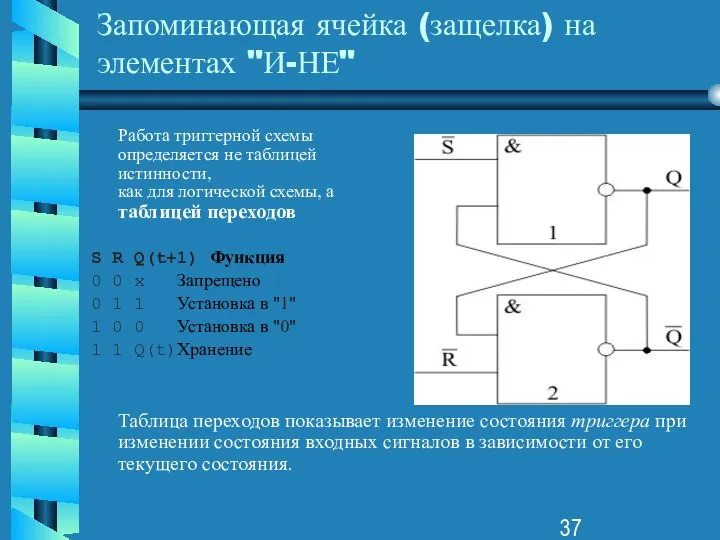

- 37. Запоминающая ячейка (защелка) на элементах "И-НЕ" Работа триггерной схемы определяется не таблицей истинности, как для логической

- 39. Скачать презентацию

Интеллектуальная игра

Интеллектуальная игра  Земельные, водные и биологические ресурсы России Подготовила Студентка группы Э122б Арсёнова В.

Земельные, водные и биологические ресурсы России Подготовила Студентка группы Э122б Арсёнова В. Автор материалов: Безруких Марьяна Михайловна Трудности обучения письму и чтению в начальной школе. Род

Автор материалов: Безруких Марьяна Михайловна Трудности обучения письму и чтению в начальной школе. Род Дизайнер школьной формы

Дизайнер школьной формы Организация воспитательной работы Принципы построения воспитательной работы

Организация воспитательной работы Принципы построения воспитательной работы Актуальные требования к персоналу гостиниц и иных средств размещений

Актуальные требования к персоналу гостиниц и иных средств размещений Деньги, кредит, банки К.э.н., доцент Демина Надежда Константиновна

Деньги, кредит, банки К.э.н., доцент Демина Надежда Константиновна  Прошу дождя

Прошу дождя Вклад Н.Д.Кондратьева в общую теорию систем Выполнила: студентка 2 курса ФТД Т-114 Галибина Любовь

Вклад Н.Д.Кондратьева в общую теорию систем Выполнила: студентка 2 курса ФТД Т-114 Галибина Любовь  Happy saint valentine`s day

Happy saint valentine`s day Neue Wörter

Neue Wörter Презентация на тему Урок изобразительного искусства

Презентация на тему Урок изобразительного искусства  Оптоволоконна електроніка

Оптоволоконна електроніка Технология разработки СБИС типа СнК на отечественной платформе по заданным алгоритмам

Технология разработки СБИС типа СнК на отечественной платформе по заданным алгоритмам Партія Вільних Демократів

Партія Вільних Демократів Конфликт. Его виды, примеры

Конфликт. Его виды, примеры Исследование взаимосвязей социально-экономических явлений

Исследование взаимосвязей социально-экономических явлений Услуги по юридическому сопровождению деятельности таможенных представителей и участников внешнеэкономической деятельности

Услуги по юридическому сопровождению деятельности таможенных представителей и участников внешнеэкономической деятельности Презентация на тему "Нынешний школьный аттестат удостоверяет только, что его обладателю хватило способности выдержать столько-

Презентация на тему "Нынешний школьный аттестат удостоверяет только, что его обладателю хватило способности выдержать столько- Виды портрета человека

Виды портрета человека 9-1-2

9-1-2 в космосе еще одна - презентация для начальной школы

в космосе еще одна - презентация для начальной школы Пространственная вертикаль

Пространственная вертикаль Net radiation

Net radiation  Урок русского языка

Урок русского языка  Презентация на тему "Интернациональность английских пословиц и поговорок" - скачать презентации по Педагогике

Презентация на тему "Интернациональность английских пословиц и поговорок" - скачать презентации по Педагогике Презентация на тему: «Инфаркт миокарда»

Презентация на тему: «Инфаркт миокарда»  Удивительные обычаи и традиции разных народов мира

Удивительные обычаи и традиции разных народов мира