Содержание

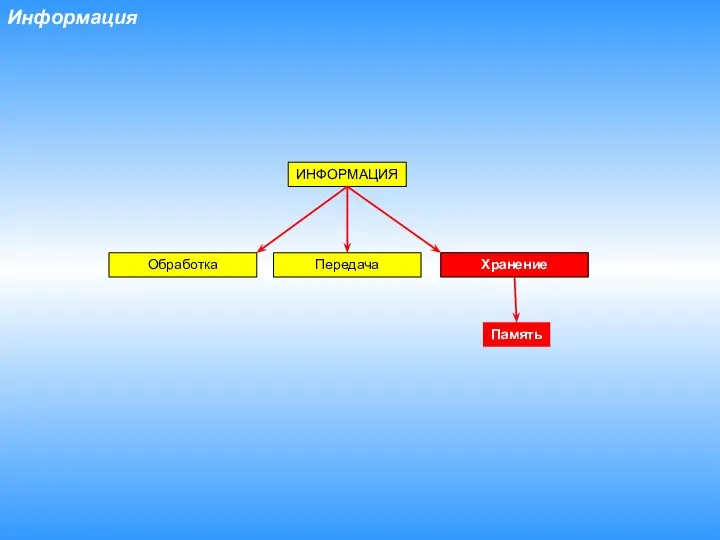

- 2. Информация ИНФОРМАЦИЯ Передача Хранение Обработка Память

- 3. Характеристики памяти Общие характеристики Объем [bit] Быстродействие Энергозависимость Стоимость Плотность [bit/sm3] или [bit/sm2] Время доступа на

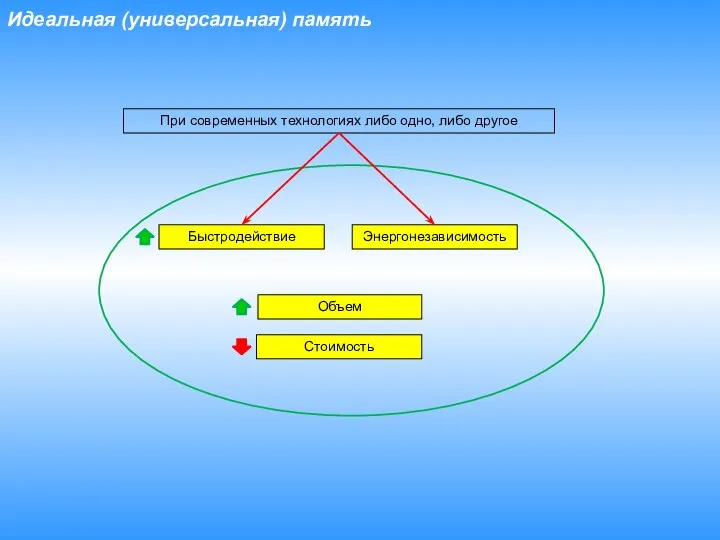

- 4. Идеальная (универсальная) память Объем Быстродействие Энергонезависимость Стоимость При современных технологиях либо одно, либо другое

- 5. Полупроводниковая память Быстродействие Энергонезависимость ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ или или

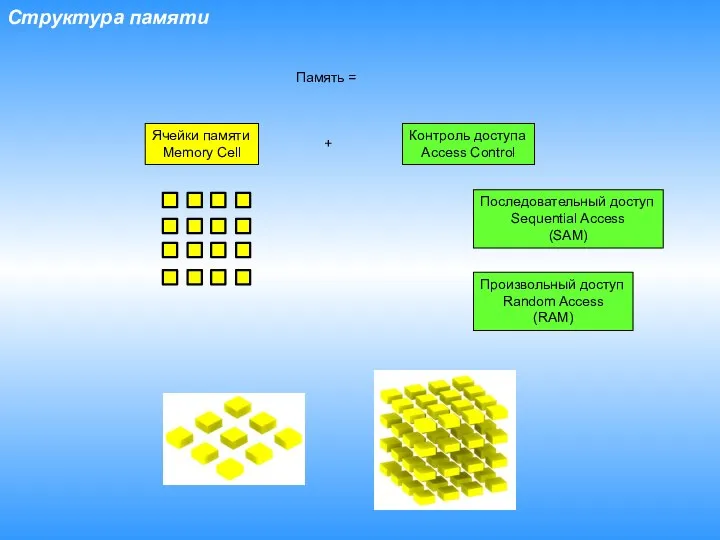

- 6. Структура памяти Ячейки памяти Memory Cell Контроль доступа Access Control Произвольный доступ Random Access (RAM) Последовательный

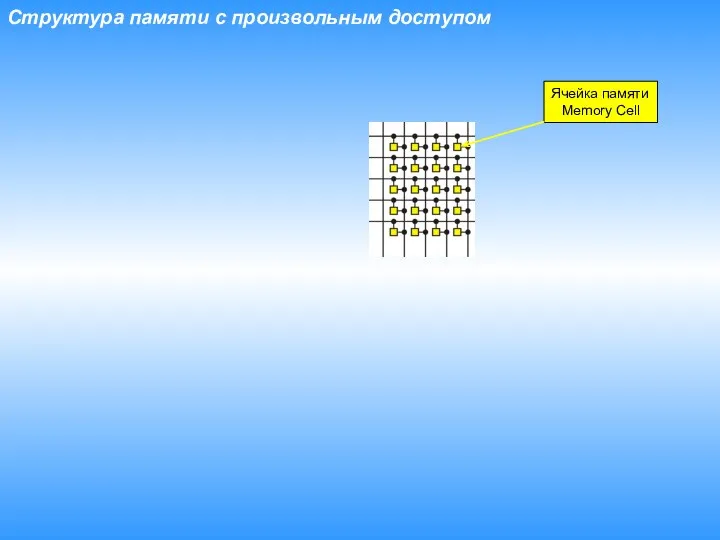

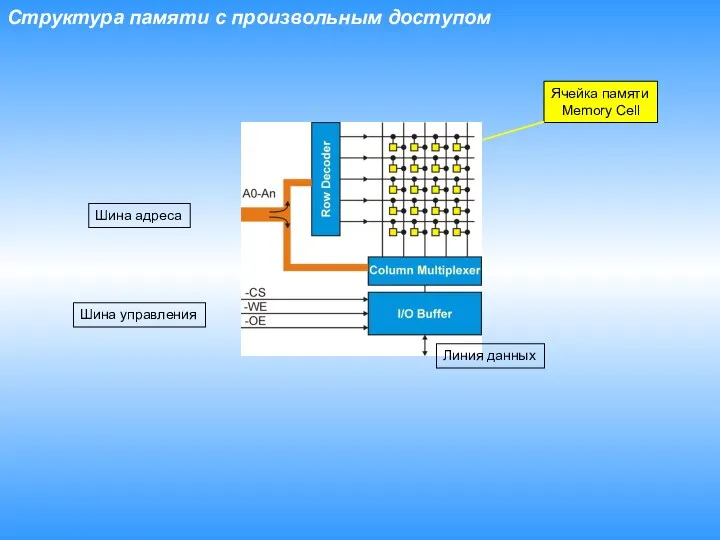

- 7. Структура памяти с произвольным доступом Ячейка памяти Memory Cell

- 8. Структура памяти с произвольным доступом Ячейка памяти Memory Cell Шина адреса Линия данных Шина управления

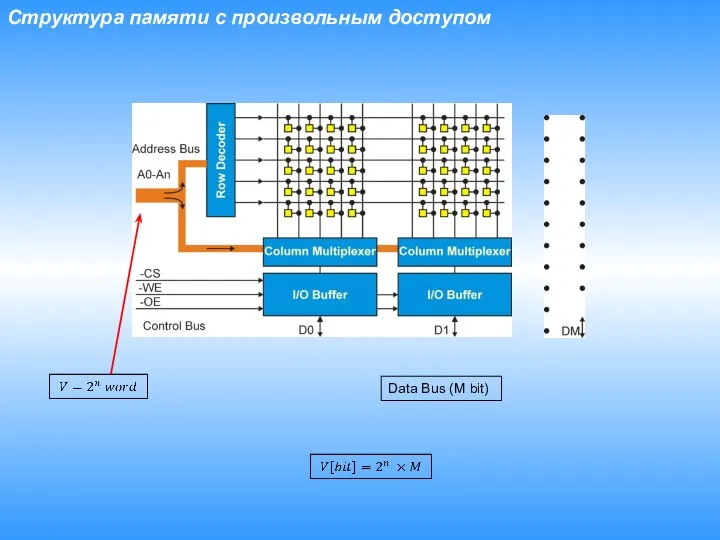

- 9. Структура памяти с произвольным доступом Data Bus (M bit)

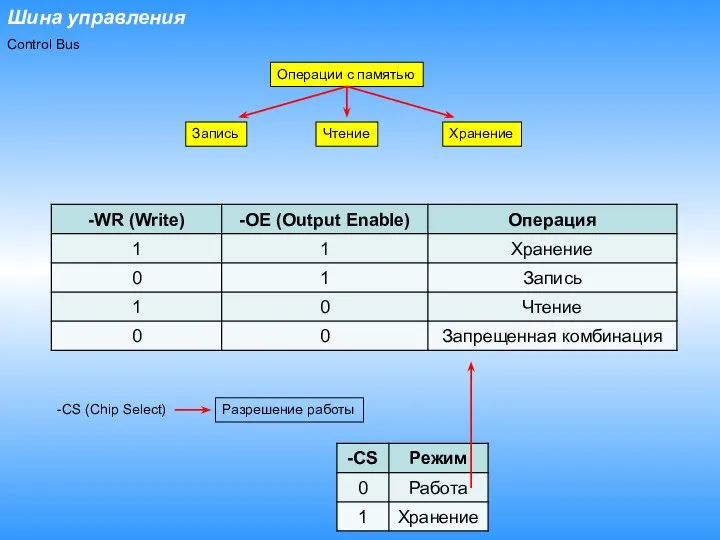

- 10. Шина управления Control Bus Операции с памятью Запись Чтение Хранение -CS (Chip Select) Разрешение работы

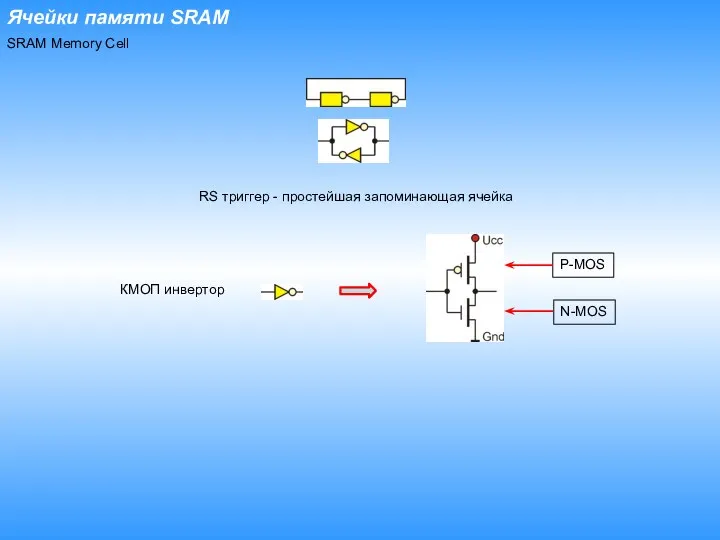

- 11. RS триггер - простейшая запоминающая ячейка КМОП инвертор Ячейки памяти SRAM P-MOS N-MOS SRAM Memory Cell

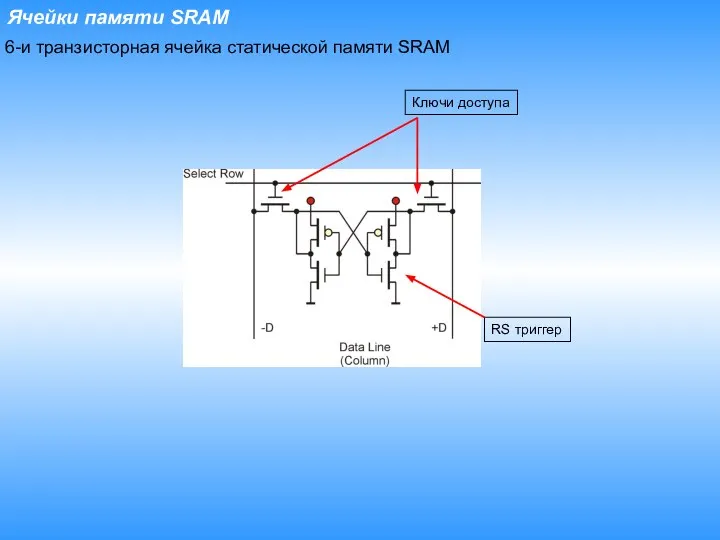

- 12. 6-и транзисторная ячейка статической памяти SRAM Ключи доступа RS триггер Ячейки памяти SRAM

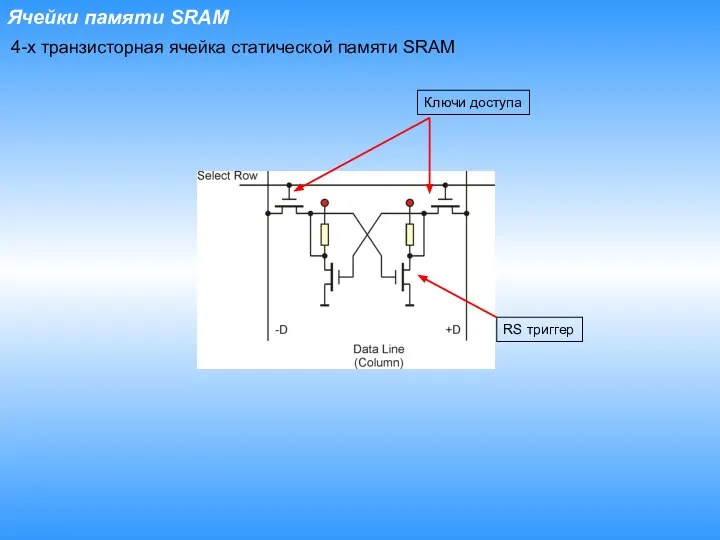

- 13. 4-х транзисторная ячейка статической памяти SRAM Ячейки памяти SRAM Ключи доступа RS триггер

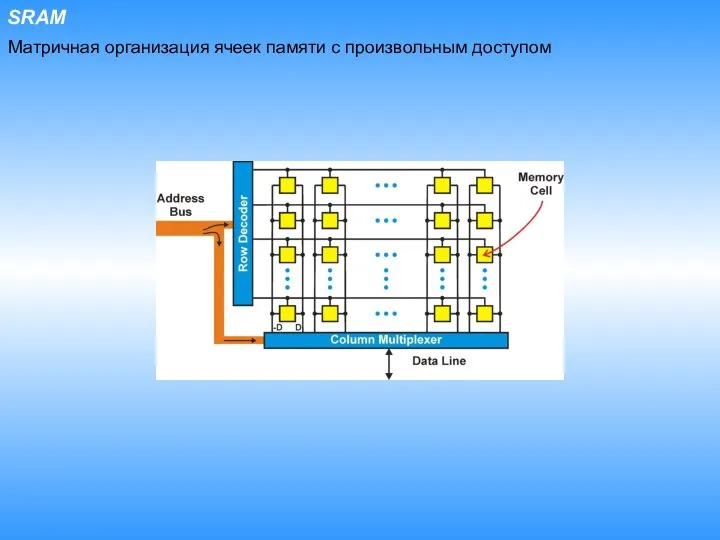

- 14. Матричная организация ячеек памяти с произвольным доступом SRAM

- 15. SRAM Асинхронная Синхронная SRAM

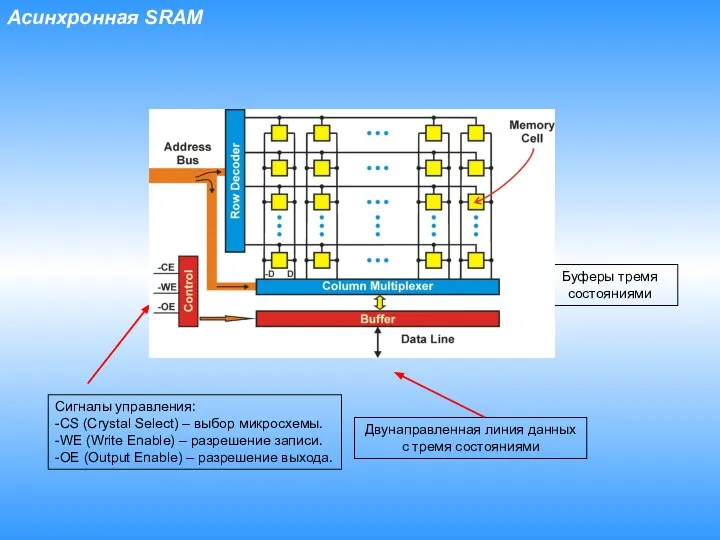

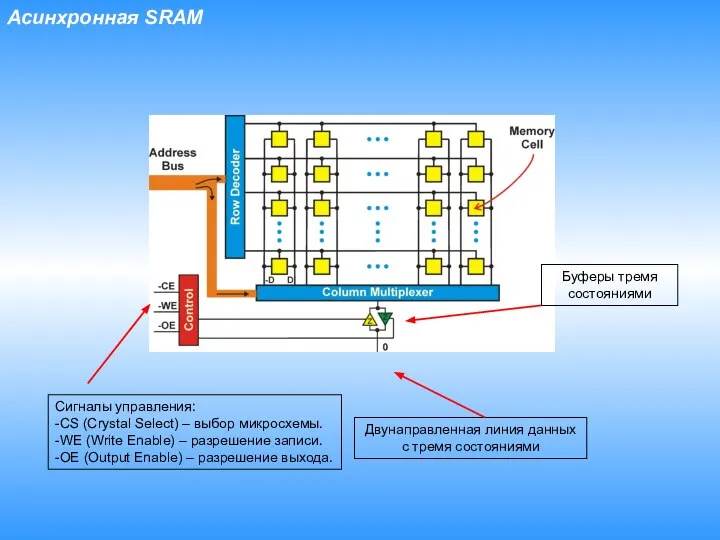

- 16. Сигналы управления: -CS (Crystal Select) – выбор микросхемы. -WE (Write Enable) – разрешение записи. -OE (Output

- 17. Сигналы управления: -CS (Crystal Select) – выбор микросхемы. -WE (Write Enable) – разрешение записи. -OE (Output

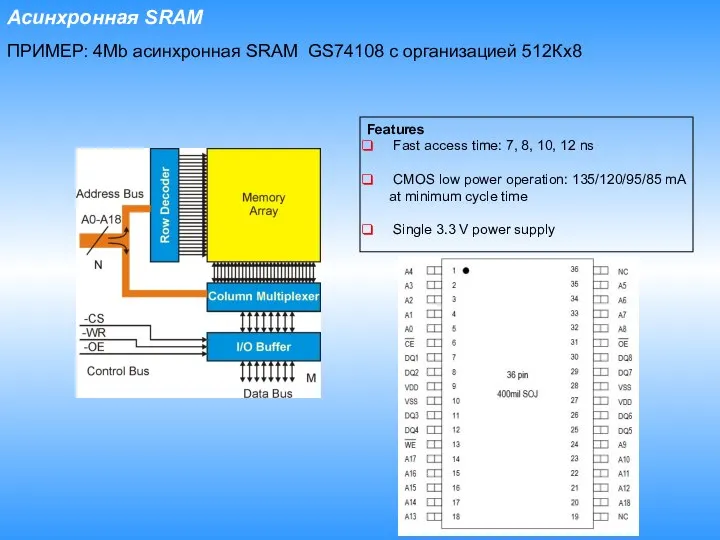

- 18. Features Fast access time: 7, 8, 10, 12 ns CMOS low power operation: 135/120/95/85 mA at

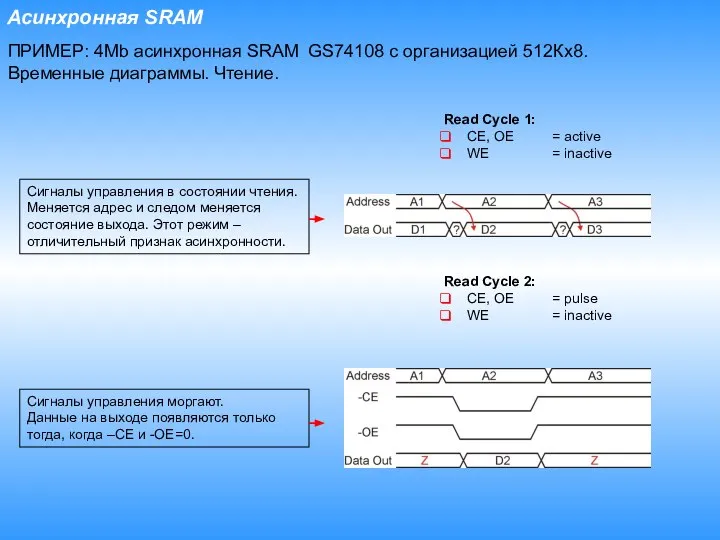

- 19. ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Чтение. Сигналы управления в состоянии чтения.

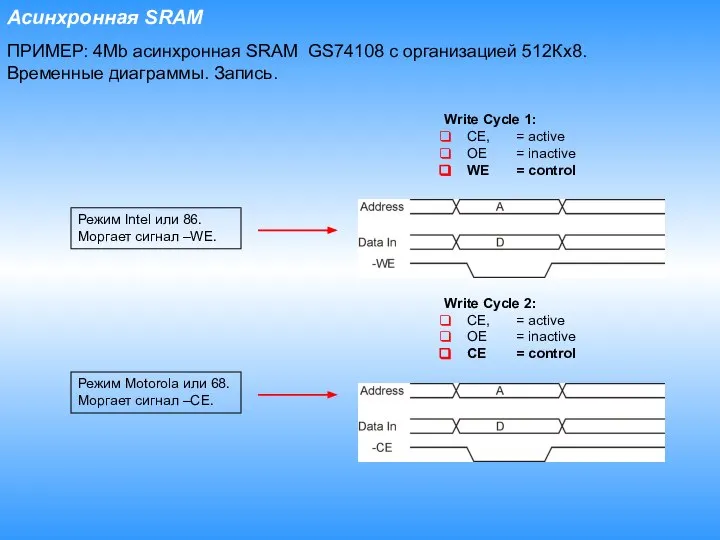

- 20. ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Запись. Режим Intel или 86. Моргает

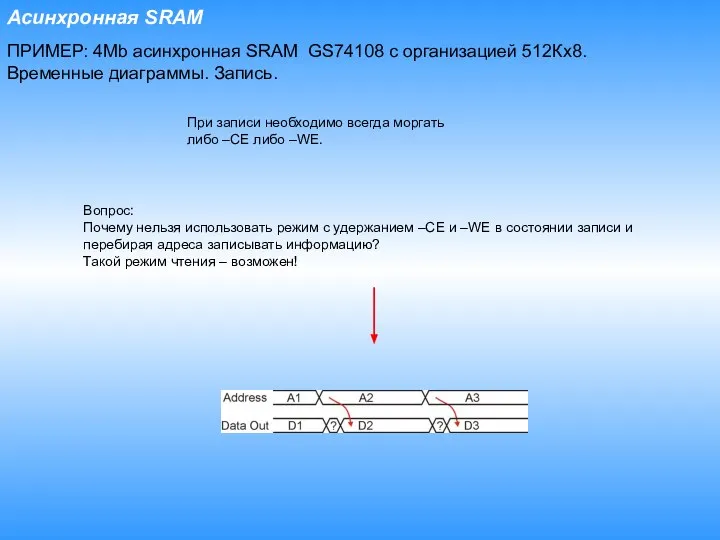

- 21. ПРИМЕР: 4Mb асинхронная SRAM GS74108 с организацией 512Кх8. Временные диаграммы. Запись. Вопрос: Почему нельзя использовать режим

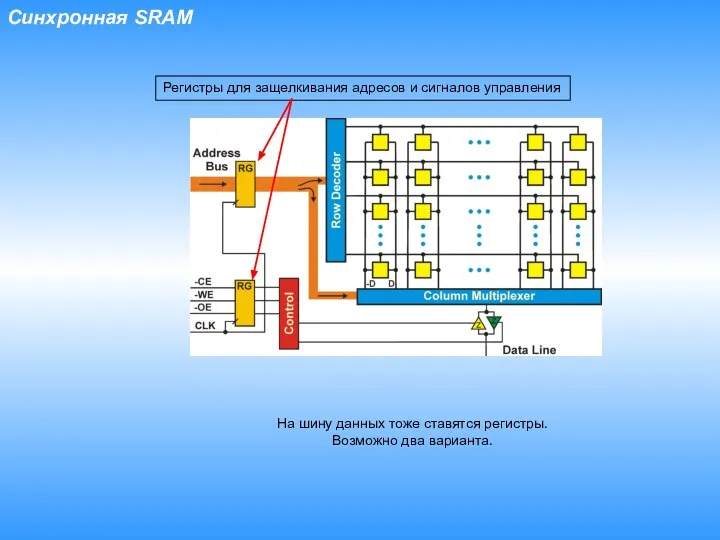

- 22. Регистры для защелкивания адресов и сигналов управления На шину данных тоже ставятся регистры. Возможно два варианта.

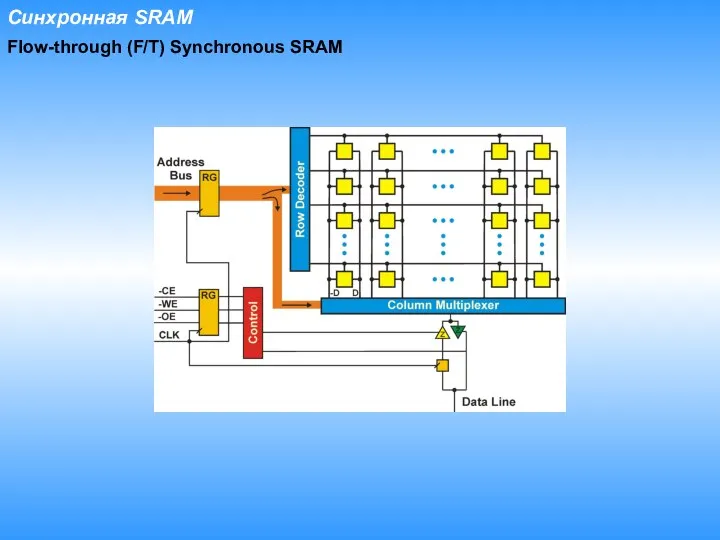

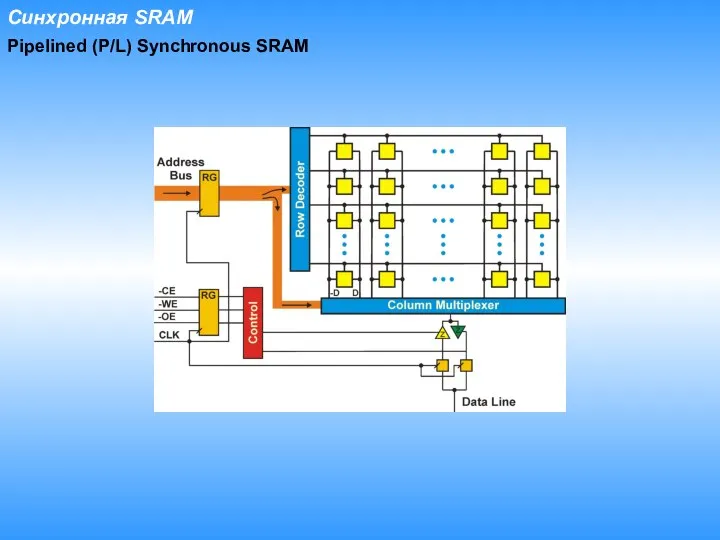

- 23. Flow-through (F/T) Synchronous SRAM Синхронная SRAM

- 24. Pipelined (P/L) Synchronous SRAM Синхронная SRAM

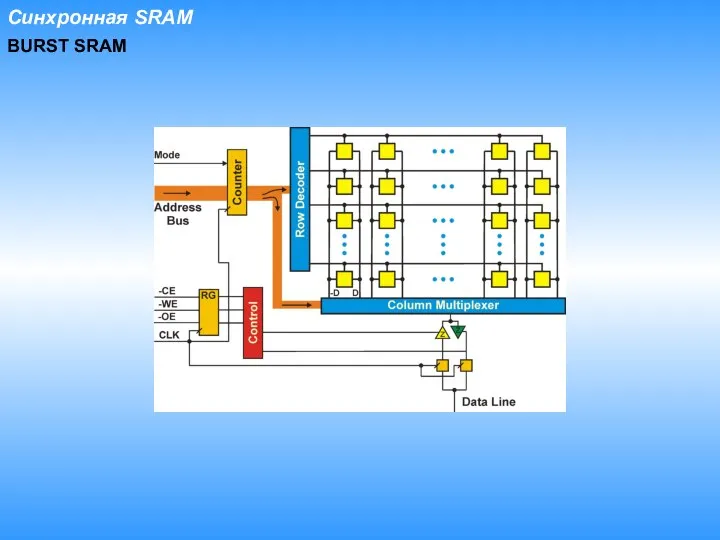

- 25. BURST SRAM Синхронная SRAM

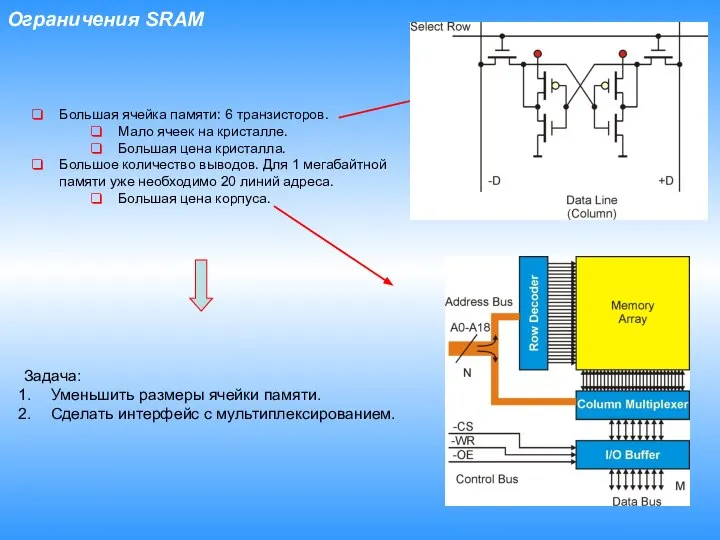

- 26. Ограничения SRAM Большая ячейка памяти: 6 транзисторов. Мало ячеек на кристалле. Большая цена кристалла. Большое количество

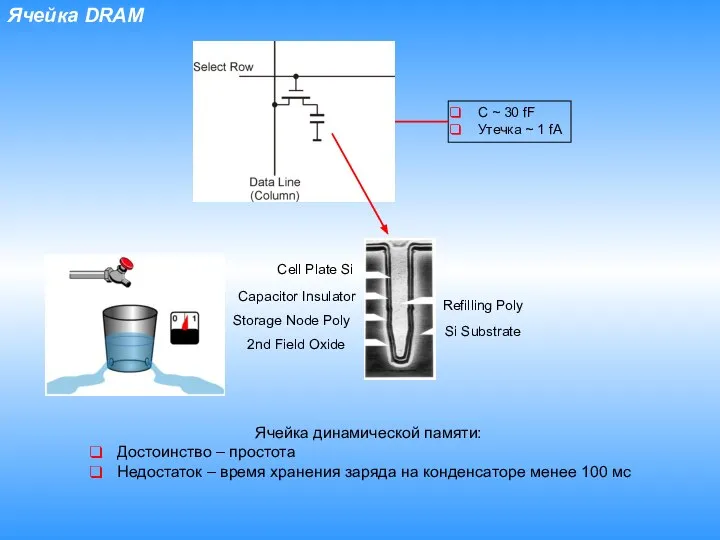

- 27. Ячейка DRAM Ячейка динамической памяти: Достоинство – простота Недостаток – время хранения заряда на конденсаторе менее

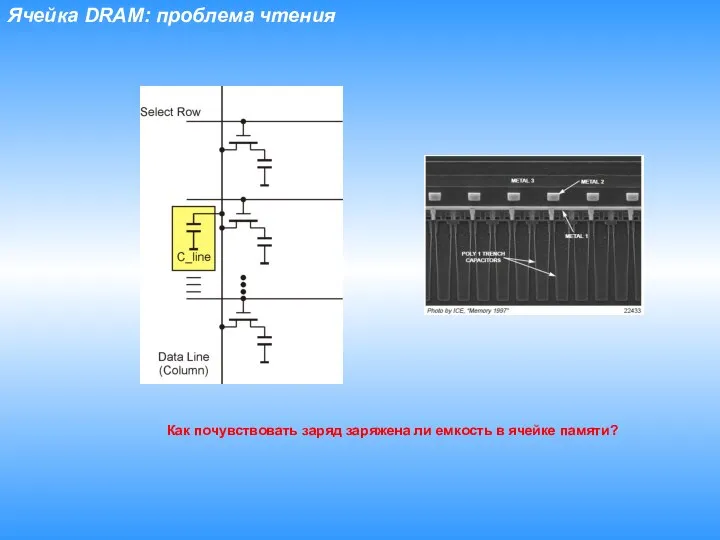

- 28. Ячейка DRAM: проблема чтения Как почувствовать заряд заряжена ли емкость в ячейке памяти?

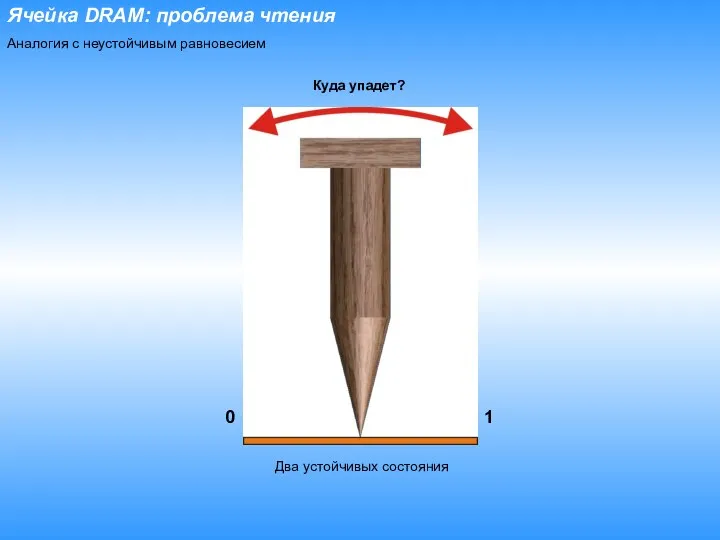

- 29. Ячейка DRAM: проблема чтения Аналогия с неустойчивым равновесием Куда упадет? 0 1 Два устойчивых состояния

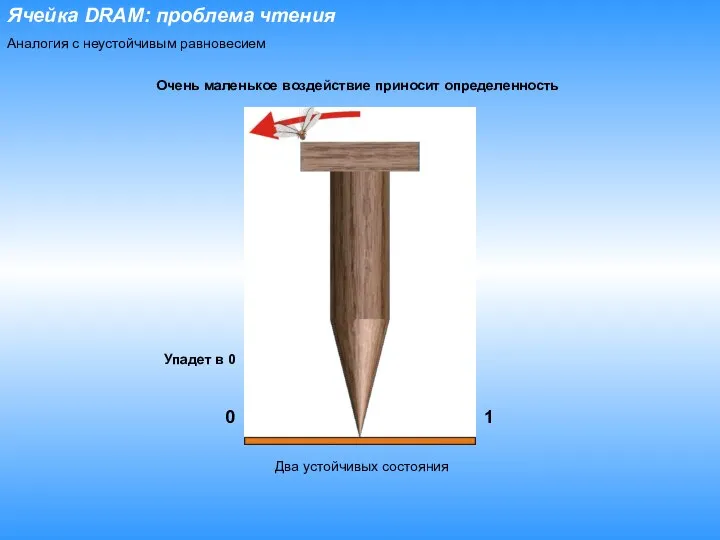

- 30. Ячейка DRAM: проблема чтения Аналогия с неустойчивым равновесием Очень маленькое воздействие приносит определенность 0 1 Два

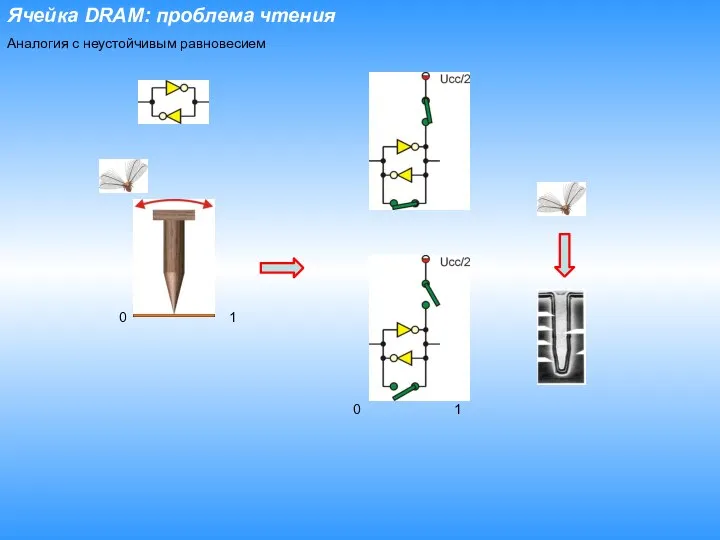

- 31. Ячейка DRAM: проблема чтения Аналогия с неустойчивым равновесием 0 1 0 1

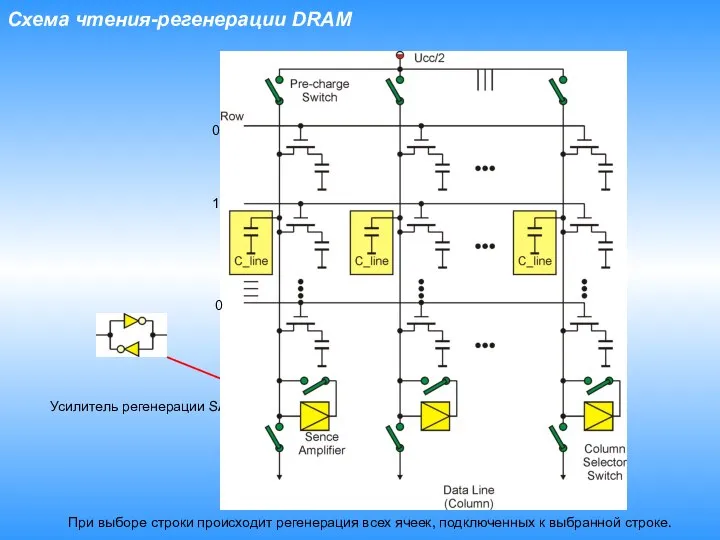

- 32. Схема чтения-регенерации DRAM Усилитель регенерации SA При выборе строки происходит регенерация всех ячеек, подключенных к выбранной

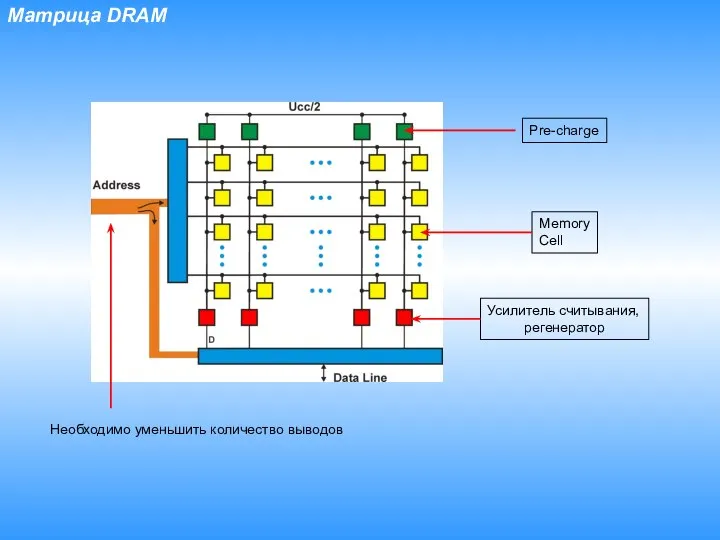

- 33. Матрица DRAM Необходимо уменьшить количество выводов Pre-charge Memory Cell Усилитель считывания, регенератор

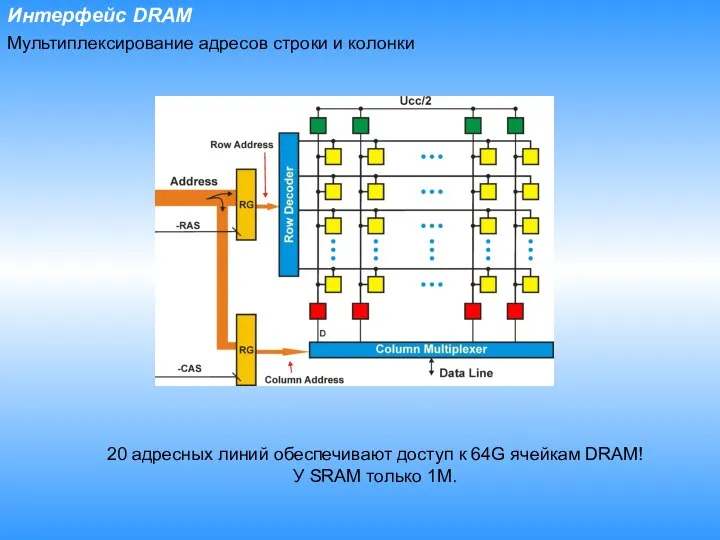

- 34. Интерфейс DRAM Мультиплексирование адресов строки и колонки 20 адресных линий обеспечивают доступ к 64G ячейкам DRAM!

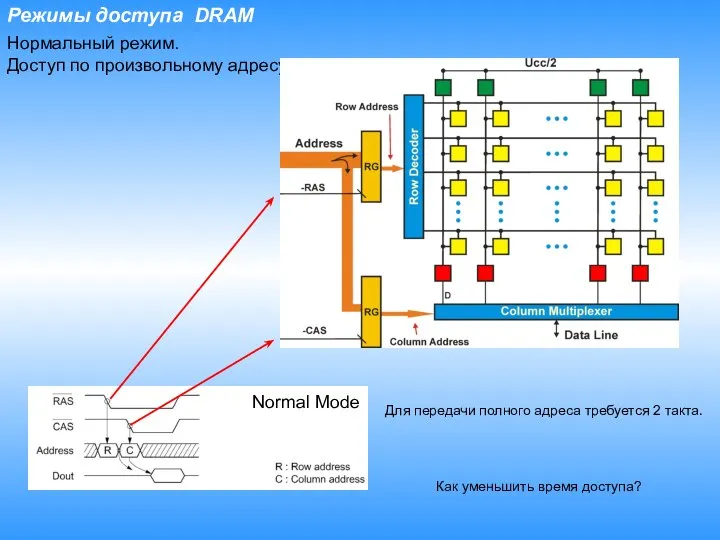

- 35. Режимы доступа DRAM Нормальный режим. Доступ по произвольному адресу. Normal Mode Для передачи полного адреса требуется

- 36. Режимы доступа DRAM Режим быстрого доступа внутри строки. Fast Page Mode. Вначале полный доступ по произвольному

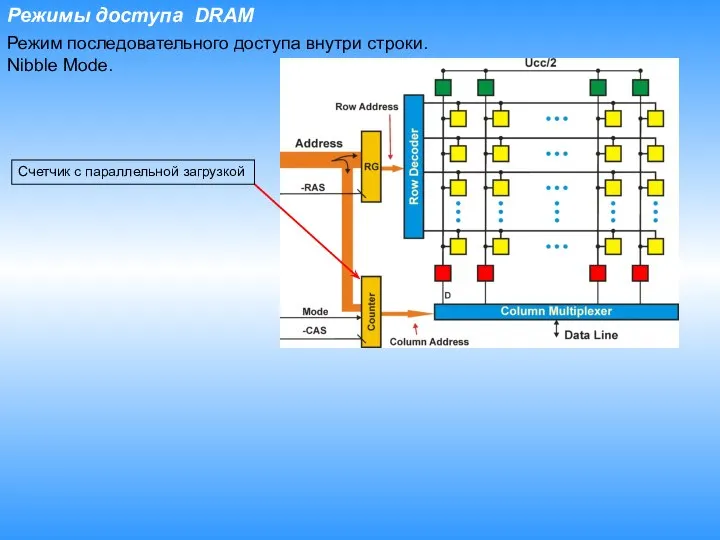

- 37. Режимы доступа DRAM Режим последовательного доступа внутри строки. Nibble Mode. Счетчик с параллельной загрузкой

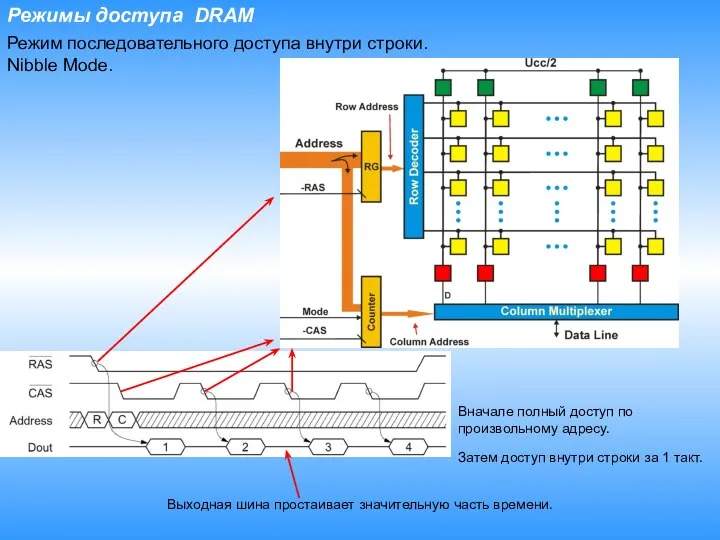

- 38. Режимы доступа DRAM Режим последовательного доступа внутри строки. Nibble Mode. Вначале полный доступ по произвольному адресу.

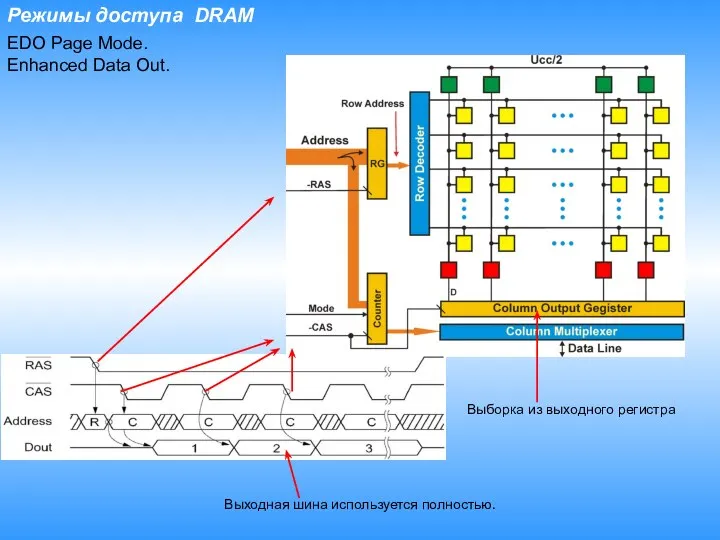

- 39. Режимы доступа DRAM EDO Page Mode. Enhanced Data Out. Выходная шина используется полностью. Выборка из выходного

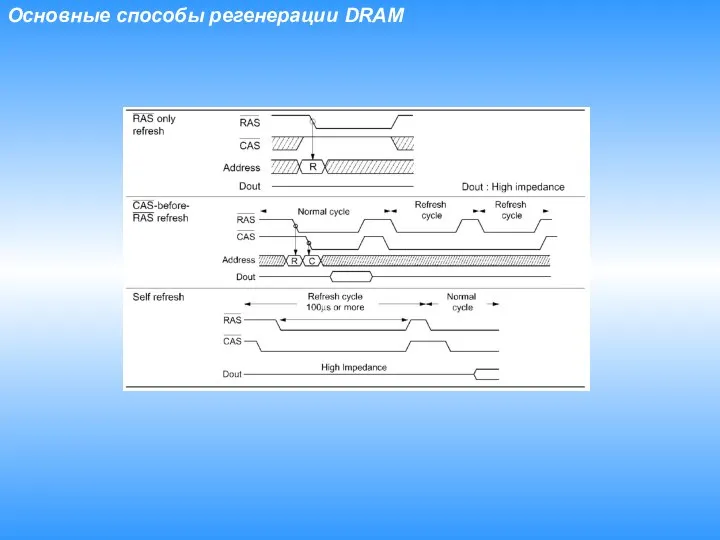

- 40. Основные способы регенерации DRAM

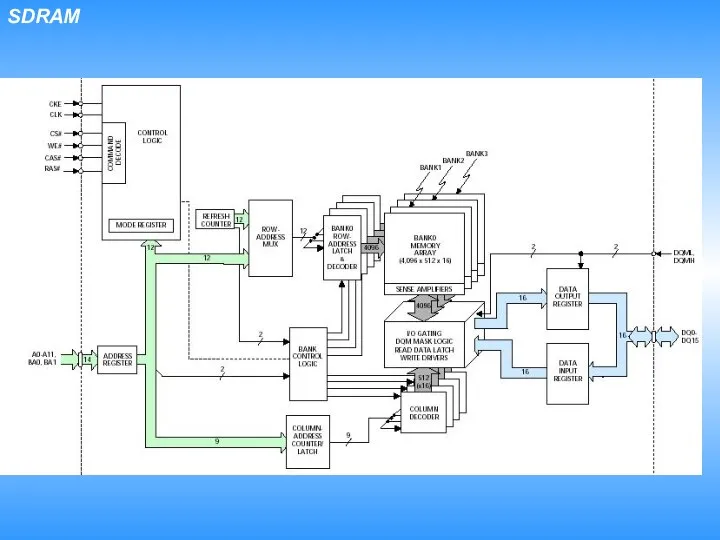

- 41. SDRAM

- 43. Скачать презентацию

![Характеристики памяти Общие характеристики Объем [bit] Быстродействие Энергозависимость Стоимость Плотность [bit/sm3]](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1468500/slide-2.jpg)

Презентация Платежный баланс России

Презентация Платежный баланс России Пантеон славянских богов. Дажьбог

Пантеон славянских богов. Дажьбог CЛУЧАЙ И МАТЕМАТИКА

CЛУЧАЙ И МАТЕМАТИКА  Эпоха Возрождения

Эпоха Возрождения Теория вероятности и математическая статистика

Теория вероятности и математическая статистика  Права на результаты интеллектуальной деятельности и средства индивидуализации

Права на результаты интеллектуальной деятельности и средства индивидуализации Ваш ребёнок идет в школу Советы и рекомендации родителям будущих первоклассников, а так же ответы на часто задаваемые вопросы.

Ваш ребёнок идет в школу Советы и рекомендации родителям будущих первоклассников, а так же ответы на часто задаваемые вопросы. Экосистема цифрового мобильного контента

Экосистема цифрового мобильного контента Ведение воинского учета

Ведение воинского учета Научные традиции и научные революции

Научные традиции и научные революции  Смена имени

Смена имени Ферменты

Ферменты  Лабиринтит. ЭТИОЛОГИЯ. КЛИНИКА. ЛЕЧЕНИЕ.

Лабиринтит. ЭТИОЛОГИЯ. КЛИНИКА. ЛЕЧЕНИЕ. Лесное испытание

Лесное испытание Духовная жизнь советского общества

Духовная жизнь советского общества  Сущность и виды административного процесса

Сущность и виды административного процесса 15 декабря - Международный день чая

15 декабря - Международный день чая ИСПОЛЬЗОВАНИЕ ПОЛИГРАФА

ИСПОЛЬЗОВАНИЕ ПОЛИГРАФА Преступления против здоровья населения и общественной нравственности (ст. 228-245 УК РФ)

Преступления против здоровья населения и общественной нравственности (ст. 228-245 УК РФ) Динамика информационного потока по проблеме производства изотопов 99Mo и 99mTc для ядерной медицины

Динамика информационного потока по проблеме производства изотопов 99Mo и 99mTc для ядерной медицины  Персик

Персик Презентация на тему "Реализация проекта «Школа успешного ученика»" - скачать презентации по Педагогике

Презентация на тему "Реализация проекта «Школа успешного ученика»" - скачать презентации по Педагогике Стили и направления зарубежного изобразительного искусства

Стили и направления зарубежного изобразительного искусства Симметрия в природе

Симметрия в природе Презентация Колбасы

Презентация Колбасы Школа 21 века (Парфенова О.Ю.

Школа 21 века (Парфенова О.Ю. Формирующая оценка. Роль учителя в оценке качества предоставляемых образовательных услуг. 15.11.2011г ст. препод. каф. управления Е

Формирующая оценка. Роль учителя в оценке качества предоставляемых образовательных услуг. 15.11.2011г ст. препод. каф. управления Е Комуністична партія України

Комуністична партія України