Содержание

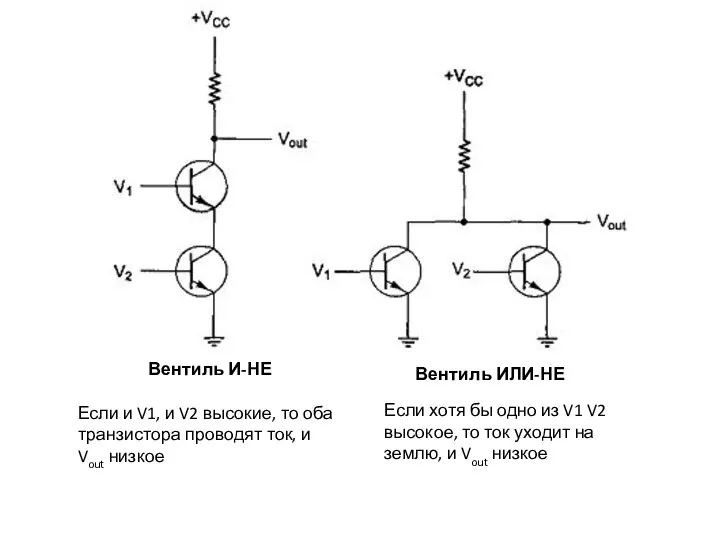

- 2. Вентиль И-НЕ Если и V1, и V2 высокие, то оба транзистора проводят ток, и Vout низкое

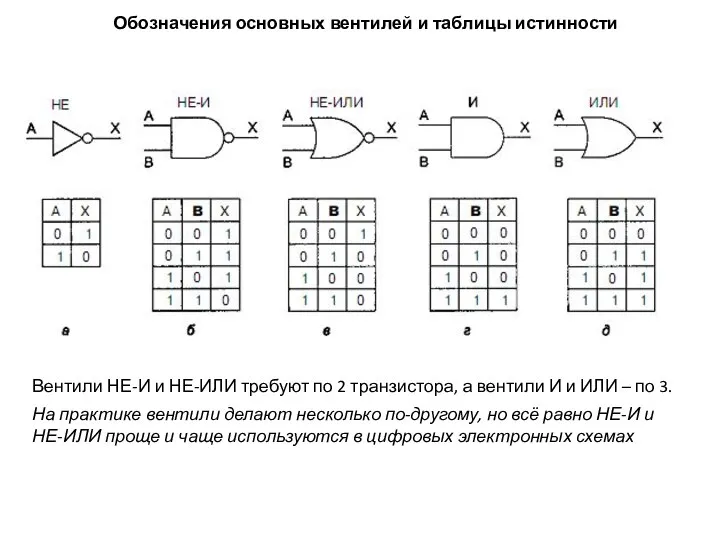

- 3. Обозначения основных вентилей и таблицы истинности Вентили НЕ-И и НЕ-ИЛИ требуют по 2 транзистора, а вентили

- 4. Классификация технологий производства вентилей Биполярная - ТТЛ (транзисторно-транзисторная логика) - ЭСЛ (эмиттерно-связанная логика) – более высокая

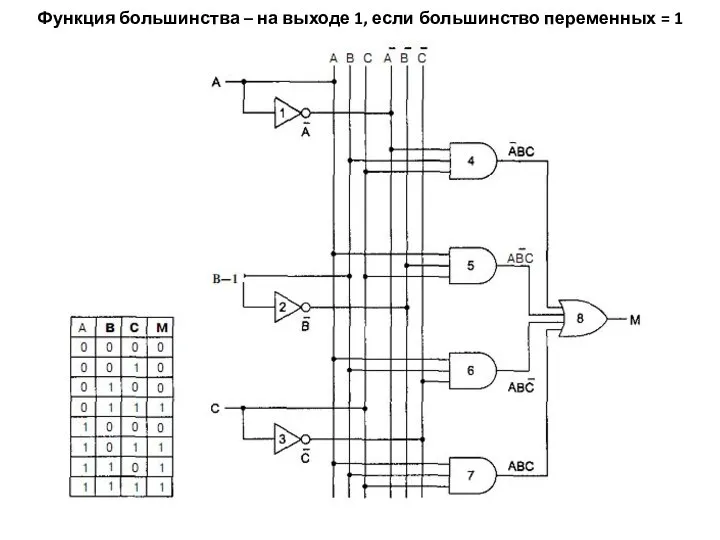

- 5. Функция большинства – на выходе 1, если большинство переменных = 1

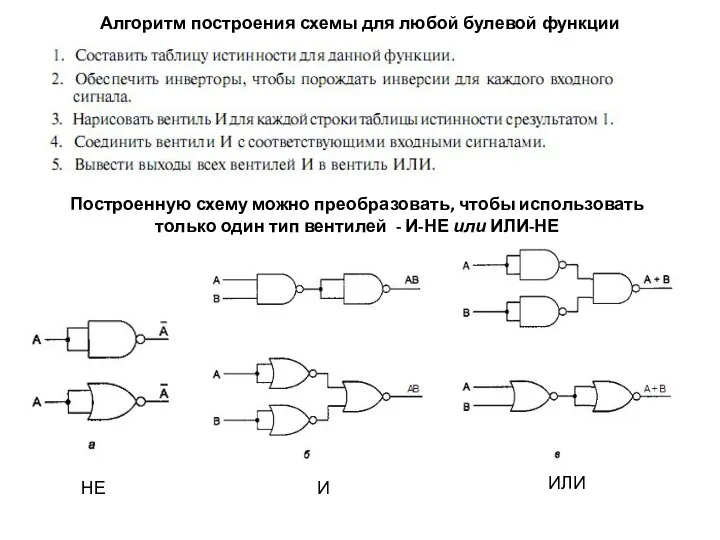

- 6. Алгоритм построения схемы для любой булевой функции Построенную схему можно преобразовать, чтобы использовать только один тип

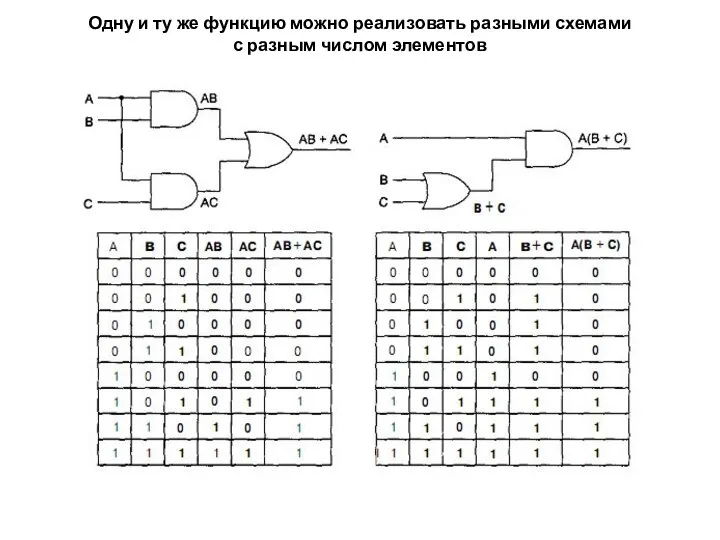

- 7. Одну и ту же функцию можно реализовать разными схемами с разным числом элементов

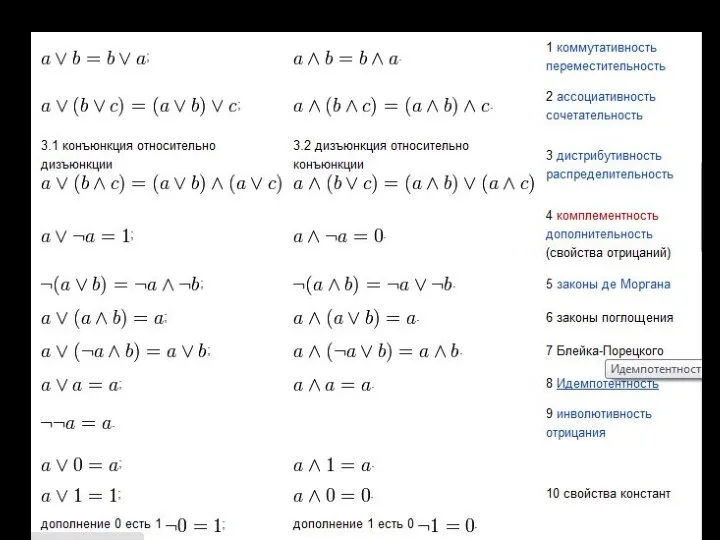

- 8. Для минимизации булевых функций используются законы булевой алгебры

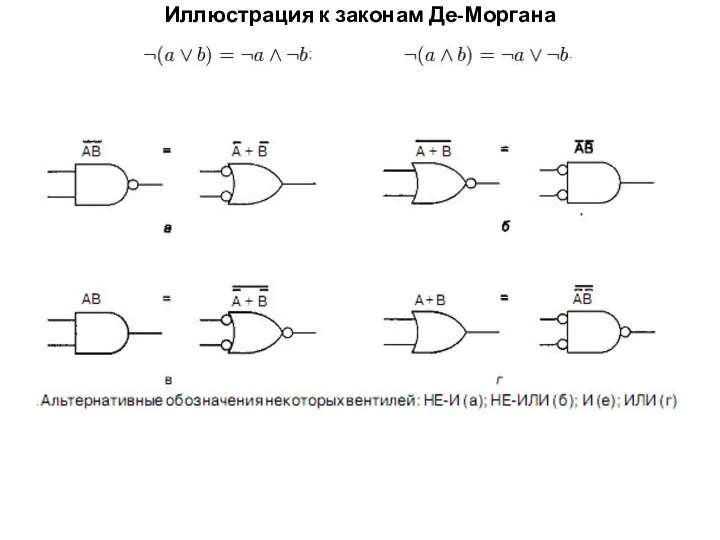

- 9. Иллюстрация к законам Де-Моргана

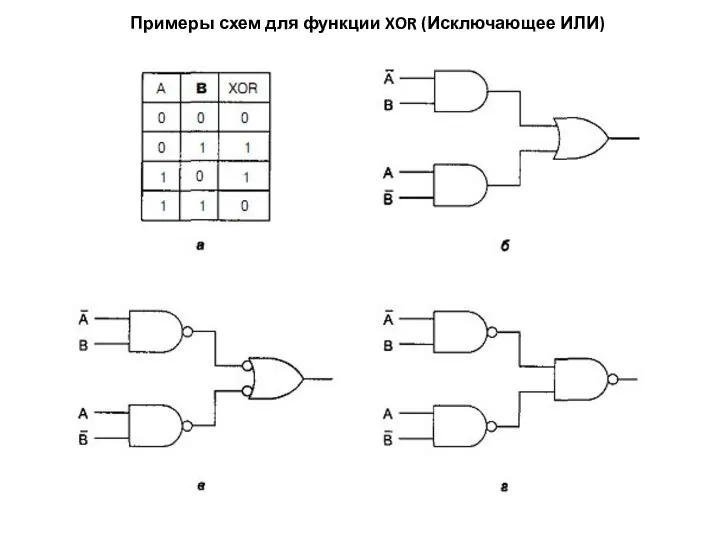

- 10. Примеры схем для функции XOR (Исключающее ИЛИ)

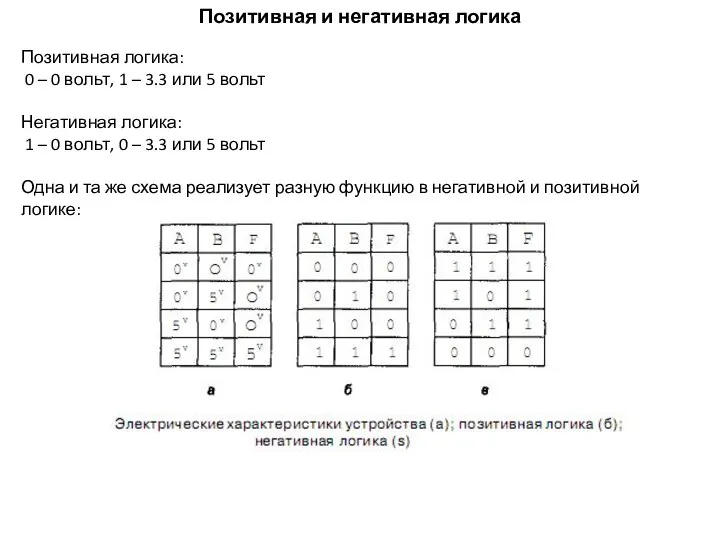

- 11. Позитивная и негативная логика Позитивная логика: 0 – 0 вольт, 1 – 3.3 или 5 вольт

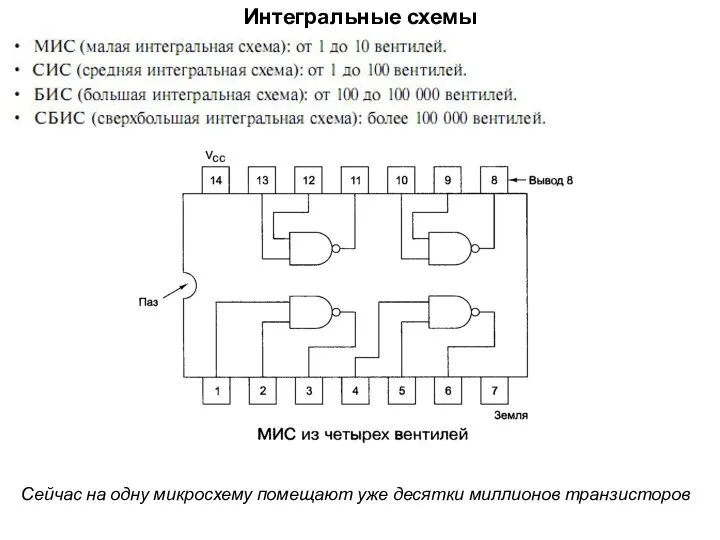

- 12. Интегральные схемы Сейчас на одну микросхему помещают уже десятки миллионов транзисторов

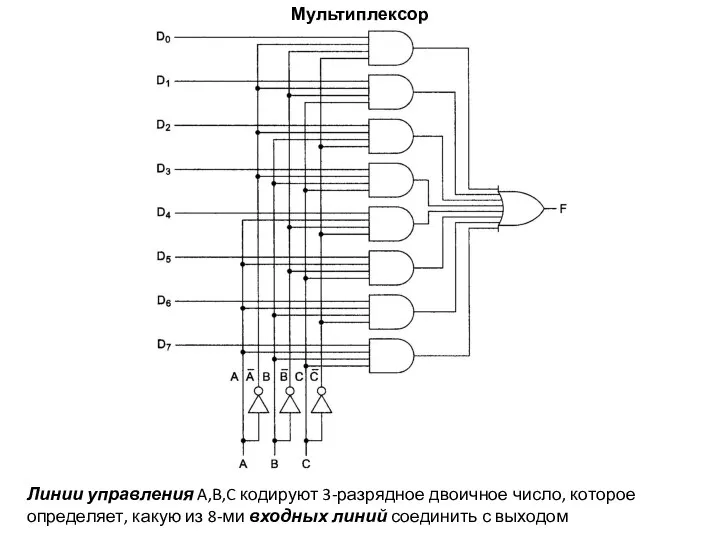

- 13. Мультиплексор Линии управления A,B,C кодируют 3-разрядное двоичное число, которое определяет, какую из 8-ми входных линий соединить

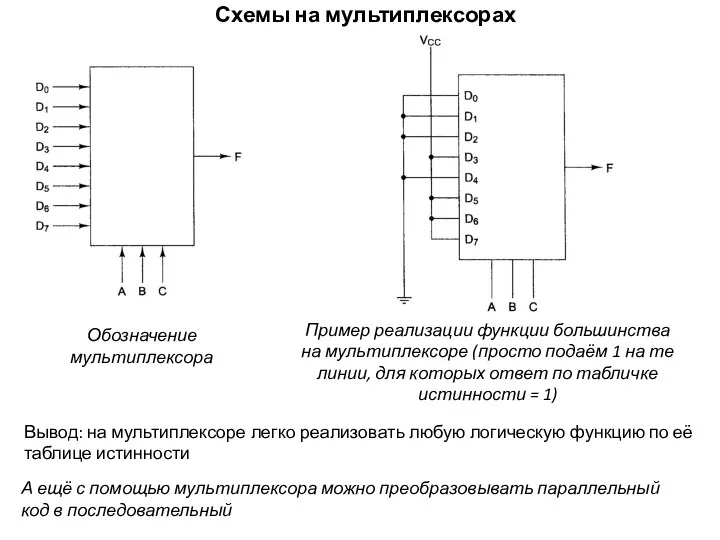

- 14. Схемы на мультиплексорах Обозначение мультиплексора Пример реализации функции большинства на мультиплексоре (просто подаём 1 на те

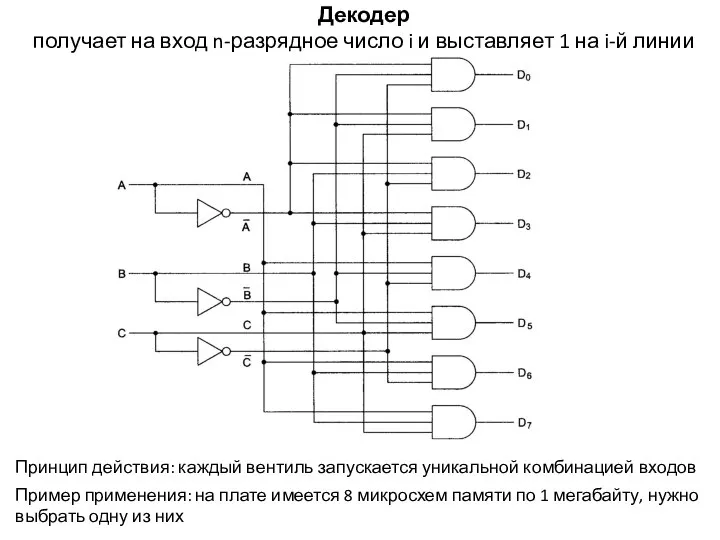

- 15. Декодер получает на вход n-разрядное число i и выставляет 1 на i-й линии Принцип действия: каждый

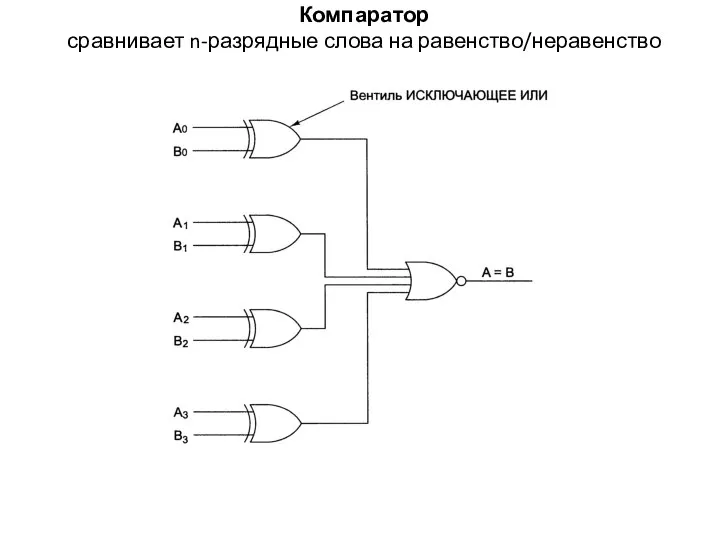

- 16. Компаратор сравнивает n-разрядные слова на равенство/неравенство

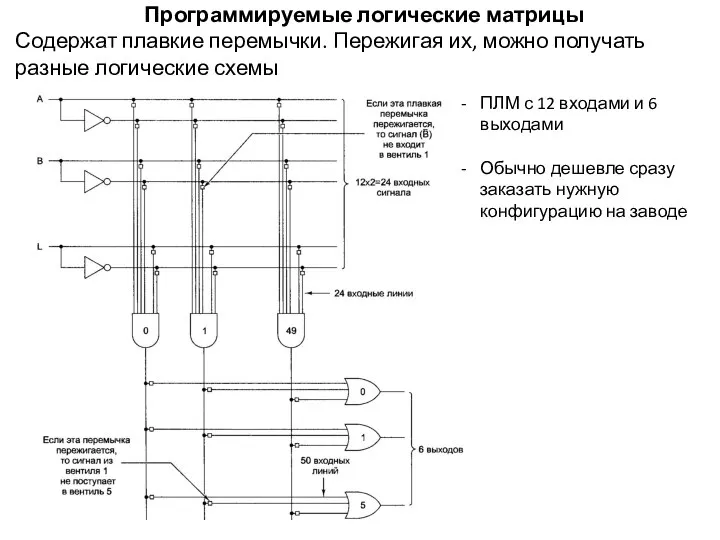

- 17. Программируемые логические матрицы Содержат плавкие перемычки. Пережигая их, можно получать разные логические схемы ПЛМ с 12

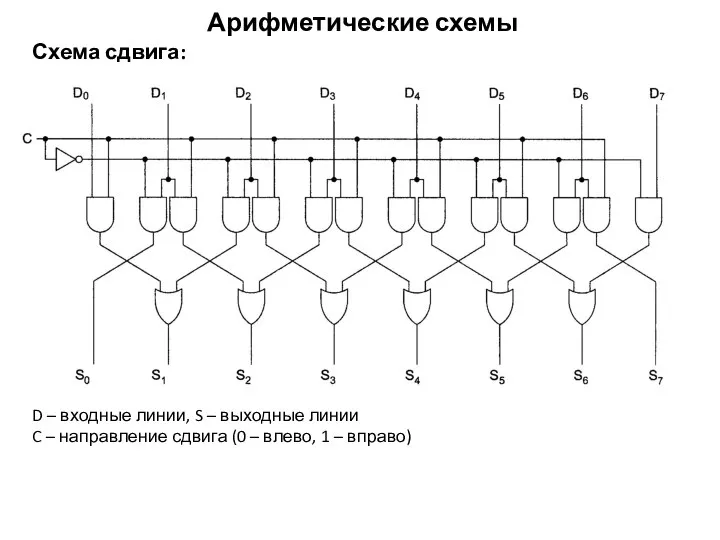

- 18. Арифметические схемы Схема сдвига: D – входные линии, S – выходные линии C – направление сдвига

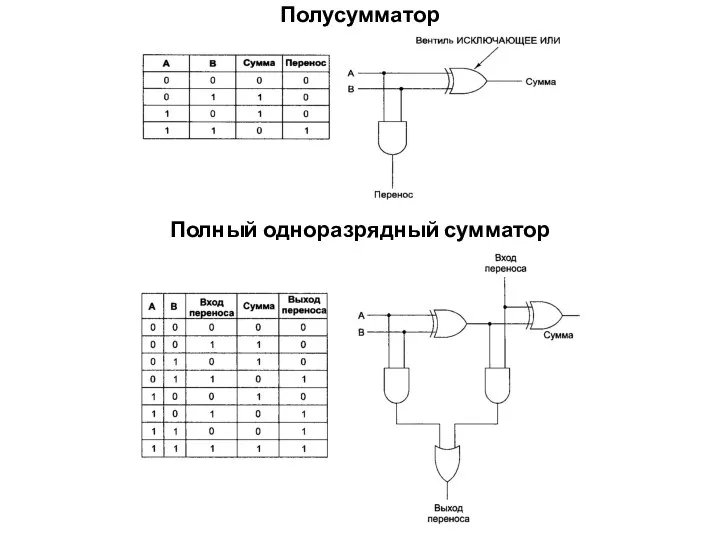

- 19. Полусумматор Полный одноразрядный сумматор

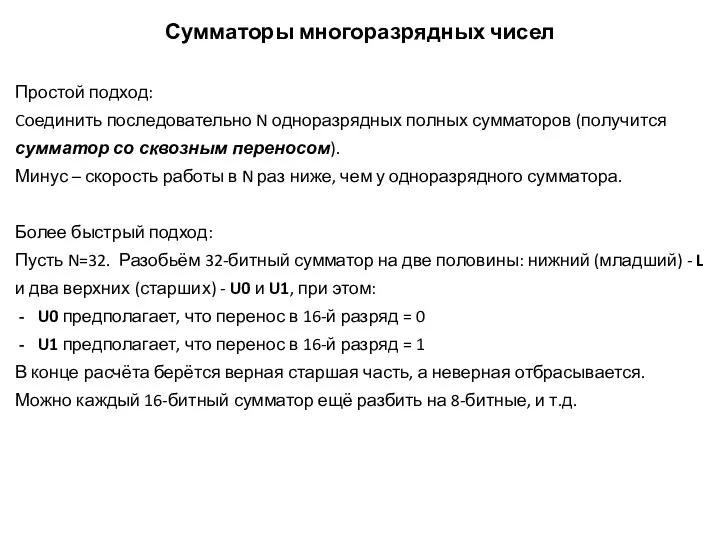

- 20. Сумматоры многоразрядных чисел Простой подход: Cоединить последовательно N одноразрядных полных сумматоров (получится сумматор со сквозным переносом).

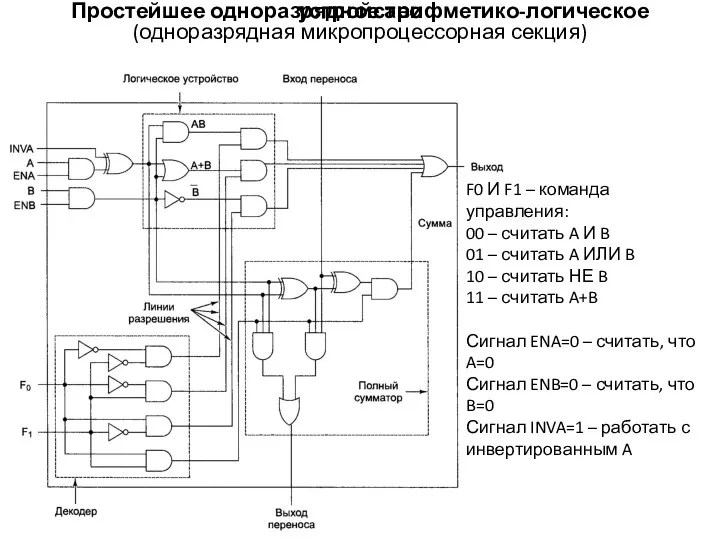

- 21. Простейшее одноразрядное арифметико-логическое устройство (одноразрядная микропроцессорная секция) F0 И F1 – команда управления: 00 – считать

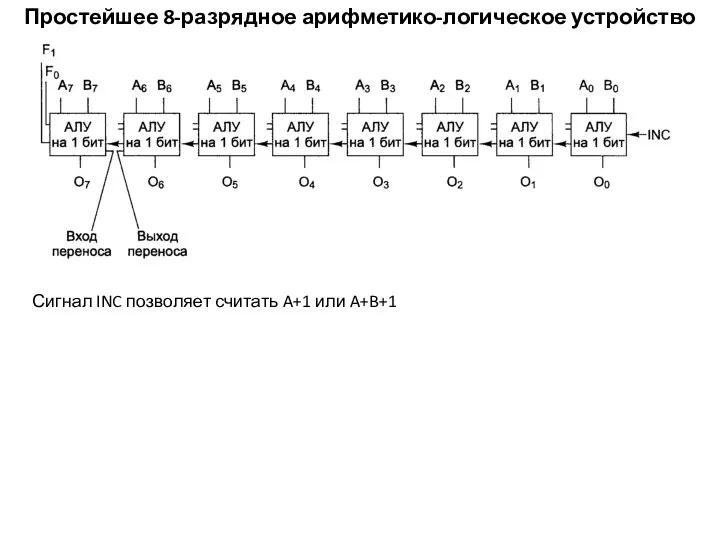

- 22. Простейшее 8-разрядное арифметико-логическое устройство Сигнал INC позволяет считать A+1 или A+B+1

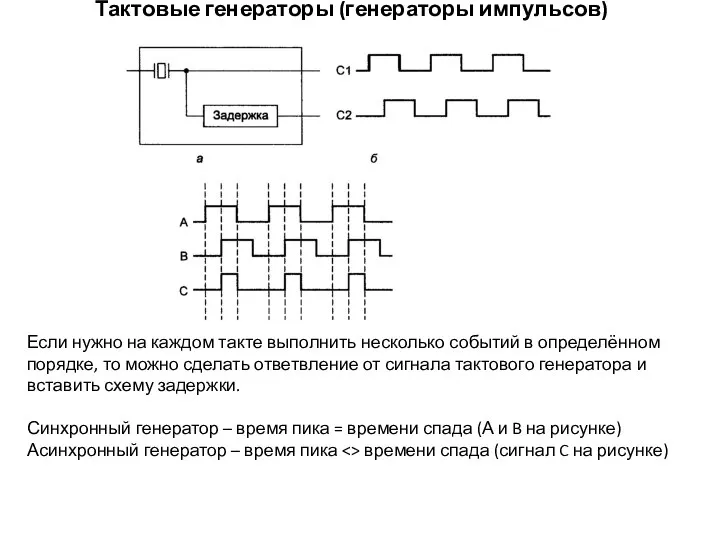

- 23. Тактовые генераторы (генераторы импульсов) Если нужно на каждом такте выполнить несколько событий в определённом порядке, то

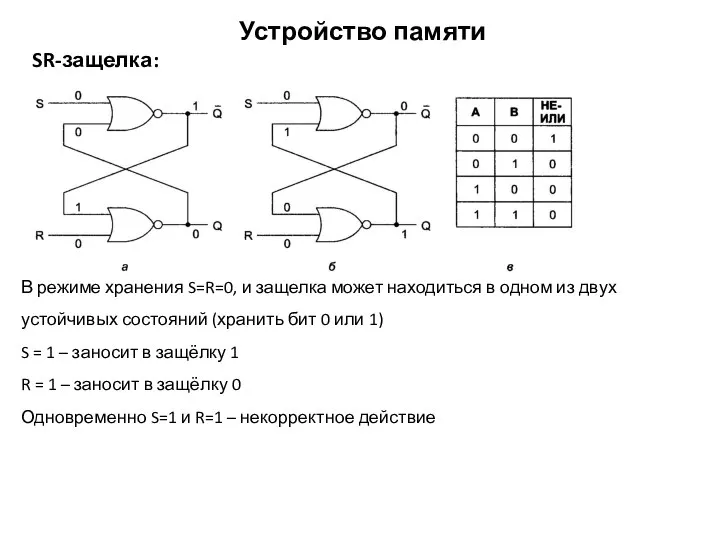

- 24. Устройство памяти SR-защелка: В режиме хранения S=R=0, и защелка может находиться в одном из двух устойчивых

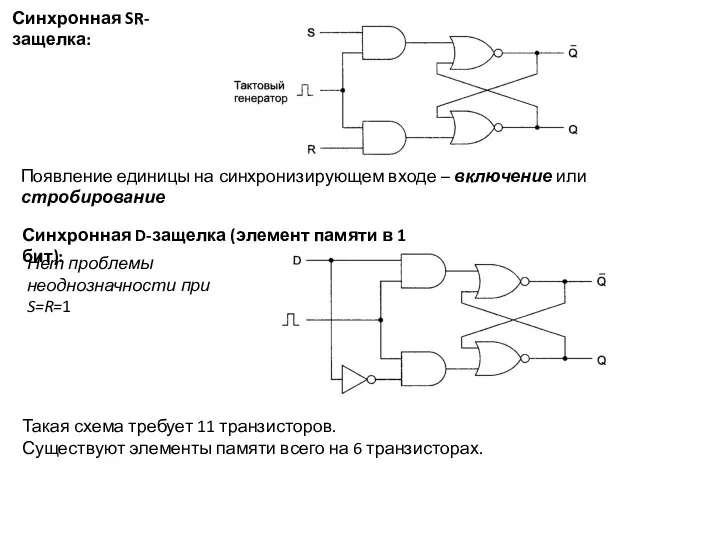

- 25. Синхронная SR-защелка: Появление единицы на синхронизирующем входе – включение или стробирование Синхронная D-защелка (элемент памяти в

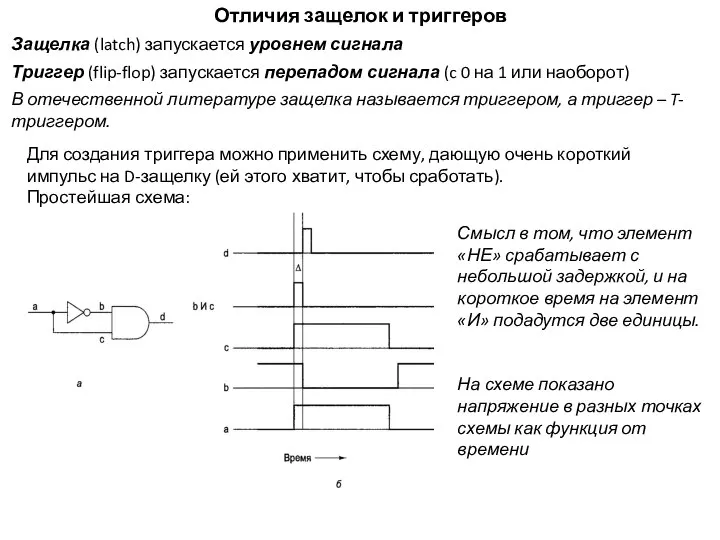

- 26. Отличия защелок и триггеров Защелка (latch) запускается уровнем сигнала Триггер (flip-flop) запускается перепадом сигнала (c 0

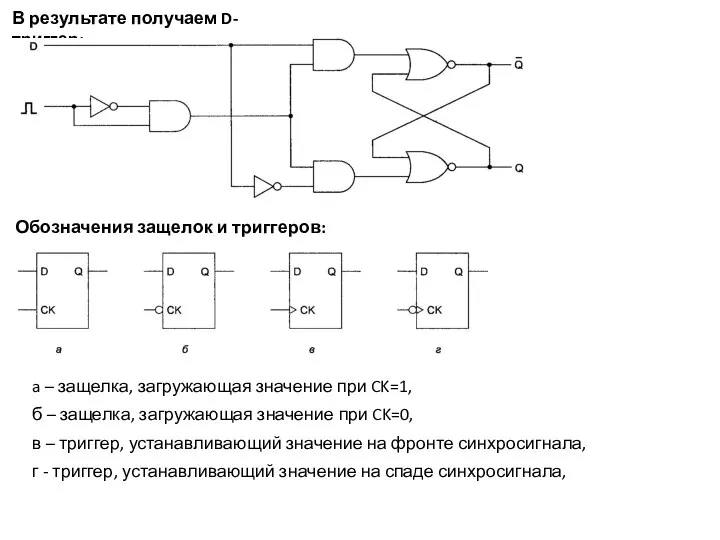

- 27. В результате получаем D-триггер: Обозначения защелок и триггеров: a – защелка, загружающая значение при CK=1, б

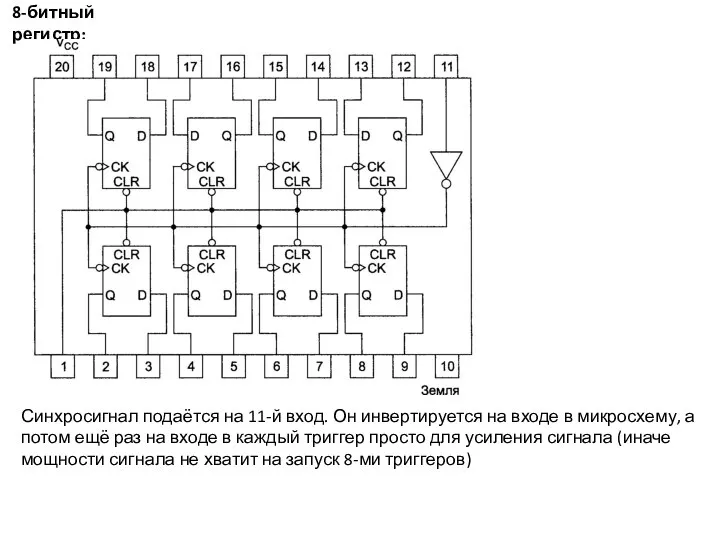

- 28. 8-битный регистр: Синхросигнал подаётся на 11-й вход. Он инвертируется на входе в микросхему, а потом ещё

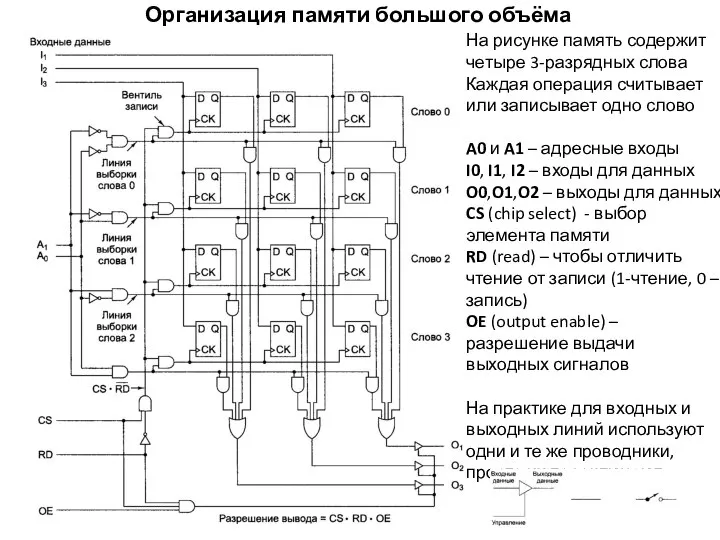

- 29. Организация памяти большого объёма На рисунке память содержит четыре 3-разрядных слова Каждая операция считывает или записывает

- 31. Скачать презентацию

Эволюция иммунной системы

Эволюция иммунной системы Архитектура ЭВМ

Архитектура ЭВМ Предмет и методы изучения морфологии

Предмет и методы изучения морфологии SADT

SADT Ортағасырлардағы Шығыс пен Батыстағы коллекциялау

Ортағасырлардағы Шығыс пен Батыстағы коллекциялау Составляющие тренированности организма человека

Составляющие тренированности организма человека основы ЛФК

основы ЛФК Контент-аналіз веб-серіалу Mr.Freeman

Контент-аналіз веб-серіалу Mr.Freeman Программа «Беги за мной. Богучанский район»

Программа «Беги за мной. Богучанский район» Духовная культура

Духовная культура Наша мова. (Тэма 1)

Наша мова. (Тэма 1) Презентация "Адаптированная Теория Ограничений" - скачать презентации по Экономике

Презентация "Адаптированная Теория Ограничений" - скачать презентации по Экономике Творческое планирование для творческого человека. Запись он-лайн курса с реальной группой

Творческое планирование для творческого человека. Запись он-лайн курса с реальной группой ЭКСПЕРТИЗА МЁДА

ЭКСПЕРТИЗА МЁДА Проект некапитальных торговых объектов для размещения на территории ТЦ «Заречье»

Проект некапитальных торговых объектов для размещения на территории ТЦ «Заречье» Южный федеральный округ Выполнили студенты 4 курса Группы Т-096 Шаповалова, Исаева,Рулев

Южный федеральный округ Выполнили студенты 4 курса Группы Т-096 Шаповалова, Исаева,Рулев  Учет отдельных факторов в уравнении материального баланса

Учет отдельных факторов в уравнении материального баланса Всемирное культурное наследие России

Всемирное культурное наследие России Тайны Тибета

Тайны Тибета Система текущей и промежуточной аттестации обучающихся в общеобразовательных учреждениях (инновационные подходы)

Система текущей и промежуточной аттестации обучающихся в общеобразовательных учреждениях (инновационные подходы) Простагландины

Простагландины Возникновение русского языка

Возникновение русского языка Геополитические конструкции накануне ВМВ

Геополитические конструкции накануне ВМВ Прямые и портфельные инвестиции Выполнили студентки группы Т-116 Хропина Ольга и Фунтикова Виктория

Прямые и портфельные инвестиции Выполнили студентки группы Т-116 Хропина Ольга и Фунтикова Виктория  Презентация ТЕОРИЯ ГЛАСИЕР

Презентация ТЕОРИЯ ГЛАСИЕР Система технического обслуживания и ремонта оборудования

Система технического обслуживания и ремонта оборудования Порядок проведения предварительного слушания в суде с участием присяжных заседателей

Порядок проведения предварительного слушания в суде с участием присяжных заседателей Принципы объектно-ориентированного программирования

Принципы объектно-ориентированного программирования