Содержание

- 2. Пояснения к схеме OR: положительный импульс на выходе возникает при появлении положительного импульса на любом {а,

- 3. На рис. 6.8 показана схема NOT (НЕ) на полевых КМОП-транзисторах транзисторно-транзисторной технологии. Пояснение к схеме NOT:

- 6. Триггер Если триггер находится в состоянии «О», то у него на выходе q «высокое» напряжение (порядка

- 9. jk и счётный ( Т – триггер) Прежде чем начать изучение jk триггера, вспомним принципы работы

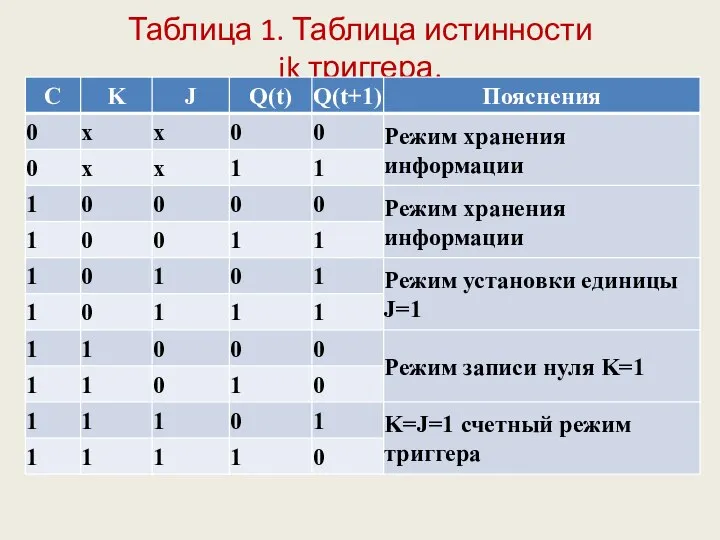

- 10. Таблица 1. Таблица истинности jk триггера.

- 11. Один из вариантов внутренней схемы JK-триггера приведен на рисунке 1. Рис. 1. Внутренняя схема jk триггера

- 17. Скачать презентацию

Слайд 2

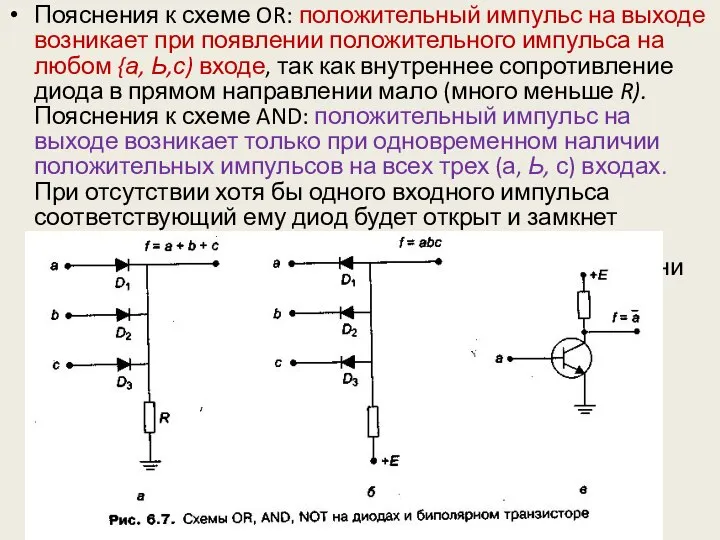

Пояснения к схеме OR: положительный импульс на выходе возникает при появлении

Пояснения к схеме OR: положительный импульс на выходе возникает при появлении

положительного импульса на любом {а, Ь,с) входе, так как внутреннее сопротивление диода в прямом направлении мало (много меньше R). Пояснения к схеме AND: положительный импульс на выходе возникает только при одновременном наличии положительных импульсов на всех трех (а, Ь, с) входах. При отсутствии хотя бы одного входного импульса соответствующий ему диод будет открыт и замкнет питающее напряжение +Е через внутренние сопротивления диода и источника входного сигнала (они много меньше R) на «землю».

Слайд 3

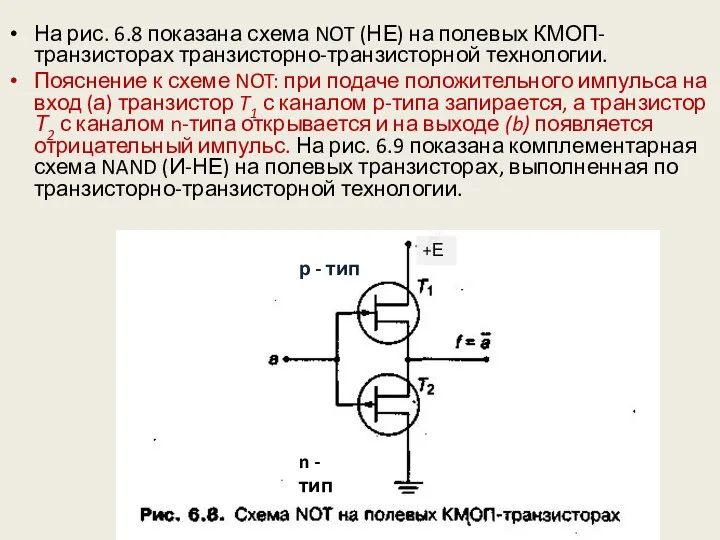

На рис. 6.8 показана схема NOT (НЕ) на полевых КМОП-транзисторах транзисторно-транзисторной

На рис. 6.8 показана схема NOT (НЕ) на полевых КМОП-транзисторах транзисторно-транзисторной

технологии.

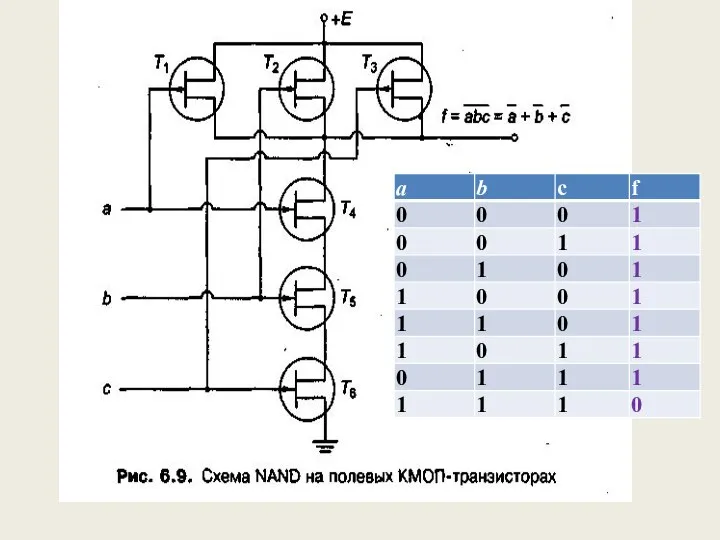

Пояснение к схеме NOT: при подаче положительного импульса на вход (а) транзистор T1 с каналом р-типа запирается, а транзистор Т2 с каналом n-типа открывается и на выходе (b) появляется отрицательный импульс. На рис. 6.9 показана комплементарная схема NAND (И-НЕ) на полевых транзисторах, выполненная по транзисторно-транзисторной технологии.

Пояснение к схеме NOT: при подаче положительного импульса на вход (а) транзистор T1 с каналом р-типа запирается, а транзистор Т2 с каналом n-типа открывается и на выходе (b) появляется отрицательный импульс. На рис. 6.9 показана комплементарная схема NAND (И-НЕ) на полевых транзисторах, выполненная по транзисторно-транзисторной технологии.

+Е

р - тип

n - тип

Слайд 4

Слайд 5

Слайд 6

Триггер

Если триггер находится в состоянии «О», то у него на выходе

Триггер

Если триггер находится в состоянии «О», то у него на выходе

q «высокое» напряжение (порядка нескольких вольт или даже меньше), на выходе q «низкое» (обычно нулевое) напряжение, если триггер находится в состоянии «О», то напряжения распределены наоборот.

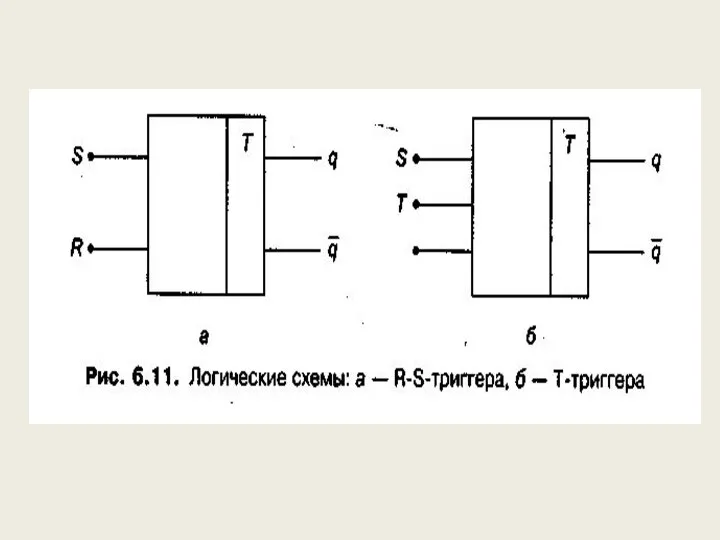

Триггера могут иметь раздельные входы:

R (Reset) — вход установки «О»;

S (Set) — вход установки «1».

Каждый вход устанавливает триггер в соответствующее состояние, такие триггеры часто называют R-S-триггерами.

Триггеры могут иметь счетный вход Т (toggle, релаксатор), очередной импульс «1» на счетном входе изменит состояние триггера. Такие триггеры часто называют Т-триггерами.

Триггер, установленный в какое либо состояние, сохраняет его до тех пор, пока импульс, поданный на один из входов, не изменит это состояние.

Логические схемы R-S- и Т-триггера показаны на рис. 6.11.

Триггера могут иметь раздельные входы:

R (Reset) — вход установки «О»;

S (Set) — вход установки «1».

Каждый вход устанавливает триггер в соответствующее состояние, такие триггеры часто называют R-S-триггерами.

Триггеры могут иметь счетный вход Т (toggle, релаксатор), очередной импульс «1» на счетном входе изменит состояние триггера. Такие триггеры часто называют Т-триггерами.

Триггер, установленный в какое либо состояние, сохраняет его до тех пор, пока импульс, поданный на один из входов, не изменит это состояние.

Логические схемы R-S- и Т-триггера показаны на рис. 6.11.

Слайд 7

Слайд 8

Слайд 9

jk и счётный ( Т – триггер)

Прежде чем начать изучение jk триггера,

jk и счётный ( Т – триггер)

Прежде чем начать изучение jk триггера,

вспомним принципы работы RS-триггера. Напомню, что в этом триггере есть запрещённые комбинации входных сигналов. Одновременная подача единичных сигналов на входы R и S запрещены. Очень хотелось бы избавиться от этой неприятной ситуации.

Таблица истинности jk триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов jk триггер изменяет своё состояние на противоположное. Таблица истинности jk триггера приведена в таблице 1.

Таблица истинности jk триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц jk триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов jk триггер изменяет своё состояние на противоположное. Таблица истинности jk триггера приведена в таблице 1.

Слайд 10

Таблица 1. Таблица истинности jk триггера.

Таблица 1. Таблица истинности jk триггера.

Слайд 11

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 1.

Рис. 1. Внутренняя схема

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 1.

Рис. 1. Внутренняя схема

jk триггера

Для реализации счетного режима в схеме jk триггера, приведенной на рисунке 1, введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря этой обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация. При подаче на входы j и k логической единицы одновременно триггер переходит в счетный режим, подобно T триггеру.

Для реализации счетного режима в схеме jk триггера, приведенной на рисунке 1, введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря этой обратной связи на входах R и S первого триггера никогда не может возникнуть запрещенная комбинация. При подаче на входы j и k логической единицы одновременно триггер переходит в счетный режим, подобно T триггеру.

Слайд 12

Слайд 13

Слайд 14

Слайд 15

- Предыдущая

комфортабельность автомобиля и трактораСледующая -

Аналогия в архитектурах человека и ЭВМ

Нелинейные электрические цепи постоянного тока

Нелинейные электрические цепи постоянного тока Функциональное назначение здания. Помещение

Функциональное назначение здания. Помещение Організація та проведення спортивних змагань

Організація та проведення спортивних змагань День рождения Деда Мороза

День рождения Деда Мороза Экзамен ПМ 01. Билет № 8. Способы проверки отклонений от параллельности и перпендикулярности

Экзамен ПМ 01. Билет № 8. Способы проверки отклонений от параллельности и перпендикулярности Презентация "Карманные деньги" - скачать презентации по Экономике

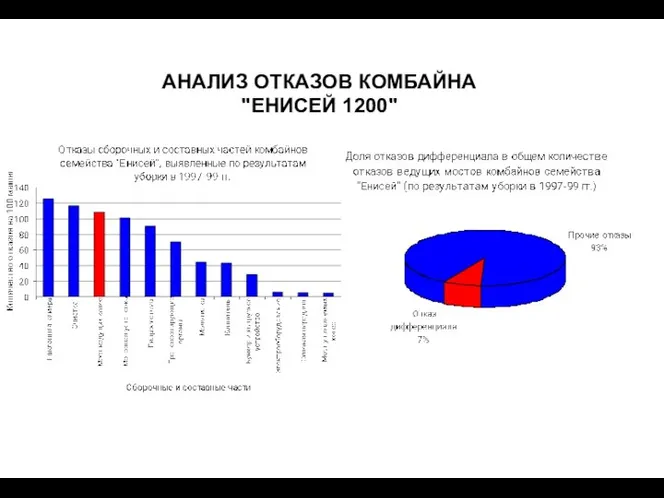

Презентация "Карманные деньги" - скачать презентации по Экономике Анализ отказов комбайна "Енисей 1200"

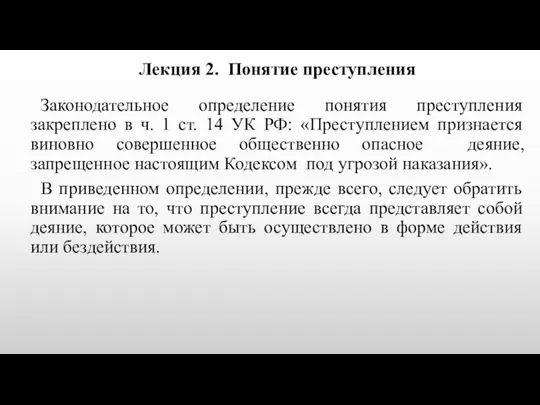

Анализ отказов комбайна "Енисей 1200" Понятие преступления и состав. Лекция 2

Понятие преступления и состав. Лекция 2 Мухта́р Омарханович Ауэ́зов 1897-1961

Мухта́р Омарханович Ауэ́зов 1897-1961 Опреснение и обессоливание воды

Опреснение и обессоливание воды Оперативный ток

Оперативный ток Прогнозирование численности населения Подготовили студентки 1-го курса Экономического факультета, группы Э122Б, Родионова Анаст

Прогнозирование численности населения Подготовили студентки 1-го курса Экономического факультета, группы Э122Б, Родионова Анаст сүтті жылулық өңдеу

сүтті жылулық өңдеу  Презентация на тему "Функции контроля. Требования к контролю. Виды контроля. Методы и формы контроля. Оценка результатов учебной

Презентация на тему "Функции контроля. Требования к контролю. Виды контроля. Методы и формы контроля. Оценка результатов учебной Конкуренция. Структура рынка

Конкуренция. Структура рынка  МБДОУ ДСОВ №135 Панина Нина Анатольевна

МБДОУ ДСОВ №135 Панина Нина Анатольевна Java Puzzlers

Java Puzzlers Презентация рабочих программ. Шитикова Ольга Николаевна Педагог-психолог МОУ «СОШ №16» I квалификационной категории

Презентация рабочих программ. Шитикова Ольга Николаевна Педагог-психолог МОУ «СОШ №16» I квалификационной категории Эритроцитоз

Эритроцитоз Холдинг «Строймаш-Вибропресс». Линия «Тенсиланд»

Холдинг «Строймаш-Вибропресс». Линия «Тенсиланд» Cleaning technology of ferroconcrete silo

Cleaning technology of ferroconcrete silo Презентация в мире животных - презентация для начальной школы

Презентация в мире животных - презентация для начальной школы Интерактивная выставка "Очарование Театра"

Интерактивная выставка "Очарование Театра" Принципы управления персоналом

Принципы управления персоналом  Сотворение мира

Сотворение мира  Селекция как научная дисциплина. Генетика- теоретическая основа селекции

Селекция как научная дисциплина. Генетика- теоретическая основа селекции Макроэкономические показатели в системе национальных счетов Подготовили студентки 2 курса группы э121б Редок Полина Витебская

Макроэкономические показатели в системе национальных счетов Подготовили студентки 2 курса группы э121б Редок Полина Витебская  Спряжение глаголов. Урок русского языка 4 класс

Спряжение глаголов. Урок русского языка 4 класс