Содержание

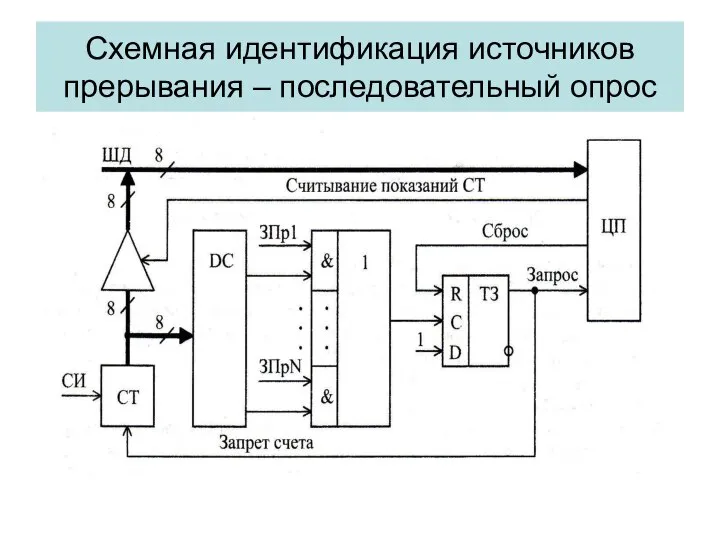

- 2. Схемная идентификация источников прерывания – последовательный опрос

- 3. Аппаратный поллинг источников прерывания – последовательный опрос Обобщенный сигнал прерывания От МП Дейзи-цепочка Отклик на события

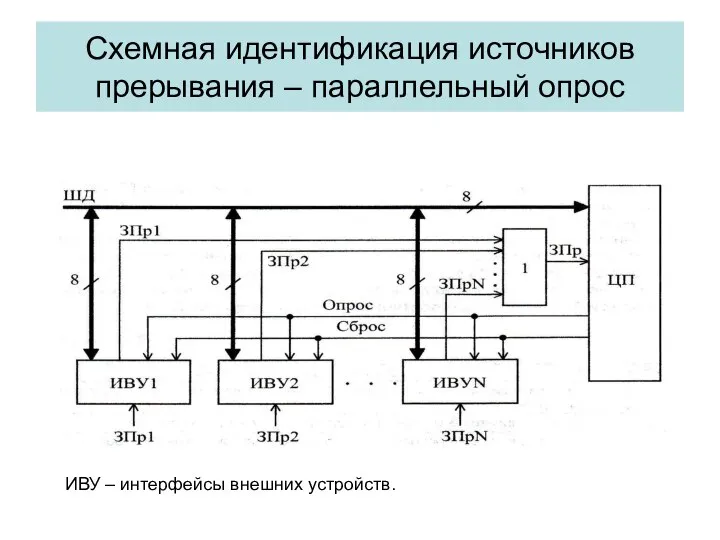

- 4. Схемная идентификация источников прерывания – параллельный опрос ИВУ – интерфейсы внешних устройств.

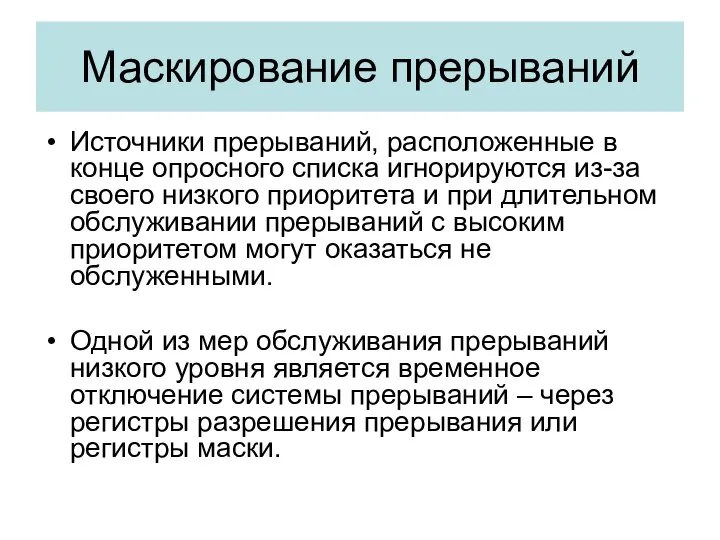

- 5. Маскирование прерываний Источники прерываний, расположенные в конце опросного списка игнорируются из-за своего низкого приоритета и при

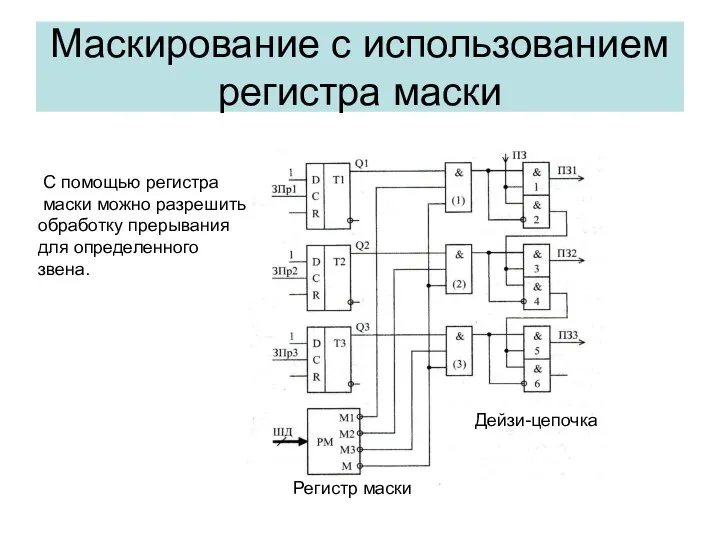

- 6. Маскирование с использованием регистра маски Дейзи-цепочка Регистр маски С помощью регистра маски можно разрешить обработку прерывания

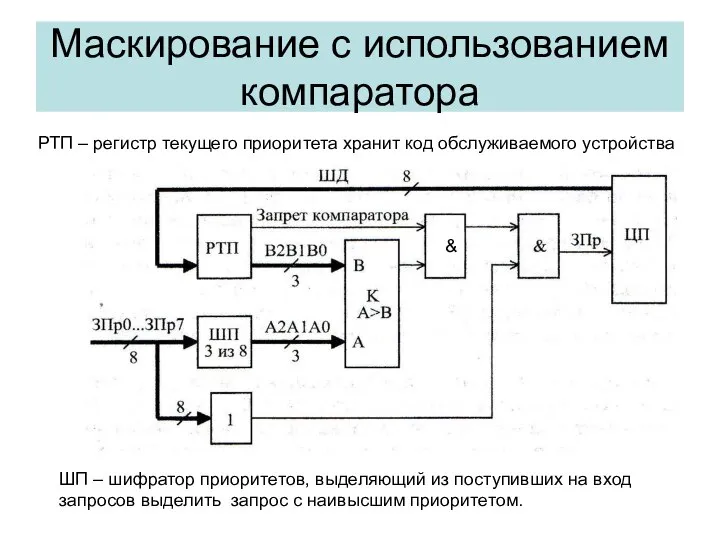

- 7. Маскирование с использованием компаратора РТП – регистр текущего приоритета хранит код обслуживаемого устройства ШП – шифратор

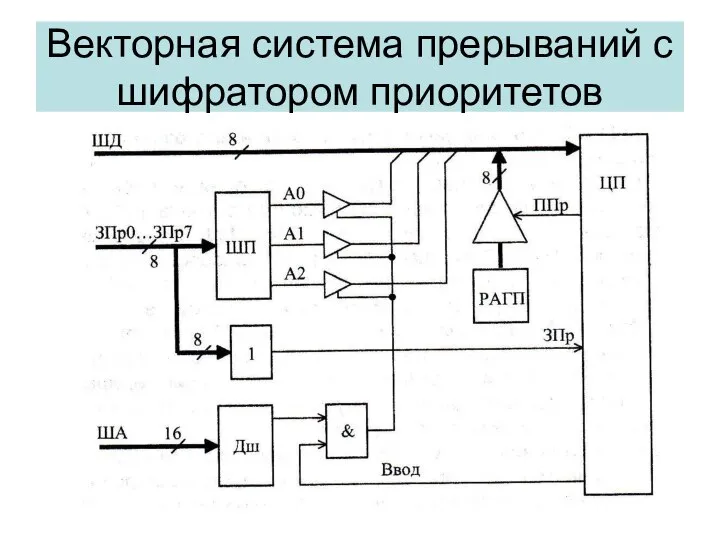

- 8. Векторная система прерываний с шифратором приоритетов

- 9. Система с одним вектором прерывания

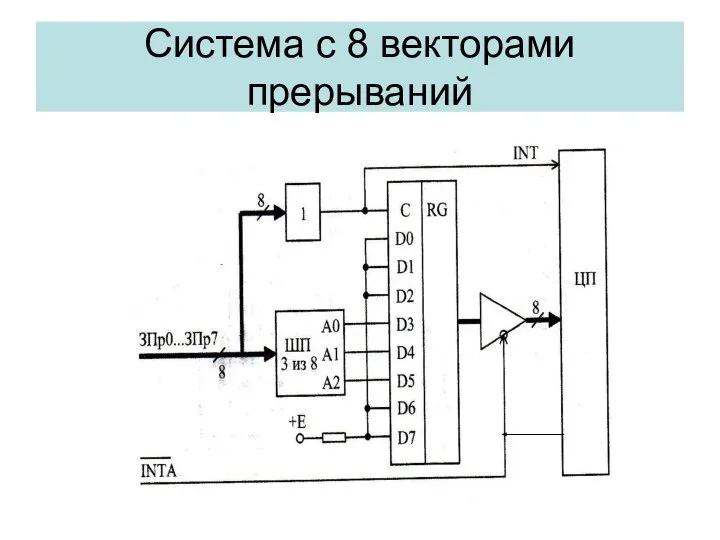

- 10. Система с 8 векторами прерываний

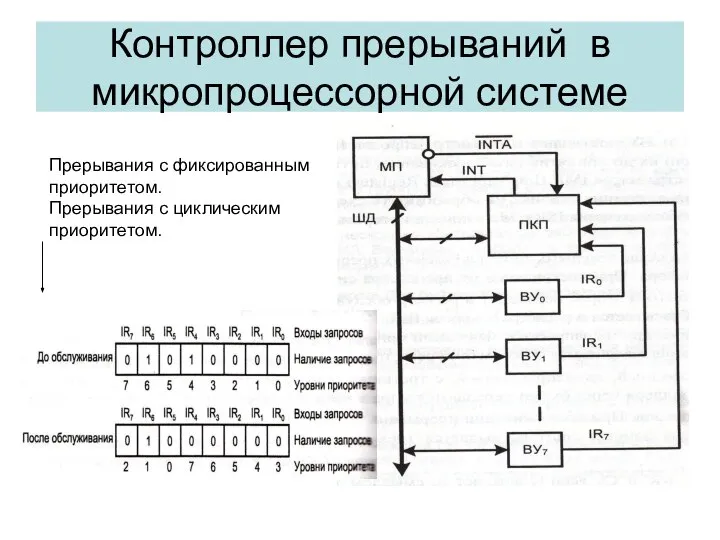

- 11. Контроллер прерываний в микропроцессорной системе Прерывания с фиксированным приоритетом. Прерывания с циклическим приоритетом.

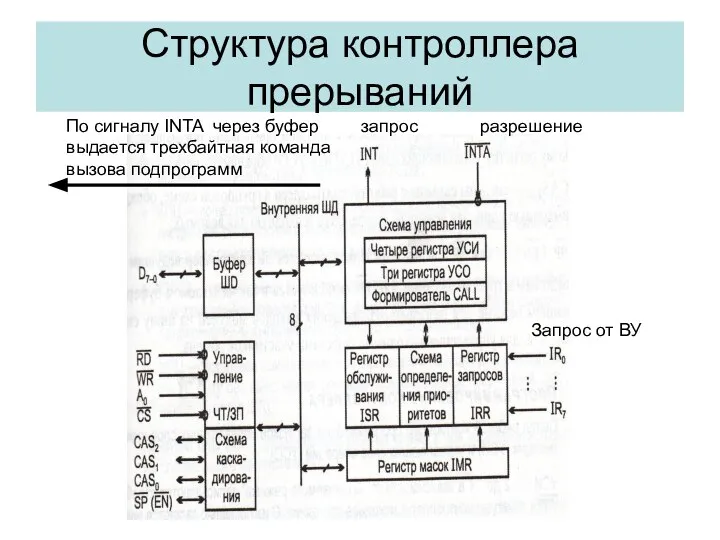

- 12. Структура контроллера прерываний запрос разрешение Запрос от ВУ По сигналу INTA через буфер выдается трехбайтная команда

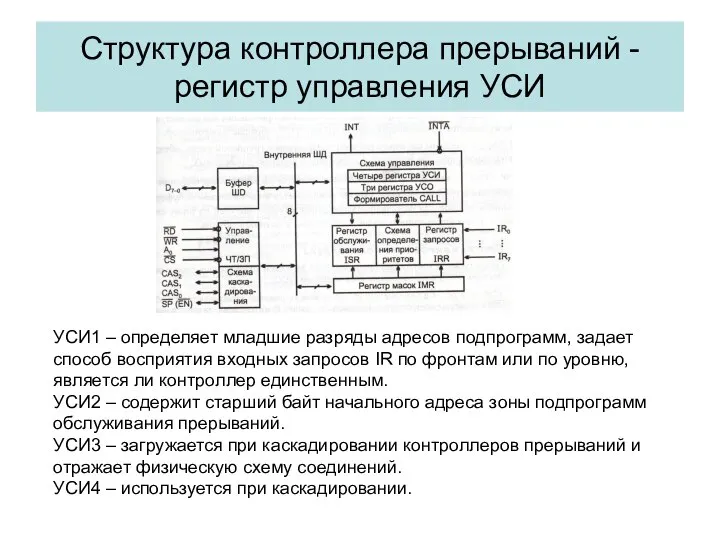

- 13. Структура контроллера прерываний - регистр управления УСИ УСИ1 – определяет младшие разряды адресов подпрограмм, задает способ

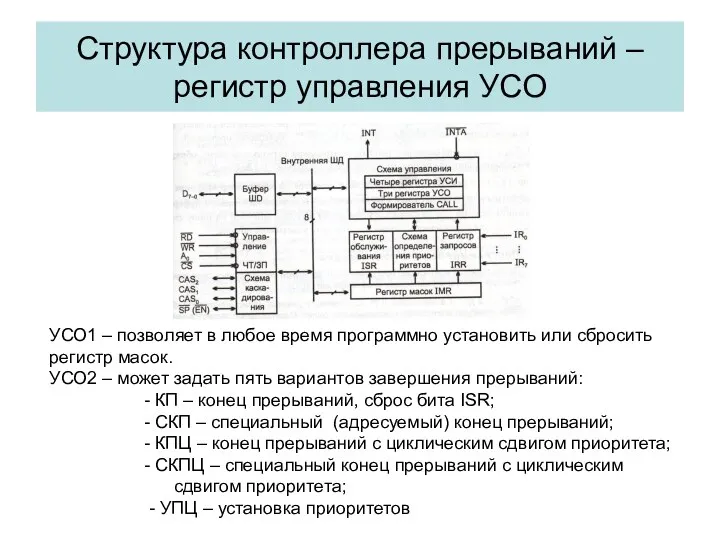

- 14. Структура контроллера прерываний – регистр управления УСО УСО1 – позволяет в любое время программно установить или

- 15. Каскадное включение контроллеров прерывания Каскадирование позволяет расширить число обрабатываемых запросов. Возможно каскадирование до 8 контроллеров.

- 16. Контроллер прямого доступа к памяти (DMA – Direct Memory Access) Для обмена данными между устройствами внешней

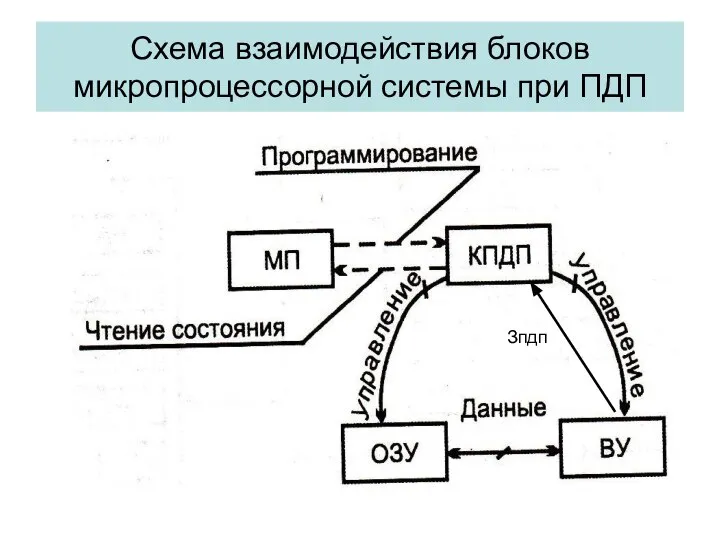

- 17. Схема взаимодействия блоков микропроцессорной системы при ПДП Зпдп

- 18. Виды ПДП С захватом цикла. Обмен байтами в моменты когда процессор не обращается к памяти. Случайные

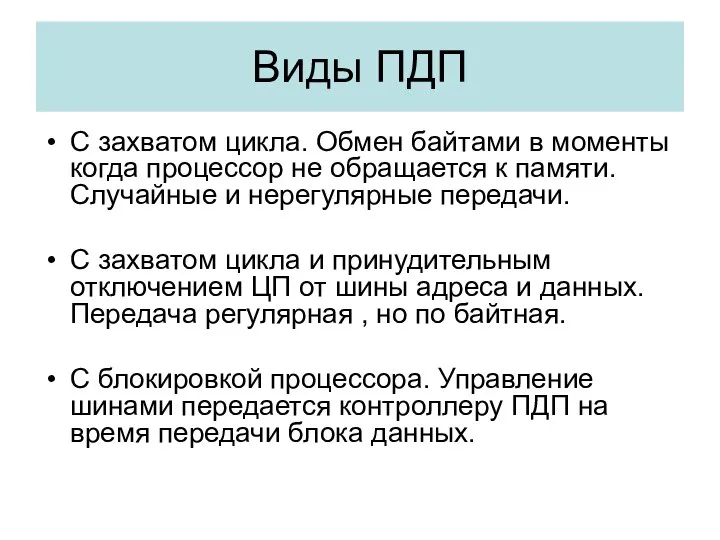

- 19. Структура МПС с контроллером ПДП МП ОЗУ Контроллер ПДП ВУ ША ШД ШУ HRQ HRQ –

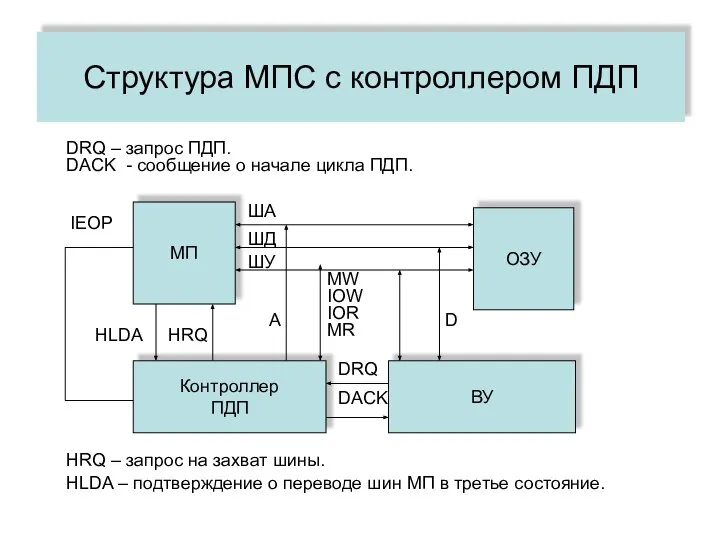

- 20. Взаимодействие ЦП, памяти и ВУ с контроллером ПДП Если нет запросов от ВУ, КПДП может быть

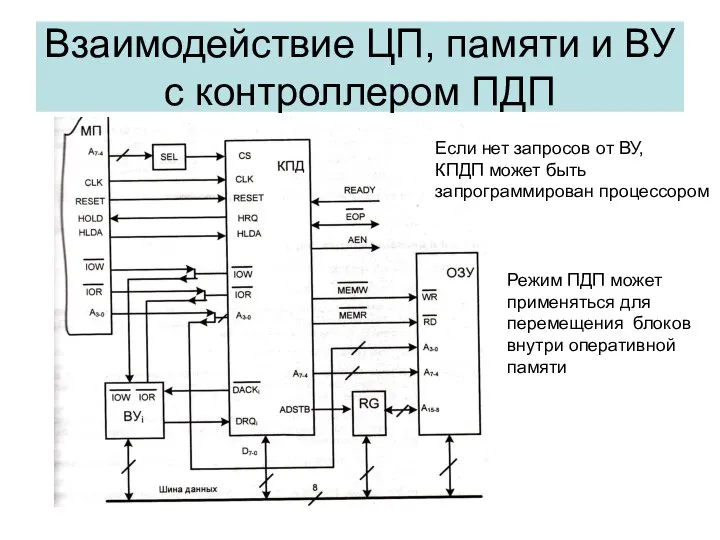

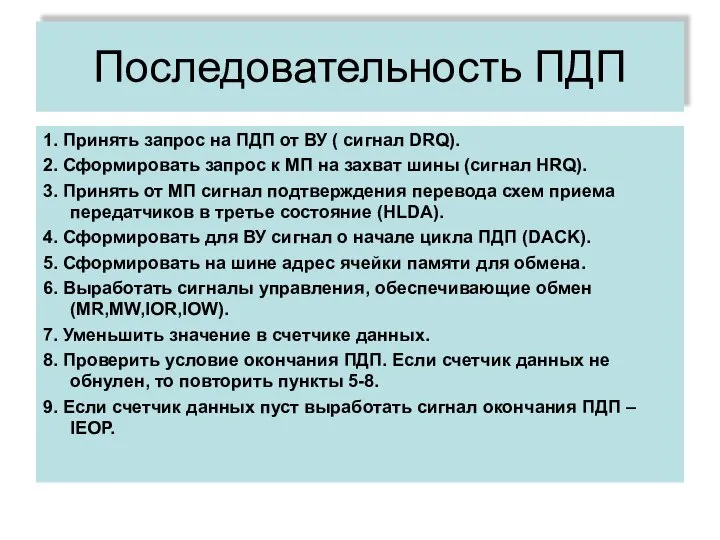

- 21. Последовательность ПДП 1. Принять запрос на ПДП от ВУ ( сигнал DRQ). 2. Сформировать запрос к

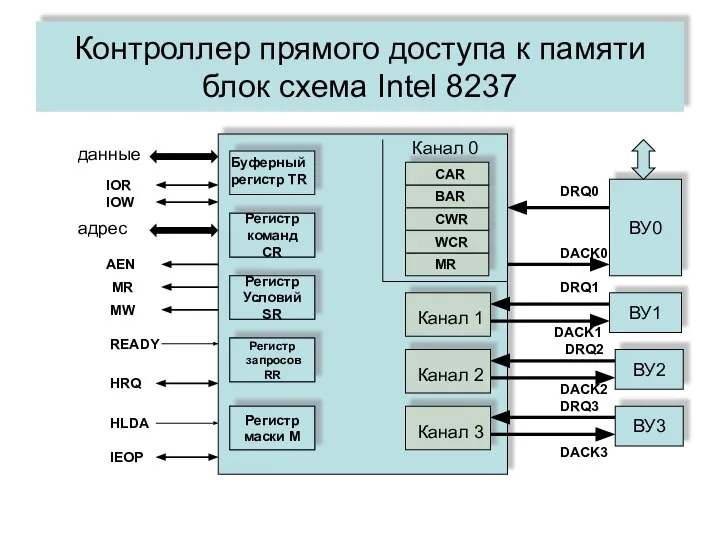

- 22. Контроллер прямого доступа к памяти блок схема Intel 8237 CAR BAR CWR WCR MR Канал 0

- 24. Скачать презентацию

Модели деловой карьеры

Модели деловой карьеры Інженерія програмного забезпечення. (Лекція 2)

Інженерія програмного забезпечення. (Лекція 2) Торгово-развлекательный комплекс "Берёзки". Планировка

Торгово-развлекательный комплекс "Берёзки". Планировка Презентация на тему "Эмоциональная зависимость" - скачать презентации по Педагогике

Презентация на тему "Эмоциональная зависимость" - скачать презентации по Педагогике Ваши Воспитатели: Леонтьева Светлана Викторовна Бардаева Марина Юрьевна

Ваши Воспитатели: Леонтьева Светлана Викторовна Бардаева Марина Юрьевна Зеленое строительство

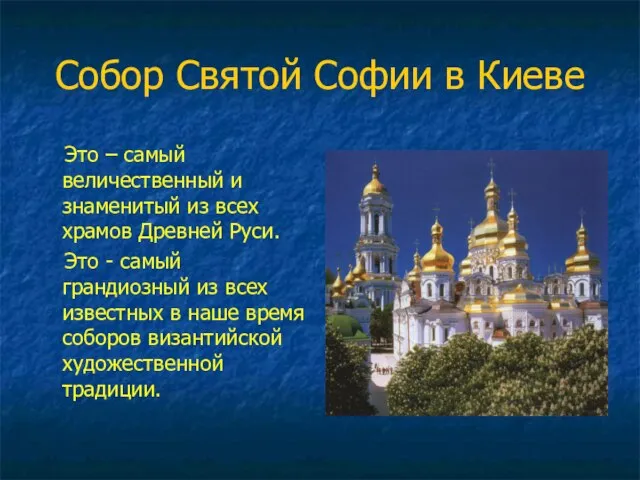

Зеленое строительство Собор Святой Софии в Киеве Это – самый величественный и знаменитый из всех храмов Древней Руси. Это - самый грандиозный из вс

Собор Святой Софии в Киеве Это – самый величественный и знаменитый из всех храмов Древней Руси. Это - самый грандиозный из вс Обучение детей ориентировке в пространстве Подготовила педагог-психолог Жигунова М.В. ГБОУ СОШ1293 СП № 1 города Москвы

Обучение детей ориентировке в пространстве Подготовила педагог-психолог Жигунова М.В. ГБОУ СОШ1293 СП № 1 города Москвы ТОЛЕРАНТНОСТЬ ИНТОЛЕРАНТНОСТЬ социальный педагог ОПСОП по Куйбышевскому району ЦРО г.о. Самара Мищенкова Лариса Петровна

ТОЛЕРАНТНОСТЬ ИНТОЛЕРАНТНОСТЬ социальный педагог ОПСОП по Куйбышевскому району ЦРО г.о. Самара Мищенкова Лариса Петровна Marea familie a Europei

Marea familie a Europei Презентация на тему "Искусство общения с родителями" - скачать презентации по Педагогике

Презентация на тему "Искусство общения с родителями" - скачать презентации по Педагогике Алгоритмы управления и аддаптации в ТКС

Алгоритмы управления и аддаптации в ТКС  Системы электроснабжения самолёта МиГ-29 и вертолета

Системы электроснабжения самолёта МиГ-29 и вертолета Хохломская роспись

Хохломская роспись Religion. How does religion effect the modern life?

Religion. How does religion effect the modern life? Региональная политика в современном мире

Региональная политика в современном мире Организация фермерского (свиноводческого) хозяйства на территории Ивановской области

Организация фермерского (свиноводческого) хозяйства на территории Ивановской области Кроссбраузерная верстка

Кроссбраузерная верстка Сборочное моделирование. Решения по управлению жизненным циклом, продукт IBM/Dassault Systemes

Сборочное моделирование. Решения по управлению жизненным циклом, продукт IBM/Dassault Systemes Криминалистическая характеристика преступления как структурный элемент частной методики расследования

Криминалистическая характеристика преступления как структурный элемент частной методики расследования Пресс-служба администрации Курской области

Пресс-служба администрации Курской области Молоко и молочные продукты - презентация для начальной школы

Молоко и молочные продукты - презентация для начальной школы Азотцентрированные соединения

Азотцентрированные соединения  Глава 1 Принципы экономики 6. Из истории экономики и экономической науки

Глава 1 Принципы экономики 6. Из истории экономики и экономической науки  Русская матрешка

Русская матрешка Тушь для ресниц Galaxy Volume 5D. Набор теней для макияжа

Тушь для ресниц Galaxy Volume 5D. Набор теней для макияжа Обследование строительных конструкций зданий и сооружений

Обследование строительных конструкций зданий и сооружений Лыжные гонки

Лыжные гонки