Содержание

- 2. Задачи системы вводы вывода

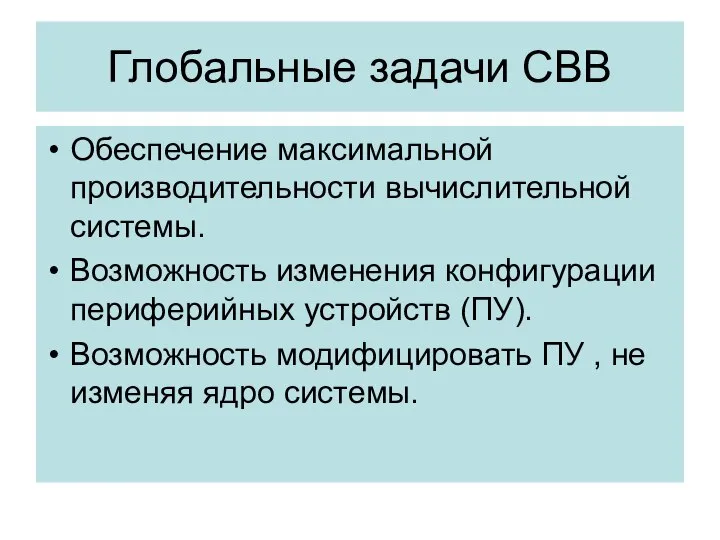

- 3. Глобальные задачи СВВ Обеспечение максимальной производительности вычислительной системы. Возможность изменения конфигурации периферийных устройств (ПУ). Возможность модифицировать

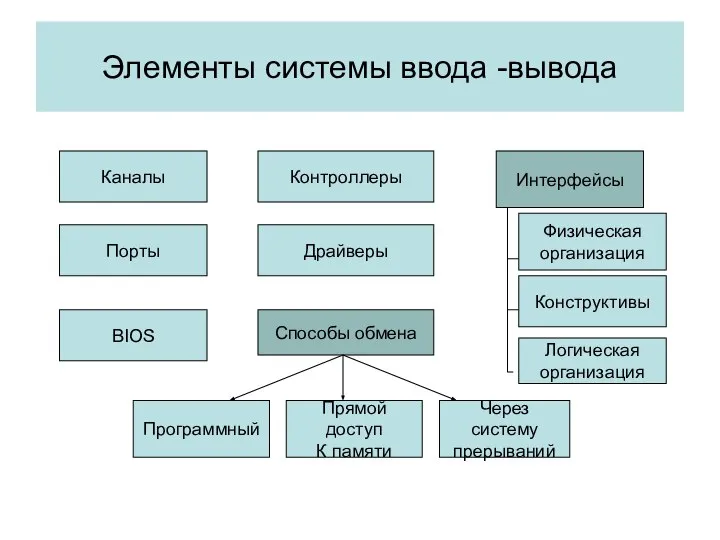

- 4. Элементы системы ввода -вывода Каналы Порты Интерфейсы Контроллеры Драйверы Способы обмена Программный Прямой доступ К памяти

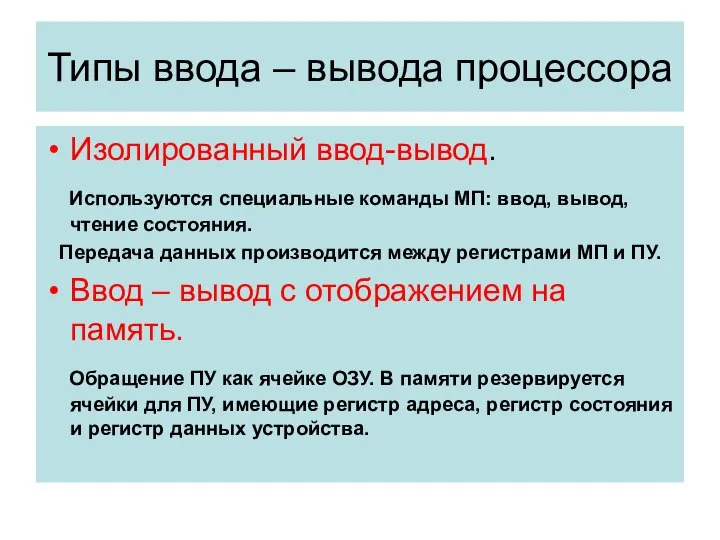

- 5. Типы ввода – вывода процессора Изолированный ввод-вывод. Используются специальные команды МП: ввод, вывод, чтение состояния. Передача

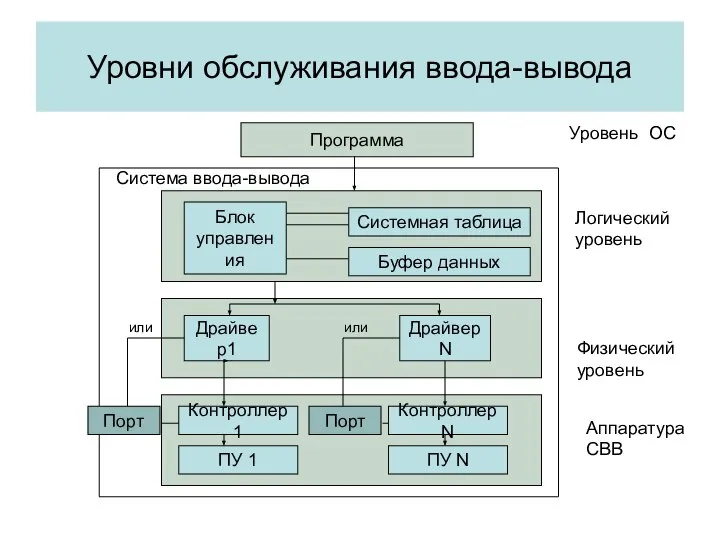

- 6. Уровни обслуживания ввода-вывода Программа Блок управления Системная таблица Буфер данных Драйвер1 Драйвер N Контроллер 1 Контроллер

- 7. Функции драйверов Проверка готовности контроллера и ПУ к обмену; Формирование управляющих сигналов и данных для ПУ;

- 8. Способы организации СВВ Программный. На основе системы прерываний. Прямой доступ к памяти. Коммутаторный. Без адресный «точка

- 9. Алгоритм программного ввода-вывода под управлением процессора 1. Сформировать начальный адрес области обмена ОЗУ. 2. Занести длину

- 10. Система прерываний Обработка прерывания. Организация системы приоритетов через систему арбитража.

- 11. Диаграмма прерывания

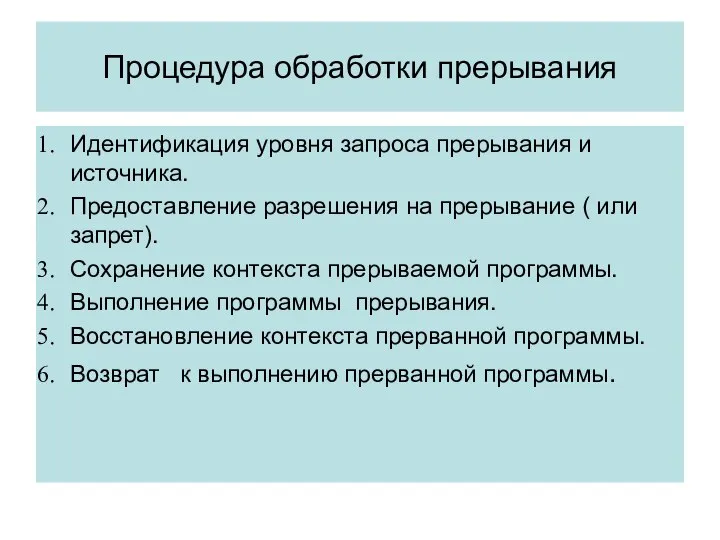

- 12. Процедура обработки прерывания Идентификация уровня запроса прерывания и источника. Предоставление разрешения на прерывание ( или запрет).

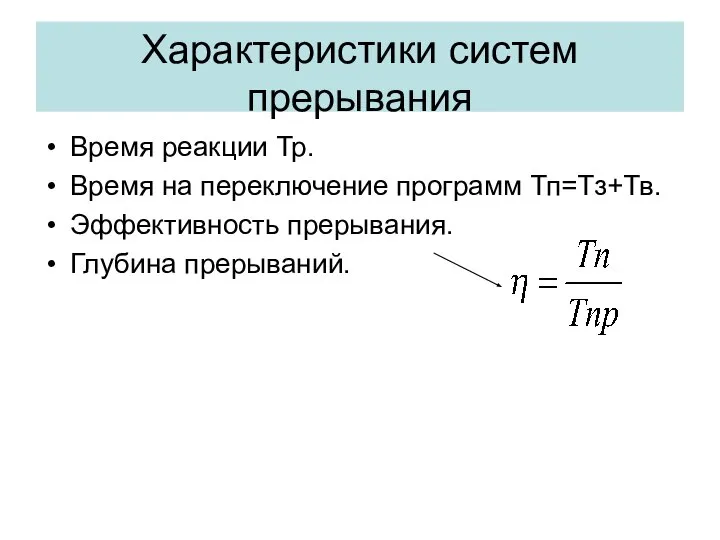

- 13. Характеристики систем прерывания Время реакции Тр. Время на переключение программ Тп=Тз+Тв. Эффективность прерывания. Глубина прерываний.

- 14. Глубина прерывания

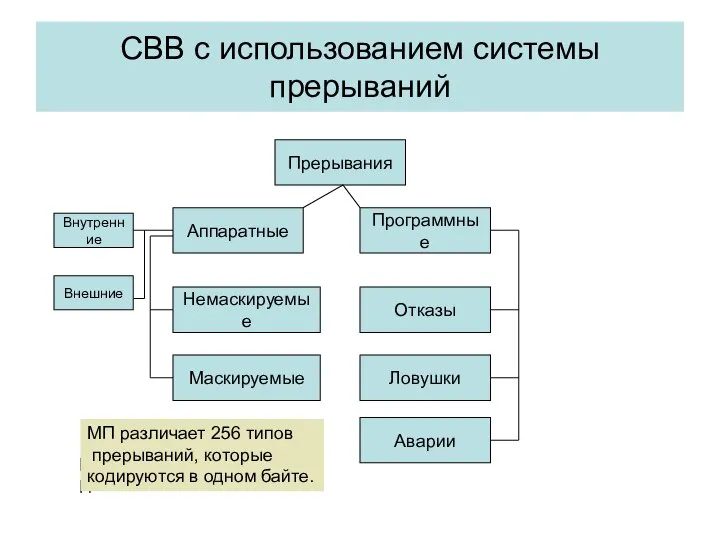

- 15. СВВ с использованием системы прерываний Прерывания Аппаратные Программные Немаскируемые Маскируемые Отказы Ловушки Аварии МП МП различает

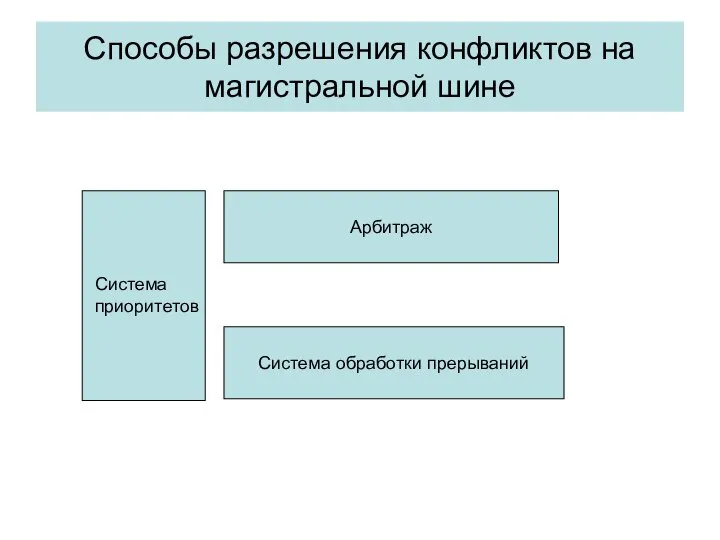

- 16. Способы разрешения конфликтов на магистральной шине Арбитраж Система обработки прерываний Система приоритетов

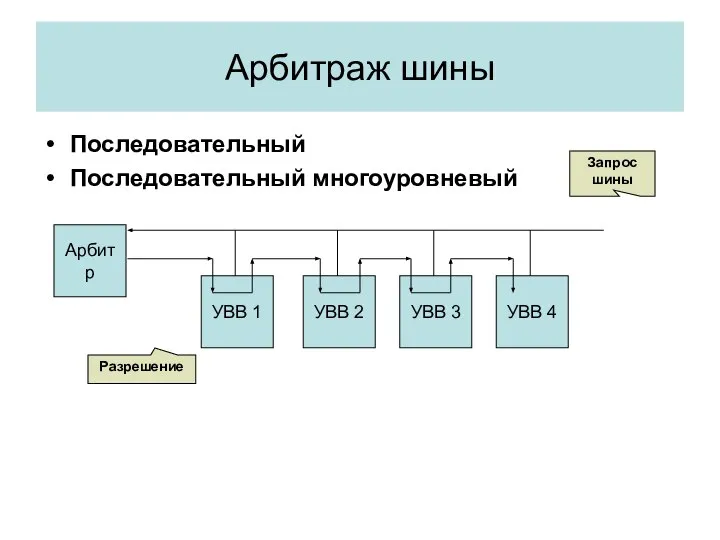

- 17. Арбитраж шины Последовательный Последовательный многоуровневый Арбитр УВВ 1 УВВ 2 УВВ 3 УВВ 4 Запрос шины

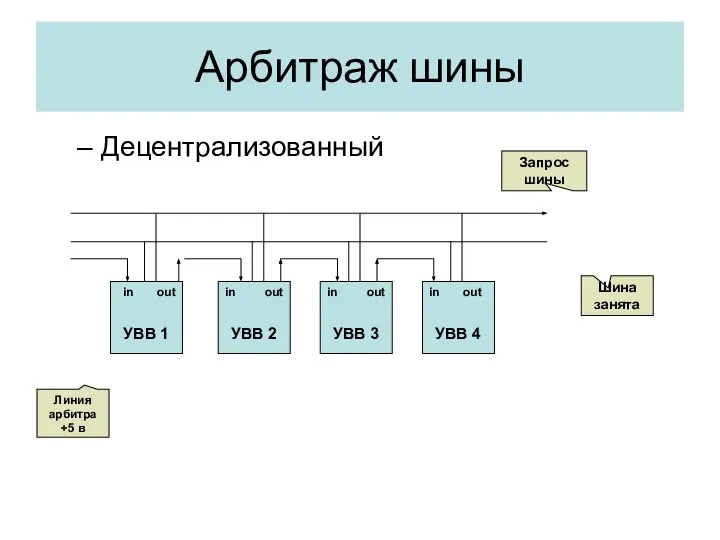

- 18. Децентрализованный Арбитраж шины in out in in in out out out Линия арбитра +5 в УВВ

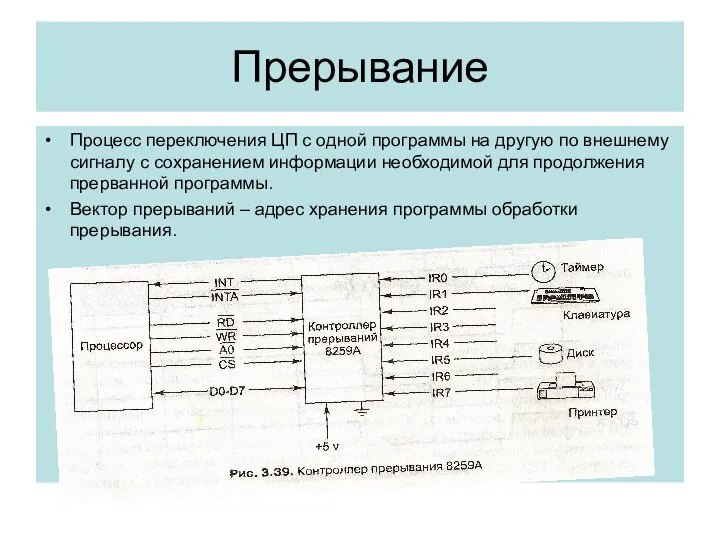

- 19. Прерывание Процесс переключения ЦП с одной программы на другую по внешнему сигналу с сохранением информации необходимой

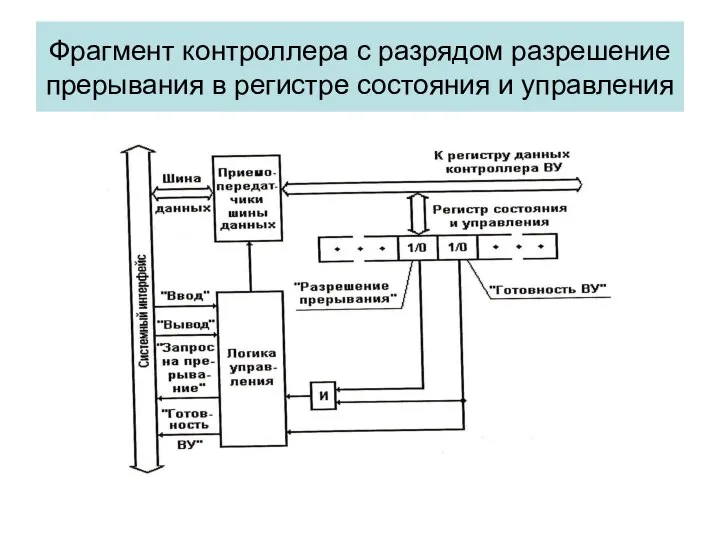

- 20. Фрагмент контроллера с разрядом разрешение прерывания в регистре состояния и управления

- 21. Вектор прерываний

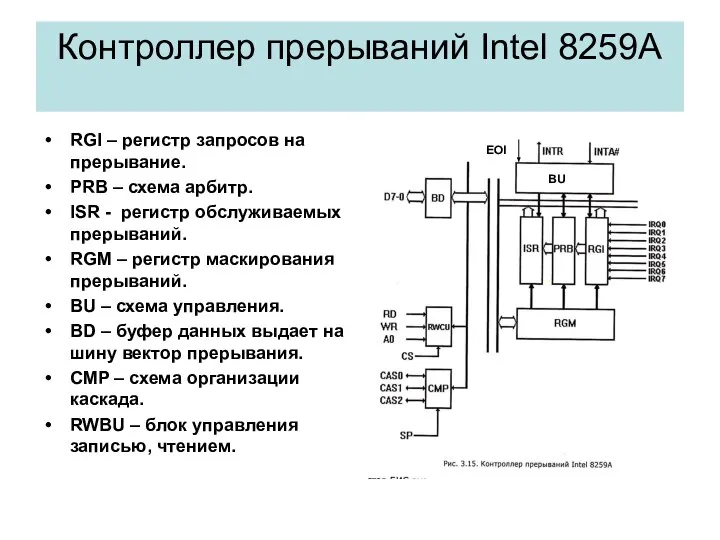

- 22. Контроллер прерываний Intel 8259A RGI – регистр запросов на прерывание. PRB – схема арбитр. ISR -

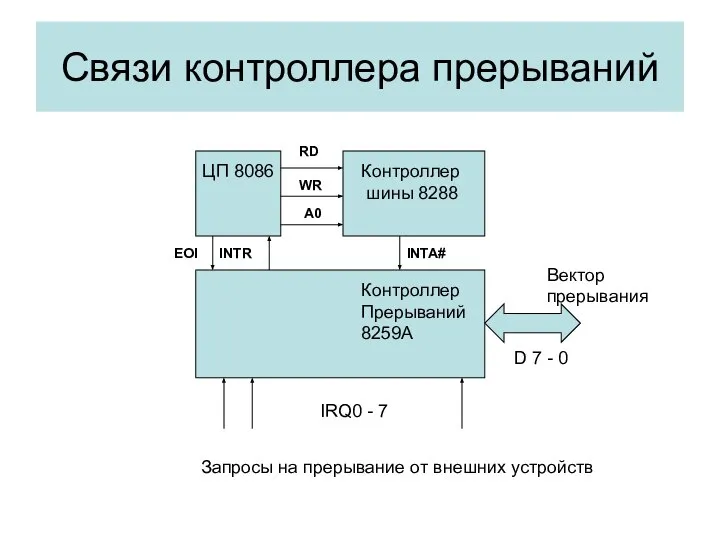

- 23. Связи контроллера прерываний ЦП 8086 Контроллер шины 8288 RD WR A0 EOI INTR INTA# Контроллер Прерываний

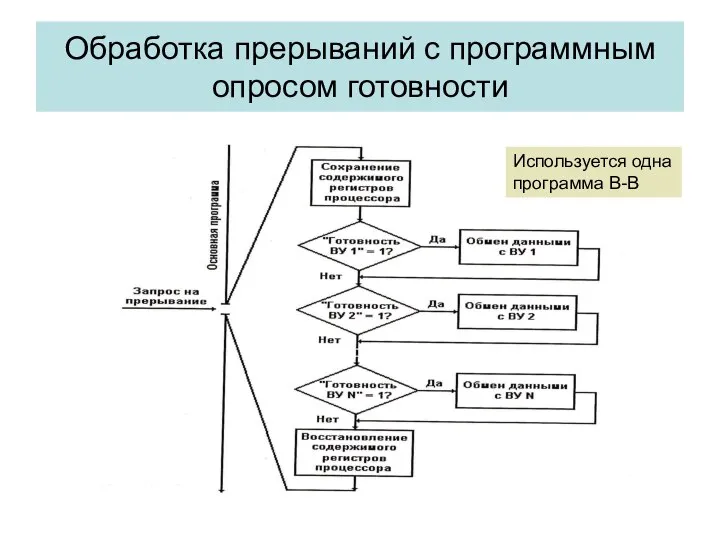

- 24. Обработка прерываний с программным опросом готовности Используется одна программа В-В

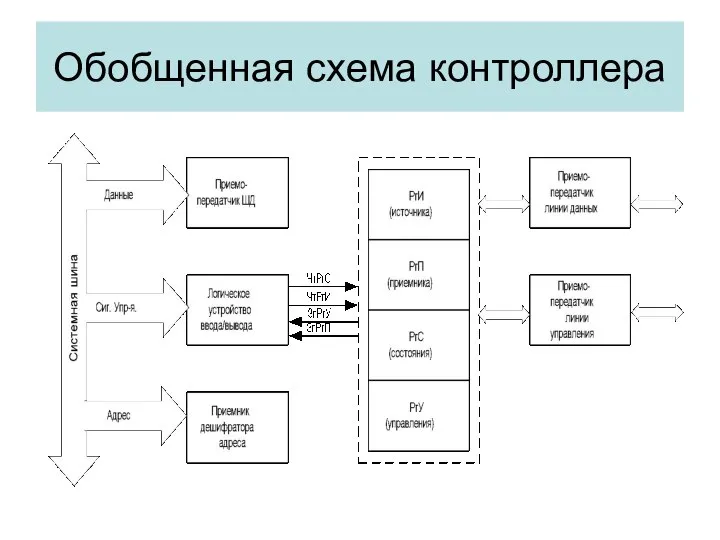

- 25. Обобщенная схема контроллера

- 26. Параллельный контроллер вывода Синхронный – приемник и передатчик работают от одного тактового генератора. Асинхронный – приемник

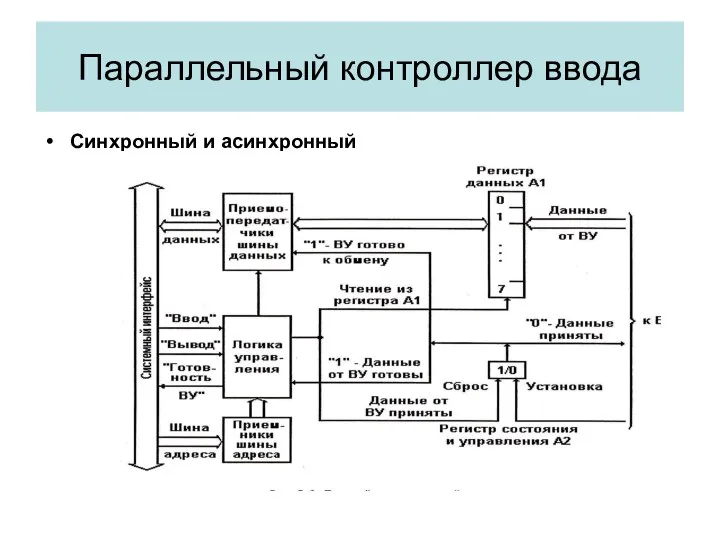

- 27. Синхронный и асинхронный Параллельный контроллер ввода

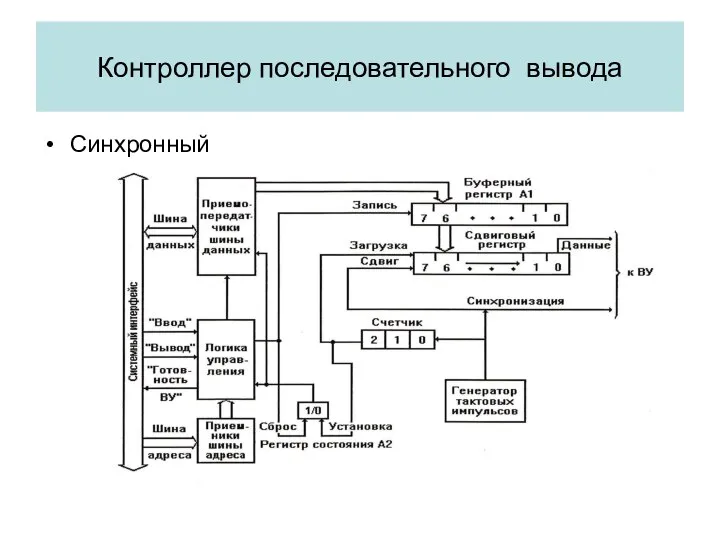

- 28. Контроллер последовательного вывода Синхронный

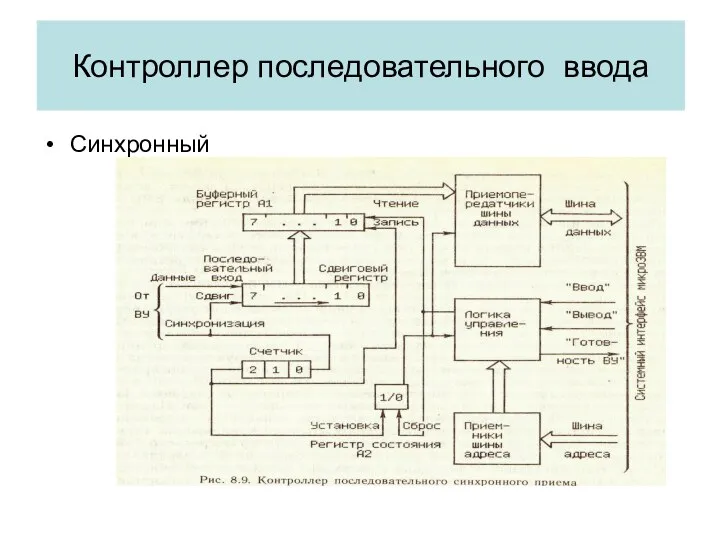

- 29. Синхронный Контроллер последовательного ввода

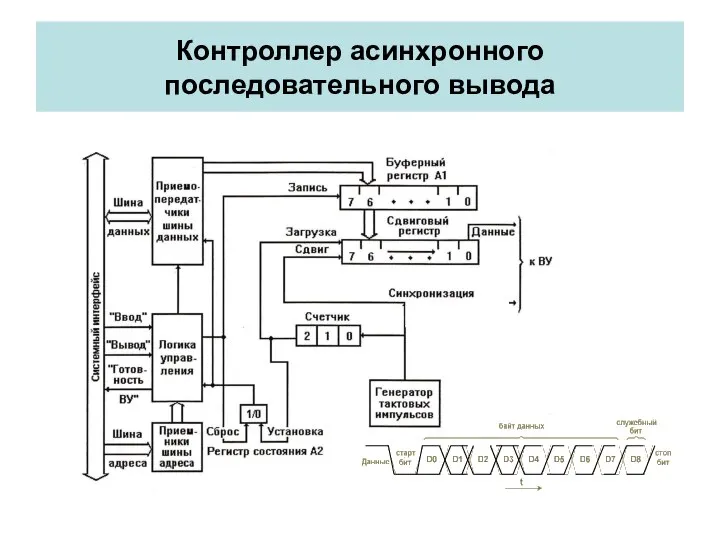

- 30. Контроллер асинхронного последовательного вывода

- 31. Контроллер асинхронного последовательного ввода

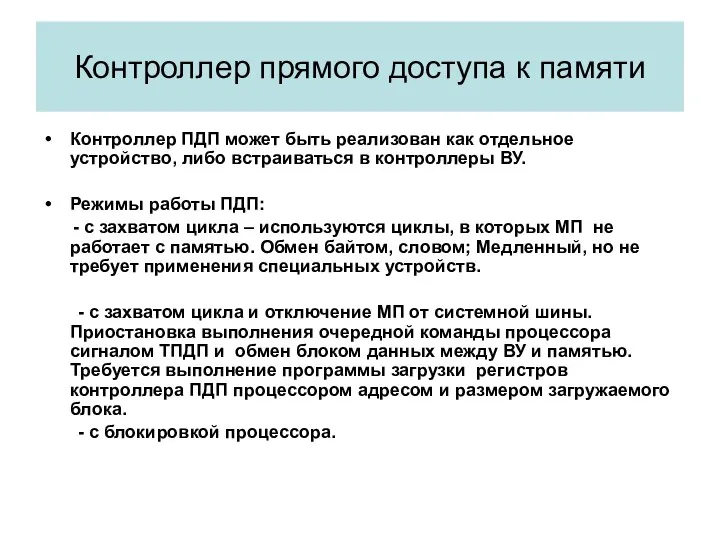

- 32. Контроллер ПДП может быть реализован как отдельное устройство, либо встраиваться в контроллеры ВУ. Режимы работы ПДП:

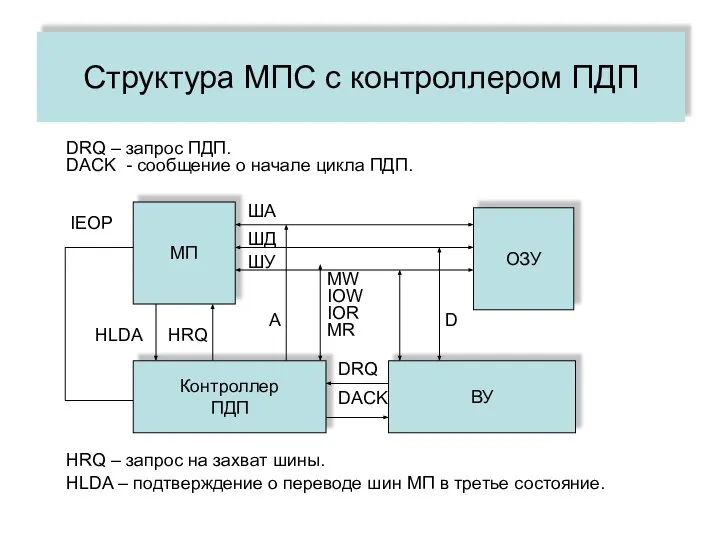

- 33. Структура МПС с контроллером ПДП МП ОЗУ Контроллер ПДП ВУ ША ШД ШУ HRQ HRQ –

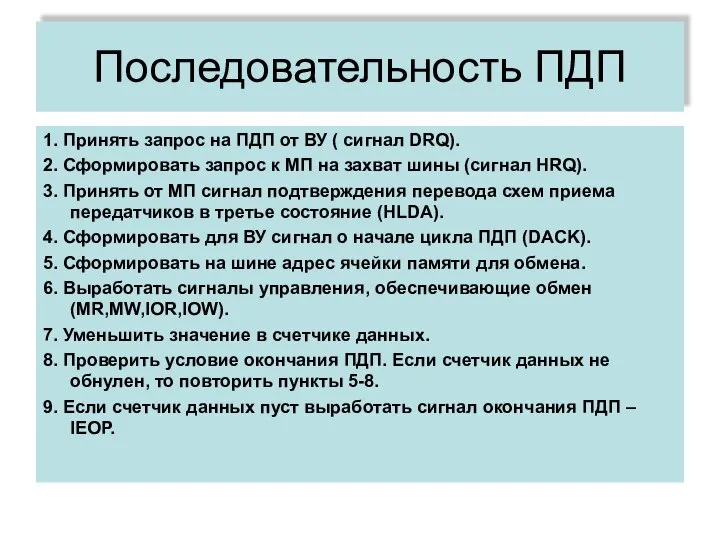

- 34. Последовательность ПДП 1. Принять запрос на ПДП от ВУ ( сигнал DRQ). 2. Сформировать запрос к

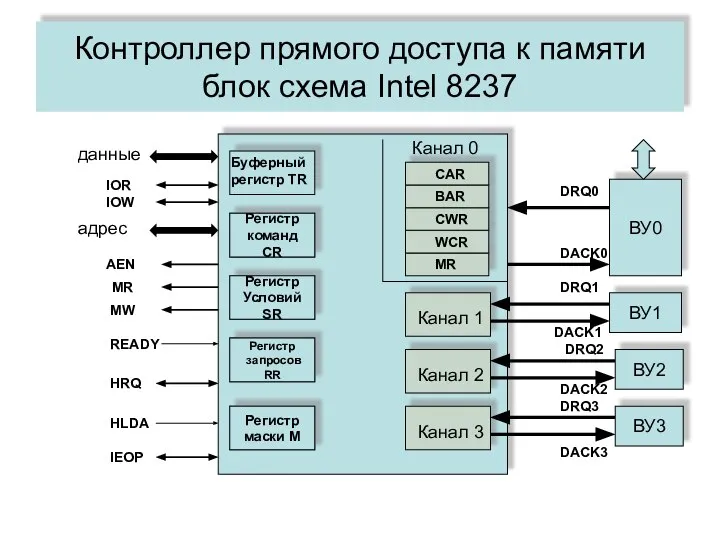

- 35. Контроллер прямого доступа к памяти блок схема Intel 8237 CAR BAR CWR WCR MR Канал 0

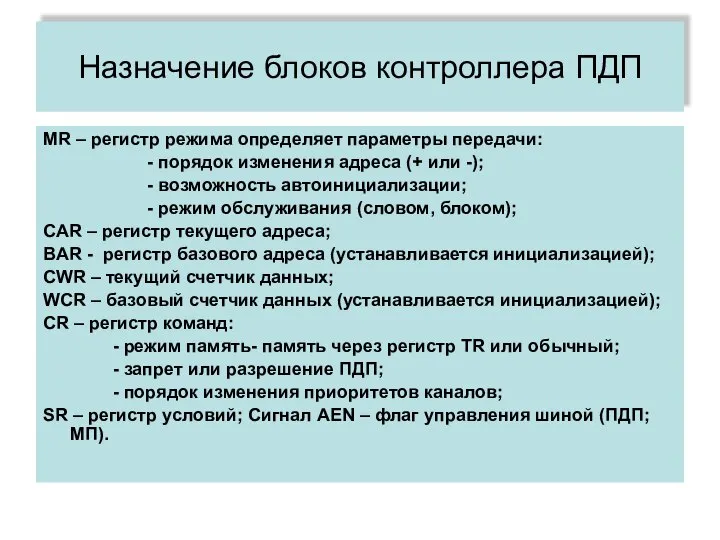

- 36. Назначение блоков контроллера ПДП MR – регистр режима определяет параметры передачи: - порядок изменения адреса (+

- 37. Фрагмент контроллера прямого доступа к памяти

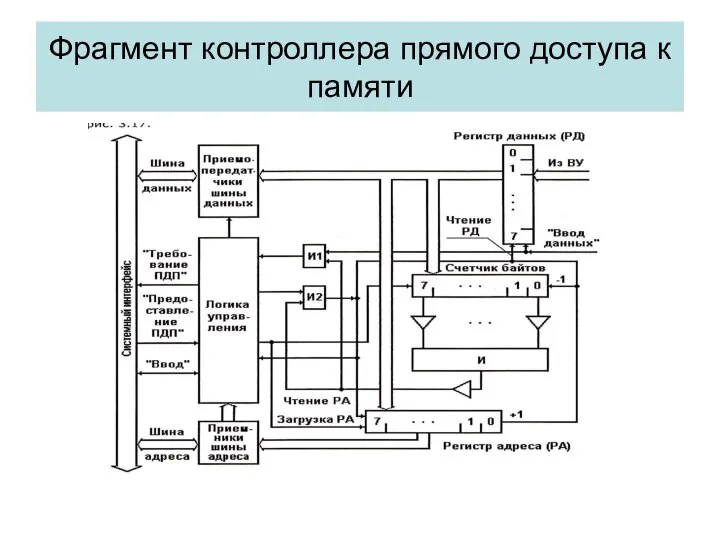

- 38. PIO- parallel Input-Output Микросхема Intel 8255A 8255A Порт А 8 разрядов Порт В 8 разрядов Порт

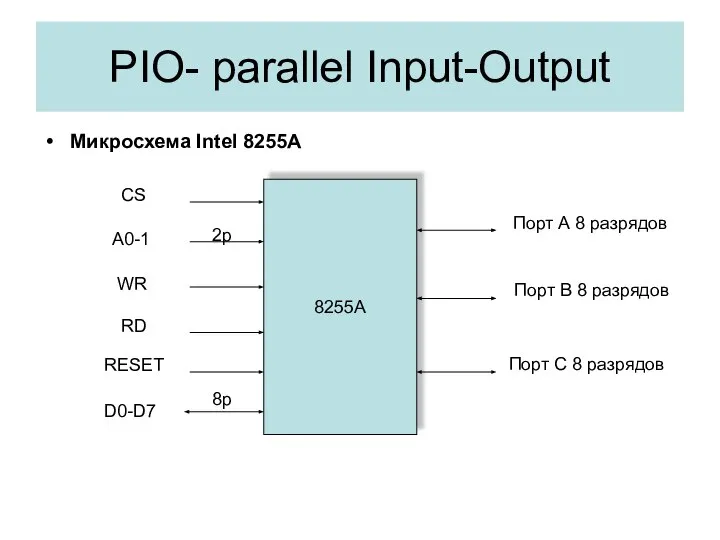

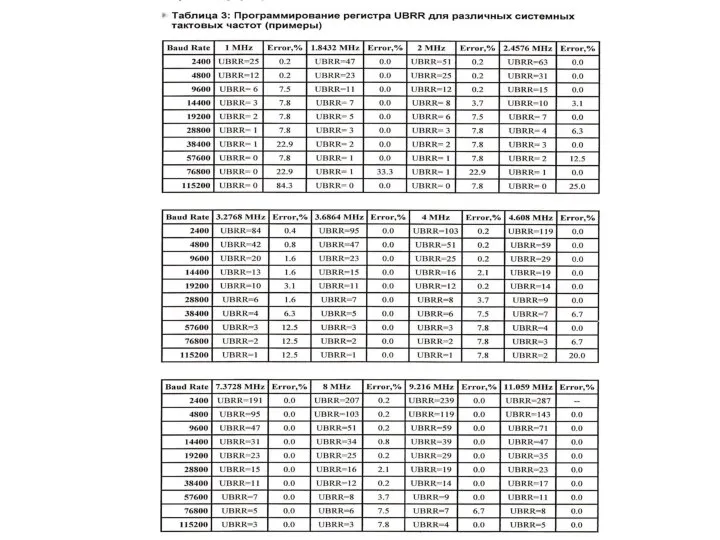

- 39. Программная модель UART(Universal Asynchronous Receiver Transmitter) МП AVR фирмы ATMEL Регистр данных передатчика UDR 10 (11)

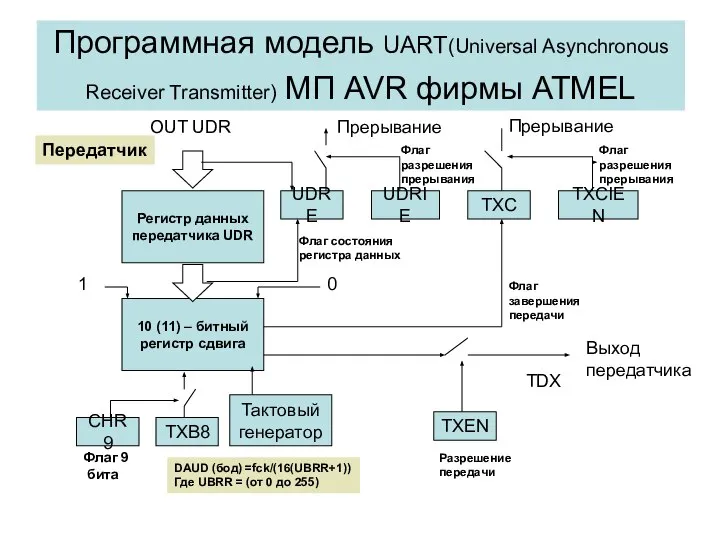

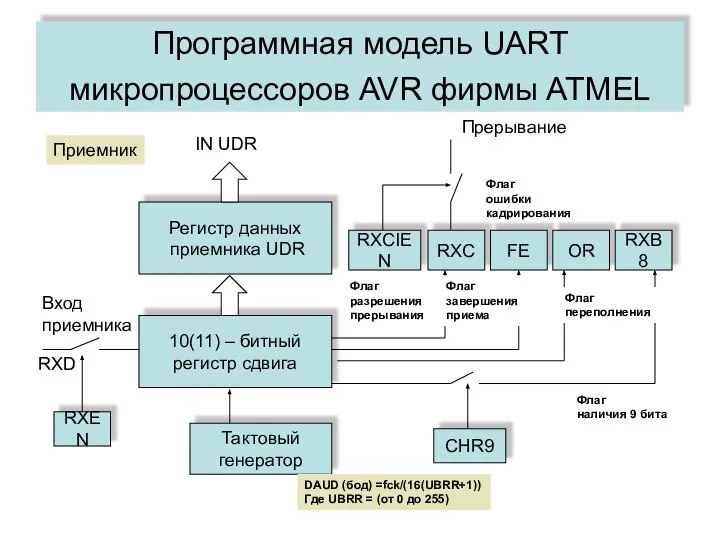

- 40. Программная модель UART микропроцессоров AVR фирмы ATMEL Регистр данных приемника UDR 10(11) – битный регистр сдвига

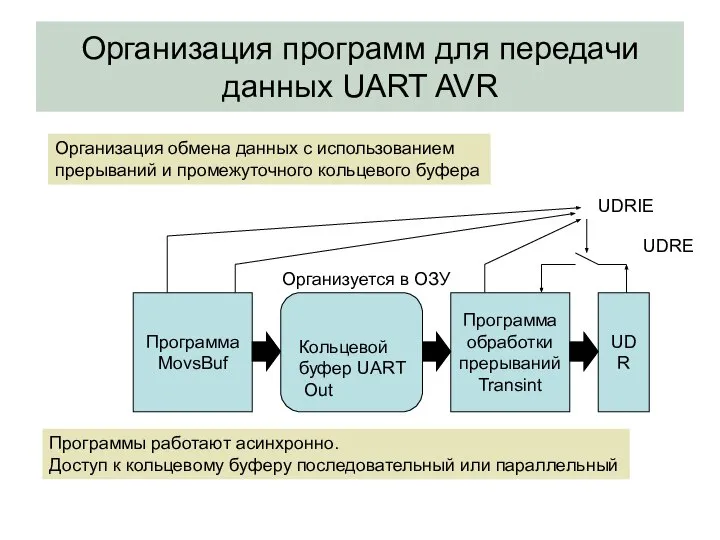

- 42. Организация программ для передачи данных UART AVR Программа MovsBuf Программа обработки прерываний Transint UDR Организация обмена

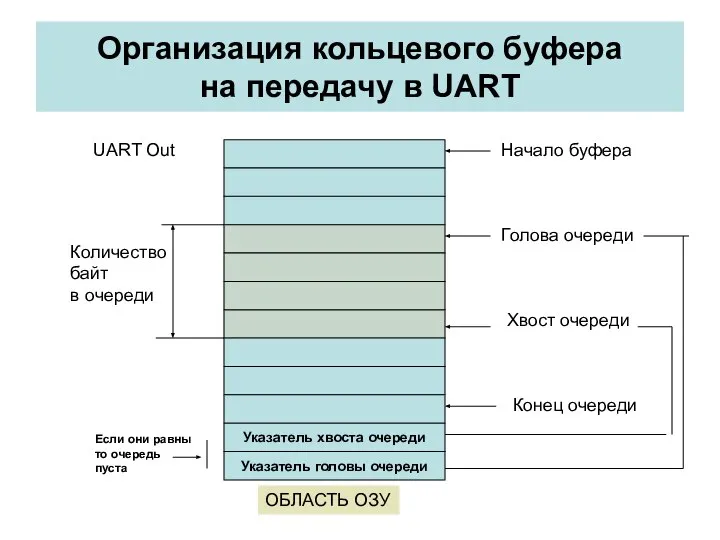

- 43. Организация кольцевого буфера на передачу в UART Указатель хвоста очереди Указатель головы очереди Начало буфера Голова

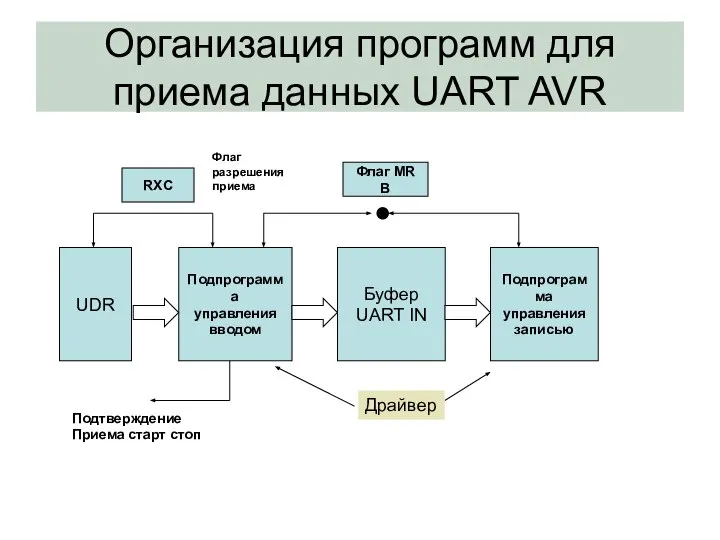

- 44. Организация программ для приема данных UART AVR Подпрограмма управления вводом Буфер UART IN Подпрограмма управления записью

- 46. Скачать презентацию

Эпидситуация по столбняку

Эпидситуация по столбняку  Презентация СРАВНИТЕЛЬНЫЙ АНАЛИЗ СОСТОЯНИЯ И РАЗВИТИЯ РЫНКОВ ТОРГОВЛИ МЕДИЦИНСКИМ ОБОРУДОВАНИЕМ В РОССИИ И ЗА РУБЕЖОМ

Презентация СРАВНИТЕЛЬНЫЙ АНАЛИЗ СОСТОЯНИЯ И РАЗВИТИЯ РЫНКОВ ТОРГОВЛИ МЕДИЦИНСКИМ ОБОРУДОВАНИЕМ В РОССИИ И ЗА РУБЕЖОМ  Викторина

Викторина Культура и личность

Культура и личность Бизнес план Кафе «Уютный дворик»

Бизнес план Кафе «Уютный дворик» Идентификация и обнаружение фальсификации продуктов животного происхождения

Идентификация и обнаружение фальсификации продуктов животного происхождения Инструменты и принадлежности сварщика

Инструменты и принадлежности сварщика Sales

Sales Тематический парк. 1С Hello Kitty. План по проекту

Тематический парк. 1С Hello Kitty. План по проекту Лексика языка Java

Лексика языка Java Sport tourism

Sport tourism Хаттама Хаттама

Хаттама Хаттама ИНФОРМАЦИОННОЕ ОБЕСПЕЧЕНИЕ РЫНКА ЦЕННЫХ БУМАГ Финансовая информация в деловой прессе Фондовые индексы Рейтинги ценных бума

ИНФОРМАЦИОННОЕ ОБЕСПЕЧЕНИЕ РЫНКА ЦЕННЫХ БУМАГ Финансовая информация в деловой прессе Фондовые индексы Рейтинги ценных бума Палитра души

Палитра души Инерциальные навигационные системы. (Тема 3)

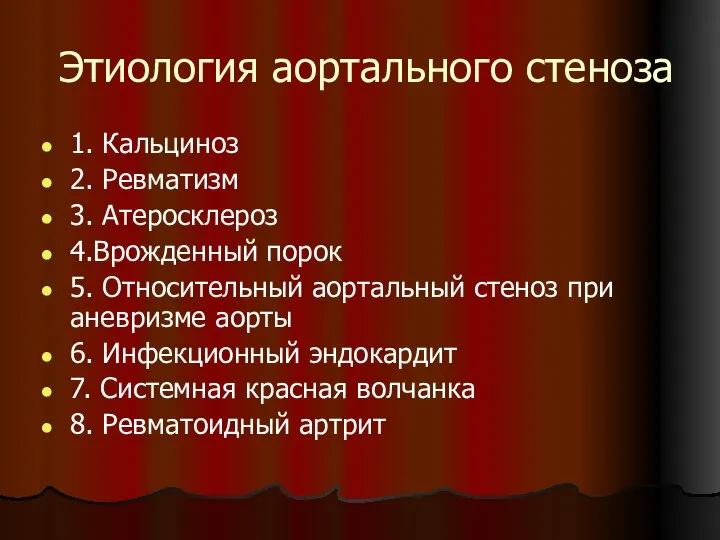

Инерциальные навигационные системы. (Тема 3) Аортальные пороки (packed)

Аортальные пороки (packed) «Музеи в орбите учебно-воспитательного процесса в начальной школе: эффекты и феномены»

«Музеи в орбите учебно-воспитательного процесса в начальной школе: эффекты и феномены» Основные формы внеурочной физкультурно-спортивной деятельности

Основные формы внеурочной физкультурно-спортивной деятельности Экономическое развитие региона в условиях выхода из мирового финансового кризиса Конкурс творческих работ студентов гр. 44БД спе

Экономическое развитие региона в условиях выхода из мирового финансового кризиса Конкурс творческих работ студентов гр. 44БД спе Ұйымда жеке тұлғалық мінез-құлықтың ерекшелігі, когнитивті диссонанс

Ұйымда жеке тұлғалық мінез-құлықтың ерекшелігі, когнитивті диссонанс Вступ до спортивної морфології

Вступ до спортивної морфології Гетто Воркаут

Гетто Воркаут Здоровьесберегающие технологии

Здоровьесберегающие технологии Рисование в технике Граттаж

Рисование в технике Граттаж Статистический анализ энергетического рынка Европы

Статистический анализ энергетического рынка Европы Устами младенца - презентация для начальной школы_

Устами младенца - презентация для начальной школы_ Инженерная графика. Введение

Инженерная графика. Введение Анализ педагогической деятельности

Анализ педагогической деятельности