Содержание

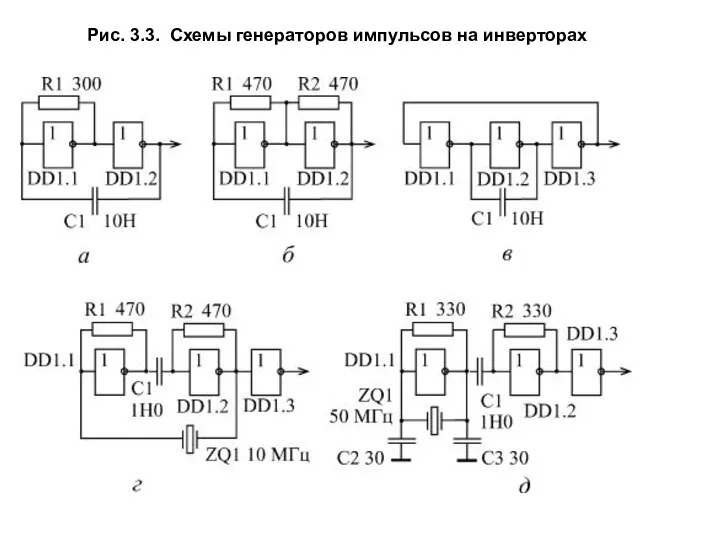

- 2. Рис. 3.3. Схемы генераторов импульсов на инверторах

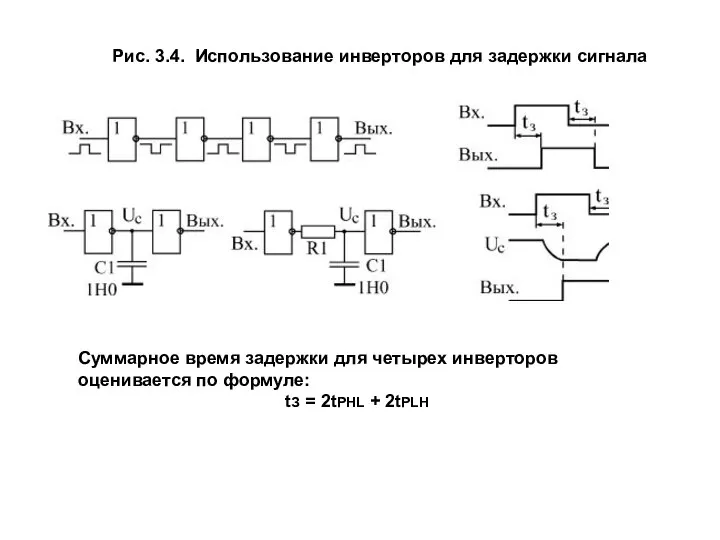

- 3. Рис. 3.4. Использование инверторов для задержки сигнала Суммарное время задержки для четырех инверторов оценивается по формуле:

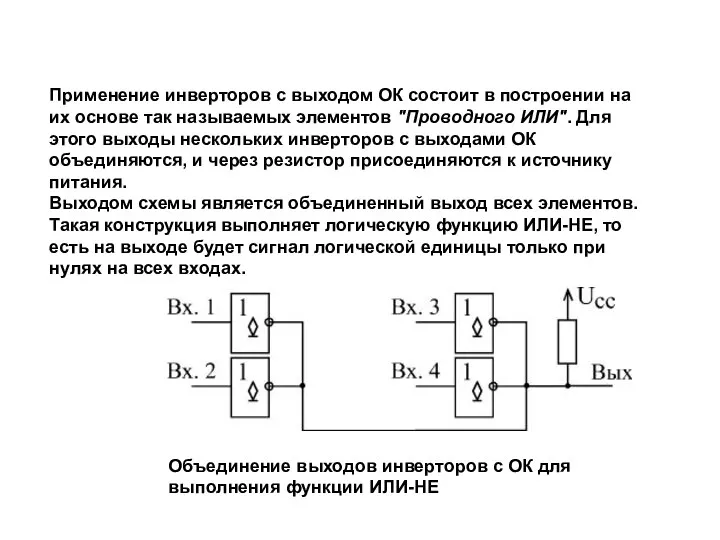

- 4. Применение инверторов с выходом ОК состоит в построении на их основе так называемых элементов "Проводного ИЛИ".

- 5. Повторители и буферы Выполняют следующие функции: увеличение нагрузочной способности сигнала, то есть позволяют подавать один сигнал

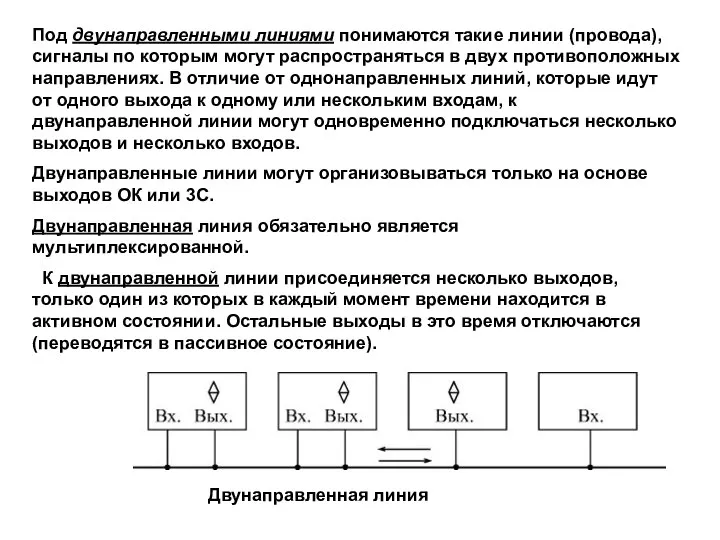

- 6. Под двунаправленными линиями понимаются такие линии (провода), сигналы по которым могут распространяться в двух противоположных направлениях.

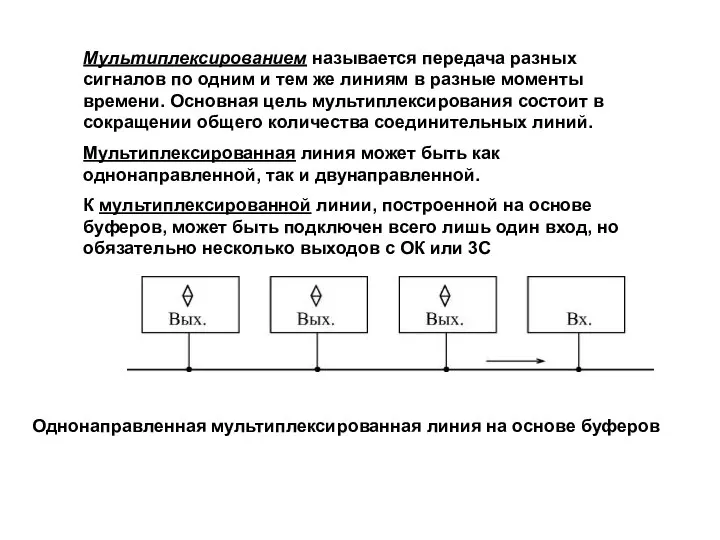

- 7. Мультиплексированием называется передача разных сигналов по одним и тем же линиям в разные моменты времени. Основная

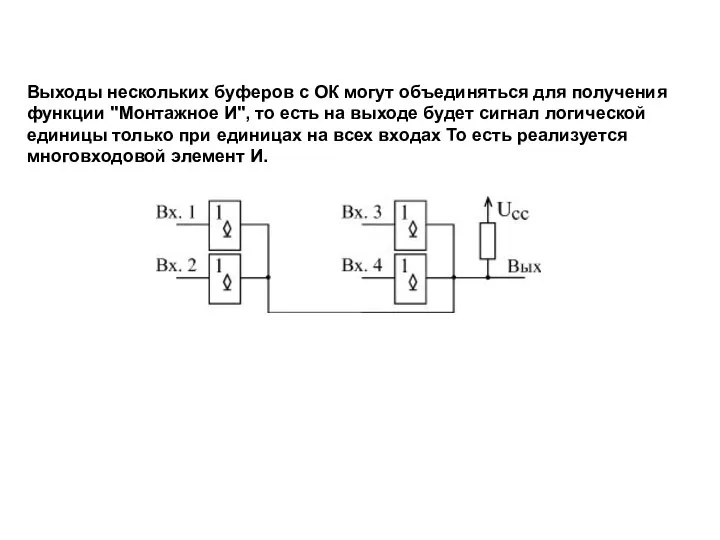

- 8. Выходы нескольких буферов с ОК могут объединяться для получения функции "Монтажное И", то есть на выходе

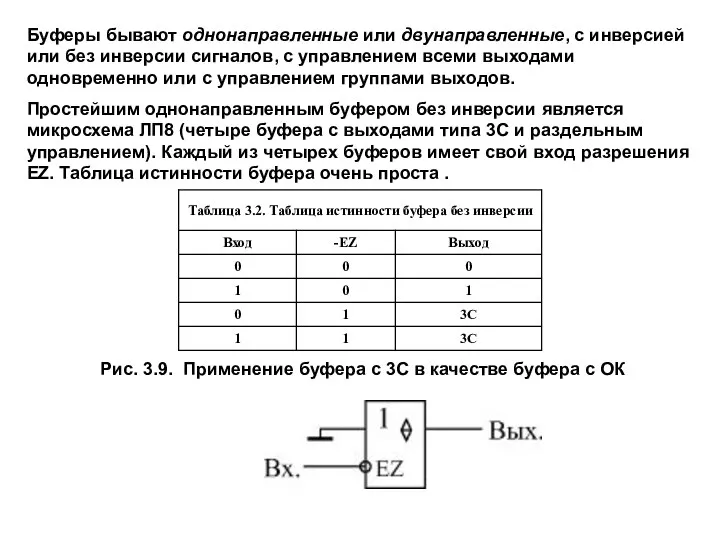

- 9. Буферы бывают однонаправленные или двунаправленные, с инверсией или без инверсии сигналов, с управлением всеми выходами одновременно

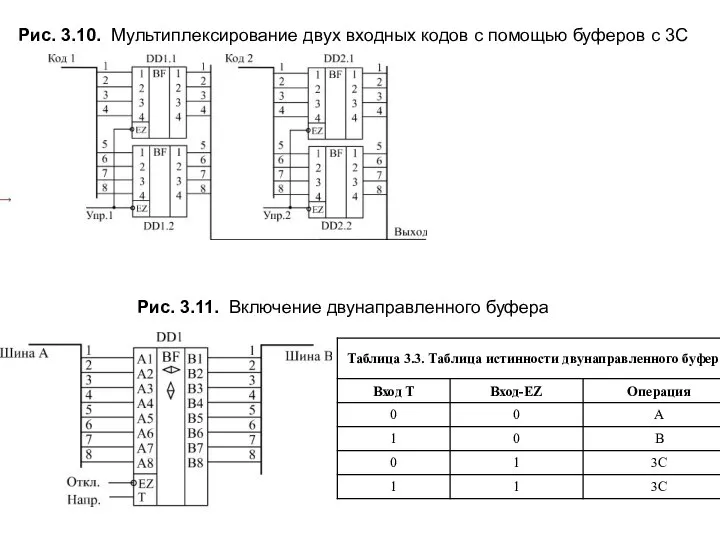

- 10. Рис. 3.10. Мультиплексирование двух входных кодов с помощью буферов с 3С Рис. 3.11. Включение двунаправленного буфера

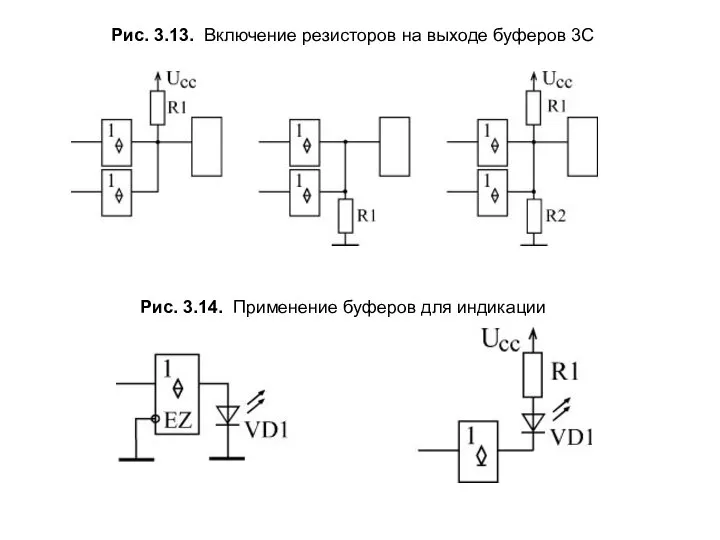

- 11. Рис. 3.13. Включение резисторов на выходе буферов 3С Рис. 3.14. Применение буферов для индикации

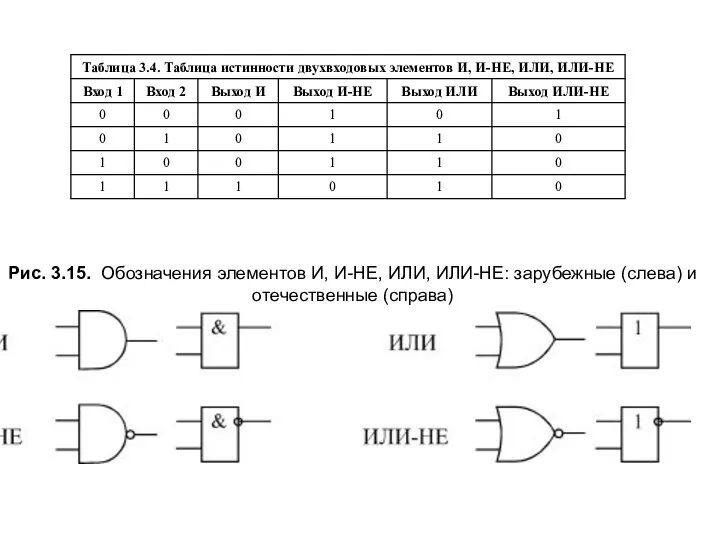

- 12. Рис. 3.15. Обозначения элементов И, И-НЕ, ИЛИ, ИЛИ-НЕ: зарубежные (слева) и отечественные (справа)

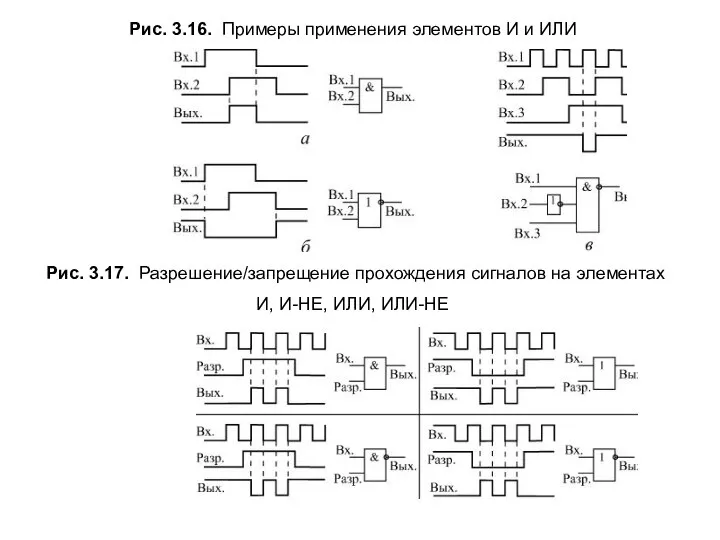

- 13. Рис. 3.17. Разрешение/запрещение прохождения сигналов на элементах И, И-НЕ, ИЛИ, ИЛИ-НЕ Рис. 3.16. Примеры применения элементов

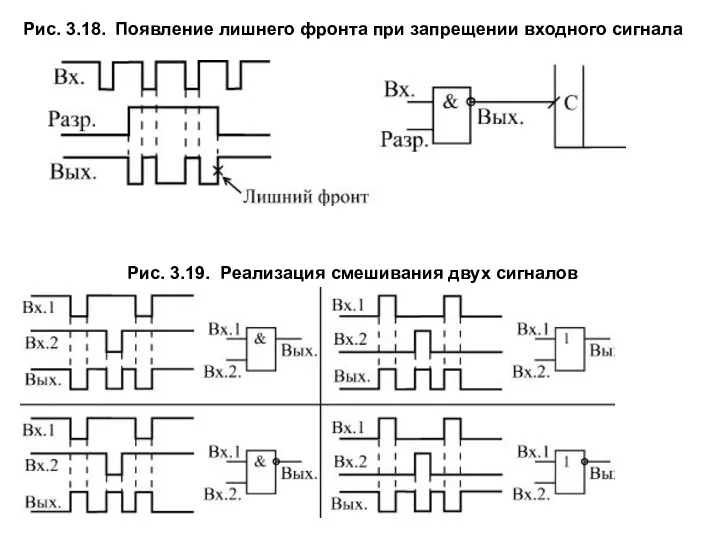

- 14. Рис. 3.19. Реализация смешивания двух сигналов Рис. 3.18. Появление лишнего фронта при запрещении входного сигнала

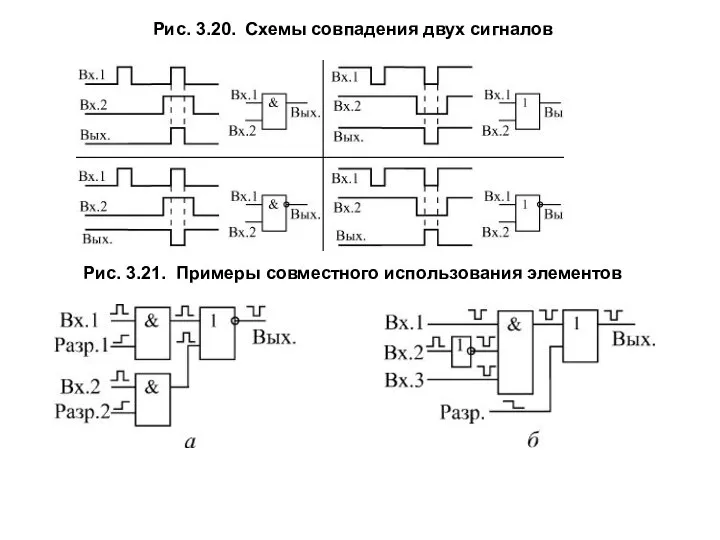

- 15. Рис. 3.21. Примеры совместного использования элементов Рис. 3.20. Схемы совпадения двух сигналов

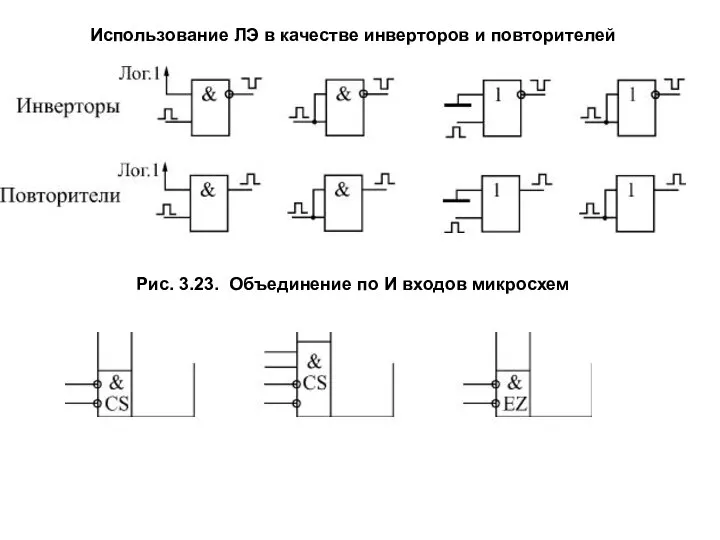

- 16. Использование ЛЭ в качестве инверторов и повторителей Рис. 3.23. Объединение по И входов микросхем

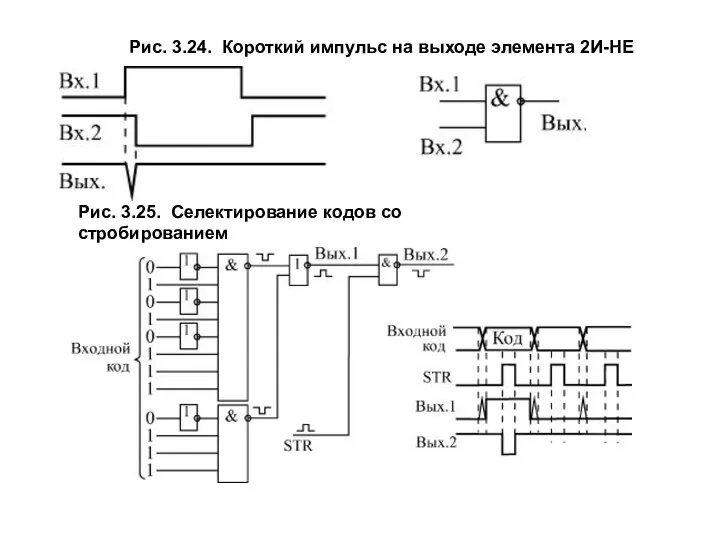

- 17. Рис. 3.24. Короткий импульс на выходе элемента 2И-НЕ Рис. 3.25. Селектирование кодов со стробированием

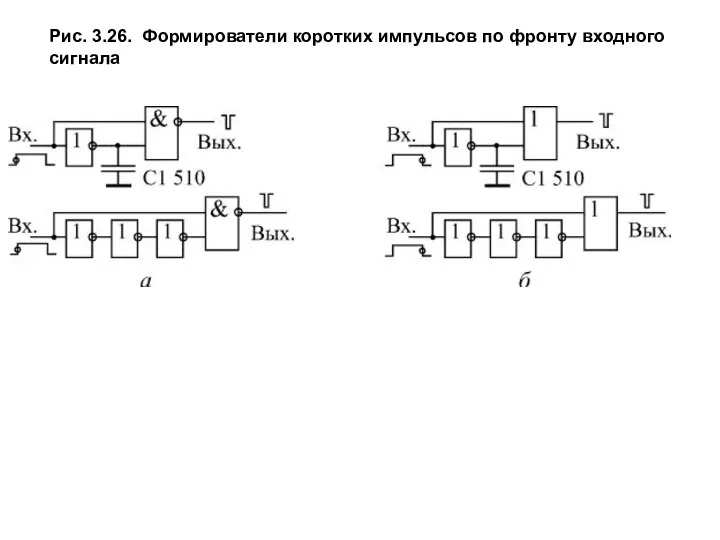

- 18. Рис. 3.26. Формирователи коротких импульсов по фронту входного сигнала

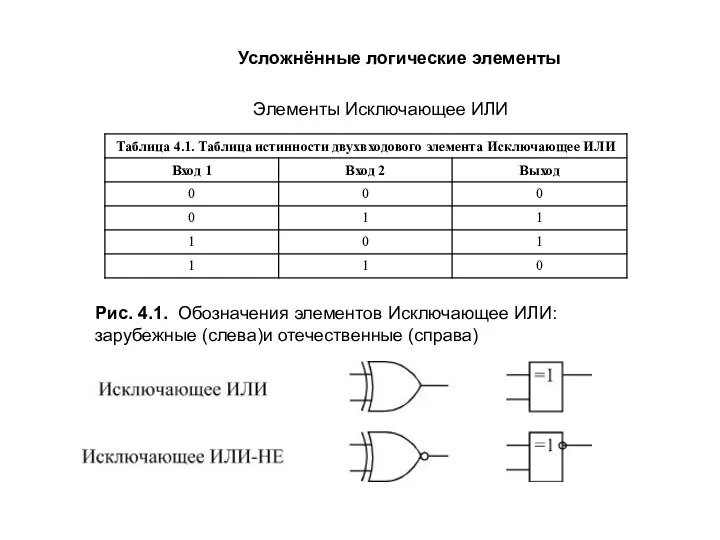

- 19. Усложнённые логические элементы Элементы Исключающее ИЛИ Рис. 4.1. Обозначения элементов Исключающее ИЛИ: зарубежные (слева)и отечественные (справа)

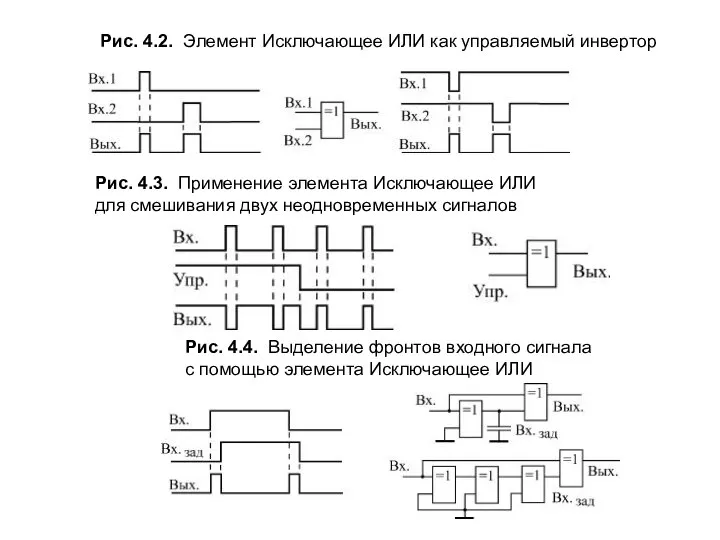

- 20. Рис. 4.2. Элемент Исключающее ИЛИ как управляемый инвертор Рис. 4.3. Применение элемента Исключающее ИЛИ для смешивания

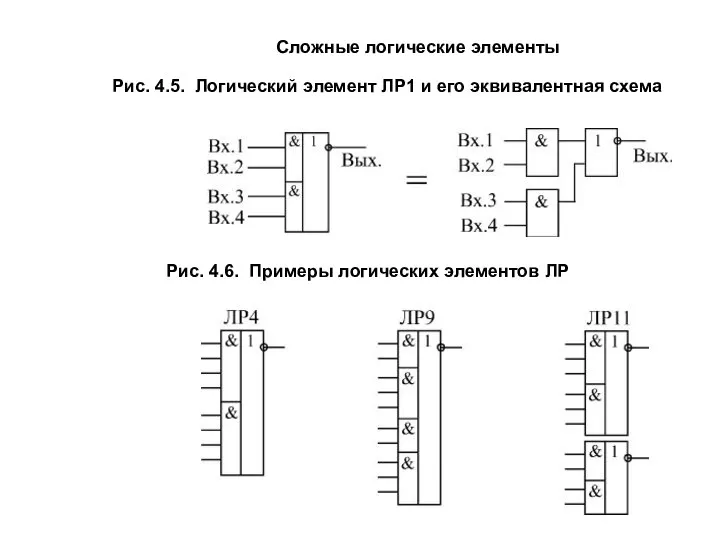

- 21. Сложные логические элементы Рис. 4.5. Логический элемент ЛР1 и его эквивалентная схема Рис. 4.6. Примеры логических

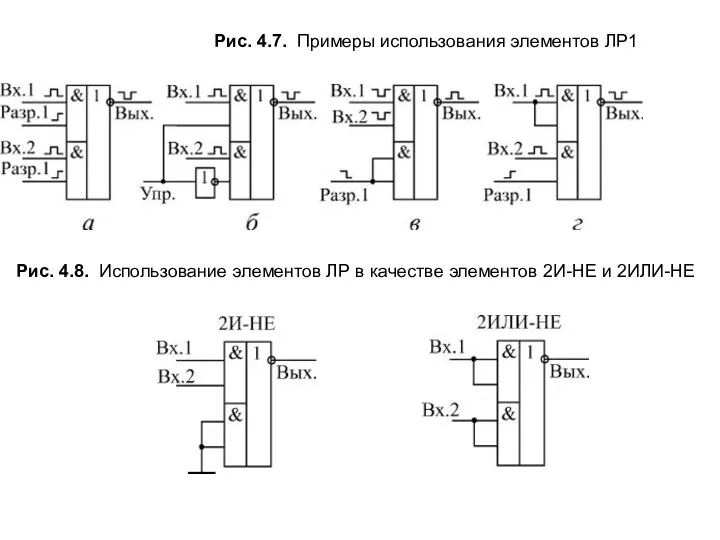

- 22. Рис. 4.7. Примеры использования элементов ЛР1 Рис. 4.8. Использование элементов ЛР в качестве элементов 2И-НЕ и

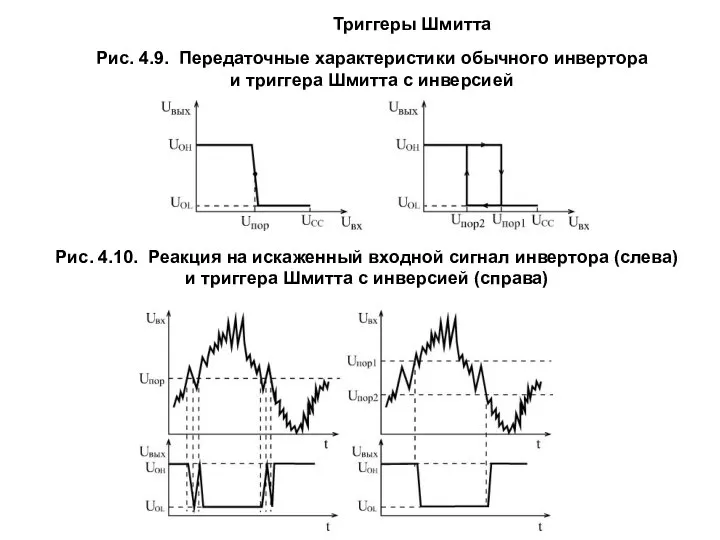

- 23. Триггеры Шмитта Рис. 4.9. Передаточные характеристики обычного инвертора и триггера Шмитта с инверсией Рис. 4.10. Реакция

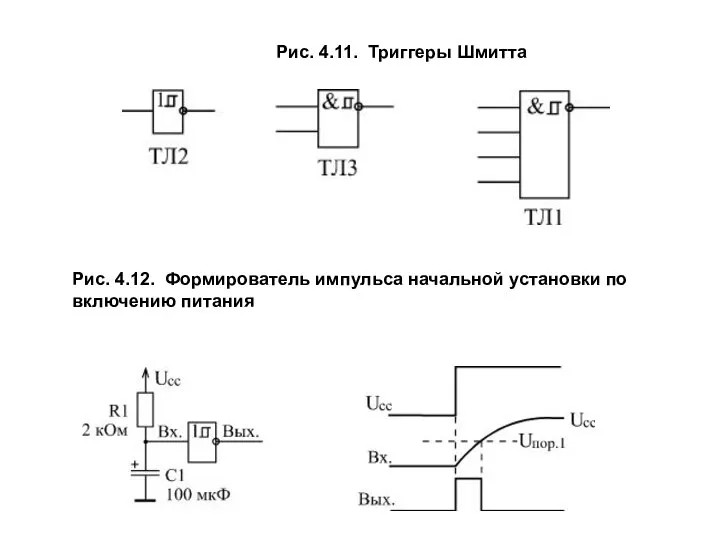

- 24. Рис. 4.11. Триггеры Шмитта Рис. 4.12. Формирователь импульса начальной установки по включению питания

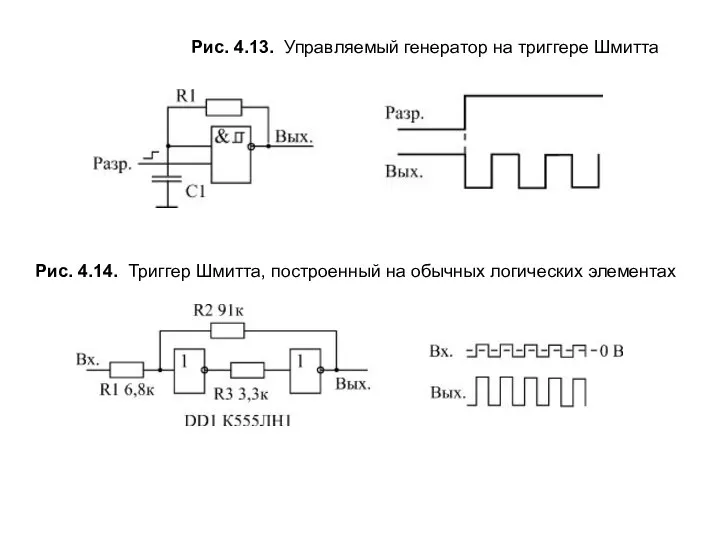

- 25. Рис. 4.13. Управляемый генератор на триггере Шмитта Рис. 4.14. Триггер Шмитта, построенный на обычных логических элементах

- 27. Скачать презентацию

МУНИЦИПАЛЬНОЕ ОБЩЕОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ «СРЕДНЯЯ ОБЩЕОБРАЗОВАТЕЛЬНАЯ ШКОЛА №5» ПРОЕКТ «Рыболовство: традиция и совр

МУНИЦИПАЛЬНОЕ ОБЩЕОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ «СРЕДНЯЯ ОБЩЕОБРАЗОВАТЕЛЬНАЯ ШКОЛА №5» ПРОЕКТ «Рыболовство: традиция и совр Нарушения менструальной функции. Нейроэндокринные синдромы в гинекологии.

Нарушения менструальной функции. Нейроэндокринные синдромы в гинекологии.  Единицы величин

Единицы величин Командный вид спорта мини-футбол

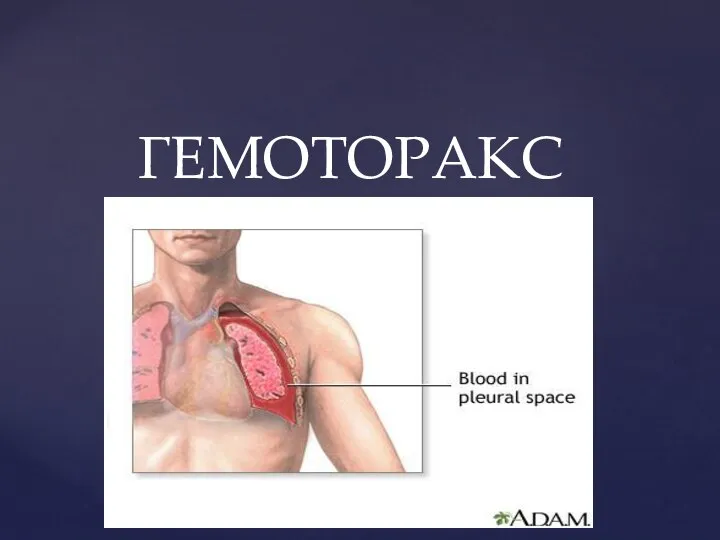

Командный вид спорта мини-футбол ГЕМОТОРАКС

ГЕМОТОРАКС  Керамические виниры Работа выполнена Моськиной Е.Н.265группа

Керамические виниры Работа выполнена Моськиной Е.Н.265группа БЖД

БЖД Микропроцессорные системы

Микропроцессорные системы Информационное обеспечение фарм бизнеса

Информационное обеспечение фарм бизнеса Калифорнийский Университет в Беркли

Калифорнийский Университет в Беркли ШКОЛА ЧЕЛОВЕЧЕСКИХ ОТНОШЕНИЙ Выполнили студентки 1 курса экономического факультета группы М 111 Б Русакова Ксения и Федорова

ШКОЛА ЧЕЛОВЕЧЕСКИХ ОТНОШЕНИЙ Выполнили студентки 1 курса экономического факультета группы М 111 Б Русакова Ксения и Федорова  Презентация разметка

Презентация разметка Программа на языке QBasic. Реализация линейного алгоритма на QBASIC

Программа на языке QBasic. Реализация линейного алгоритма на QBASIC ТЭД НБ-418К и ТЛ-2К1

ТЭД НБ-418К и ТЛ-2К1 Фотодело. Направление света

Фотодело. Направление света Презентация Разработка предложений по борьбе с коррупцией в таможенных администрациях на основе анализа международного опыта

Презентация Разработка предложений по борьбе с коррупцией в таможенных администрациях на основе анализа международного опыта  Отчёт о стажировке по программированию

Отчёт о стажировке по программированию Методы газотермического напыления

Методы газотермического напыления Понятие о космосе. Исследование космоса - презентация для начальной школы_

Понятие о космосе. Исследование космоса - презентация для начальной школы_ Система защиты персональных данных

Система защиты персональных данных Образовательная программа Нашей Новой Школы

Образовательная программа Нашей Новой Школы Итоги проведения проекта: Ночь Святого Патрика

Итоги проведения проекта: Ночь Святого Патрика Презентация на тему "Родительская любовь и Воспитание" - скачать презентации по Педагогике

Презентация на тему "Родительская любовь и Воспитание" - скачать презентации по Педагогике Скелет «работы

Скелет «работы Достоевский Фёдор Михайлович 1821 – 1881

Достоевский Фёдор Михайлович 1821 – 1881 Индексный метод

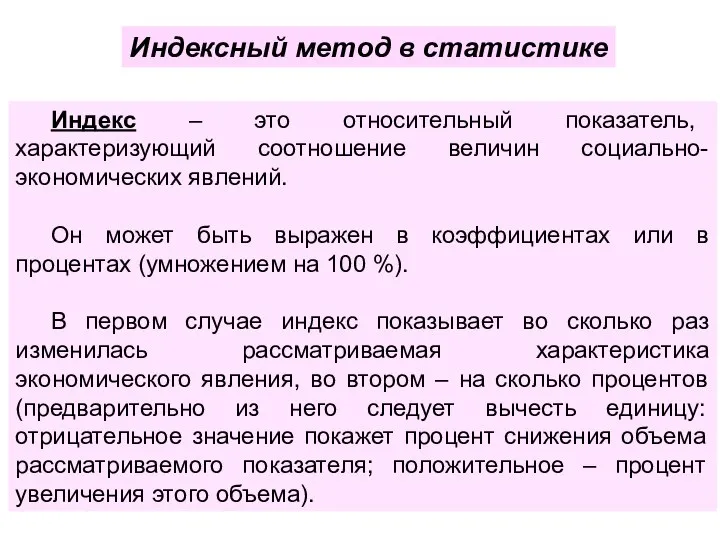

Индексный метод  Значение целей и планов

Значение целей и планов Религиозность

Религиозность