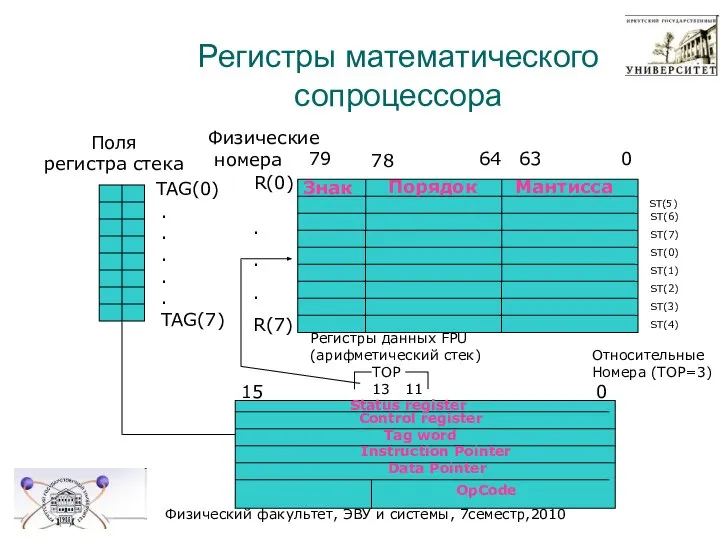

Младший байт регистра состояния содержит флажки особых случаев сопроцессора: переполнение стека,

потеря точности, потеря значащих разрядов, численное переполнение, деление на ноль, денормализация, недействительная операция. Если соответствующий особый случай возник и не был замаскирован (в слове управления), это приведет к генерации центральным процессором особого случая сопроцессора (#16).

Младшее слово регистра управления содержит биты масок особых случаев. Сопроцессор допускает индивидуальное маскирование особых случаев. Если тот или иной особый случай замаскирован, при возникновении соответствующей ситуации сопроцессор выполняет некоторые заранее определенные внутренние действия, которые зачастую приемлемы для большинства применений. Например, если замаскирован особый случай деления на ноль, то выполнение операции 85,32/0 даст результат + ∞.

Старшее слово регистра управления содержит два поля: управление точностью PC (биты 8 и 9) и управление округлением RC (биты 10 и 11). Биты управления точностью можно использовать для понижения точности вычислений. По умолчанию используется расширенная точность (PC = 112), можно также использовать двойную точность (PC = 102) и одинарную точность (PC = 002)

Физический факультет, ЭВУ и системы, 7семестр,2010

День грамотности Внеклассное мероприятие для 4 класса Учитель начальных классов МОУ «БСОШ№96» Заостровных Т.Н.

День грамотности Внеклассное мероприятие для 4 класса Учитель начальных классов МОУ «БСОШ№96» Заостровных Т.Н. Действие как процесс Исследовательская работа

Действие как процесс Исследовательская работа Зона степей. Животный и растительный мир степей. Учитель начальных классов МОУ «Лицей №22» Новикова Н.Б.

Зона степей. Животный и растительный мир степей. Учитель начальных классов МОУ «Лицей №22» Новикова Н.Б.  словарное слово болото 3 класс УМК ПНШ - презентация для начальной школы

словарное слово болото 3 класс УМК ПНШ - презентация для начальной школы Графика языка паскаль

Графика языка паскаль Перспективный двигатель внутреннего сгорания

Перспективный двигатель внутреннего сгорания Исследовательская работа Тема: «Царица сибирских полей» Выволнил: Перепёлкин Матвей,

Исследовательская работа Тема: «Царица сибирских полей» Выволнил: Перепёлкин Матвей,  Художественный образ

Художественный образ Скандинавская мифология

Скандинавская мифология  Новый Раменский. Планировочные решения

Новый Раменский. Планировочные решения Математики в годы Великой Отечественной войны

Математики в годы Великой Отечественной войны Технологія матеріалів

Технологія матеріалів Учёт конфиденциальных документов

Учёт конфиденциальных документов Основы логики

Основы логики Как рисовать морскую черепаху - презентация для начальной школы

Как рисовать морскую черепаху - презентация для начальной школы Схема освещения и светосигнальных цепей тепловоза 2ТЭ-116

Схема освещения и светосигнальных цепей тепловоза 2ТЭ-116 Файлы. Типы файлов

Файлы. Типы файлов Общественная организация территориальное общественное самоуправление города Ульяновска «Двор речников»

Общественная организация территориальное общественное самоуправление города Ульяновска «Двор речников» Негативные последствия влияния шума и вибрации на человека и среду обитания

Негативные последствия влияния шума и вибрации на человека и среду обитания Вводная лекция по специальности: товаровед - приемщик ломбарда

Вводная лекция по специальности: товаровед - приемщик ломбарда урок

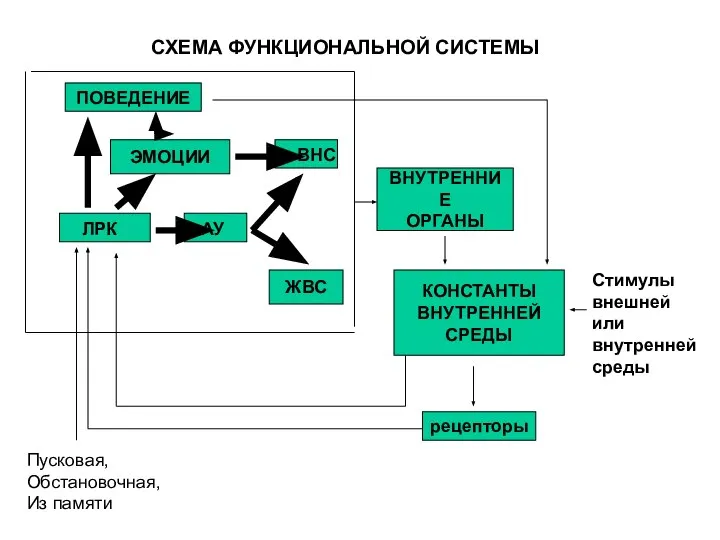

урок Роль реципрокного торможения

Роль реципрокного торможения Биполярные транзисторы

Биполярные транзисторы  Звіт про роботу в конкурсах - презентация для начальной школы_

Звіт про роботу в конкурсах - презентация для начальной школы_ Понятие о стоматологической заболеваемости населения

Понятие о стоматологической заболеваемости населения Тема урока № 10 Доходы. Виды доходов

Тема урока № 10 Доходы. Виды доходов  «Ученик, который учится без желания, это птица без крыльев». Саади

«Ученик, который учится без желания, это птица без крыльев». Саади СРО - саморегулируемые организации

СРО - саморегулируемые организации