Содержание

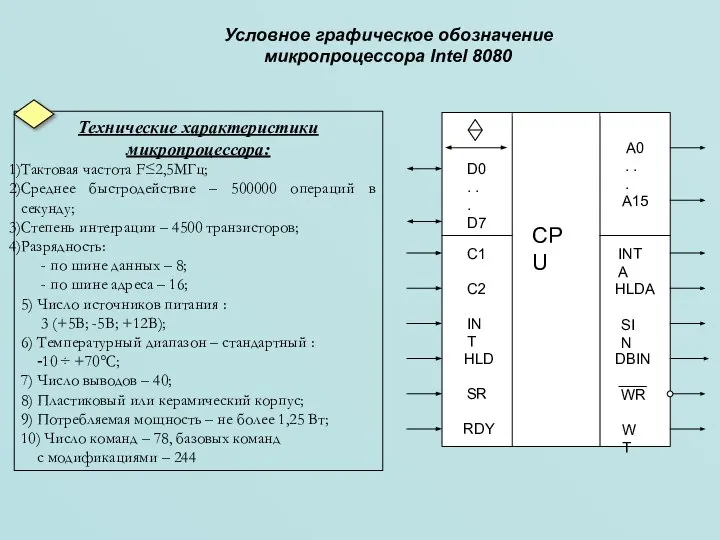

- 2. Технические характеристики микропроцессора: Тактовая частота F≤2,5МГц; Среднее быстродействие – 500000 операций в секунду; Степень интеграции –

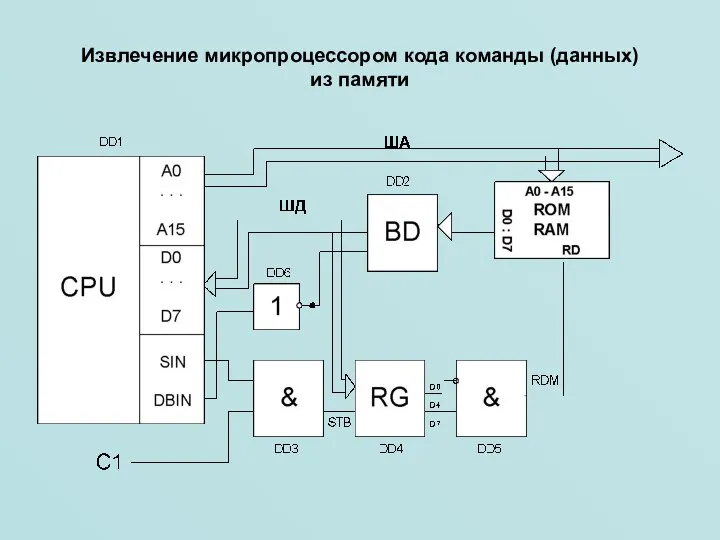

- 3. Извлечение микропроцессором кода команды (данных) из памяти

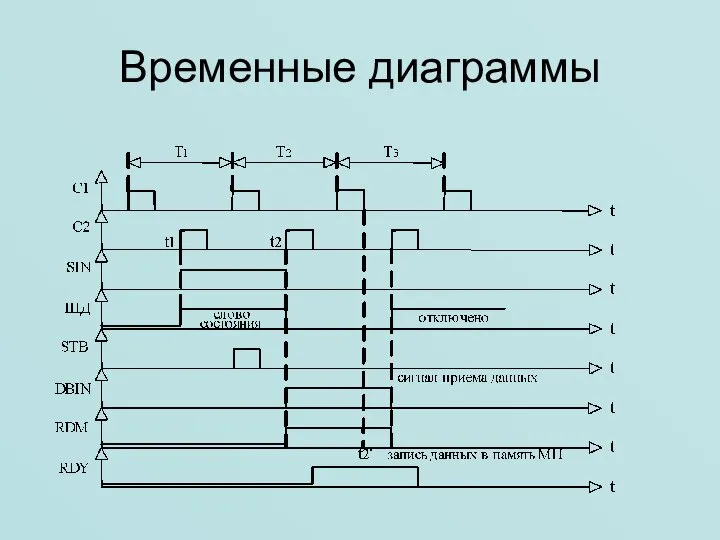

- 4. Временные диаграммы

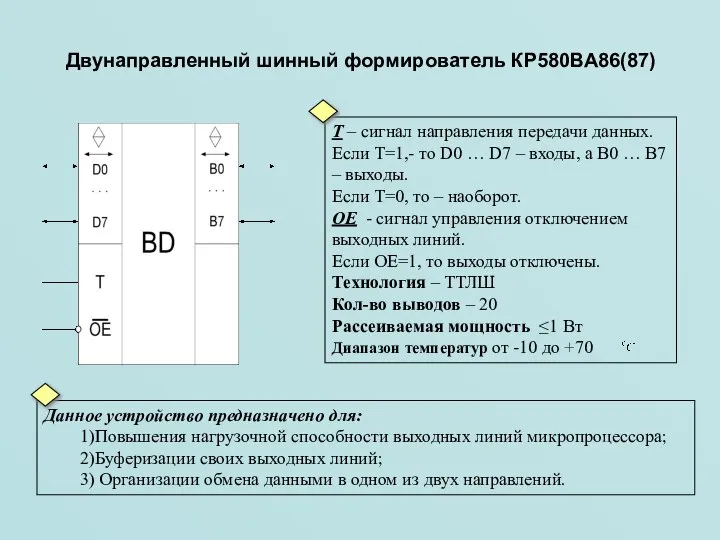

- 5. Двунаправленный шинный формирователь КР580ВА86(87) Данное устройство предназначено для: 1)Повышения нагрузочной способности выходных линий микропроцессора; 2)Буферизации своих

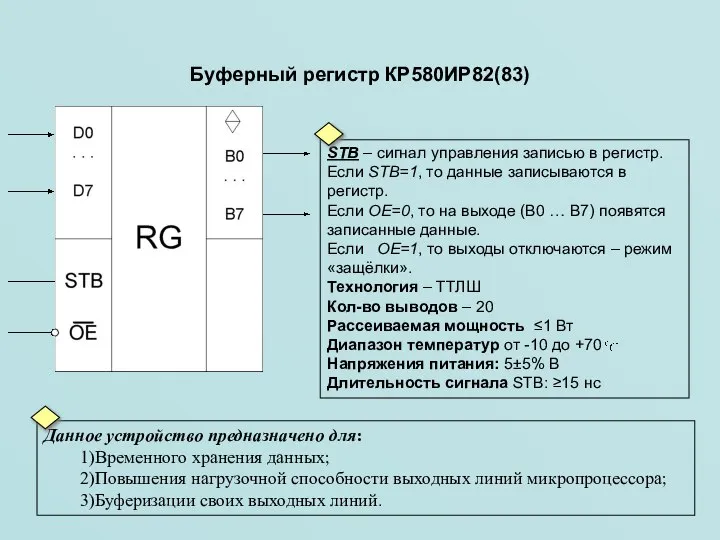

- 6. Буферный регистр КР580ИР82(83) Данное устройство предназначено для: 1)Временного хранения данных; 2)Повышения нагрузочной способности выходных линий микропроцессора;

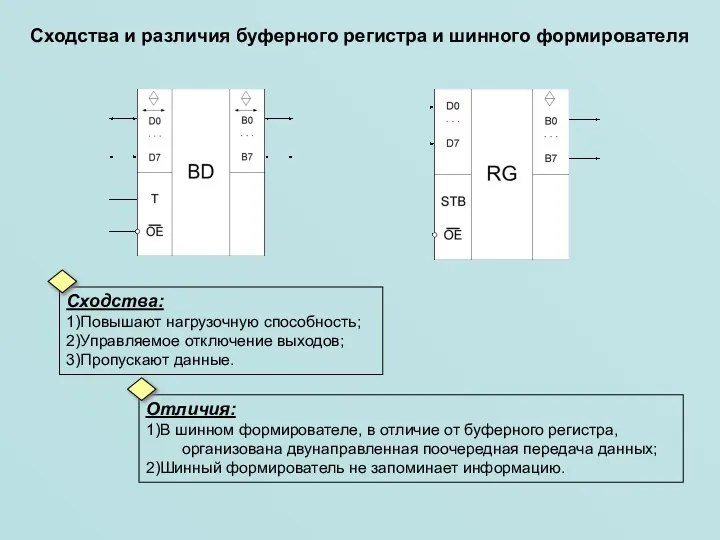

- 7. Сходства и различия буферного регистра и шинного формирователя Сходства: 1)Повышают нагрузочную способность; 2)Управляемое отключение выходов; 3)Пропускают

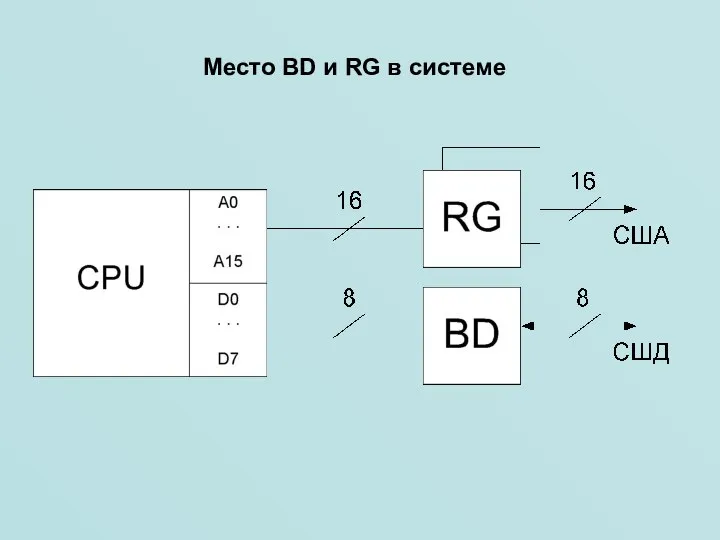

- 8. Место BD и RG в системе

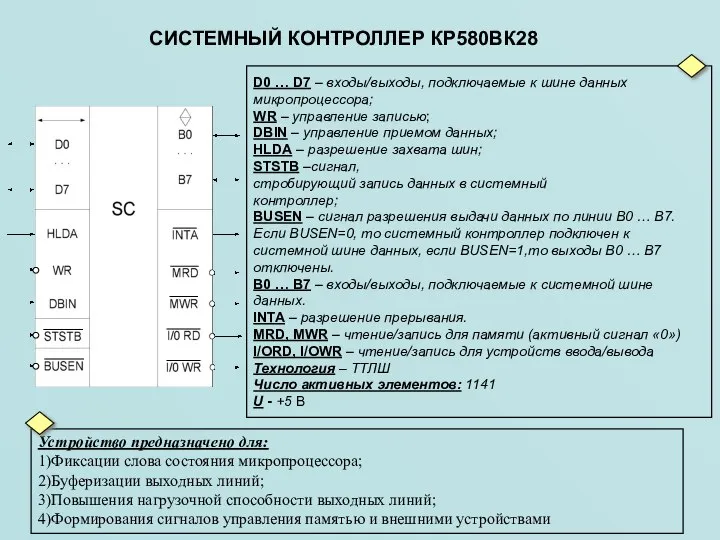

- 9. СИСТЕМНЫЙ КОНТРОЛЛЕР КР580ВК28 D0 … D7 – входы/выходы, подключаемые к шине данных микропроцессора; WR – управление

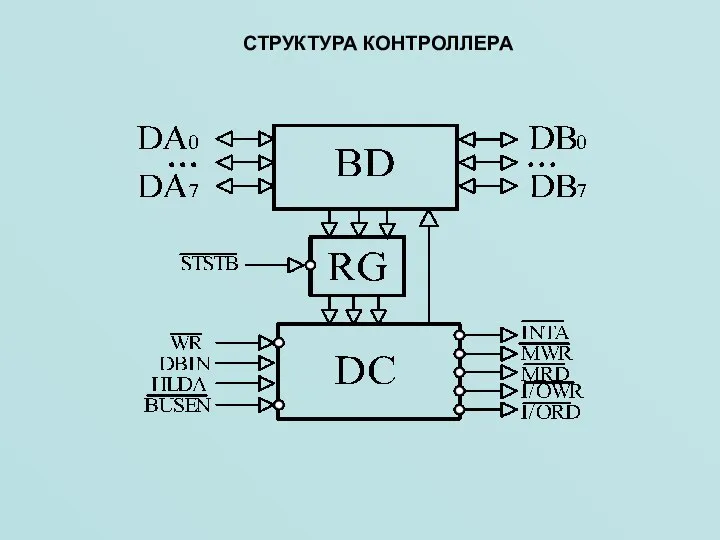

- 10. СТРУКТУРА КОНТРОЛЛЕРА

- 11. ПРОГРАММИРУЕМЫЙ ПАРАЛЛЕЛЬНЫЙ ИНТЕРФЕЙС КР580ВВ55 Основные технические характеристики: 1) NMOP – технология; 2) Корпус с 40 выводами;

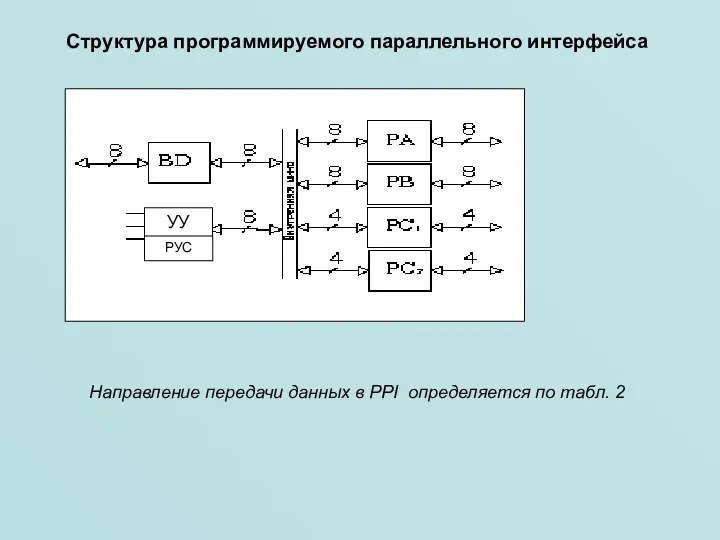

- 12. Структура программируемого параллельного интерфейса Направление передачи данных в PPI определяется по табл. 2

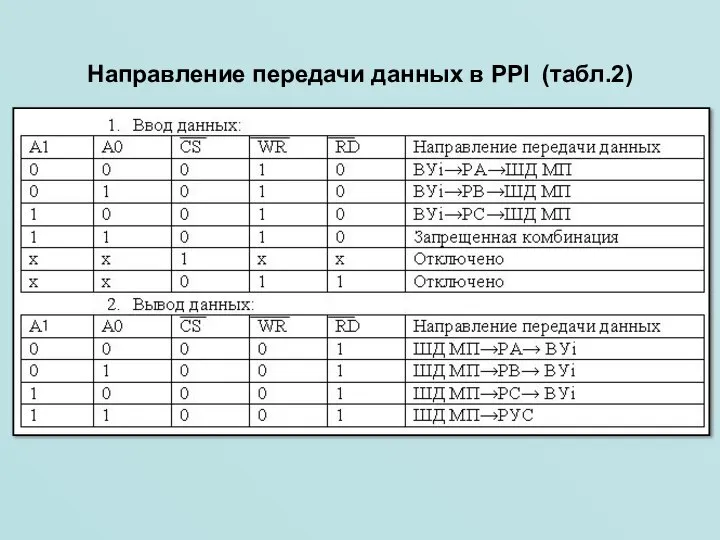

- 13. Направление передачи данных в PPI (табл.2)

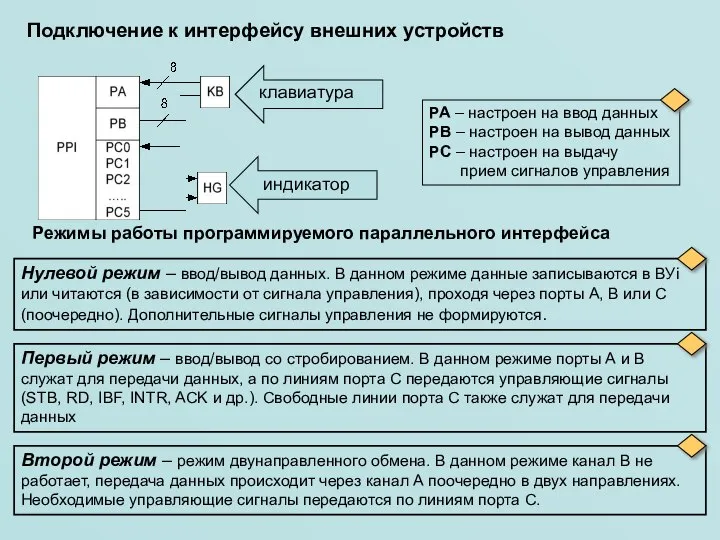

- 14. Подключение к интерфейсу внешних устройств Режимы работы программируемого параллельного интерфейса Нулевой режим – ввод/вывод данных. В

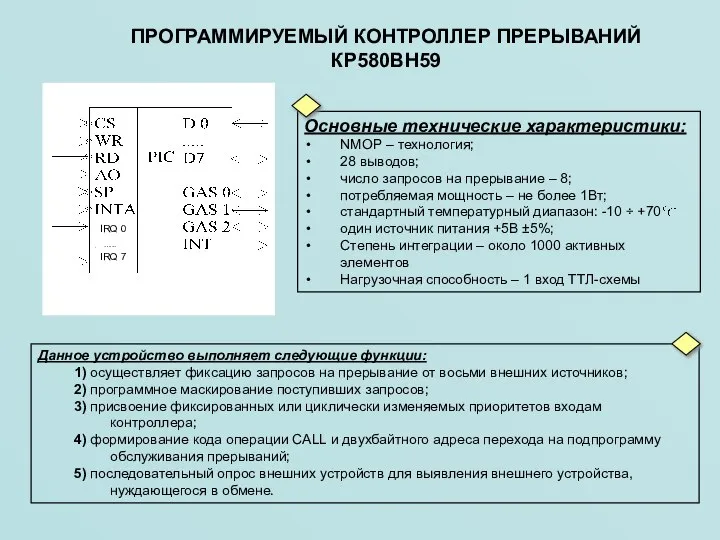

- 15. ПРОГРАММИРУЕМЫЙ КОНТРОЛЛЕР ПРЕРЫВАНИЙ КР580ВН59 Данное устройство выполняет следующие функции: 1) осуществляет фиксацию запросов на прерывание от

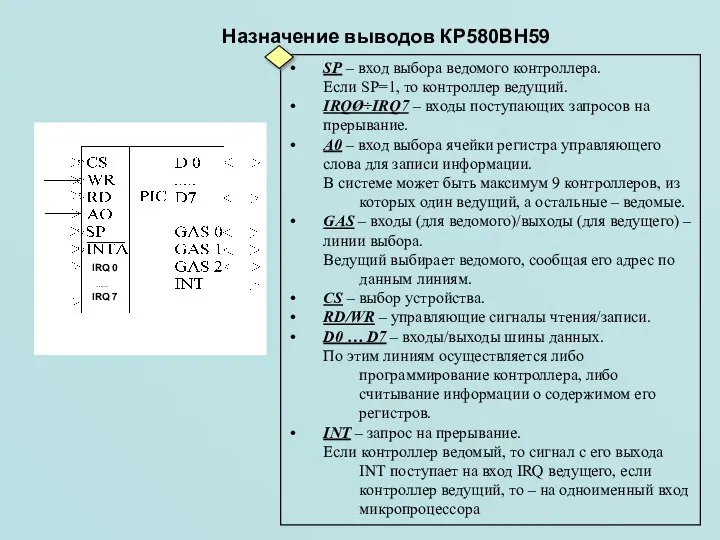

- 16. Назначение выводов КР580ВН59 SP – вход выбора ведомого контроллера. Если SP=1, то контроллер ведущий. IRQØ÷IRQ7 –

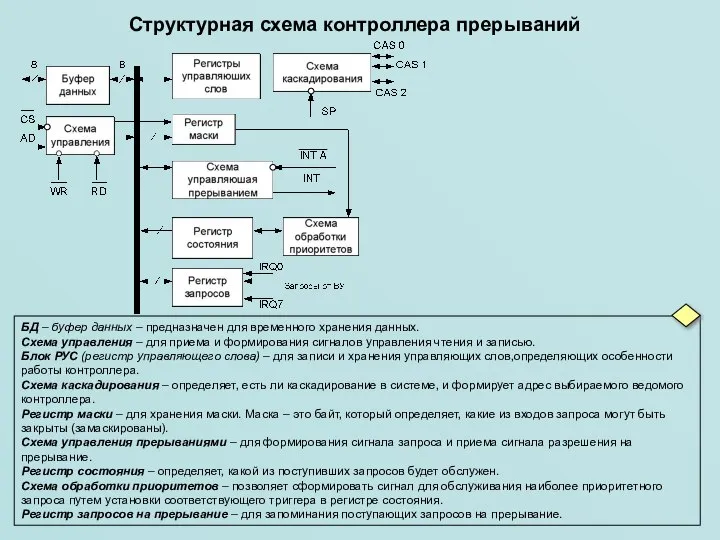

- 17. Структурная схема контроллера прерываний БД – буфер данных – предназначен для временного хранения данных. Схема управления

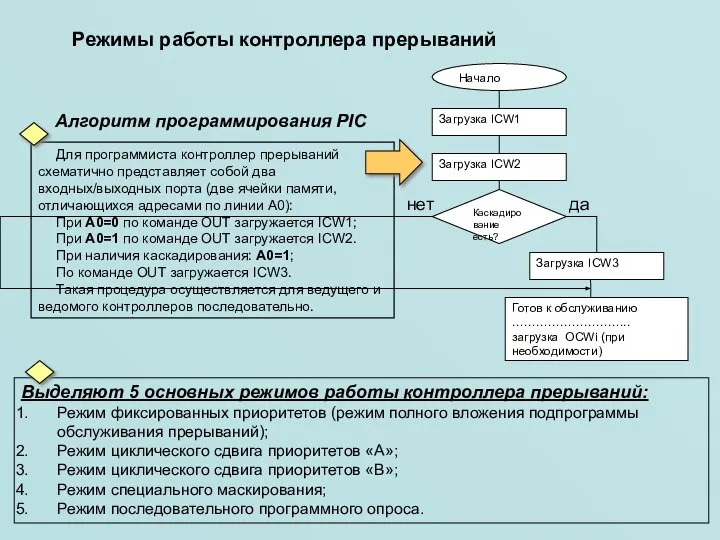

- 18. Режимы работы контроллера прерываний Выделяют 5 основных режимов работы контроллера прерываний: Режим фиксированных приоритетов (режим полного

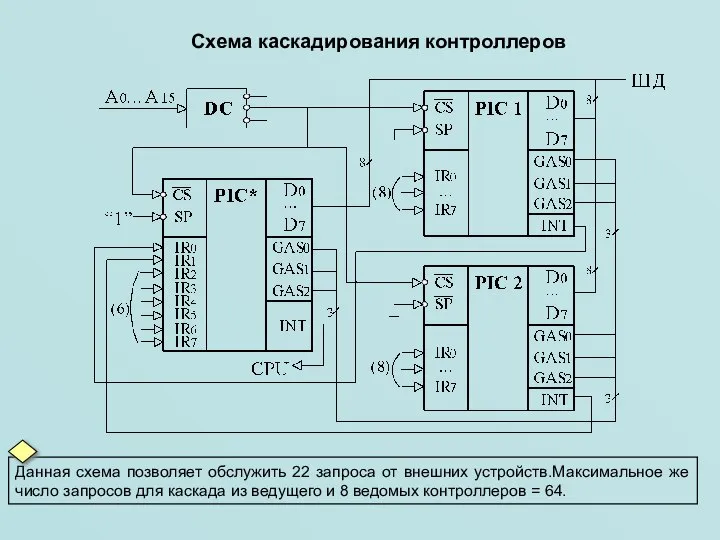

- 19. Схема каскадирования контроллеров Данная схема позволяет обслужить 22 запроса от внешних устройств.Максимальное же число запросов для

- 20. Метод схемного последовательного опроса ВУ

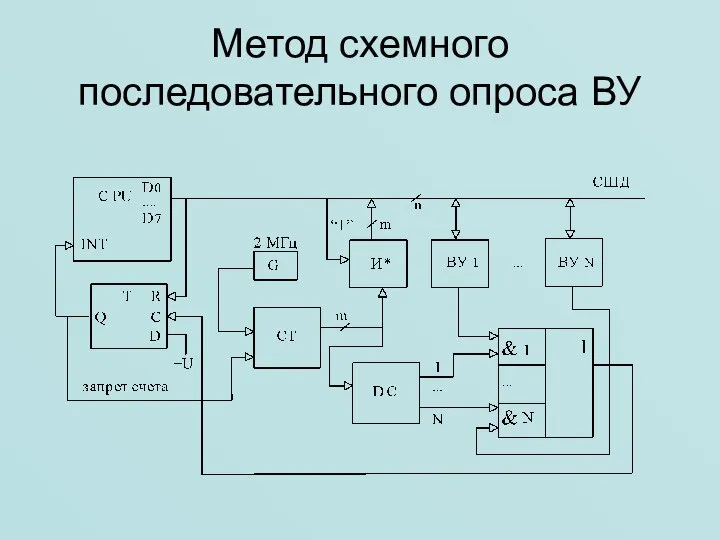

- 21. Схема, реализующая передачу вектора прерываний в МП, не обладающий способностью реакции на векторное прерывание

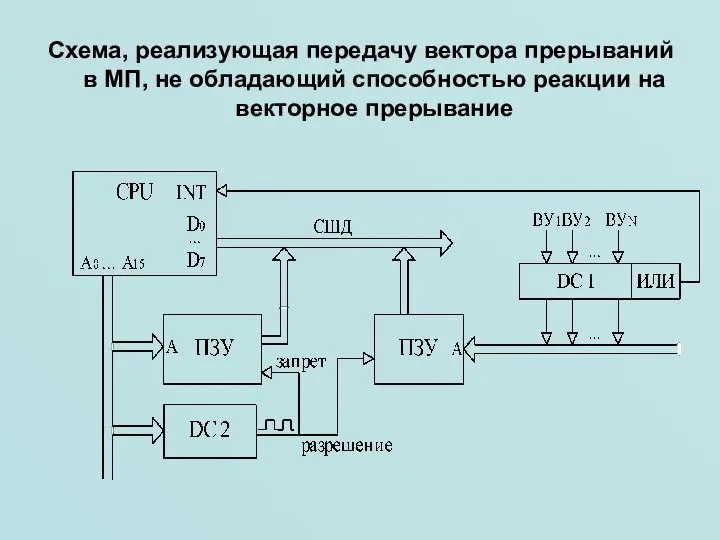

- 22. ПРОГРАММИРУЕМЫЙ ТАЙМЕР КР580ВИ53 Данное устройство предназначено для задания временных интервалов в микропроцессорных системах и может быть

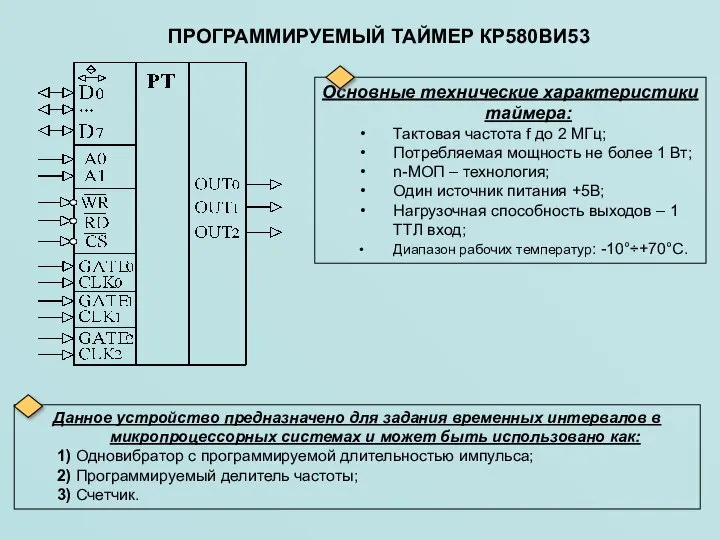

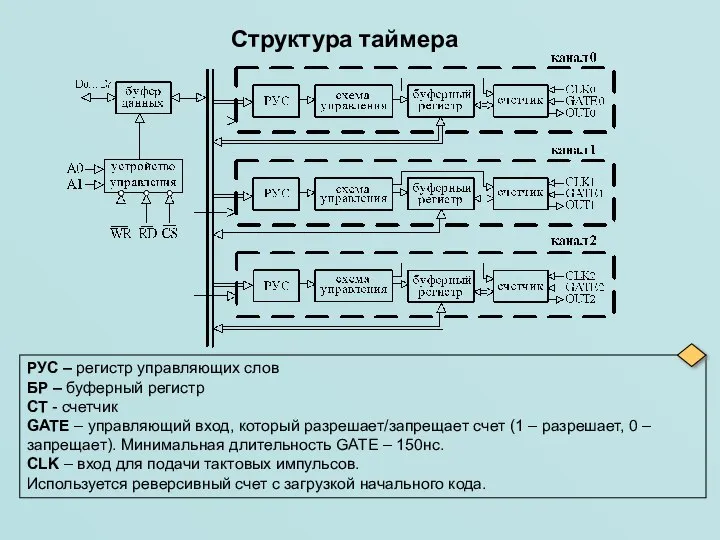

- 23. Структура таймера РУС – регистр управляющих слов БР – буферный регистр СТ - счетчик GATE –

- 24. Структура управляющего слова

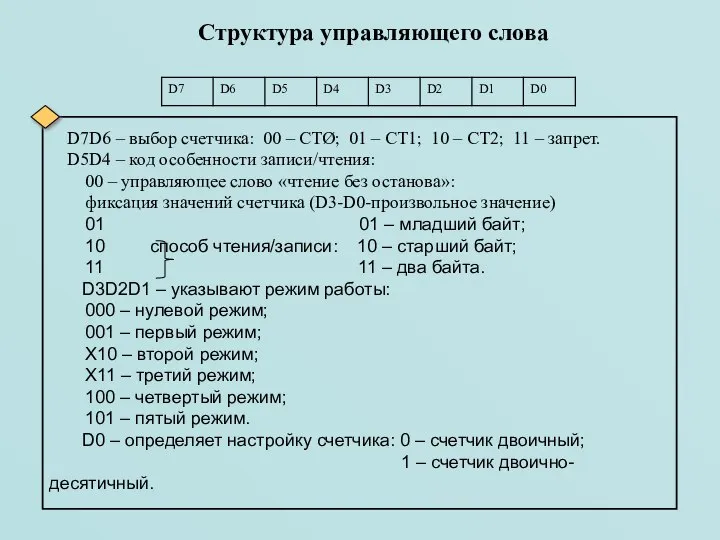

- 25. Таблица передачи данных

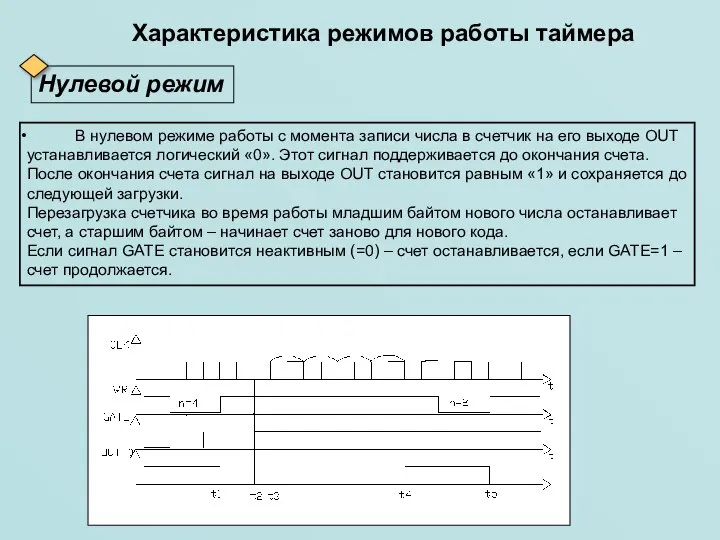

- 26. Характеристика режимов работы таймера Нулевой режим В нулевом режиме работы с момента записи числа в счетчик

- 27. В первом режиме на выходе счетчика формируется отрицательный импульс, длительность которого определяется следующим образом: низкий уровень

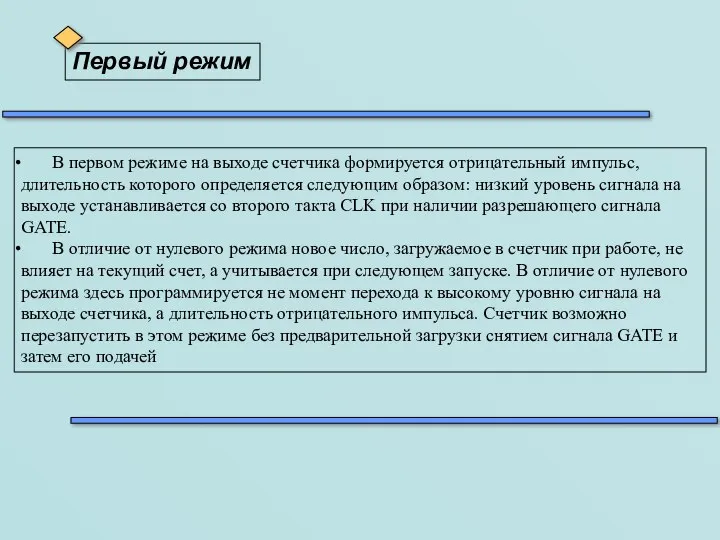

- 28. Второй режим В этом режиме счетчик работает как программируемый делитель частоты. Каждый раз после просчета числа,

- 29. Третий режим В этом режиме счетчик работает как программируемый делитель частоты на два. В данном режиме

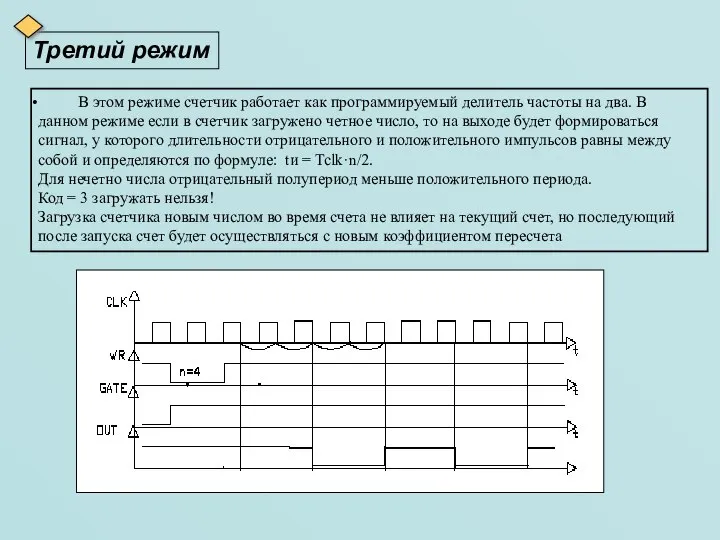

- 30. Четвертый режим В режиме «4» после загрузки кода в счетчик и наличия разрешающего сигнала на входе

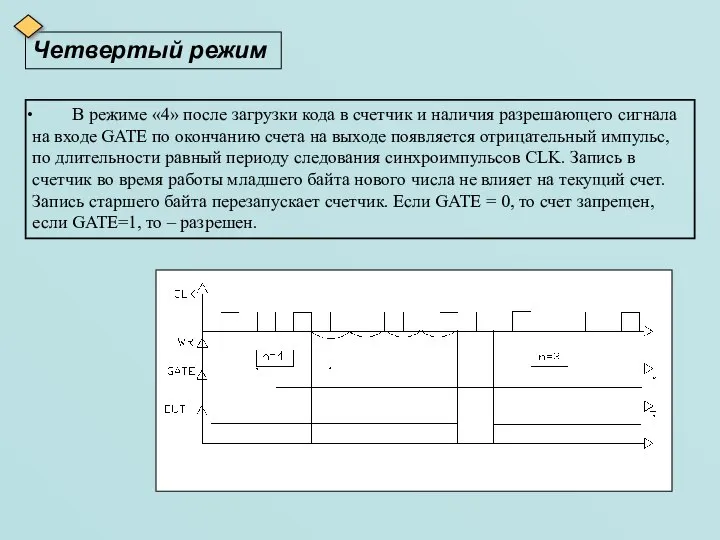

- 31. Пятый режим Отличием данного режима от предыдущего является то, что в нем счетчик является перезапускаемым с

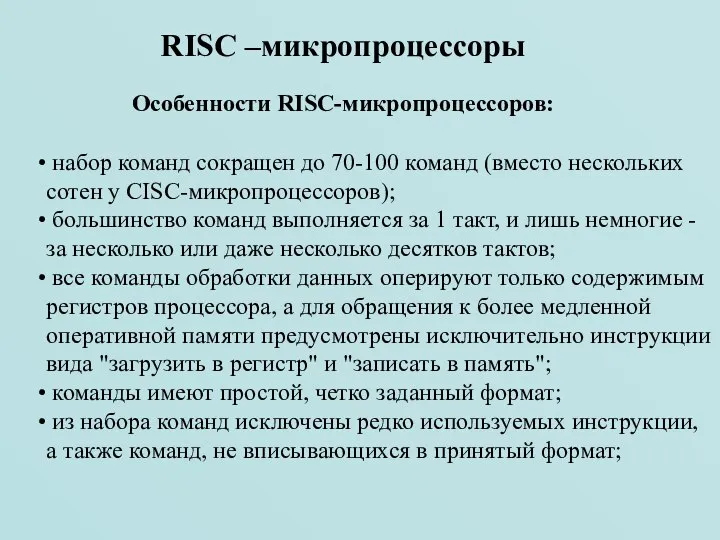

- 32. набор команд сокращен до 70-100 команд (вместо нескольких сотен у CISC-микропроцессоров); большинство команд выполняется за 1

- 33. Наиболее известными RISC-микропроцессоры: SPARC фирмы Sun Microsystems, Alpha 21х64 фирмы Digital EquIPment Rx000 фирмы MIPS Computer

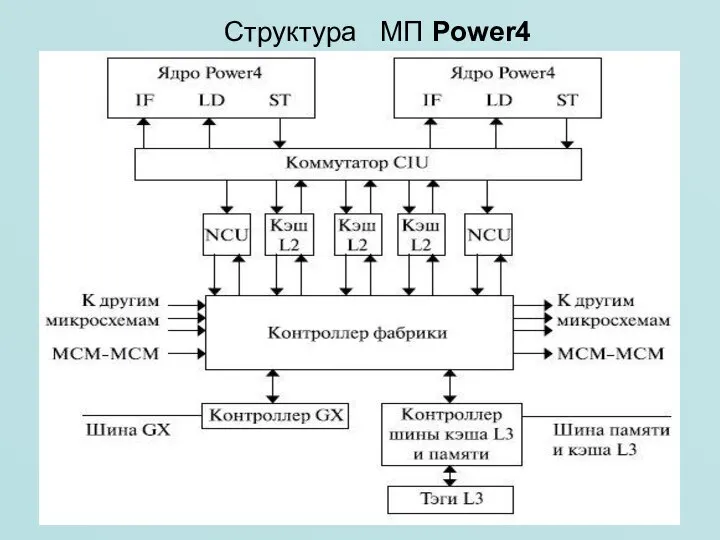

- 34. Структура МП Power4

- 36. Скачать презентацию

Механизм Отражения (Reflection) в C#

Механизм Отражения (Reflection) в C# Презентация на тему "Как правильно выбрать эффективный биологически активный препарат" - скачать презентации по Медицине

Презентация на тему "Как правильно выбрать эффективный биологически активный препарат" - скачать презентации по Медицине ТЕМА 5 БЕЗРАБОТИЦА В пользе безработицы больше всего уверены те, кто не знаком с ней по личному опыту. Джон Гелбрэйт, американски

ТЕМА 5 БЕЗРАБОТИЦА В пользе безработицы больше всего уверены те, кто не знаком с ней по личному опыту. Джон Гелбрэйт, американски Развития психики

Развития психики Рекурсия. Сортировка слиянием. Восходящая сортировка слиянием. Сложность сортировки. Устойчивость сортировок

Рекурсия. Сортировка слиянием. Восходящая сортировка слиянием. Сложность сортировки. Устойчивость сортировок Трансграничные туры социально-культурной направленности

Трансграничные туры социально-культурной направленности Нравственные основы службы в органах внутренних дел. Профессиональная этика сотрудника органов внутренних дел

Нравственные основы службы в органах внутренних дел. Профессиональная этика сотрудника органов внутренних дел Правовые основы охраны труда

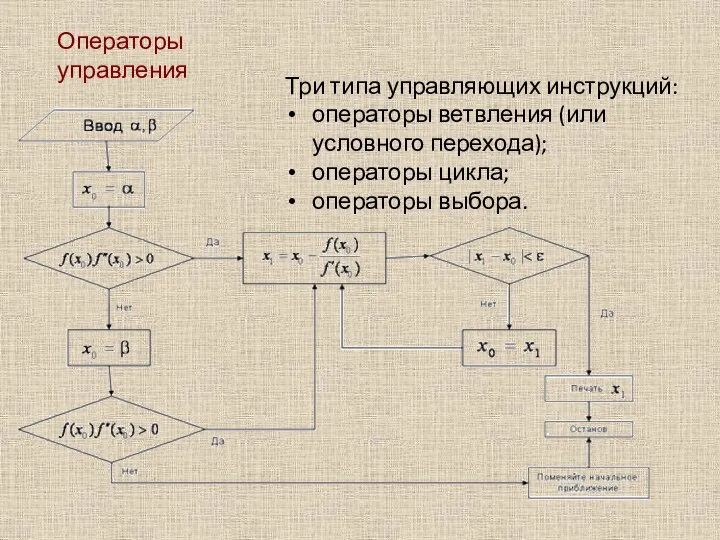

Правовые основы охраны труда Операторы управления

Операторы управления Презентация Цена и общая стоимость контракта Виды цен Определение валюты цены

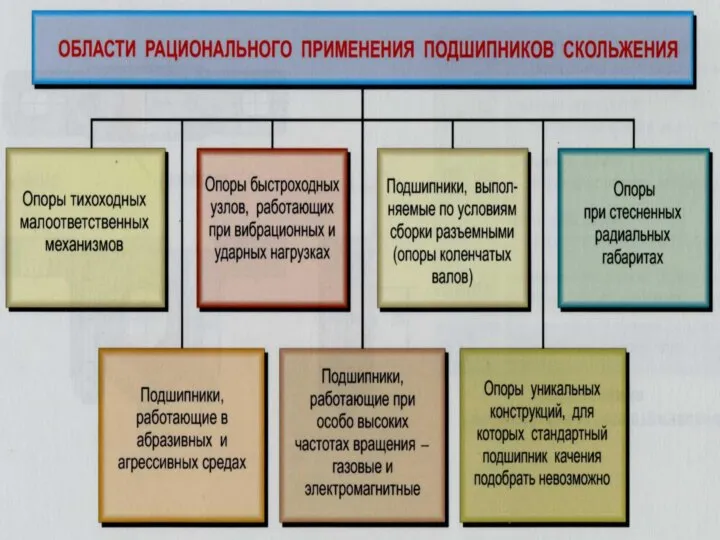

Презентация Цена и общая стоимость контракта Виды цен Определение валюты цены  Области рационального применения подшипников скольжения

Области рационального применения подшипников скольжения Презентация Законы и иные источники ПСО. Их роль

Презентация Законы и иные источники ПСО. Их роль Litania Loretańska

Litania Loretańska Языки программирования

Языки программирования Методология научных исследований

Методология научных исследований Проблемно-контрольные вопросы Что такое институт права. Какие признаки присущи правовому институту? Что представляют собой

Проблемно-контрольные вопросы Что такое институт права. Какие признаки присущи правовому институту? Что представляют собой  НАЛОГОВЫЙ КОДЕКС: для транспортных предприятий

НАЛОГОВЫЙ КОДЕКС: для транспортных предприятий  Презентация Microsoft Office PowerPoint

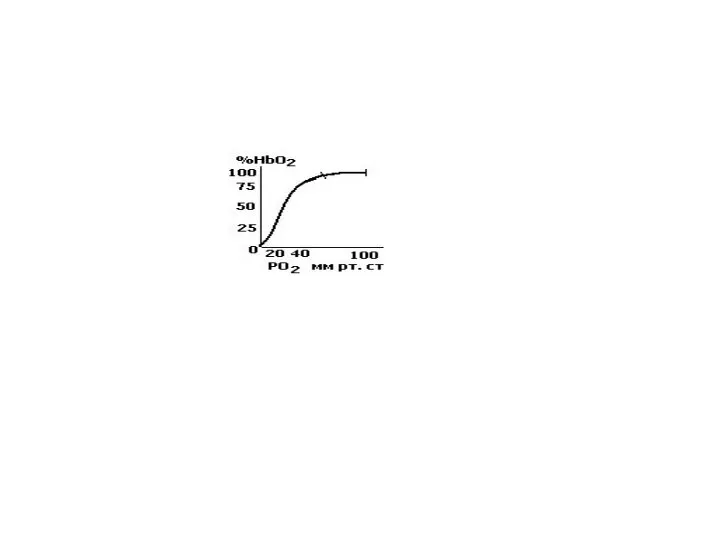

Презентация Microsoft Office PowerPoint дыхание 2

дыхание 2 Устройство пк

Устройство пк  Аттестация как элемент планирования карьеры

Аттестация как элемент планирования карьеры Субиндексы степени развития бизнеса Нечаева Анастасия, Юрлова Виктория, МЭ-102

Субиндексы степени развития бизнеса Нечаева Анастасия, Юрлова Виктория, МЭ-102 Тензор поляризуемости диэлектрика

Тензор поляризуемости диэлектрика

Регистры x86-64. Компьютерные основы программирования. Представление программ, часть 4

Регистры x86-64. Компьютерные основы программирования. Представление программ, часть 4 Инфляция «Инфляция — одна из форм налогообложения, не нуждающаяся в законодательном одобрении». Лауреат Нобелевской премии по

Инфляция «Инфляция — одна из форм налогообложения, не нуждающаяся в законодательном одобрении». Лауреат Нобелевской премии по Мужская парфюмерия

Мужская парфюмерия Политическая система

Политическая система Понятие и виды правомерного поведения

Понятие и виды правомерного поведения