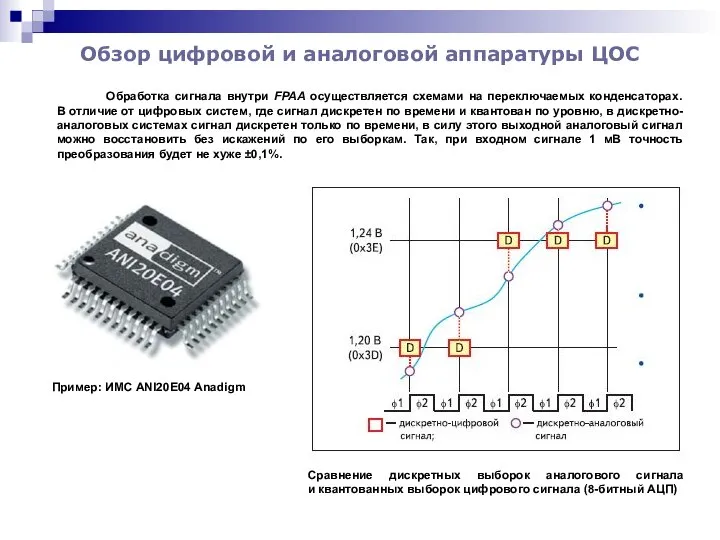

Обзор цифровой и аналоговой аппаратуры ЦОС

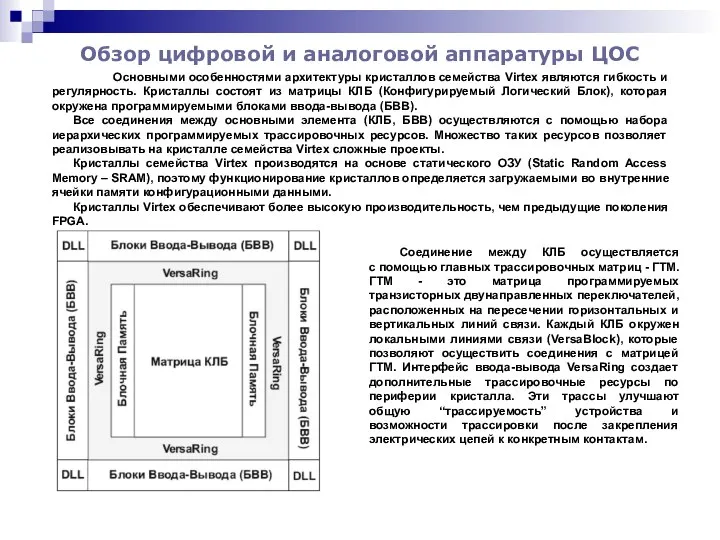

Основными особенностями архитектуры кристаллов семейства

Virtex являются гибкость и регулярность. Кристаллы состоят из матрицы КЛБ (Конфигурируемый Логический Блок), которая окружена программируемыми блоками ввода-вывода (БВВ).

Все соединения между основными элемента (КЛБ, БВВ) осуществляются с помощью набора иерархических программируемых трассировочных ресурсов. Множество таких ресурсов позволяет реализовывать на кристалле семейства Virtex сложные проекты.

Кристаллы семейства Virtex производятся на основе статического ОЗУ (Static Random Access Memory – SRAM), поэтому функционирование кристаллов определяется загружаемыми во внутренние ячейки памяти конфигурационными данными.

Кристаллы Virtex обеспечивают более высокую производительность, чем предыдущие поколения FPGA.

Соединение между КЛБ осуществляется

с помощью главных трассировочных матриц - ГТМ. ГТМ - это матрица программируемых транзисторных двунаправленных переключателей, расположенных на пересечении горизонтальных и вертикальных линий связи. Каждый КЛБ окружен локальными линиями связи (VersaBlock), которые позволяют осуществить соединения с матрицей ГТМ. Интерфейс ввода-вывода VersaRing создает дополнительные трассировочные ресурсы по периферии кристалла. Эти трассы улучшают общую “трассируемость” устройства и возможности трассировки после закрепления электрических цепей к конкретным контактам.

ПРОБЛЕМЫ ИДЕНТИФИКАЦИИ НОНОМАТЕРИАЛОВ. нАНОЦЕМЕНТ Терешкова М. Лазарюк А. С. ДС 5

ПРОБЛЕМЫ ИДЕНТИФИКАЦИИ НОНОМАТЕРИАЛОВ. нАНОЦЕМЕНТ Терешкова М. Лазарюк А. С. ДС 5 Alexander Aleksandrovich Karelin

Alexander Aleksandrovich Karelin Формирование функции голосообразования у младших школьников в условиях школы второго вида Важенина Анна Александровна, учитель-

Формирование функции голосообразования у младших школьников в условиях школы второго вида Важенина Анна Александровна, учитель- Таможенный тариф 1724 года. Принятие морского пошлинного тарифа 1731. Выполнил студент 1-го курса Т-102 Гулый Максим

Таможенный тариф 1724 года. Принятие морского пошлинного тарифа 1731. Выполнил студент 1-го курса Т-102 Гулый Максим Первобытная магия и ритуалы

Первобытная магия и ритуалы Модели макроравновесия

Модели макроравновесия  Переходные процессы в электроприводах

Переходные процессы в электроприводах История создания матрёшки

История создания матрёшки НДФЛ

НДФЛ  Презентация на тему "Права и обязанности ученика" - скачать презентации по Педагогике

Презентация на тему "Права и обязанности ученика" - скачать презентации по Педагогике Модели ГЧП: DBOOT

Модели ГЧП: DBOOT

Лыжная подготовка

Лыжная подготовка МАСТЕР-КЛАСС ПО РАЗВИТИЮ ТВОРЧЕСКИХ СПОСОБНОСТЕЙ УЧАЩИХСЯ

МАСТЕР-КЛАСС ПО РАЗВИТИЮ ТВОРЧЕСКИХ СПОСОБНОСТЕЙ УЧАЩИХСЯ Презентация на тему "Классицизм"

Презентация на тему "Классицизм" Государственное бюджетное образовательное учреждение высшего профессионального образования «Оренбургская государственная мед

Государственное бюджетное образовательное учреждение высшего профессионального образования «Оренбургская государственная мед СОДЕРЖАНИЕ ОСНОВ КОНСТИТУЦИОННОГО СТРОЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

СОДЕРЖАНИЕ ОСНОВ КОНСТИТУЦИОННОГО СТРОЯ РОССИЙСКОЙ ФЕДЕРАЦИИ институциональная экономика.ppt

институциональная экономика.ppt Правоведение. Теории происхождения государства. Механизм и функции государства

Правоведение. Теории происхождения государства. Механизм и функции государства СИСТЕМЫ АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ

СИСТЕМЫ АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ  Виды энергий

Виды энергий Звезды: спектральная классификация, классы светимости, диаграмма Герцшпрунга-Рессела

Звезды: спектральная классификация, классы светимости, диаграмма Герцшпрунга-Рессела Правила игры мини футбола

Правила игры мини футбола Депутат МО

Депутат МО Проблемы трансплантологии

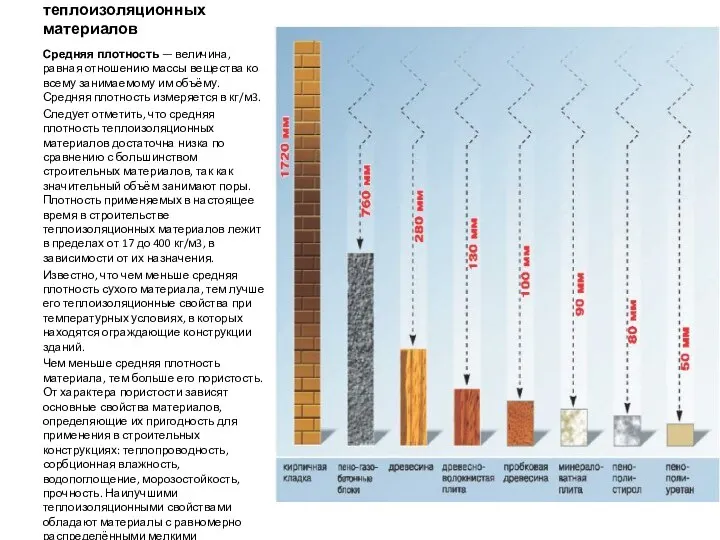

Проблемы трансплантологии  Плотность теплоизоляционных материалов

Плотность теплоизоляционных материалов Система образования России Проблемы

Система образования России Проблемы  Отношения тождества, пересечения и подчинения

Отношения тождества, пересечения и подчинения ФГОС в ДОУ Образовательная область «Художественно-эстетическое развитие» раздел «Музыка» Музыкальный руководитель: Кухта О

ФГОС в ДОУ Образовательная область «Художественно-эстетическое развитие» раздел «Музыка» Музыкальный руководитель: Кухта О