Содержание

- 2. Планарная технология Основным технологическим методом создания современных интегральных микросхем остается разработанная в конце 50-х годов двадцатого

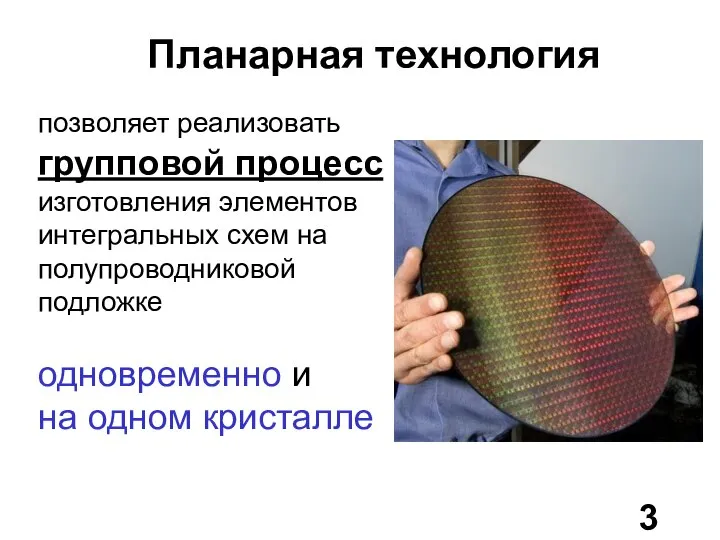

- 3. Планарная технология позволяет реализовать групповой процесс изготовления элементов интегральных схем на полупроводниковой подложке одновременно и на

- 4. Планарный процесс (от англ. planar, от лат. planus – плоский, ровный), – совокупность технологических операций, проводимых

- 5. Основные операции планарной технологии легирование полупроводника (диффузия примесей в полупроводник и ионная имплантация) окисление кремния травление

- 6. Легирование атомами примеси Сущность процессов легирования полупроводника заключается в создании на поверхности полупроводника источника примеси и

- 7. Окисление кремния В результате процесса окисления происходит взаимодействие поверхностного слоя кремния с кислородом и создание на

- 8. Травление Травление – это технологическая операция удаления обрабатываемого материала в процессе химического взаимодействия и растворения в

- 9. Локальное травление и фотолитография Дальнейшим развитием локального травления является метод фотолитографии, использующий в качестве защитного слоя

- 10. Технологический маршрут Изготовление каждого полупроводникового прибора (соответственно, интегральной микросхемы) идет по строго определенной последовательности. Такая последовательность

- 11. Сопроводительный лист На предприятиях микроэлектроники данная последовательность отражена в маршрутной карте (сопроводительном листе) соответствующей партии пластин,

- 12. Принципы планарной технологии взаимосвязь конструкции интегральных микросхем и технологии их изготовления совместимость элементов (на одном кристалле)

- 13. Взаимосвязь конструкции интегральных микросхем и технологии их изготовления Проектирование конструкции интегральной микросхемы связано с технологией ее

- 14. Конструктивно-технологические ограничения при разработке и изготовлении интегральных микросхем Наряду с конструктивными, эксплутационными и электрическими параметрами для

- 15. Совместимость элементов интегральных микросхем Единый групповой метод изготовления. Основной элемент – самый сложный элемент ИС -

- 16. Локальность технологических обработок Во время технологических операций обрабатывается не вся поверхность пластины. Методы локальных технологий: масочная

- 17. Послойное формирование элементов микросхем Локальные обработки различных участков пластины выполняют многократно. Фотолитографический цикл: 2 типа

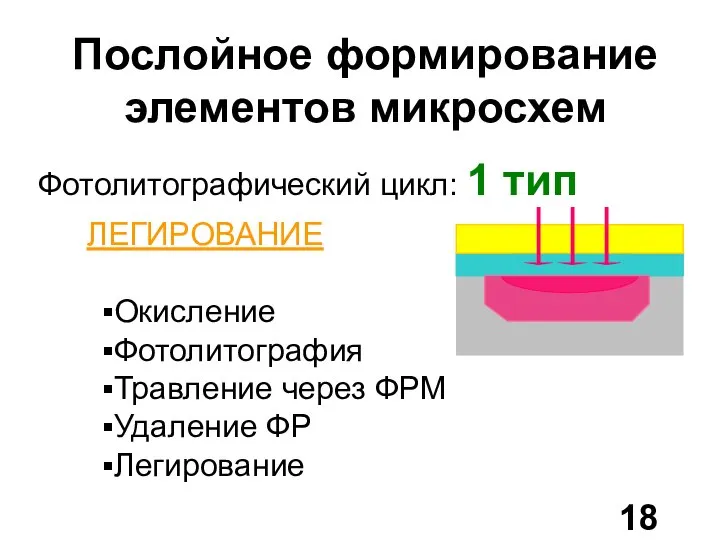

- 18. Послойное формирование элементов микросхем Фотолитографический цикл: 1 тип ЛЕГИРОВАНИЕ Окисление Фотолитография Травление через ФРМ Удаление ФР

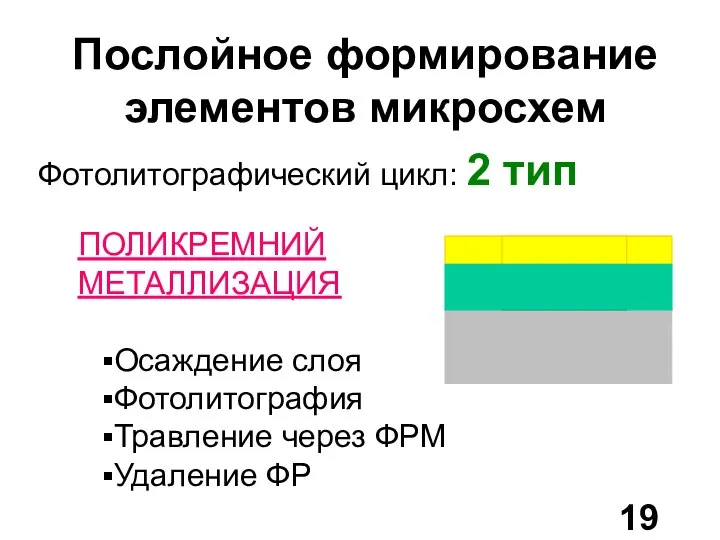

- 19. Послойное формирование элементов микросхем Фотолитографический цикл: 2 тип ПОЛИКРЕМНИЙ МЕТАЛЛИЗАЦИЯ Осаждение слоя Фотолитография Травление через ФРМ

- 20. Технологический маршрут изготовления интегральных микросхем на основе биполярных изопланарных транзисторов

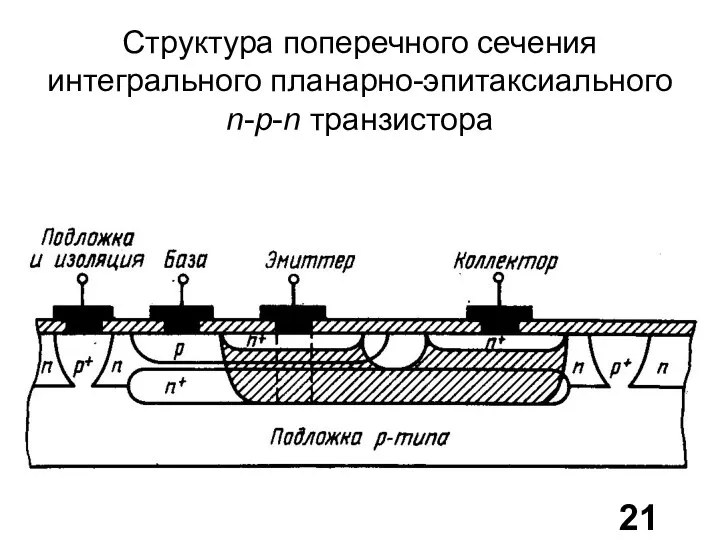

- 21. Структура поперечного сечения интегрального планарно-эпитаксиального n-p-n транзистора

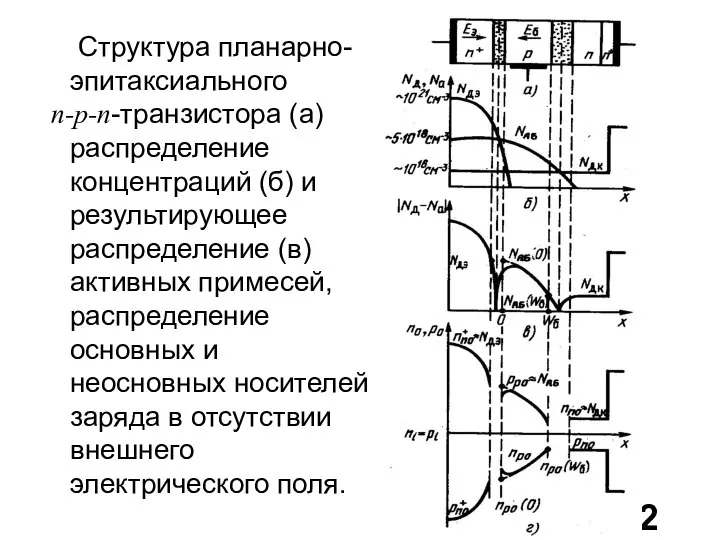

- 22. Структура планарно-эпитаксиального n-p-n-транзистора (а) распределение концентраций (б) и результирующее распределение (в) активных примесей, распределение основных и

- 23. Для разделения приборов в составе кристалла используется комбинированная изоляция: диэлектрическая и изоляция p-n-переходом.

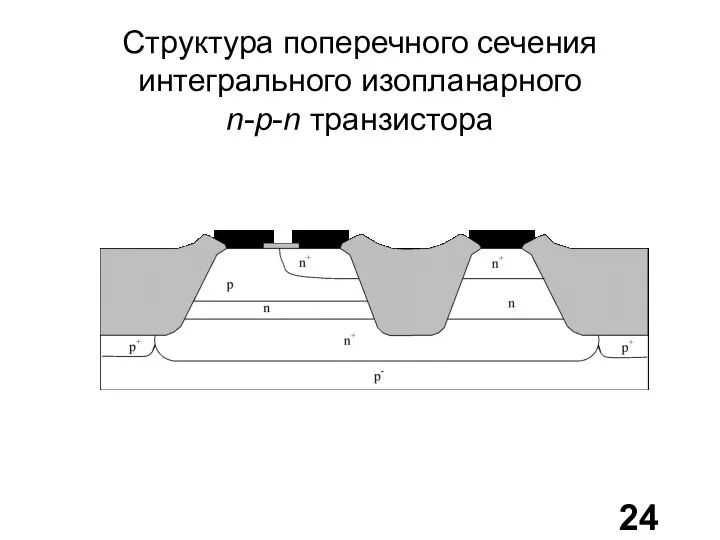

- 24. Структура поперечного сечения интегрального изопланарного n-p-n транзистора

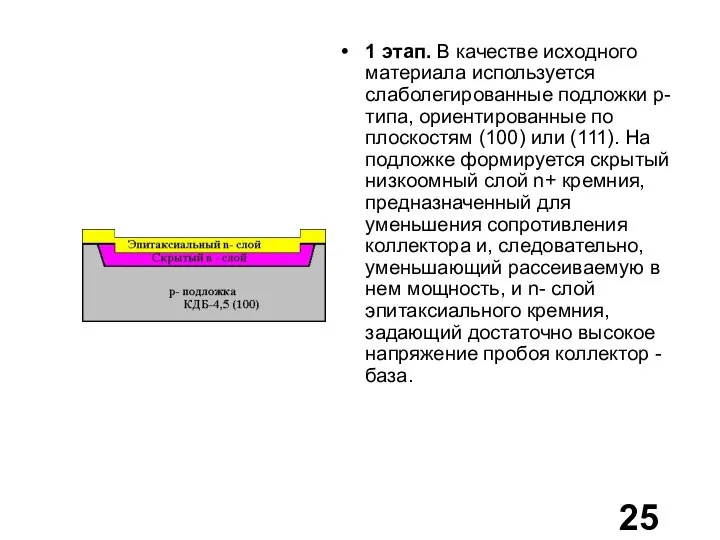

- 25. 1 этап. В качестве исходного материала используется слаболегированные подложки p- типа, ориентированные по плоскостям (100) или

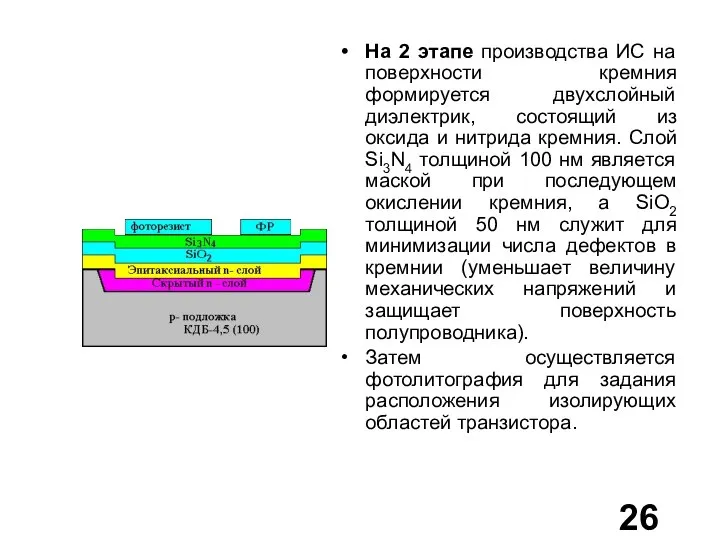

- 26. На 2 этапе производства ИС на поверхности кремния формируется двухслойный диэлектрик, состоящий из оксида и нитрида

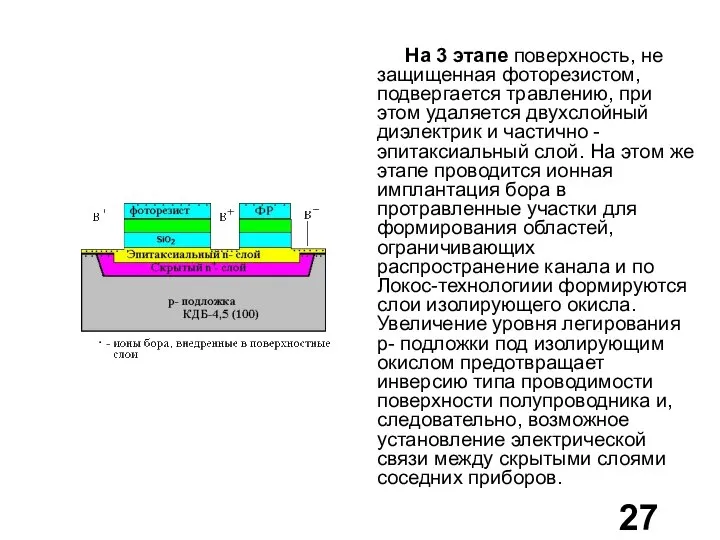

- 27. На 3 этапе поверхность, не защищенная фоторезистом, подвергается травлению, при этом удаляется двухслойный диэлектрик и частично

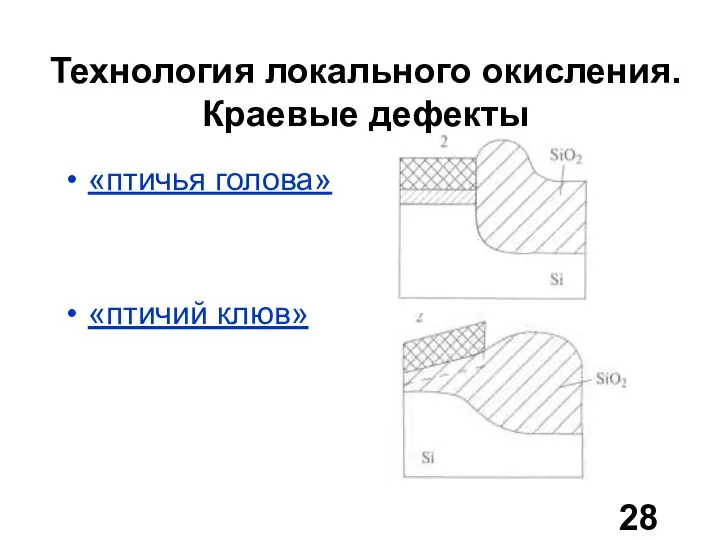

- 28. Технология локального окисления. Краевые дефекты «птичья голова» «птичий клюв»

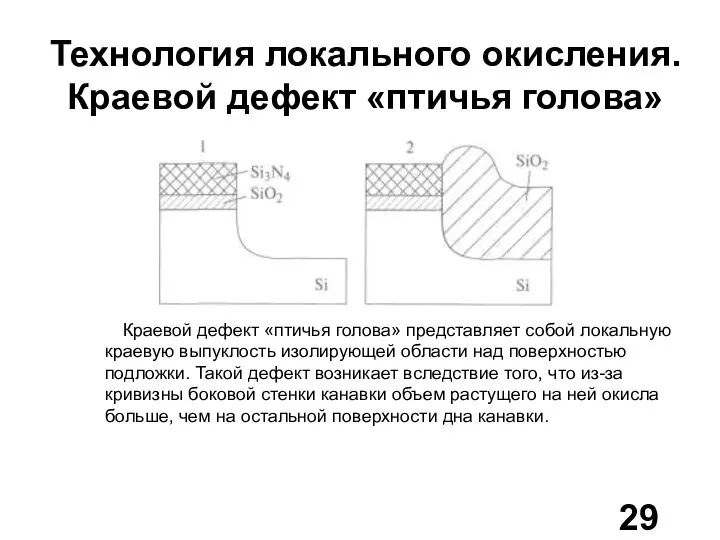

- 29. Технология локального окисления. Краевой дефект «птичья голова» Краевой дефект «птичья голова» представляет собой локальную краевую выпуклость

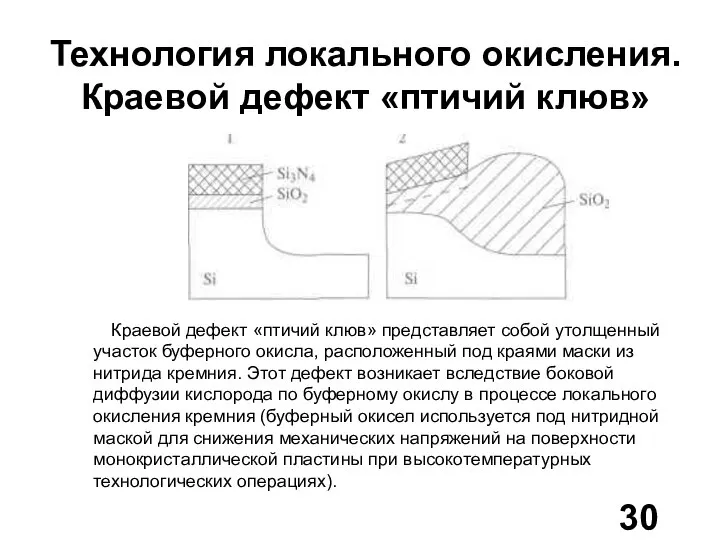

- 30. Технология локального окисления. Краевой дефект «птичий клюв» Краевой дефект «птичий клюв» представляет собой утолщенный участок буферного

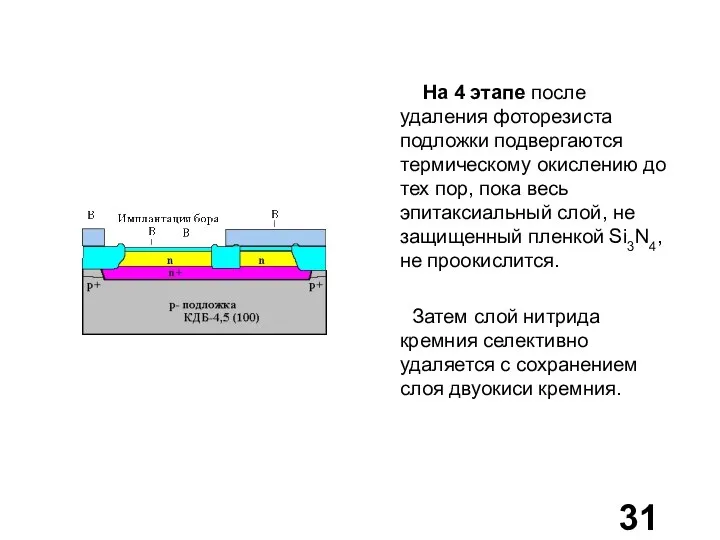

- 31. На 4 этапе после удаления фоторезиста подложки подвергаются термическому окислению до тех пор, пока весь эпитаксиальный

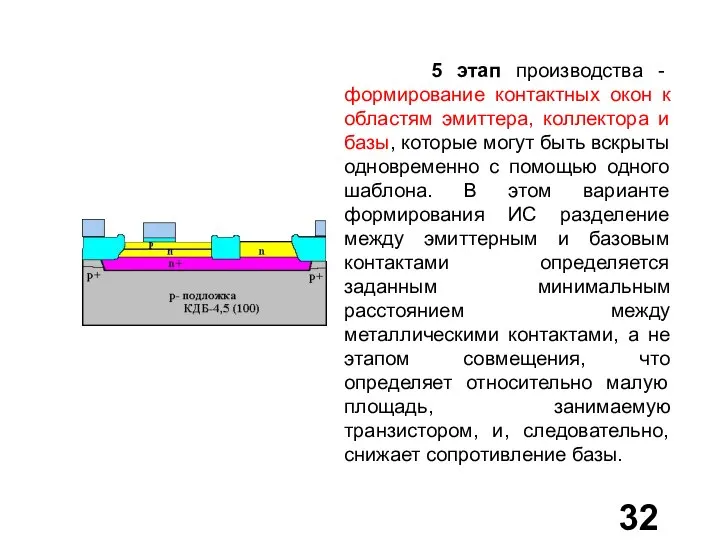

- 32. 5 этап производства - формирование контактных окон к областям эмиттера, коллектора и базы, которые могут быть

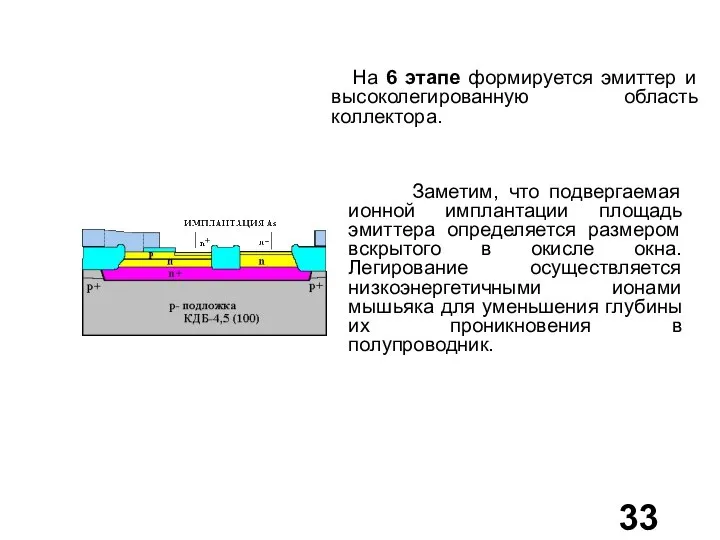

- 33. На 6 этапе формируется эмиттер и высоколегированную область коллектора. Заметим, что подвергаемая ионной имплантации площадь эмиттера

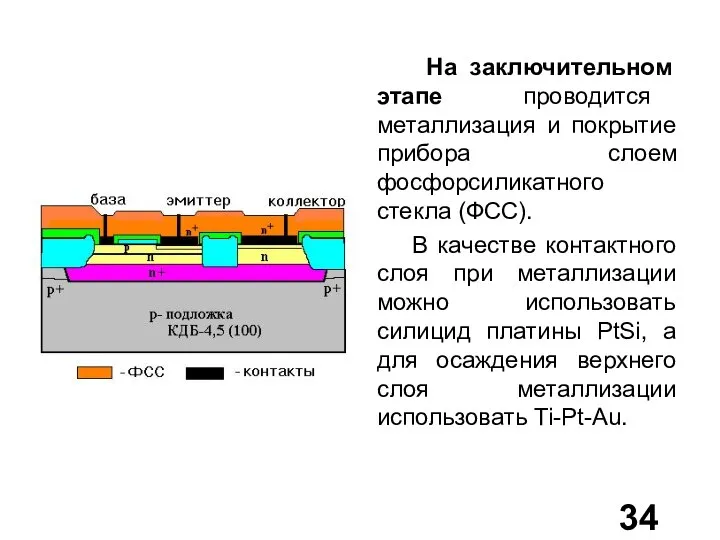

- 34. На заключительном этапе проводится металлизация и покрытие прибора слоем фосфорсиликатного стекла (ФСС). В качестве контактного слоя

- 35. Технология МОП интегральных микросхем

- 36. Преимущества МОП ИС над биполярными ИС малые размеры и площадь упрощенная изоляция низкая потребляемая и рассеиваемая

- 37. Первый транзистор, работающий на эффекте поля, был продемонстрирован в 1960 году. Сначала полевые транзисторы с двуокисью

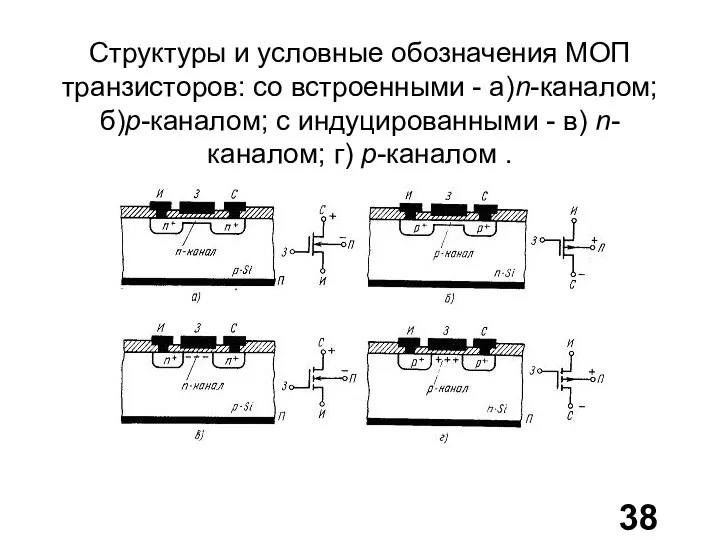

- 38. Структуры и условные обозначения МОП транзисторов: со встроенными - а)n-каналом; б)p-каналом; с индуцированными - в) n-каналом;

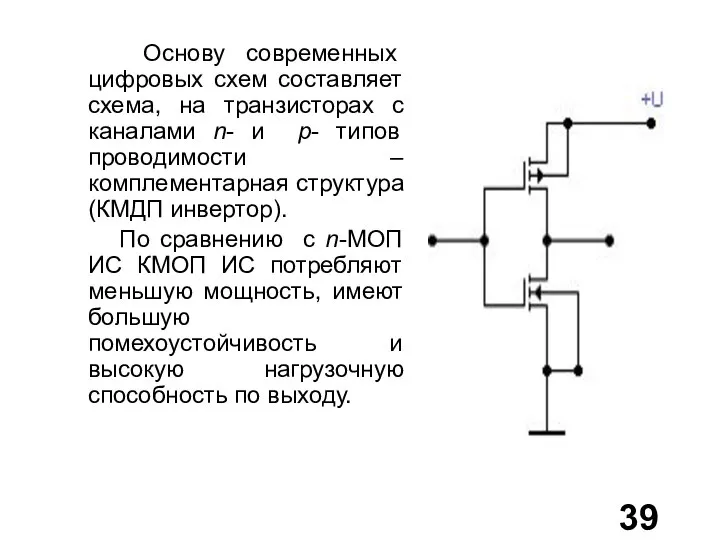

- 39. Основу современных цифровых схем составляет схема, на транзисторах с каналами n- и p- типов проводимости –

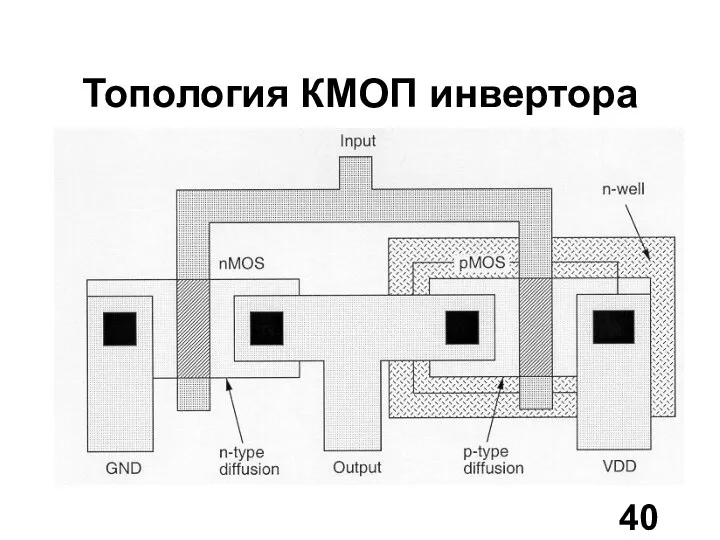

- 40. Топология КМОП инвертора

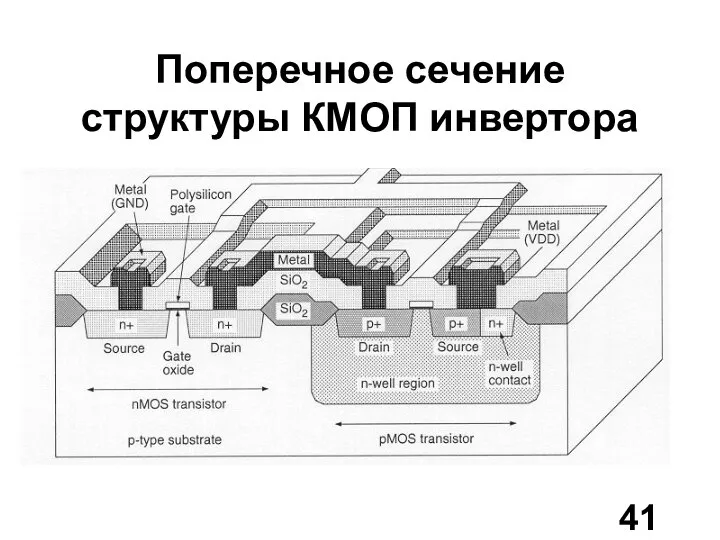

- 41. Поперечное сечение структуры КМОП инвертора

- 42. Технологический маршрут изготовления КМОП интегральных микросхем с p-карманом

- 43. ИС на транзисторах со структурой металл-диэлектрик-полупроводник (МДП) получили широкое распространение. В качестве диэлектрика в настоящее время

- 44. Выбор подложки для КМОП технологии В качестве подложки выбирают кремний p- типа проводимости легированный бором КДБ

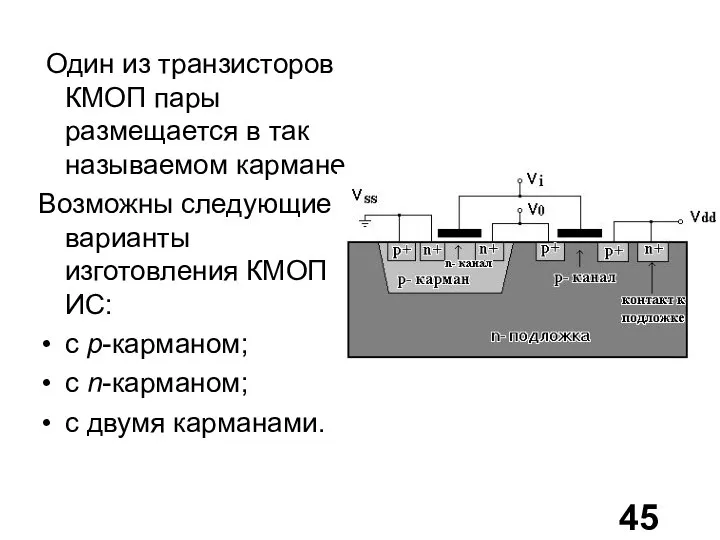

- 45. Один из транзисторов КМОП пары размещается в так называемом кармане. Возможны следующие варианты изготовления КМОП ИС:

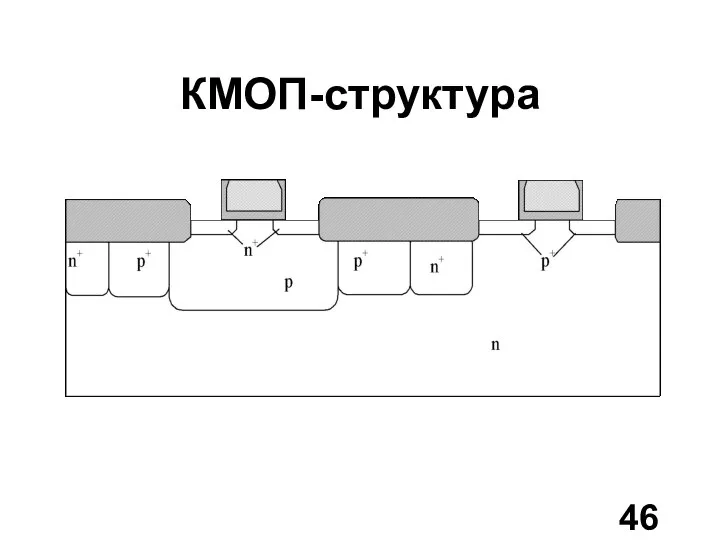

- 46. КМОП-структура

- 47. Тиристор

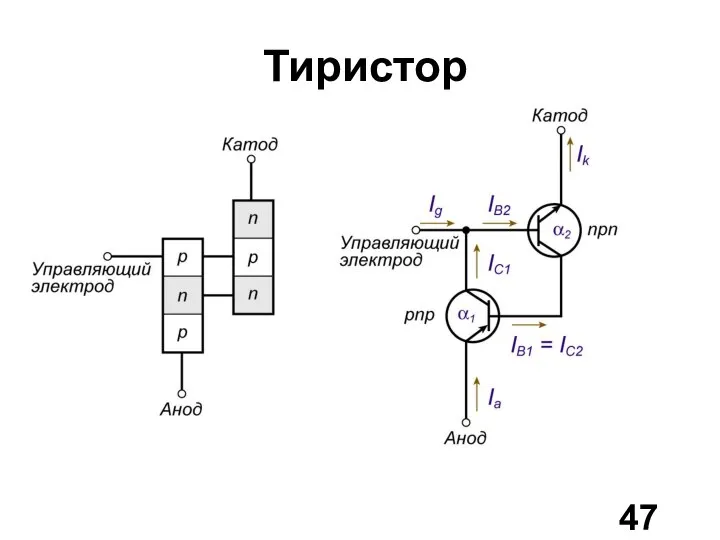

- 48. Маршрут изготовления КМОП ИС с p-карманом (Самосовмещенная технология) Формирование маски для легирования кармана (Окисление 0,1 мкм

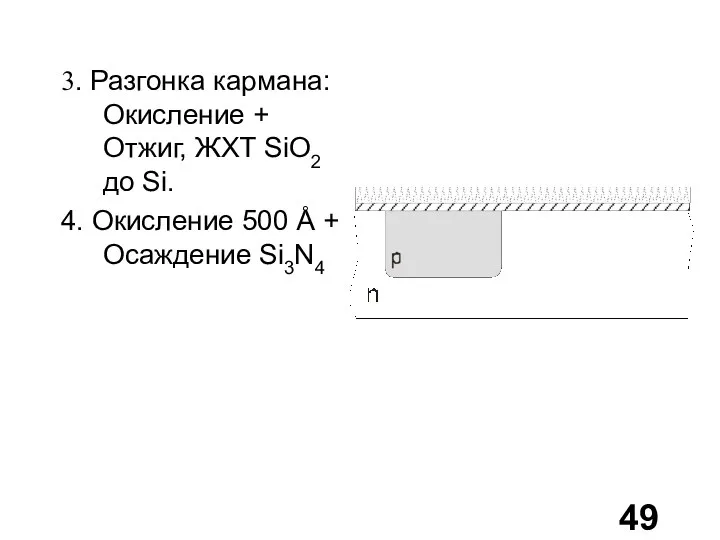

- 49. 3. Разгонка кармана: Окисление + Отжиг, ЖХТ SiO2 до Si. 4. Окисление 500 Å + Осаждение

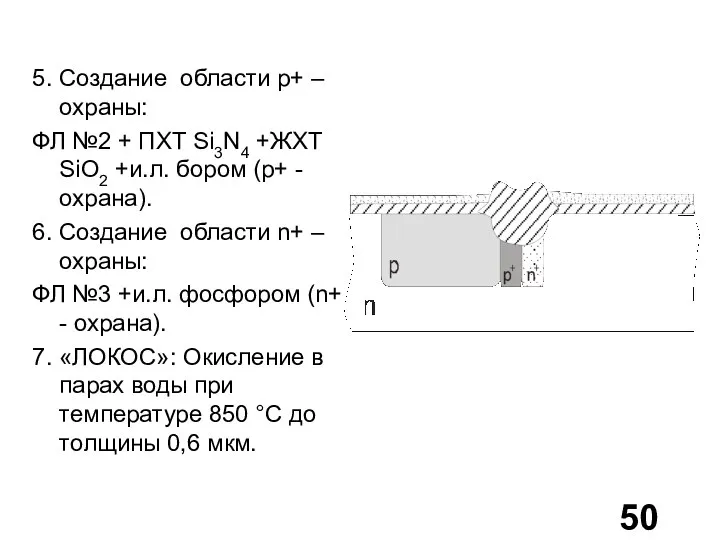

- 50. 5. Создание области р+ – охраны: ФЛ №2 + ПХТ Si3N4 +ЖХТ SiO2 +и.л. бором (р+

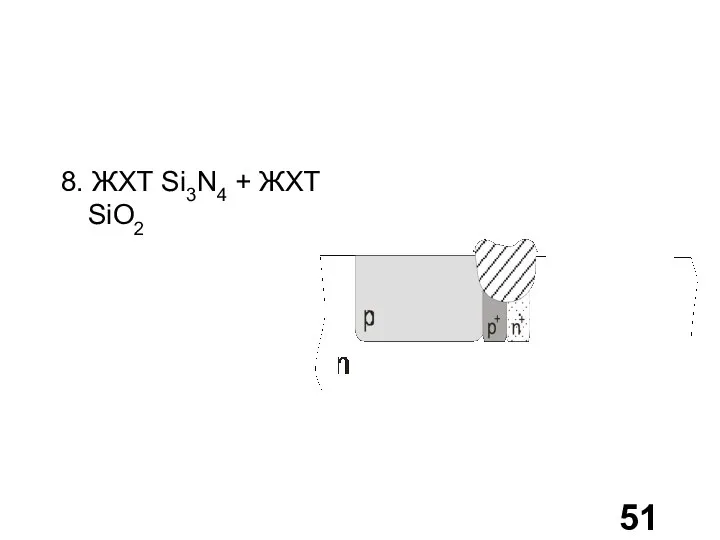

- 51. 8. ЖХТ Si3N4 + ЖХТ SiO2

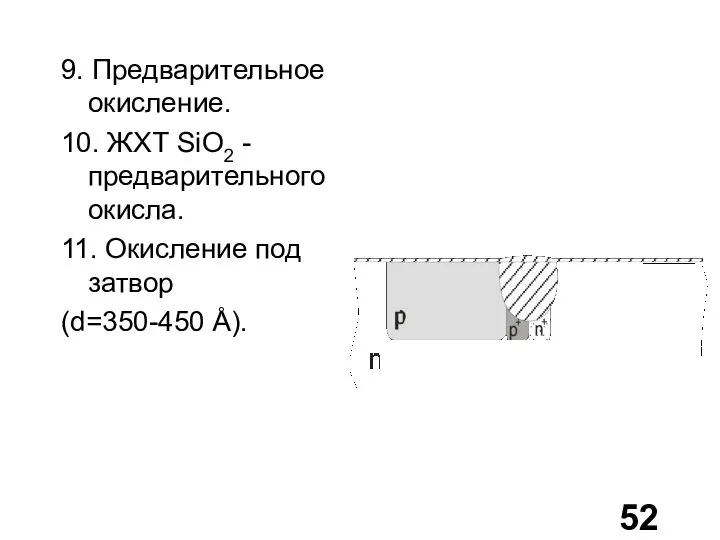

- 52. 9. Предварительное окисление. 10. ЖХТ SiO2 - предварительного окисла. 11. Окисление под затвор (d=350-450 Å).

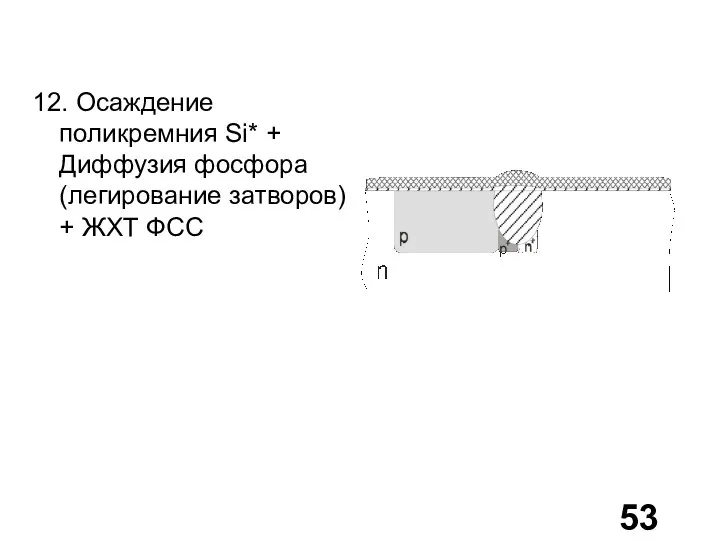

- 53. 12. Осаждение поликремния Si* + Диффузия фосфора (легирование затворов) + ЖХТ ФСС

- 54. 13. Формирование затворов: ФЛ №4+ПХТ Si*+ Окисление («спейсеры»). 14. Формирование областей (n+-стоки, исток) и (p+- стоки,

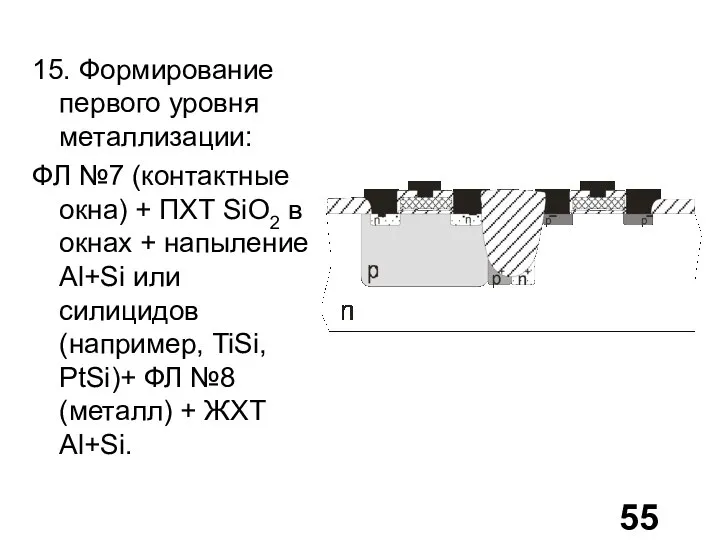

- 55. 15. Формирование первого уровня металлизации: ФЛ №7 (контактные окна) + ПХТ SiO2 в окнах + напыление

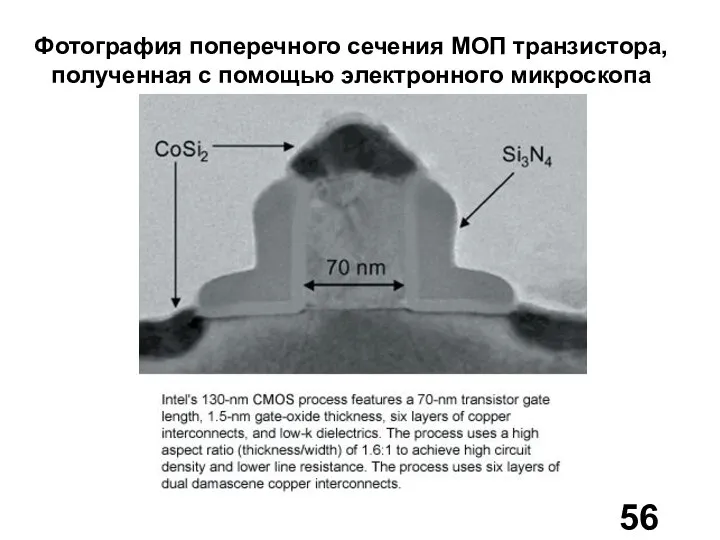

- 56. Фотография поперечного сечения МОП транзистора, полученная с помощью электронного микроскопа

- 57. Список использованных и рекомендуемых источников Технология, конструкции и методы моделирования кремниевых интегральных микросхем: в 2 ч.

- 59. Скачать презентацию

Динамические и статистические закономерности, особенности их проявления

Динамические и статистические закономерности, особенности их проявления Нарушение функционирования рычага механизма переключения коробки передач

Нарушение функционирования рычага механизма переключения коробки передач Методы фиксации цен во внешнеторговых контрактах

Методы фиксации цен во внешнеторговых контрактах Реалистические тенденции в живописи Голландии. Тема 4 Автор: учитель истории Привалова В.С.

Реалистические тенденции в живописи Голландии. Тема 4 Автор: учитель истории Привалова В.С. Закономерности истории политики. (Тема 4)

Закономерности истории политики. (Тема 4) политика монетизации экономика Давлатзода П С Группа Т-093

политика монетизации экономика Давлатзода П С Группа Т-093 Государственные награды РФ

Государственные награды РФ Махамбет Өтемісұлы (1803 – 1846 )

Махамбет Өтемісұлы (1803 – 1846 ) Сжатие данных

Сжатие данных  Презентация "Факторинг" - скачать презентации по Экономике

Презентация "Факторинг" - скачать презентации по Экономике Метод Хюккеля

Метод Хюккеля Презентация "Золотые травы хохломы" - скачать презентации по МХК

Презентация "Золотые травы хохломы" - скачать презентации по МХК tragedia_Beslana

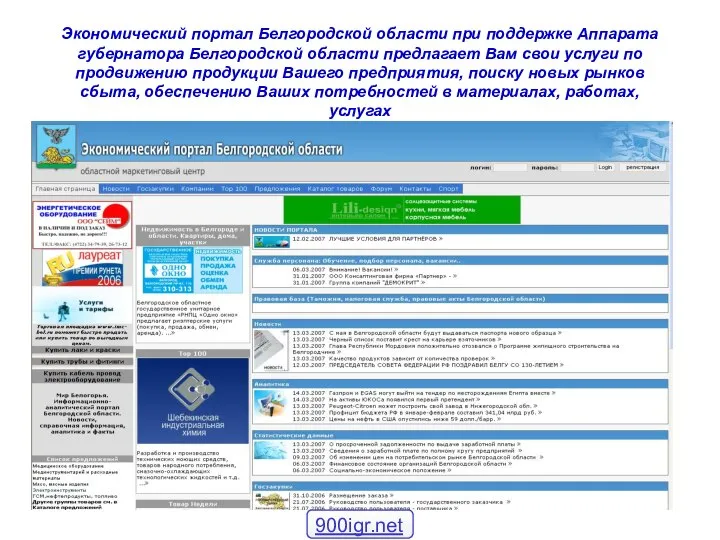

tragedia_Beslana Экономический портал Белгородской области при поддержке Аппарата губернатора Белгородской области предлагает Вам свои услуг

Экономический портал Белгородской области при поддержке Аппарата губернатора Белгородской области предлагает Вам свои услуг ТАЙМ-менеджмент Управление временем в бережливом производстве / офисе Семинар по бережливому производству

ТАЙМ-менеджмент Управление временем в бережливом производстве / офисе Семинар по бережливому производству  Морфологическая структура ландшафта

Морфологическая структура ландшафта Политическая система. Развитие теории политической системы

Политическая система. Развитие теории политической системы 7475

7475 Пресметни и посочи: /в случай че те затрудни, натисни/ 3 + 2 =

Пресметни и посочи: /в случай че те затрудни, натисни/ 3 + 2 = Индуистский храм

Индуистский храм Основные причины низкой эффективности оказания государственных (муниципальных) услуг

Основные причины низкой эффективности оказания государственных (муниципальных) услуг Презентация на тему: «Возникновение государства и права в Армении»

Презентация на тему: «Возникновение государства и права в Армении»  Германская фонология

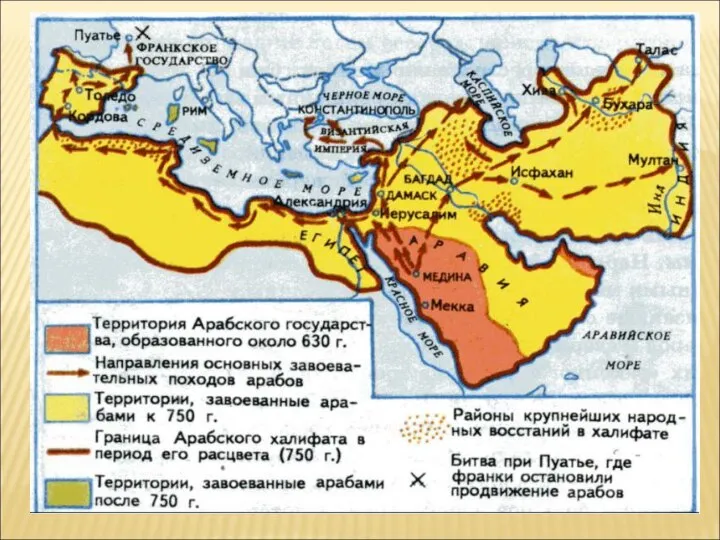

Германская фонология Культура стран халифата

Культура стран халифата СУБКУЛЬТУРЫ Субкультура (подкультура, лат. sub — под и лат. cultura — возделывание, земледелие, воспитание, почитание) в социологи

СУБКУЛЬТУРЫ Субкультура (подкультура, лат. sub — под и лат. cultura — возделывание, земледелие, воспитание, почитание) в социологи Крепежные детали. Резьбовые соединения

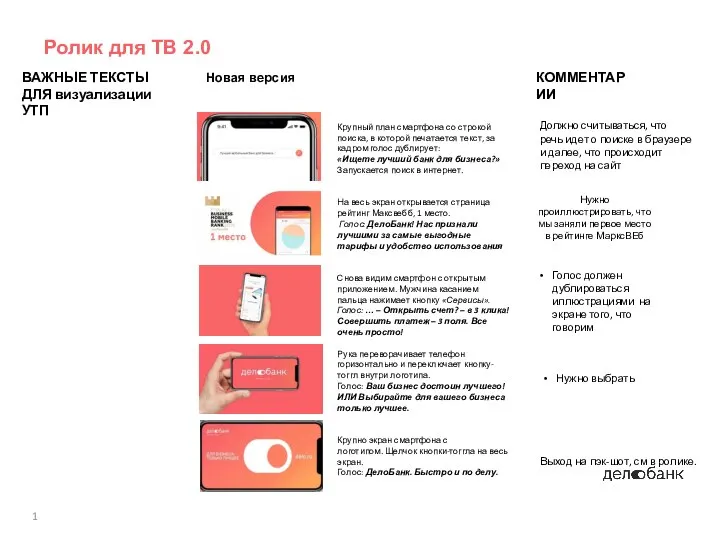

Крепежные детали. Резьбовые соединения ДелоБанк. Ролик для ТВ

ДелоБанк. Ролик для ТВ Город Киров на реке Вятка

Город Киров на реке Вятка