Содержание

- 2. 1. Логические элементы и функциональные узлы. Логические элементы обеспечивают работу с одним битом информации (ноль —

- 3. 2. Разновидность функциональных узлов. Функциональные узлы могут быть одноразрядные, т.е. обрабатывающие один разряд слова (например, сумматоры,

- 4. Асинхронная (не синхронизированная) — сигналы передаются с небольшой задержкой от элемента к элементу. Элемент или узел

- 5. 3. Функциональные узлы комбинационного типа Комбинационные узлы (узлы комбинационного типа) — функциональные узлы, логическое состояние выходов

- 6. Полный одноразрядный сумматор – схема выполняющая сложение двух одноразрядных чисел с учетом переноса из младшего разряда.

- 7. Полный многоразрядный сумматор в параллельном коде (параллельный) an-1 ... a1a0 + bn-1 ... b1b0 Sn Sn-1

- 8. 3.2 Компараторы (цифровые, или двоичные) Схемы сравнения двух кодов(a0a1..am) и (b0b1...bm) и формирования признака результата сравнения

- 9. Полные компараторы Многоразрядный компаратор (пример компаратора, производящего сравнение равно\не равно)

- 10. Логическая функция многоразрядного компаратора (равно/не равно) y = a0 + b0 v a1 + b1 v

- 11. 3.3 Шифратор Шифратор – схема, преобразующая сигнал на одном из входов в двоичный код (номера входной

- 12. Шифраторы могут иметь противоположную логику. Например, на всех входах 1 кроме одного, на котором 0, на

- 13. 3.4 Дешифратор Дешифратор – схема, преобразующая параллельный код на входах в сигнал на одном из выходов.

- 14. 3.5 Мультиплексор(селектор) – MX, MS Схема, подключающая один или несколько входов к единственному выходу Проще: имеется

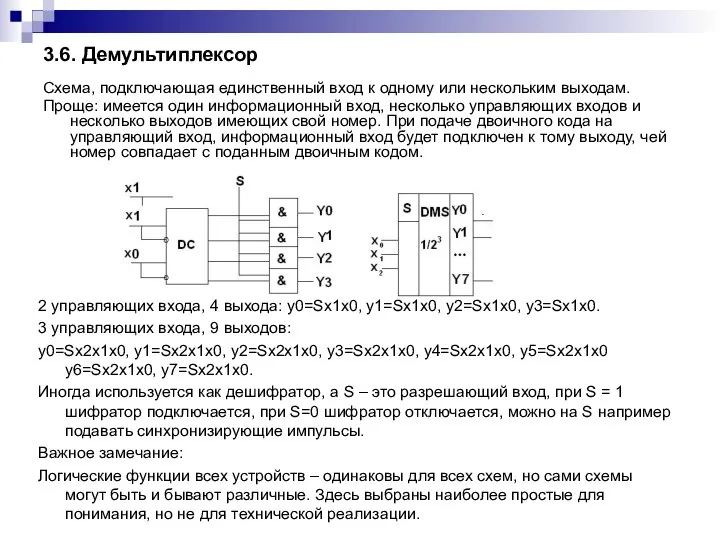

- 15. 3.6. Демультиплексор Схема, подключающая единственный вход к одному или нескольким выходам. Проще: имеется один информационный вход,

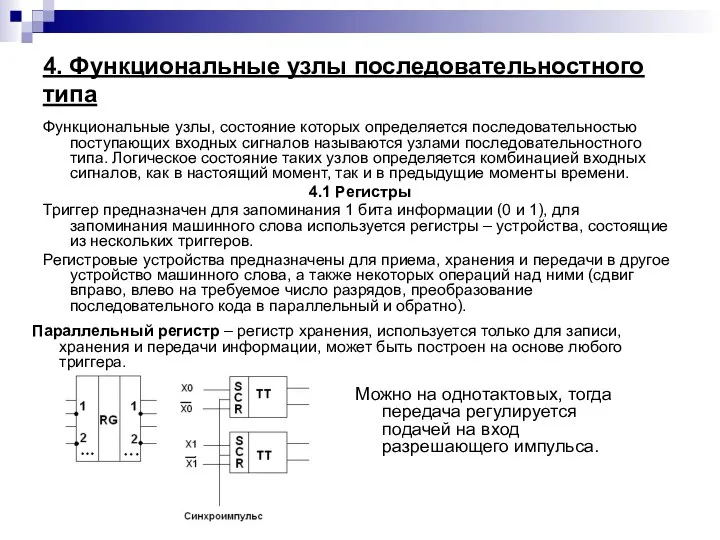

- 16. 4. Функциональные узлы последовательностного типа Функциональные узлы, состояние которых определяется последовательностью поступающих входных сигналов называются узлами

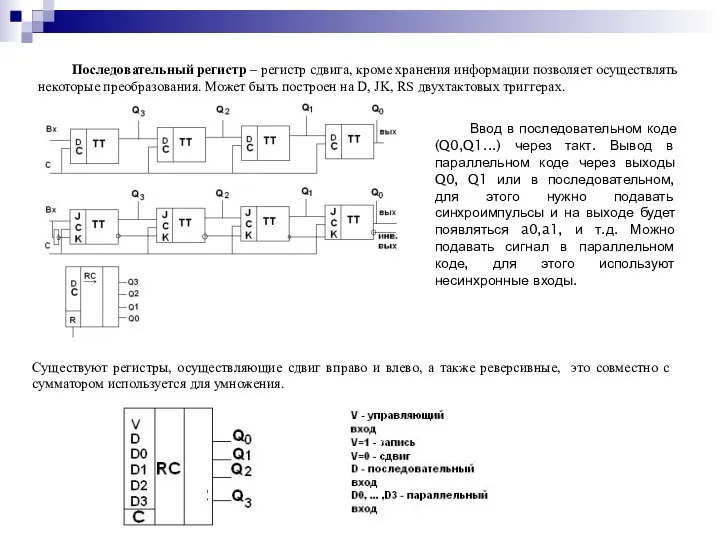

- 17. Последовательный регистр – регистр сдвига, кроме хранения информации позволяет осуществлять некоторые преобразования. Может быть построен на

- 19. Скачать презентацию

1. Логические элементы и функциональные узлы.

Логические элементы обеспечивают работу с одним

1. Логические элементы и функциональные узлы.

Логические элементы обеспечивают работу с одним

Числа, адреса, команды представляются в виде машинного слова, т.е. Совокупности нулей и единиц. Интерес представляет обработка и передача не одного бита, а их совокупности, т.е. машинного слова, включающей 16, 32, 64 бита.

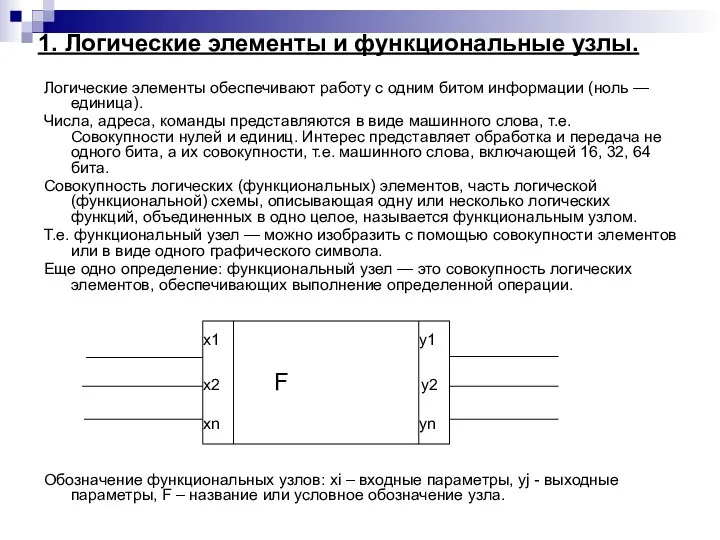

Совокупность логических (функциональных) элементов, часть логической (функциональной) схемы, описывающая одну или несколько логических функций, объединенных в одно целое, называется функциональным узлом.

Т.е. функциональный узел — можно изобразить с помощью совокупности элементов или в виде одного графического символа.

Еще одно определение: функциональный узел — это совокупность логических элементов, обеспечивающих выполнение определенной операции.

x1 y1

x2 F y2

xn yn

Обозначение функциональных узлов: xi – входные параметры, yj - выходные параметры, F – название или условное обозначение узла.

2. Разновидность функциональных узлов.

Функциональные узлы могут быть одноразрядные, т.е. обрабатывающие один

2. Разновидность функциональных узлов.

Функциональные узлы могут быть одноразрядные, т.е. обрабатывающие один

Функциональные многоразрядные узлы делятся на узлы параллельного и последовательного типа, т.е. работающие в параллельном и последовательном коде передачи информации.

Параллельный код — каждый временной такт используется для отображения одного разряда. Двоичный код слова — в виде временной последовательности. Причем слово передается по одной шине.

Параллельный код — все разделы слова передаются за один такт по отдельным шинам к отдельным элементам. При этом количество шин должно равняться количеству разрядов. Двоичный код слова — в виде пространственно разнесенной последовательности.

Последовательно-параллельный код - слово разбивается на слоги, каждый слог представляется в параллельном виде, а сами слоги передаются последовательно.

В последовательном коде могут работать сумматоры, регистры сдвига, счетчики, большинство же узлов работает в параллельном коде.

Кроме того? передача информации может быть однофазной (по одной шине) и парафазной (по двум шинам), по одной передается сигнал, а по другой инвертированный сигнал.

Передача информации может быть асинхронной и синхронной (синхронизируемой).

Асинхронная (не синхронизированная) — сигналы передаются с небольшой задержкой от элемента

Асинхронная (не синхронизированная) — сигналы передаются с небольшой задержкой от элемента

Синхронизируемая передача информации — элемент или узел срабатывает только после прихода синхроимпульса (т.е. в строго определенные моменты). Если на вход поступил сигнал, а синхроимпульс не подан, устройство не срабатывает (т.е. должен поступить сигнал плюс синхроимпульс).

Комбинационные узлы (узлы комбинационного типа) — функциональные узлы, логическое состояние выходов которых зависит только от комбинации логических сигналов на входе в данный момент времени, т.е. логическое состояние однозначно определяется комбинацией входных переменных в данный момент времени. Эти узлы «не помнят», не сохраняют информации от ранее пришедших сигналов, например, сумматоры, компараторы, преобразователи кодов, (де-)шифраторы, (де-)мультиплексоры, программирующие логические матрицы.

Последовательностные узлы (узлы последовательного типа) — функциональные узлы, логическое состояние которых определяется последовательностью поступающих входных сигналов, т.е. логическое состояние определяется комбинацией входных сигналов не только в настоящий момент, но и в предыдущие моменты времени. Говорят, что такие узлы обладают памятью, например регистры, счетчики, генераторы кодов (распределители кодов). Узлы содержат элементы памяти — триггеры.

Другое название таких узлов — цифровые автоматы Q(t+1)=f(Q(t),x(t)). Различают автомат Мили y(t)=φ(Q(t),x(t)) и автомат Мура y(t)=φ(Q(t)), где Q(t) — состояние узла, x(t), y(t) — входные и выходные сигналы.

3. Функциональные узлы комбинационного типа

Комбинационные узлы (узлы комбинационного типа) — функциональные

3. Функциональные узлы комбинационного типа

Комбинационные узлы (узлы комбинационного типа) — функциональные

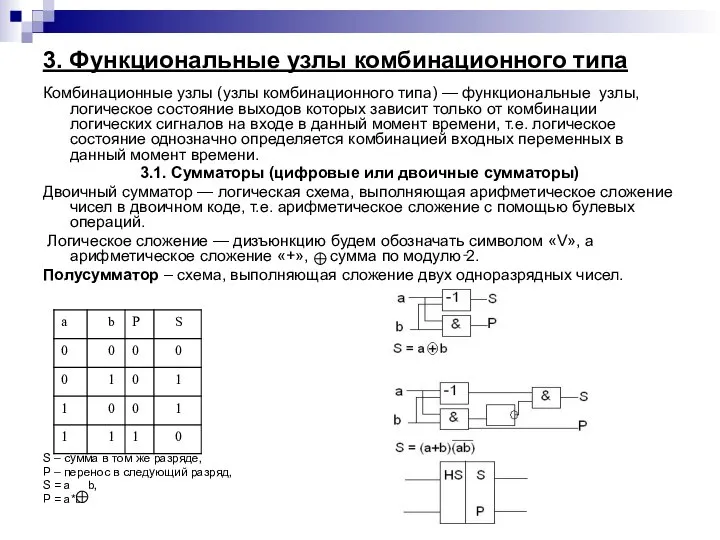

3.1. Сумматоры (цифровые или двоичные сумматоры)

Двоичный сумматор — логическая схема, выполняющая арифметическое сложение чисел в двоичном коде, т.е. арифметическое сложение с помощью булевых операций.

Логическое сложение — дизъюнкцию будем обозначать символом «V», а арифметическое сложение «+», сумма по модулю 2.

Полусумматор – схема, выполняющая сложение двух одноразрядных чисел.

S – сумма в том же разряде,

P – перенос в следующий разряд,

S = a b,

P = a*b.

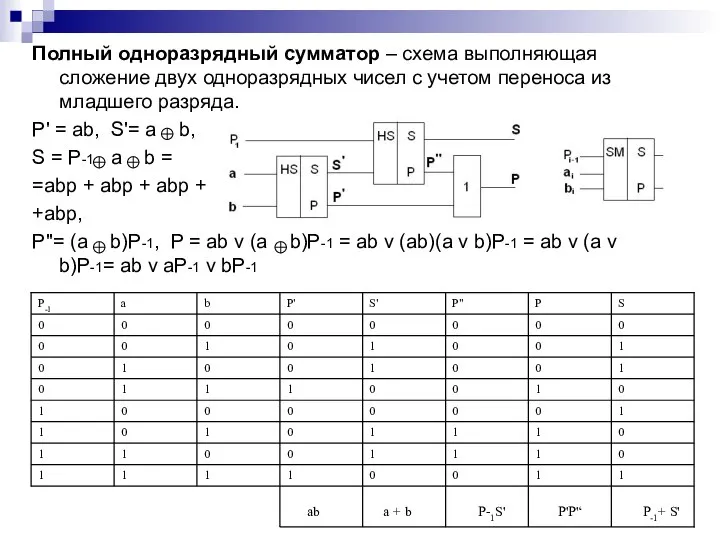

Полный одноразрядный сумматор – схема выполняющая сложение двух одноразрядных чисел с

Полный одноразрядный сумматор – схема выполняющая сложение двух одноразрядных чисел с

P' = ab, S'= a b,

S = P-1 a b =

=abp + abp + abp +

+abp,

P''= (a b)P-1, P = ab v (a b)P-1 = ab v (ab)(a v b)P-1 = ab v (a v b)P-1= ab v aP-1 v bP-1

ab a + b P-1S' P'P'‘ P-1+ S'

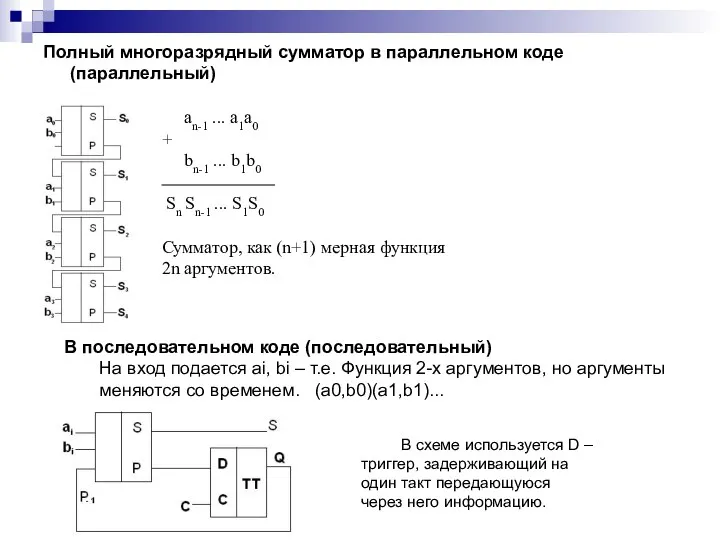

Полный многоразрядный сумматор в параллельном коде (параллельный)

an-1 ... a1a0

+

Полный многоразрядный сумматор в параллельном коде (параллельный)

an-1 ... a1a0

+

Sn Sn-1 ... S1S0

Сумматор, как (n+1) мерная функция 2n аргументов.

В последовательном коде (последовательный)

На вход подается ai, bi – т.е. Функция 2-х аргументов, но аргументы

меняются со временем. (a0,b0)(a1,b1)...

В схеме используется D –

триггер, задерживающий на

один такт передающуюся

через него информацию.

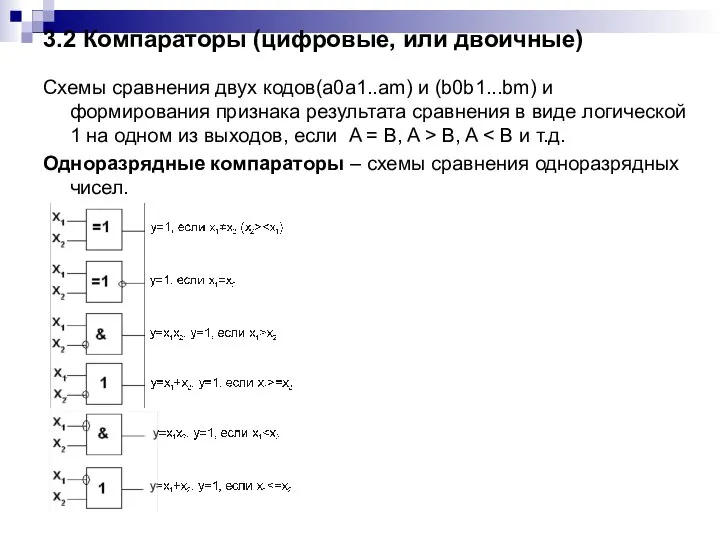

3.2 Компараторы (цифровые, или двоичные)

Схемы сравнения двух кодов(a0a1..am) и (b0b1...bm) и

3.2 Компараторы (цифровые, или двоичные)

Схемы сравнения двух кодов(a0a1..am) и (b0b1...bm) и

Одноразрядные компараторы – схемы сравнения одноразрядных чисел.

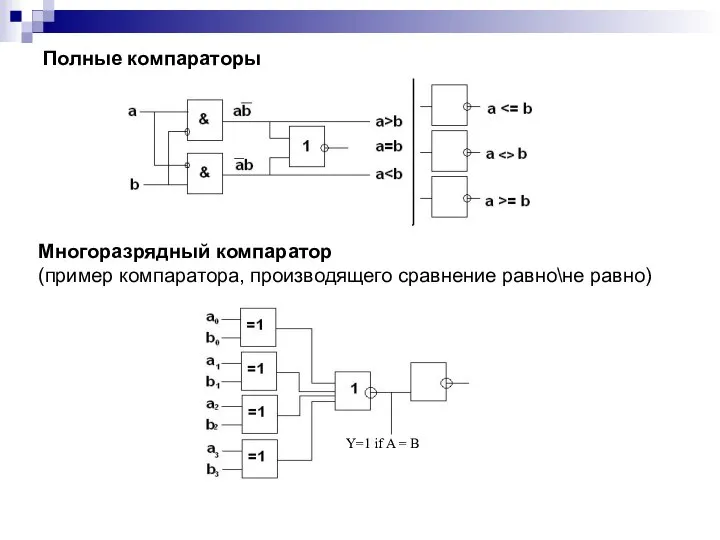

Полные компараторы

Многоразрядный компаратор

(пример компаратора, производящего сравнение равно\не равно)

Полные компараторы

Многоразрядный компаратор

(пример компаратора, производящего сравнение равно\не равно)

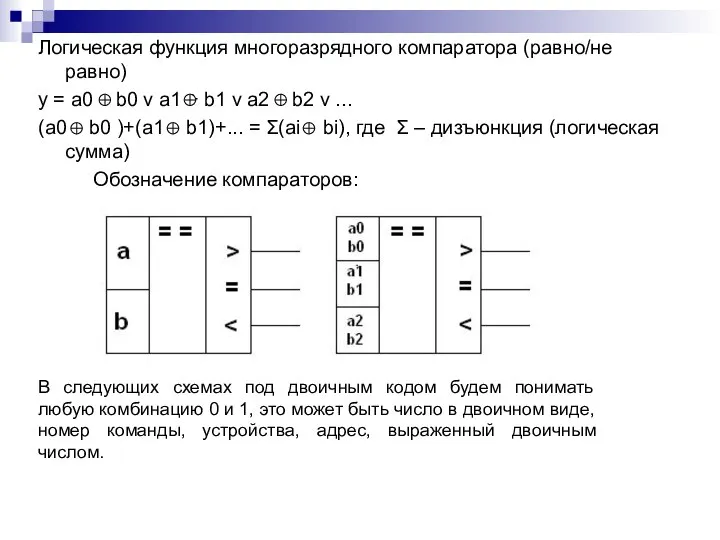

Логическая функция многоразрядного компаратора (равно/не равно)

y = a0 + b0 v

Логическая функция многоразрядного компаратора (равно/не равно)

y = a0 + b0 v

(a0 b0 )+(a1 b1)+... = Σ(ai bi), где Σ – дизъюнкция (логическая сумма)

Обозначение компараторов:

В следующих схемах под двоичным кодом будем понимать любую комбинацию 0 и 1, это может быть число в двоичном виде, номер команды, устройства, адрес, выраженный двоичным числом.

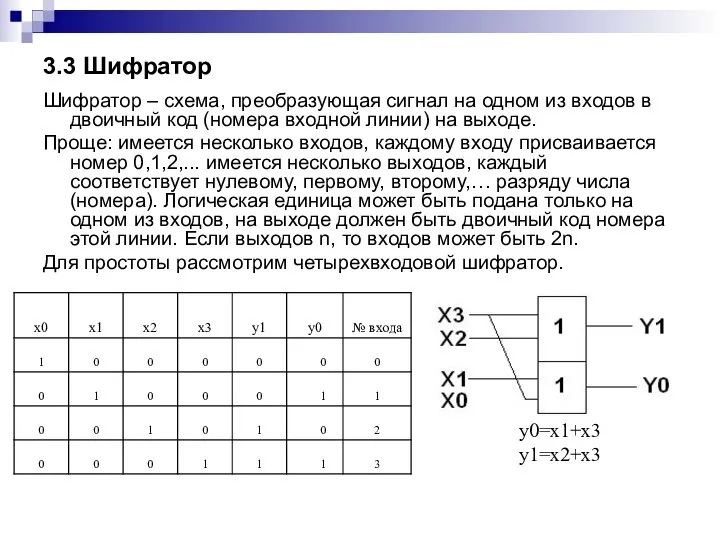

3.3 Шифратор

Шифратор – схема, преобразующая сигнал на одном из входов

3.3 Шифратор

Шифратор – схема, преобразующая сигнал на одном из входов

Проще: имеется несколько входов, каждому входу присваивается номер 0,1,2,... имеется несколько выходов, каждый соответствует нулевому, первому, второму,… разряду числа (номера). Логическая единица может быть подана только на одном из входов, на выходе должен быть двоичный код номера этой линии. Если выходов n, то входов может быть 2n.

Для простоты рассмотрим четырехвходовой шифратор.

y0=x1+x3

y1=x2+x3

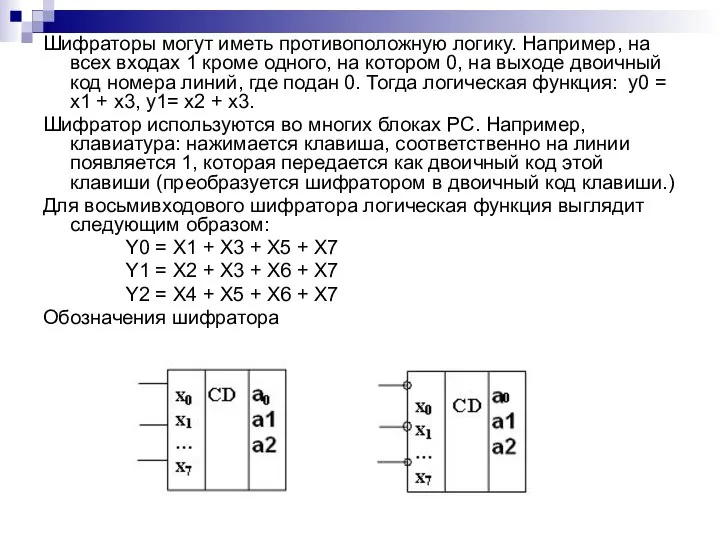

Шифраторы могут иметь противоположную логику. Например, на всех входах 1 кроме

Шифраторы могут иметь противоположную логику. Например, на всех входах 1 кроме

Шифратор используются во многих блоках PC. Например, клавиатура: нажимается клавиша, соответственно на линии появляется 1, которая передается как двоичный код этой клавиши (преобразуется шифратором в двоичный код клавиши.)

Для восьмивходового шифратора логическая функция выглядит следующим образом:

Y0 = X1 + X3 + X5 + X7

Y1 = X2 + X3 + X6 + X7

Y2 = X4 + X5 + X6 + X7

Обозначения шифратора

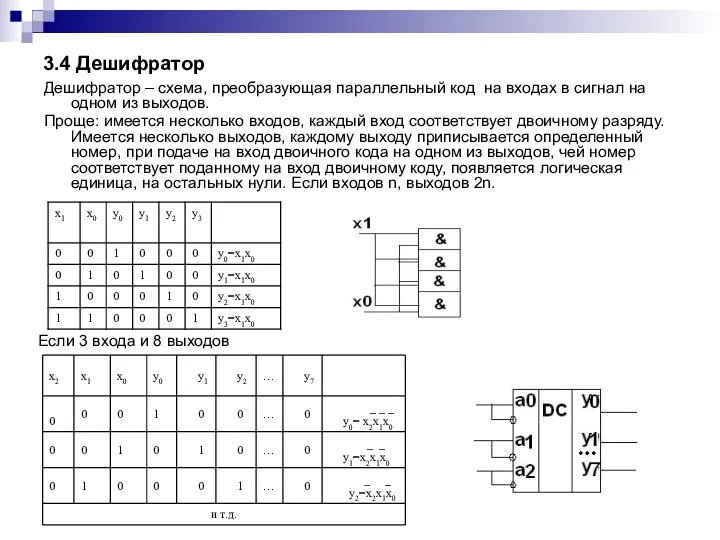

3.4 Дешифратор

Дешифратор – схема, преобразующая параллельный код на входах в сигнал

3.4 Дешифратор

Дешифратор – схема, преобразующая параллельный код на входах в сигнал

Проще: имеется несколько входов, каждый вход соответствует двоичному разряду. Имеется несколько выходов, каждому выходу приписывается определенный номер, при подаче на вход двоичного кода на одном из выходов, чей номер соответствует поданному на вход двоичному коду, появляется логическая единица, на остальных нули. Если входов n, выходов 2n.

Если 3 входа и 8 выходов

3.5 Мультиплексор(селектор) – MX, MS

Схема, подключающая один или несколько входов к

3.5 Мультиплексор(селектор) – MX, MS

Схема, подключающая один или несколько входов к

Проще: имеется несколько входов (информационных), имеющий номер, несколько управляющих входов и один выход. При подаче на управляющие входы двоичного кода номера конкретного информационного входа, этот вход будет подключен к выходу, остальные отключены.

На 4 информационных и 2 управляющих входа:

y = D0x1x0 + D1x1x0 + D2x1x0 + D3x1x0

На 8 информационных и 4 управляющих входа:

y = D0x2x1x0 + D1x2x1x0 + D2x2x1x0 + D3x2x1x0 + D4x2x1x0 + D5x2x1x0 + D6x2x1x0 + D7x2x1x0

В общем случае k управляющих и 2k информационных входов и один выход.

3.6. Демультиплексор

Схема, подключающая единственный вход к одному или нескольким выходам.

Проще: имеется

3.6. Демультиплексор

Схема, подключающая единственный вход к одному или нескольким выходам.

Проще: имеется

2 управляющих входа, 4 выхода: y0=Sx1x0, y1=Sx1x0, y2=Sx1x0, y3=Sx1x0.

3 управляющих входа, 9 выходов:

y0=Sx2x1x0, y1=Sx2x1x0, y2=Sx2x1x0, y3=Sx2x1x0, y4=Sx2x1x0, y5=Sx2x1x0 y6=Sx2x1x0, y7=Sx2x1x0.

Иногда используется как дешифратор, а S – это разрешающий вход, при S = 1 шифратор подключается, при S=0 шифратор отключается, можно на S например подавать синхронизирующие импульсы.

Важное замечание:

Логические функции всех устройств – одинаковы для всех схем, но сами схемы могут быть и бывают различные. Здесь выбраны наиболее простые для понимания, но не для технической реализации.

4. Функциональные узлы последовательностного типа

Функциональные узлы, состояние которых определяется последовательностью поступающих

4. Функциональные узлы последовательностного типа

Функциональные узлы, состояние которых определяется последовательностью поступающих

4.1 Регистры

Триггер предназначен для запоминания 1 бита информации (0 и 1), для запоминания машинного слова используется регистры – устройства, состоящие из нескольких триггеров.

Регистровые устройства предназначены для приема, хранения и передачи в другое устройство машинного слова, а также некоторых операций над ними (сдвиг вправо, влево на требуемое число разрядов, преобразование последовательного кода в параллельный и обратно).

Параллельный регистр – регистр хранения, используется только для записи, хранения и передачи информации, может быть построен на основе любого триггера.

Можно на однотактовых, тогда передача регулируется подачей на вход разрешающего импульса.

Последовательный регистр – регистр сдвига, кроме хранения информации позволяет осуществлять некоторые

Последовательный регистр – регистр сдвига, кроме хранения информации позволяет осуществлять некоторые

Существуют регистры, осуществляющие сдвиг вправо и влево, а также реверсивные, это совместно с сумматором используется для умножения.

Ввод в последовательном коде (Q0,Q1...) через такт. Вывод в параллельном коде через выходы Q0, Q1 или в последовательном, для этого нужно подавать синхроимпульсы и на выходе будет появляться a0,a1, и т.д. Можно подавать сигнал в параллельном коде, для этого используют несинхронные входы.

Нові можливості функцій в мові С++

Нові можливості функцій в мові С++ Жер ресурсына толемдер тури

Жер ресурсына толемдер тури Видеокарта GeForce GTX TITAN-X

Видеокарта GeForce GTX TITAN-X Расчет радиовещательного приемника первого класса

Расчет радиовещательного приемника первого класса Реформирование органов государственного управления в послевоенный период.

Реформирование органов государственного управления в послевоенный период. Политика ЕС в области железнодорожного транспорта Петруша

Политика ЕС в области железнодорожного транспорта Петруша Новая стартовая программа. Модель бизнеса для тебя!

Новая стартовая программа. Модель бизнеса для тебя! Офисная оргтехника и виды связи

Офисная оргтехника и виды связи Башни Нижегородского Кремля

Башни Нижегородского Кремля износ креставин

износ креставин Презентация Сущность и содержание организации как функции менеджмента

Презентация Сущность и содержание организации как функции менеджмента Презентация Источники уголовно-процессуального права 1.1. Понятие уголовно-процессуального права и уголовно-процессуального зако

Презентация Источники уголовно-процессуального права 1.1. Понятие уголовно-процессуального права и уголовно-процессуального зако Развитие стран Восточной Европы после второй мировой войны (1945- 70-е гг)

Развитие стран Восточной Европы после второй мировой войны (1945- 70-е гг) Массивы в Паскале. Одномерные массивы. (9 класс)

Массивы в Паскале. Одномерные массивы. (9 класс) МИРОВЫЕ ИНФОРМАЦИОННЫЕ РЕСУРСЫ И ЗАЩИТА

МИРОВЫЕ ИНФОРМАЦИОННЫЕ РЕСУРСЫ И ЗАЩИТА  Основные формы и методы работы социального педагога в школе . Исаевой Тамары Васильевны МОУ «Приводинская СОШ»

Основные формы и методы работы социального педагога в школе . Исаевой Тамары Васильевны МОУ «Приводинская СОШ» alfavit_pismo_bukv

alfavit_pismo_bukv Презентация Аналитика молочной промышленности

Презентация Аналитика молочной промышленности  «Маркетинг – философия бизнеса»

«Маркетинг – философия бизнеса» Заявка на участие в проекте «Комфортная городская среда». Название проекта: «Онежские берега». Г. Петрозаводск

Заявка на участие в проекте «Комфортная городская среда». Название проекта: «Онежские берега». Г. Петрозаводск Управление программным проектом

Управление программным проектом Аудитория интернета Украины в апреле 2010 г. Место Уанета среди европейских стран gemiusAudience

Аудитория интернета Украины в апреле 2010 г. Место Уанета среди европейских стран gemiusAudience Декоративное искусство в Древнем Египте

Декоративное искусство в Древнем Египте Шейпинг

Шейпинг  Источники образования доходов торговой организации

Источники образования доходов торговой организации Книга пророка Даниила

Книга пророка Даниила Выпускная квалификационная работа: Оптимизация параметров технико-технологической безопасности организации

Выпускная квалификационная работа: Оптимизация параметров технико-технологической безопасности организации ИЭУ-Монетаризм

ИЭУ-Монетаризм