Содержание

- 2. Области использования микроконтроллеров Microcontrollers CISC & RISC

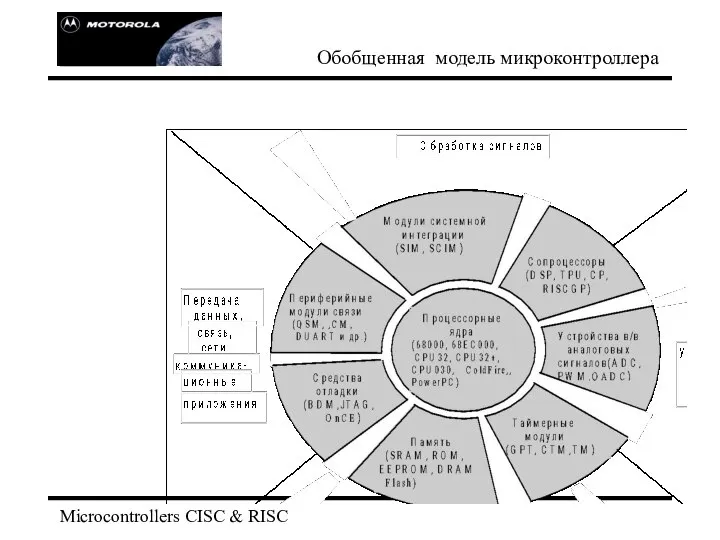

- 3. Microcontrollers CISC & RISC Обобщенная модель микроконтроллера

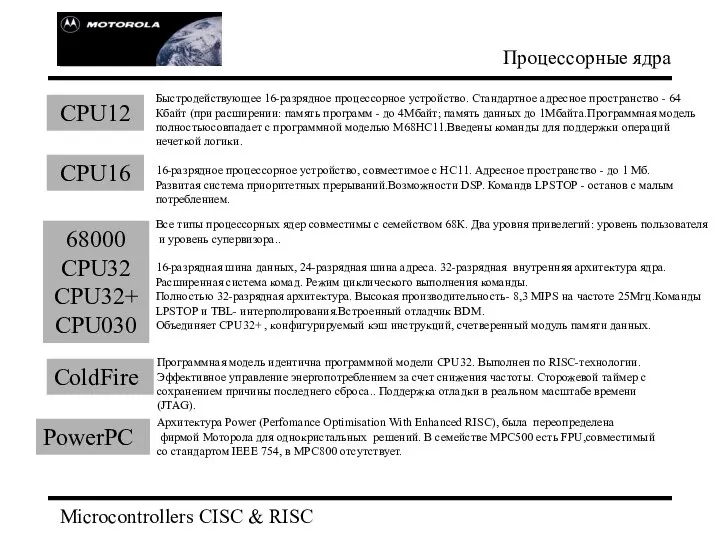

- 4. Microcontrollers CISC & RISC Процессорные ядра CPU12 CPU16 ColdFire PowerPC 68000 CPU32 CPU32+ CPU030 Быстродействующее 16-разрядное

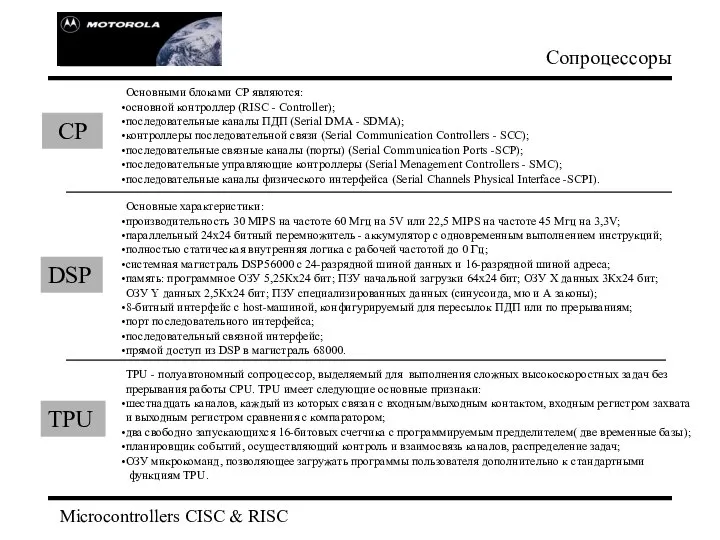

- 5. Microcontrollers CISC & RISC Сопроцессоры CP TPU DSP Основными блоками СР являются: основной контроллер (RISC -

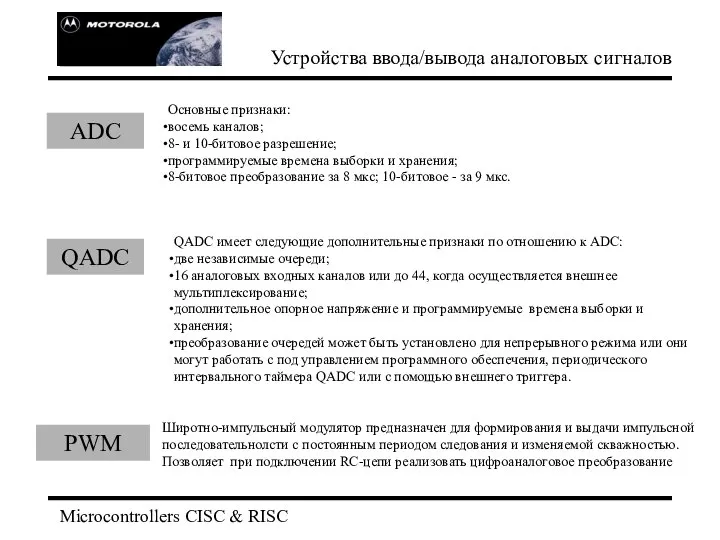

- 6. Microcontrollers CISC & RISC Устройства ввода/вывода аналоговых сигналов ADC QADC PWM Основные признаки: восемь каналов; 8-

- 7. Microcontrollers CISC & RISC Таймерные модули T GTM CTM Таймер общего назначения содержит: 11-канальный таймер; 9-ти

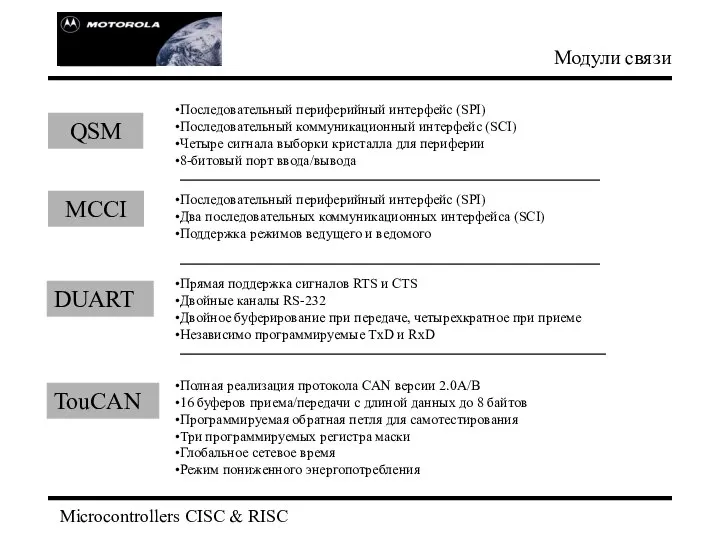

- 8. Microcontrollers CISC & RISC Модули связи QSM MCCI DUART TouCAN Последовательный периферийный интерфейс (SPI) Последовательный коммуникационный

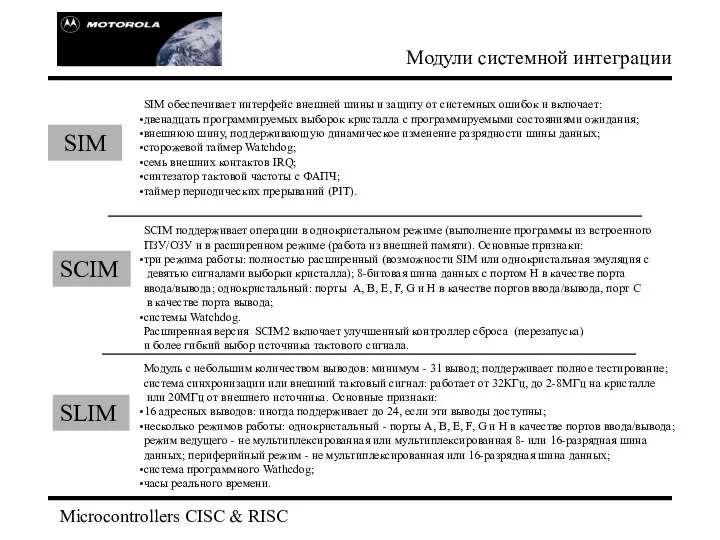

- 9. Microcontrollers CISC & RISC Модули системной интеграции SIM SCIM SLIM SIM обеспечивает интерфейс внешней шины и

- 10. Microcontrollers CISC & RISC Средства отладки BDM JTAG OnCE JTAG поддерживает nтестирование платы на основе стандарта

- 11. Microcontrollers CISC & RISC Модули памяти Flash EEPROM SRAM MRM TPU RAM ROM

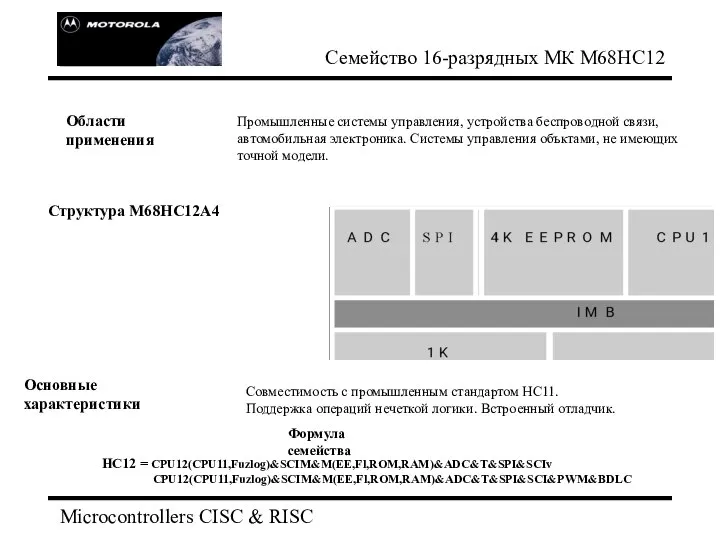

- 12. Microcontrollers CISC & RISC Cемейство 16-разрядных МК М68НС12 Промышленные системы управления, устройства беспроводной связи, автомобильная электроника.

- 13. Microcontrollers CISC & RISC Семейство М68НС12 Факторы успеха семейства М68НС12 Основан на промышленном стандарте М68НС11 Огромный

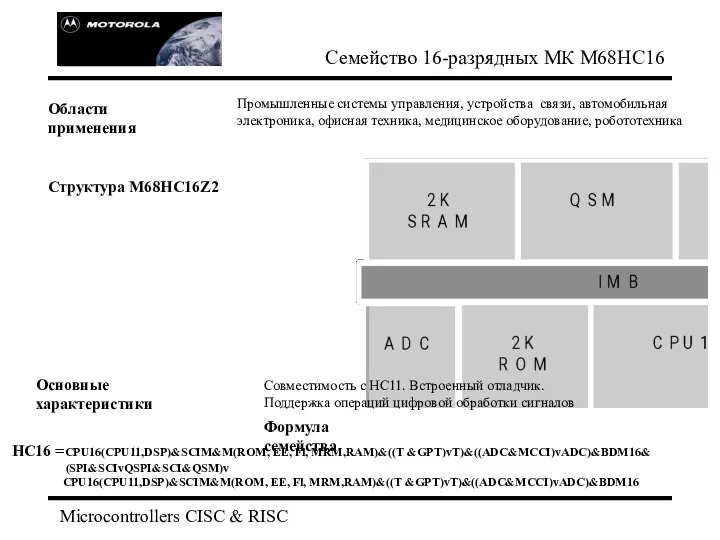

- 14. Microcontrollers CISC & RISC Семейство 16-разрядных МК М68НС16 Промышленные системы управления, устройства связи, автомобильная электроника, офисная

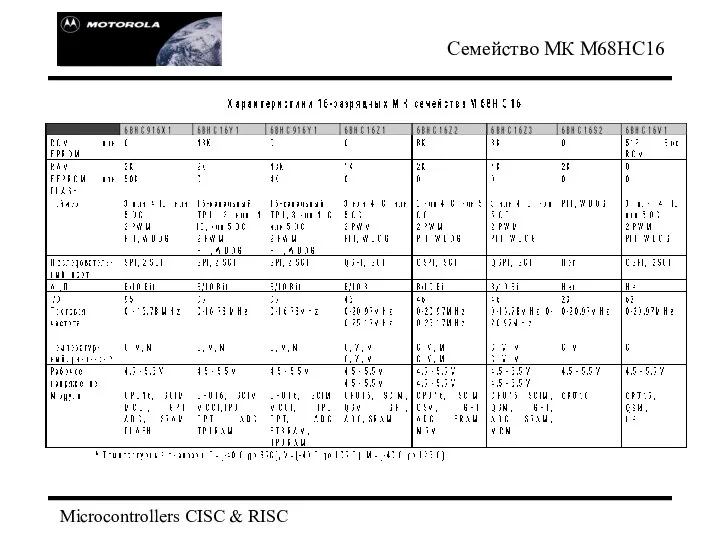

- 15. Microcontrollers CISC & RISC Семейство МК М68НС16

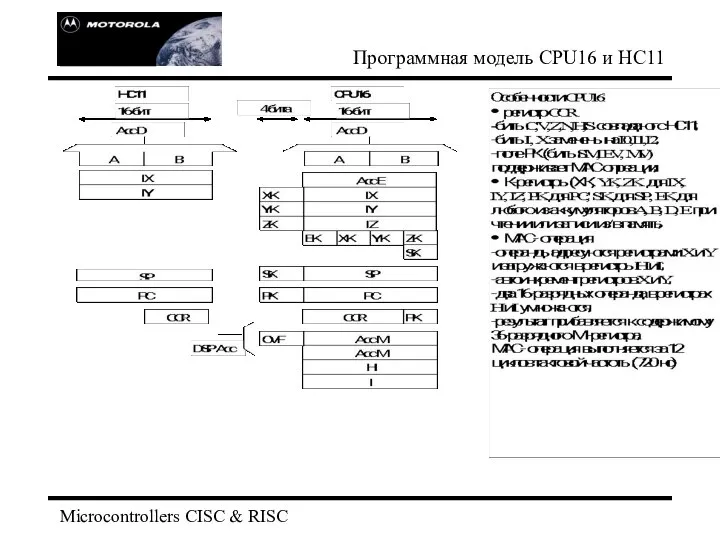

- 16. Microcontrollers CISC & RISC Программная модель CPU16 и НС11

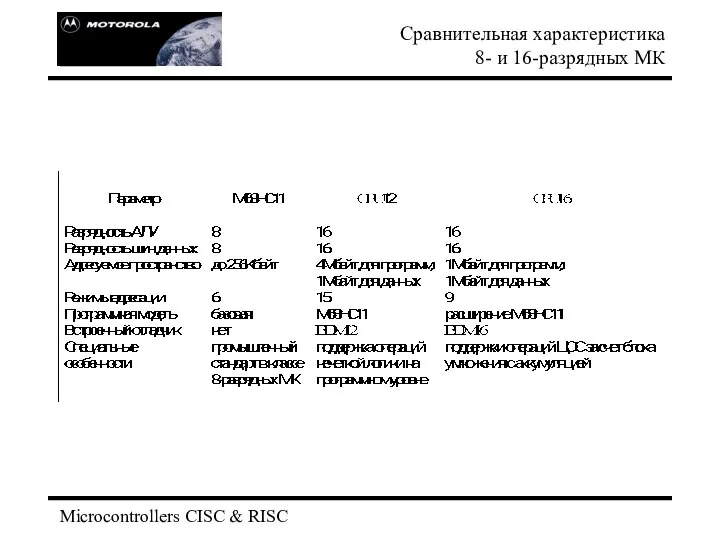

- 17. Microcontrollers CISC & RISC Сравнительная характеристика 8- и 16-разрядных МК

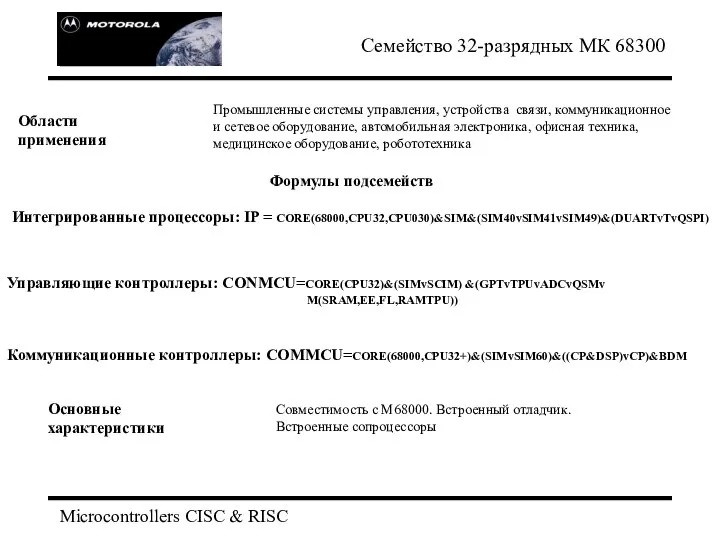

- 18. Microcontrollers CISC & RISC Семейство 32-разрядных МК 68300 Промышленные системы управления, устройства связи, коммуникационное и сетевое

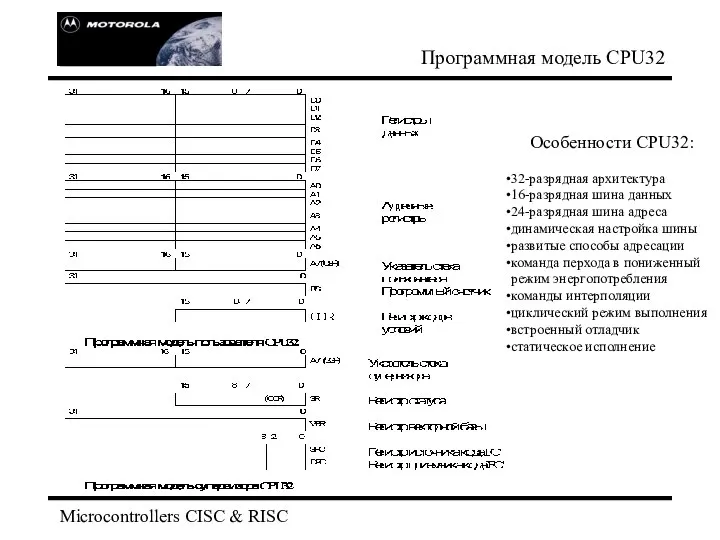

- 19. Microcontrollers CISC & RISC Программная модель CPU32 Особенности СPU32: 32-разрядная архитектура 16-разрядная шина данных 24-разрядная шина

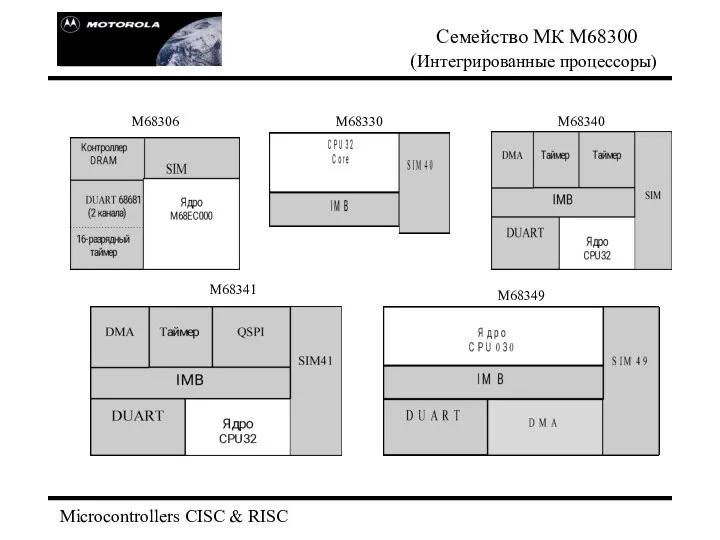

- 20. Microcontrollers CISC & RISC Семейство МК М68300 (Интегрированные процессоры) М68330 М68340 М68341 М68349

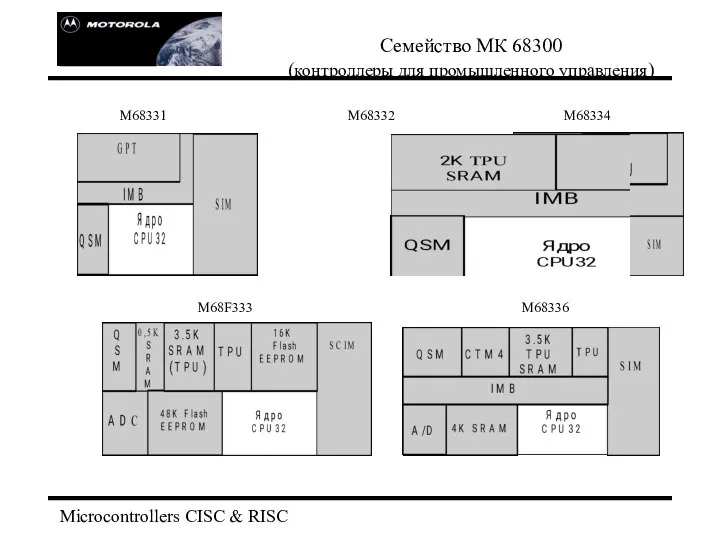

- 21. Microcontrollers CISC & RISC Семейство МК 68300 (контроллеры для промышленного управления) М68331 М68332 М68F333 М68334 М68336

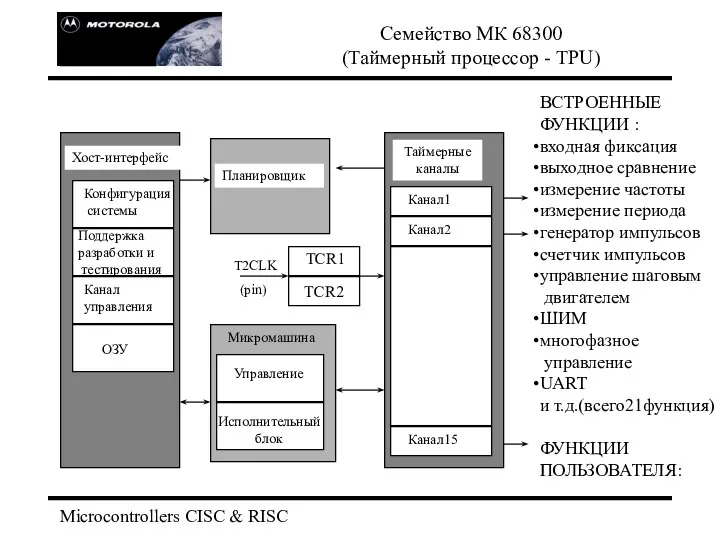

- 22. Microcontrollers CISC & RISC Семейство МК 68300 (Таймерный процессор - TPU) TCR2 Планировщик Хост-интерфейс Конфигурация системы

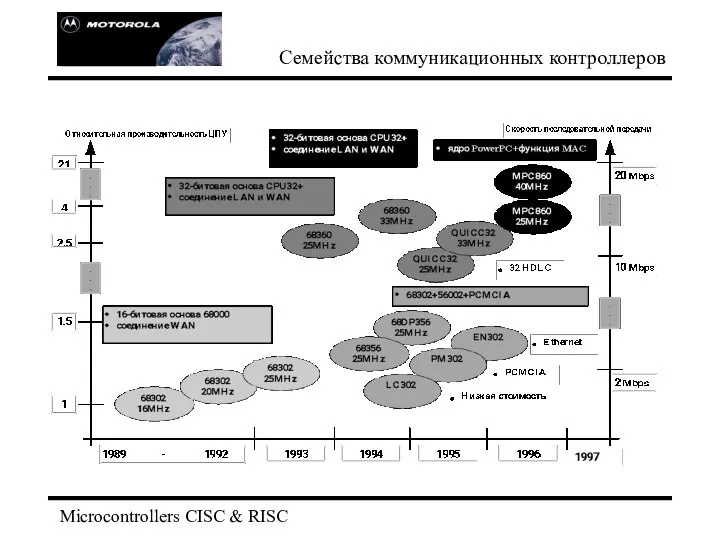

- 23. Microcontrollers CISC & RISC Семейства коммуникационных контроллеров

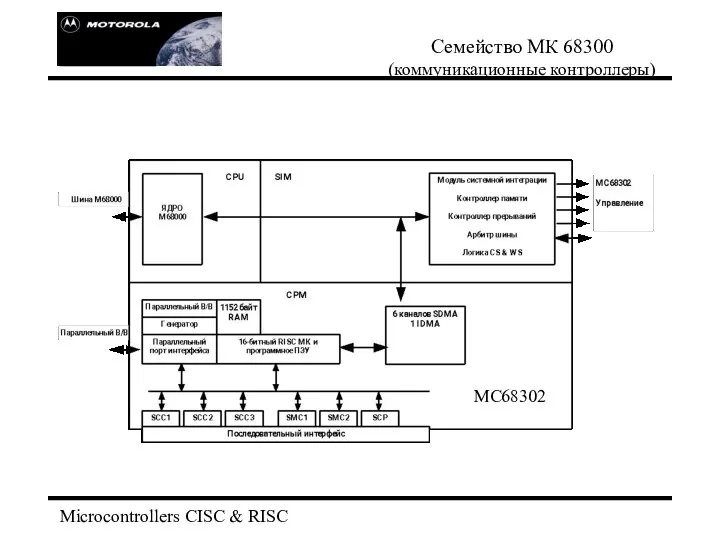

- 24. Microcontrollers CISC & RISC Семейство МК 68300 (коммуникационные контроллеры) МС68302

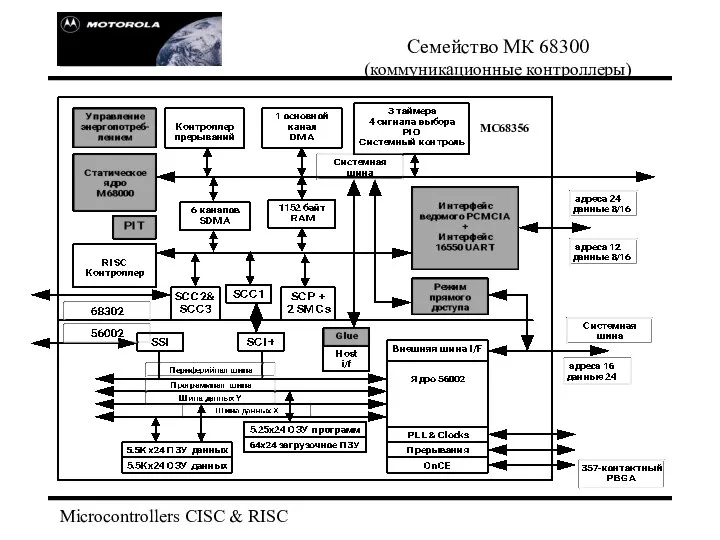

- 25. Семейство МК 68300 (коммуникационные контроллеры) Microcontrollers CISC & RISC MC68356

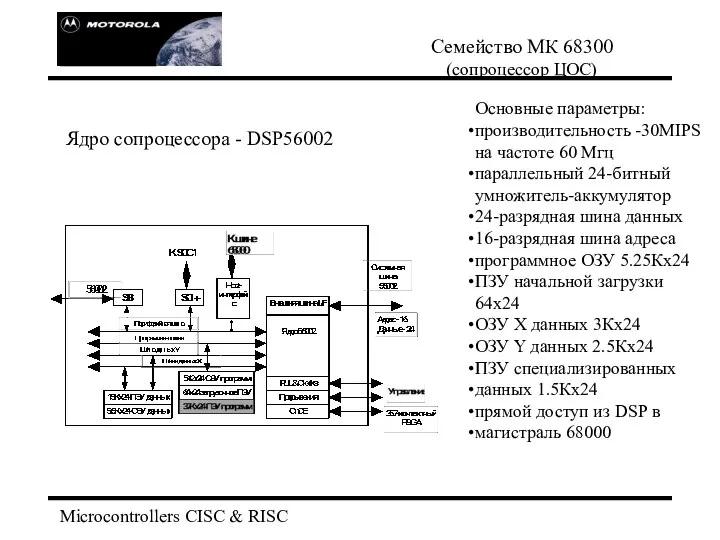

- 26. Семейство МК 68300 (сопроцессор ЦОС) Microcontrollers CISC & RISC Основные параметры: производительность -30MIPS на частоте 60

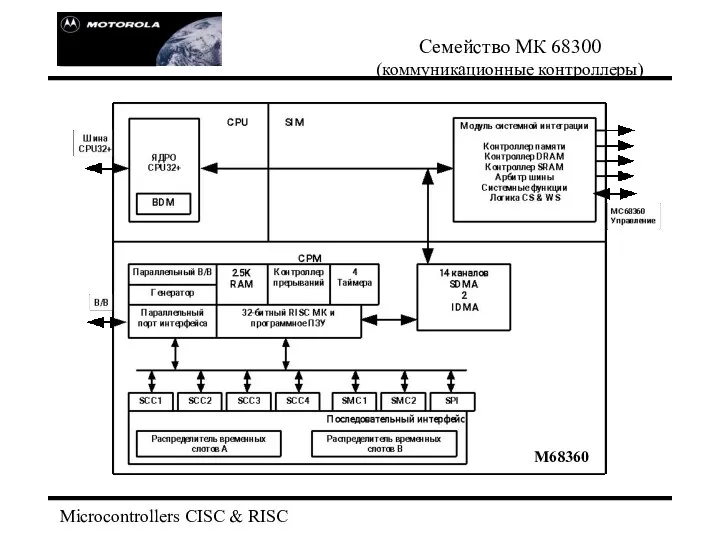

- 27. Microcontrollers CISC & RISC Семейство МК 68300 (коммуникационные контроллеры) М68360

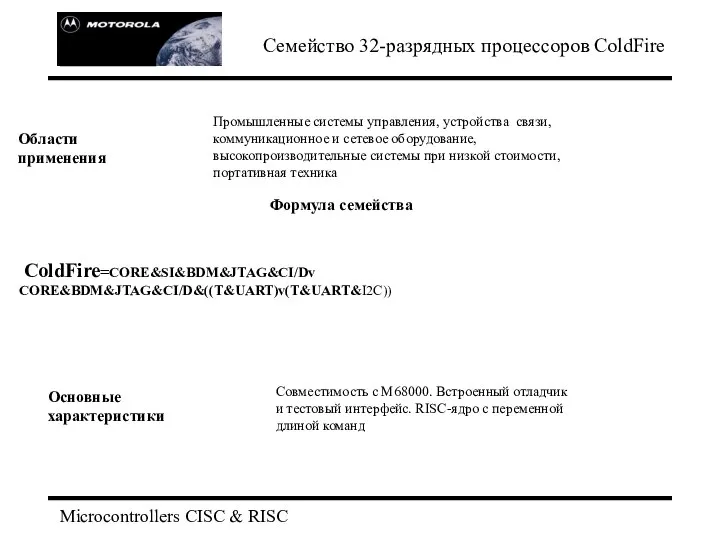

- 28. Microcontrollers CISC & RISC Семейство 32-разрядных процессоров ColdFire Промышленные системы управления, устройства связи, коммуникационное и сетевое

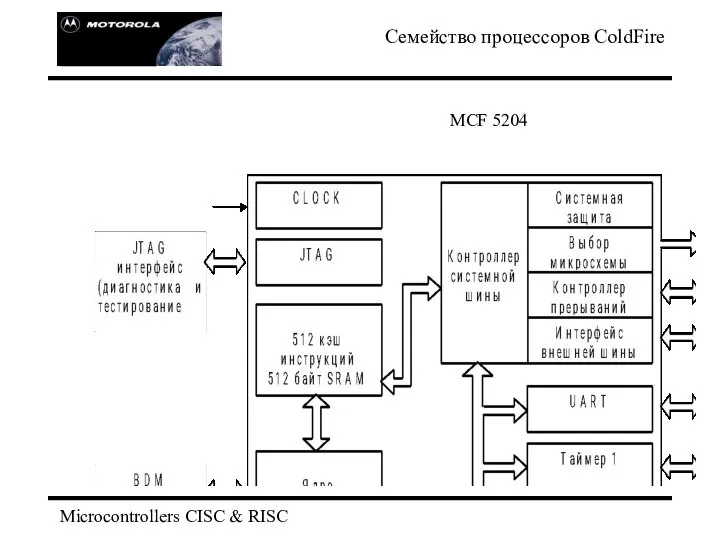

- 29. Microcontrollers CISC & RISC Семейство процессоров ColdFire MCF 5204

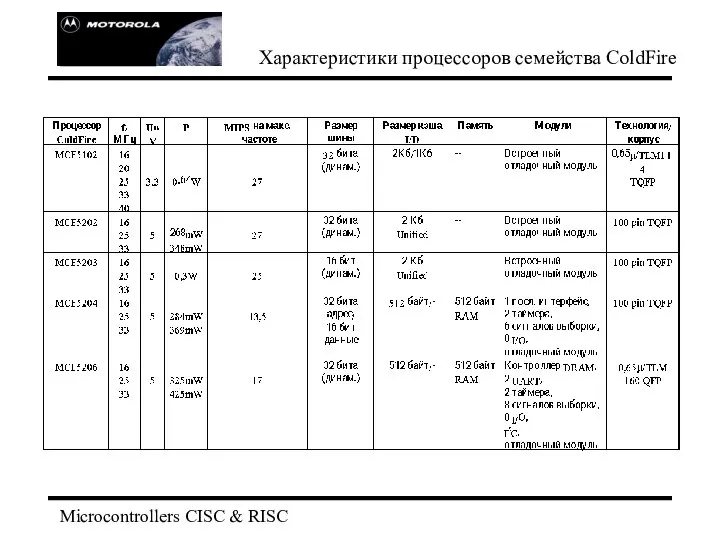

- 30. Microcontrollers CISC & RISC Характеристики процессоров семейства ColdFire

- 31. Microcontrollers CISC & RISC Семейство СoldFire Факторы успеха семейства ColdFire RISC-архитектура Высокая производительность Переменная длина команд

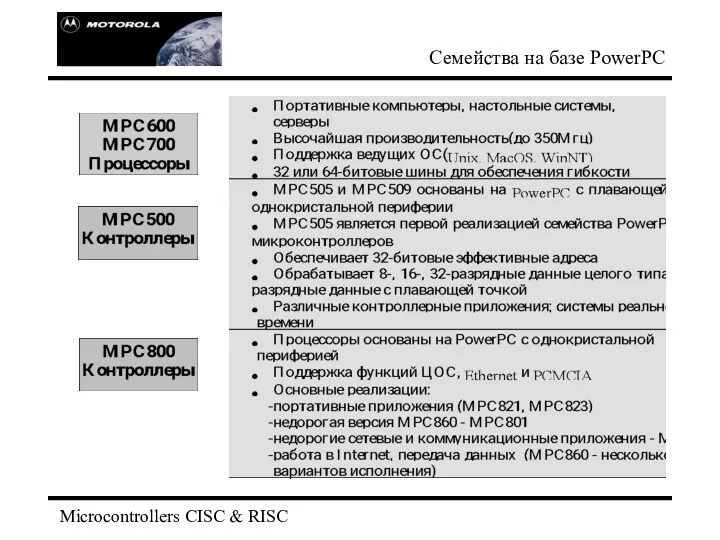

- 32. Microcontrollers CISC & RISC Семейства на базе PowerPC

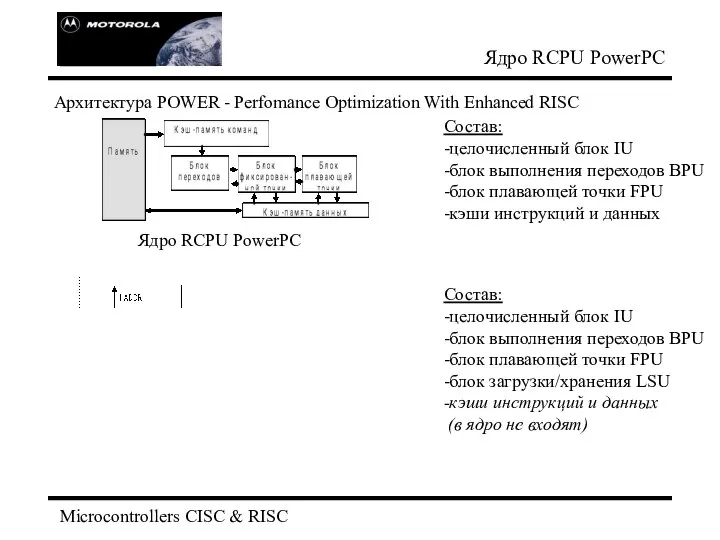

- 33. Microcontrollers CISC & RISC Ядро RCPU PowerPC Состав: -целочисленный блок IU -блок выполнения переходов BPU -блок

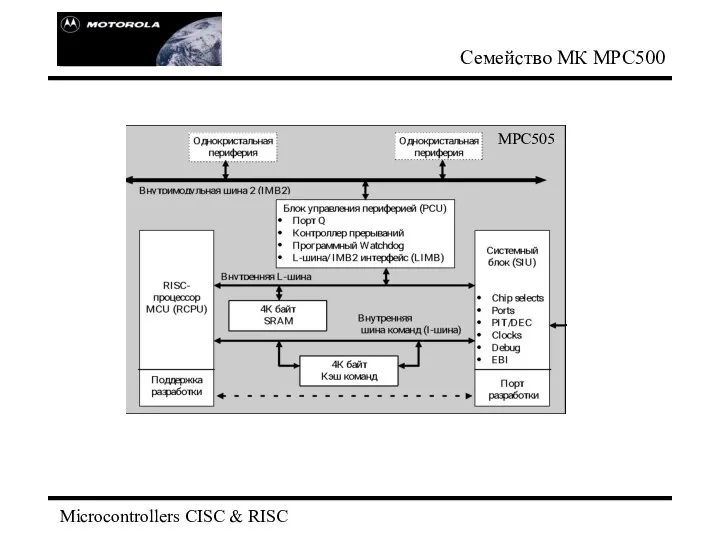

- 34. Microcontrollers CISC & RISC Семейство МК МРС500 МРС505

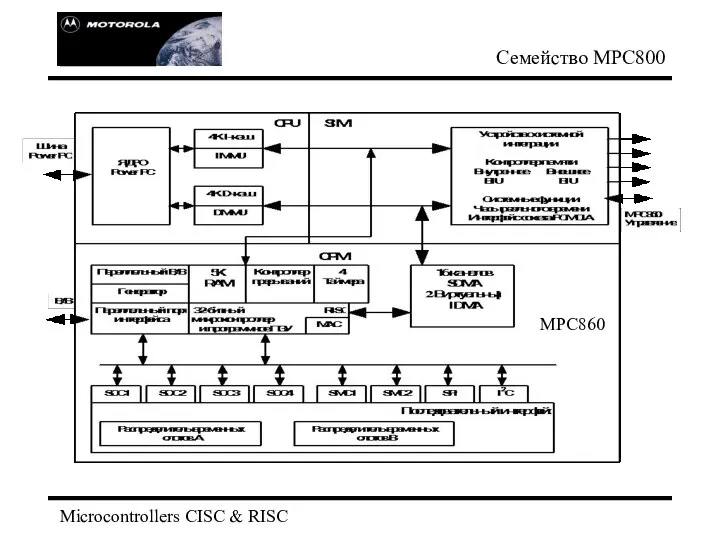

- 35. Microcontrollers CISC & RISC Семейство МРС800 МРС860

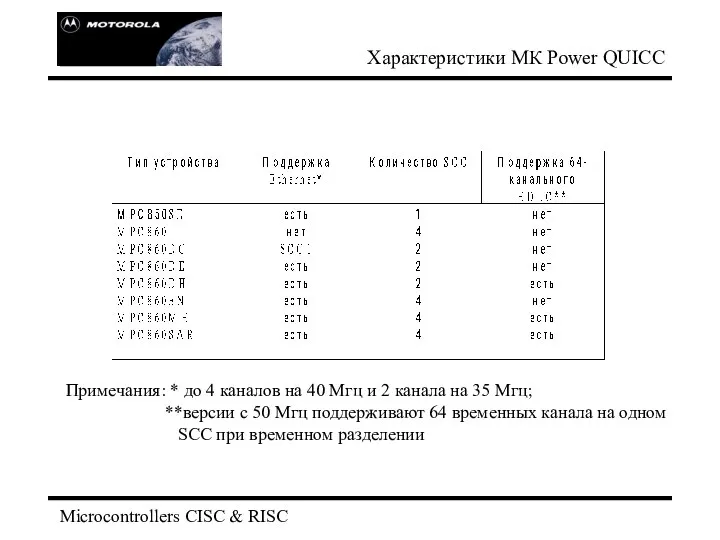

- 36. Microcontrollers CISC & RISC Характеристики МК Power QUICC Примечания: * до 4 каналов на 40 Мгц

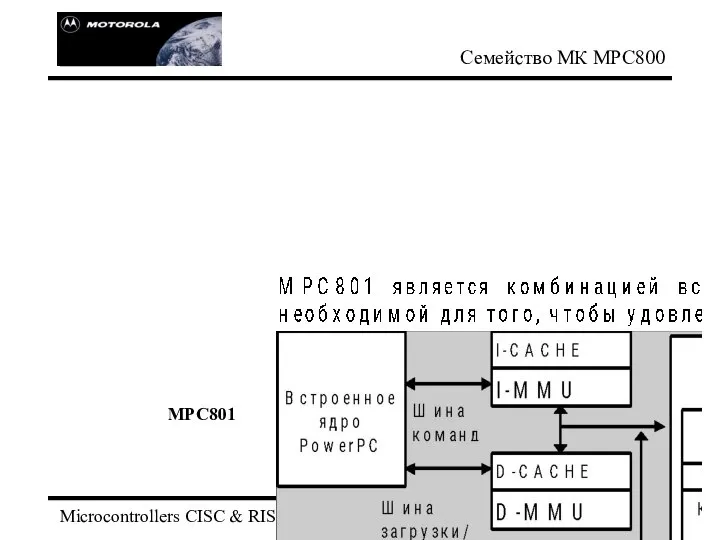

- 37. Microcontrollers CISC & RISC Семейство МК МРС800 МРС801

- 38. Microcontrollers CISC & RISC Семейство МК МРС800 MPC821

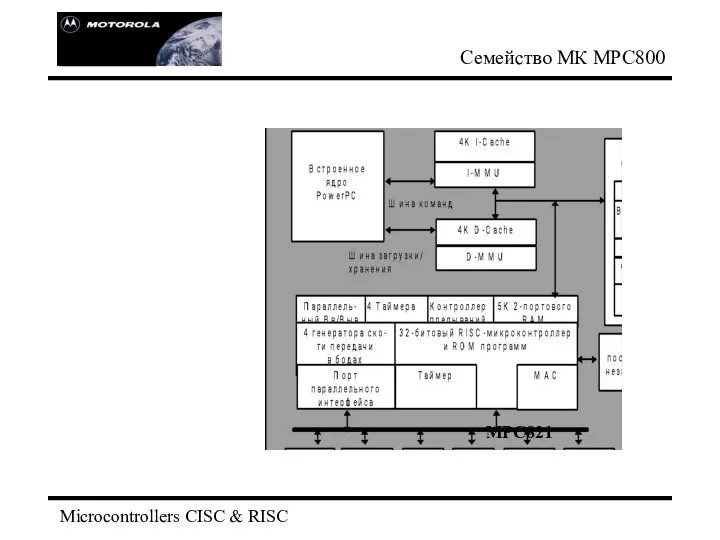

- 39. Семейство МК МРС800 Microcontrollers CISC & RISC МРС823

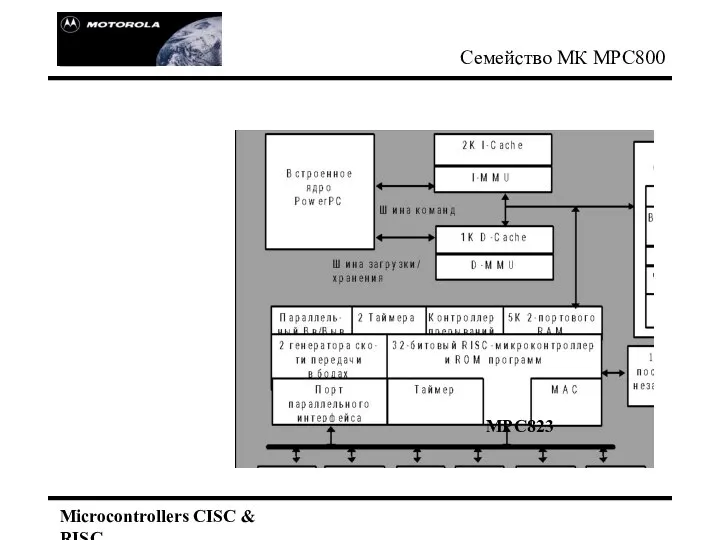

- 40. Microcontrollers CISC & RISC Управление энергопотреблением

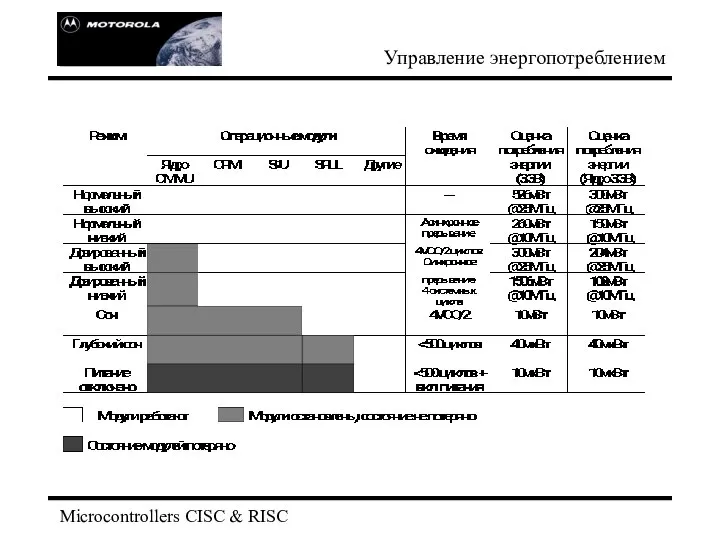

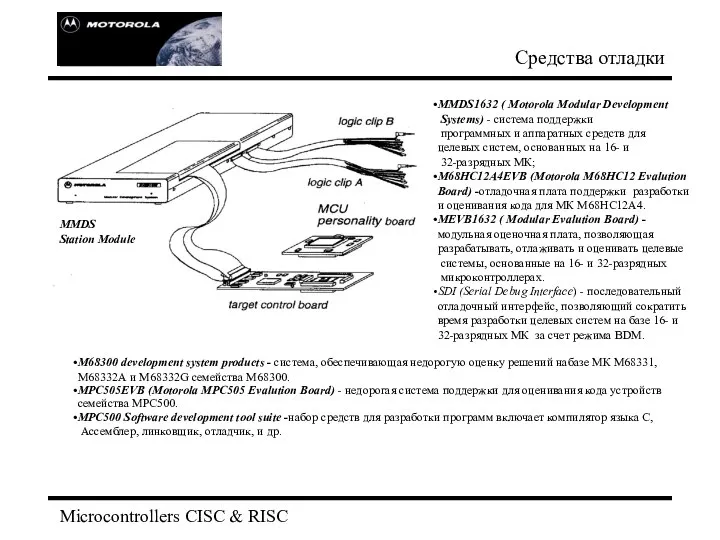

- 41. Microcontrollers CISC & RISC Средства отладки MMDS Station Module MMDS1632 ( Motorola Modular Development Systems) -

- 42. Microcontrollers CISC & RISC Средства отладки (MMDS1632) Прямое соединение станции с платформой Гибкое соединение станции с

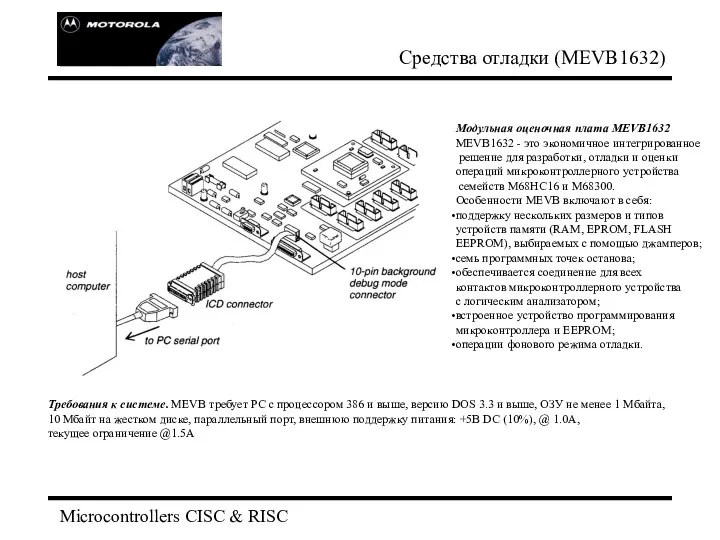

- 43. Microcontrollers CISC & RISC Средства отладки (MEVB1632) Модульная оценочная плата MEVB1632 MEVB1632 - это экономичное интегрированное

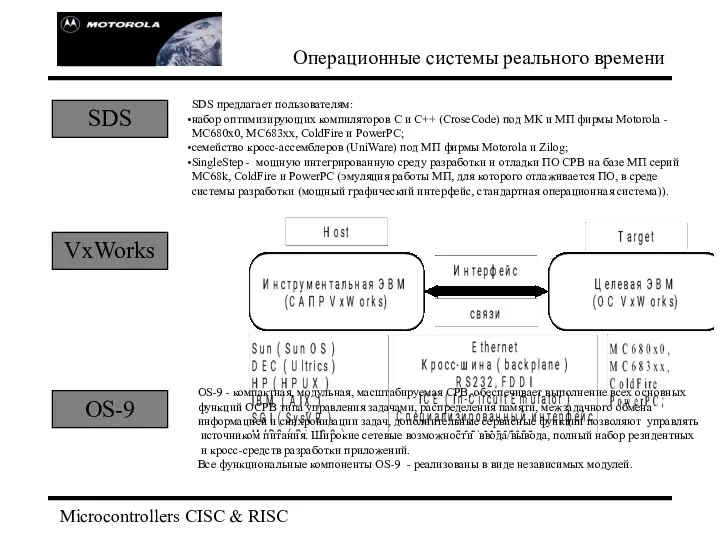

- 44. Microcontrollers CISC & RISC Операционные системы реального времени SDS VxWorks OS-9 SDS предлагает пользователям: набор оптимизирующих

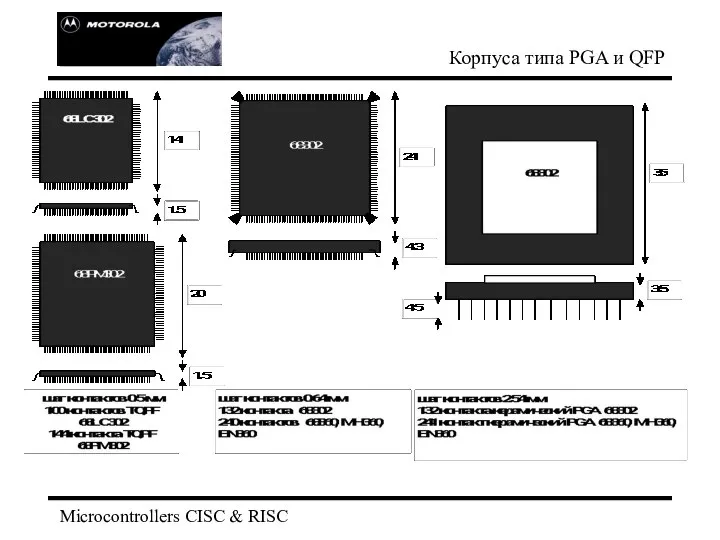

- 45. Microcontrollers CISC & RISC Корпуса типа PGA и QFP

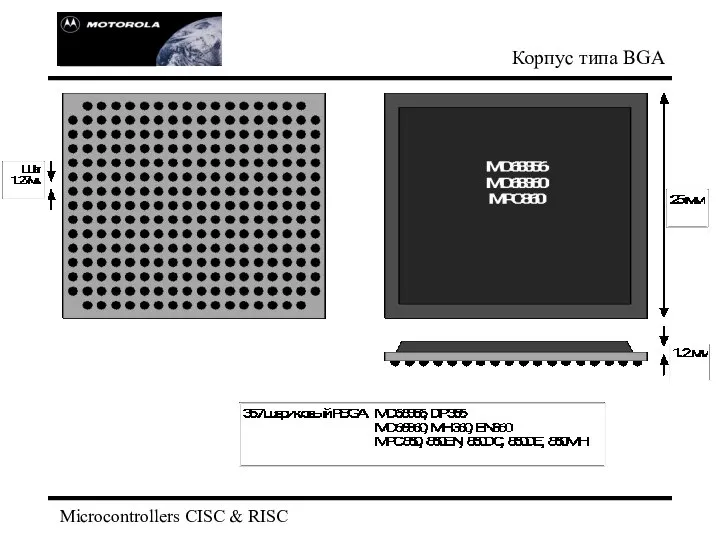

- 46. Microcontrollers CISC & RISC Корпус типа BGA

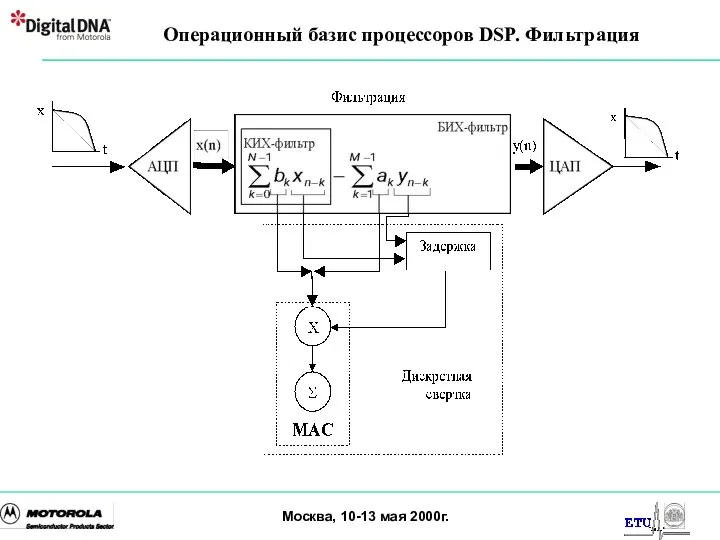

- 47. Операционный базис процессоров DSP. Фильтрация Москва, 10-13 мая 2000г.

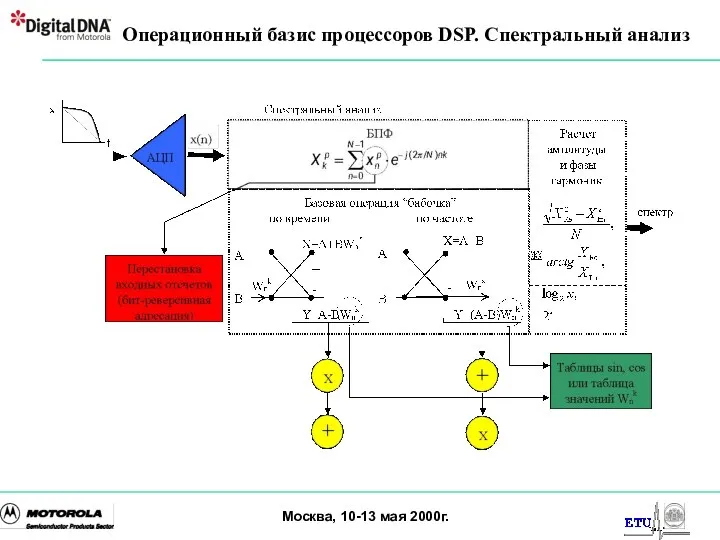

- 48. Операционный базис процессоров DSP. Спектральный анализ Москва, 10-13 мая 2000г.

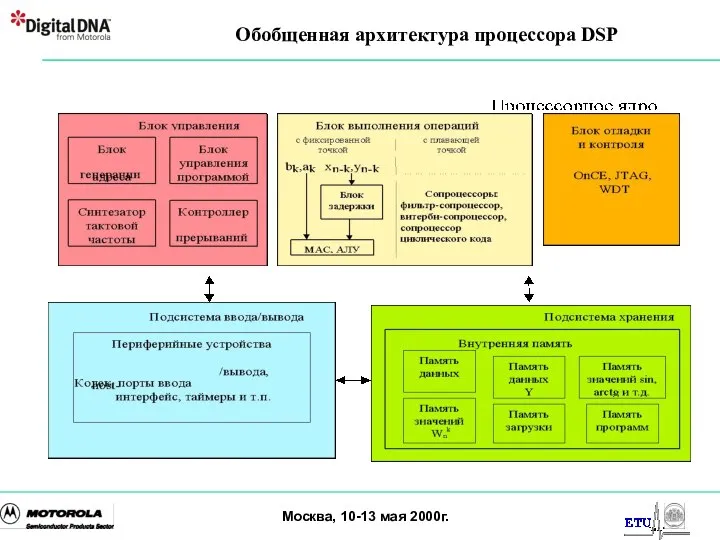

- 49. Обобщенная архитектура процессора DSP Москва, 10-13 мая 2000г.

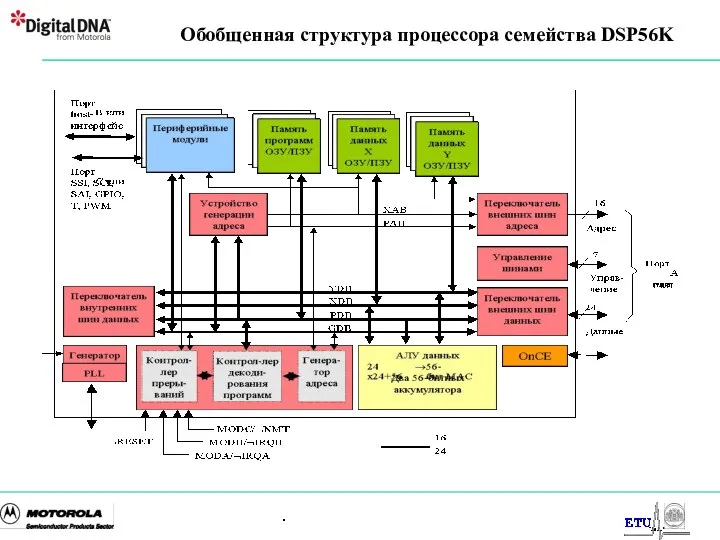

- 50. Обобщенная структура процессора семейства DSP56K .

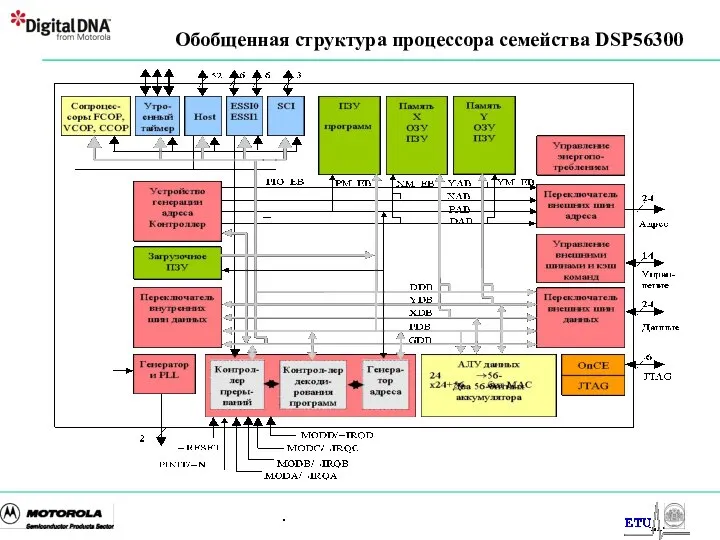

- 51. . Обобщенная структура процессора семейства DSP56300

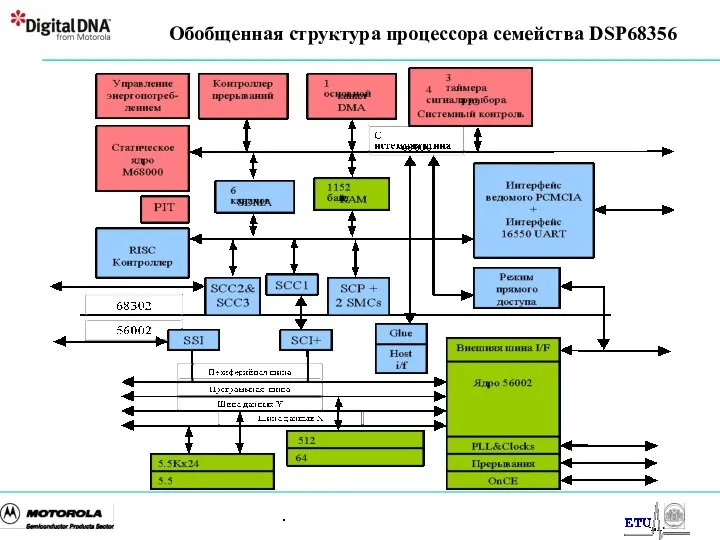

- 52. . Обобщенная структура процессора семейства DSP68356

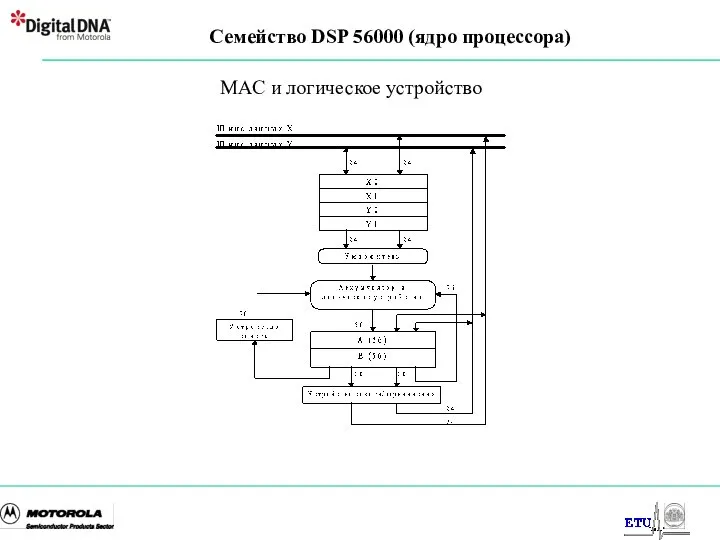

- 53. Семейство DSP 56000 (ядро процессора) MAC и логическое устройство

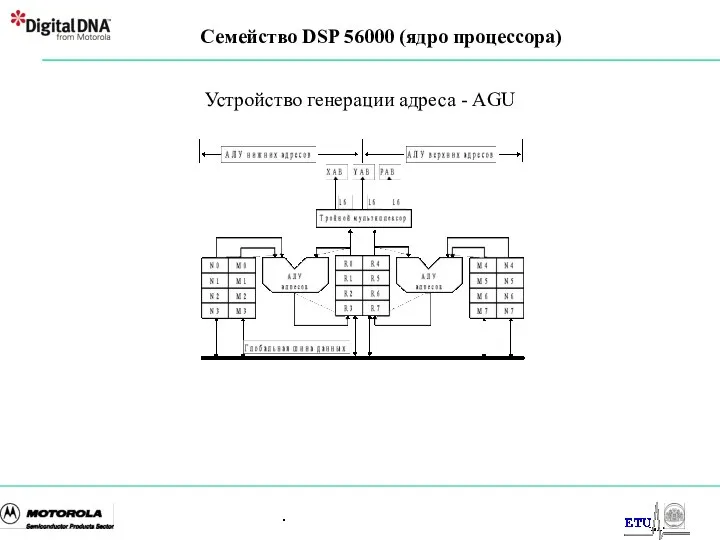

- 54. . Семейство DSP 56000 (ядро процессора) Устройство генерации адреса - AGU

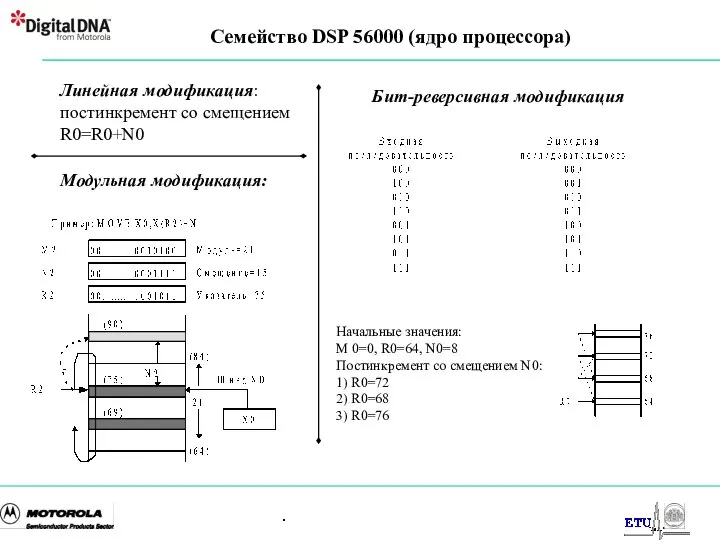

- 55. . Начальные значения: M 0=0, R0=64, N0=8 Постинкремент со смещением N0: 1) R0=72 2) R0=68 3)

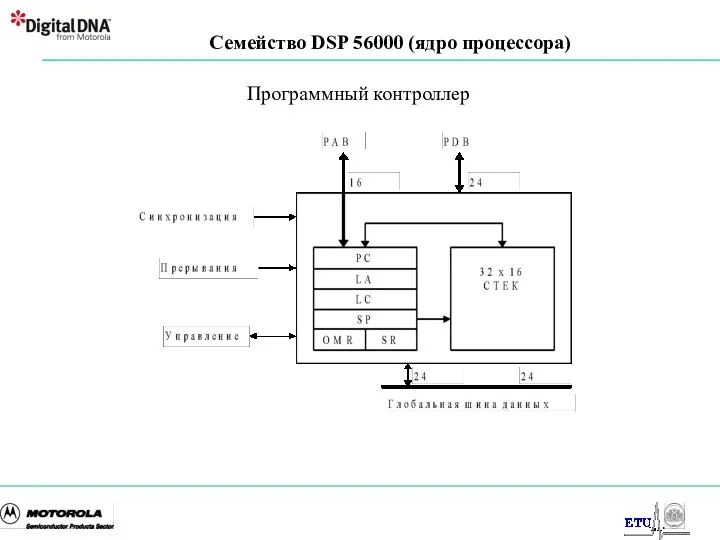

- 56. Семейство DSP 56000 (ядро процессора) Программный контроллер

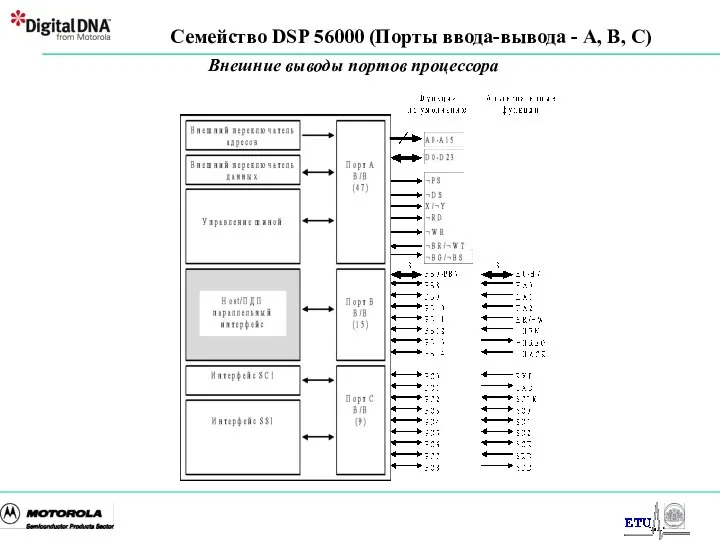

- 57. Семейство DSP 56000 (Порты ввода-вывода - A, B, C) Внешние выводы портов процессора

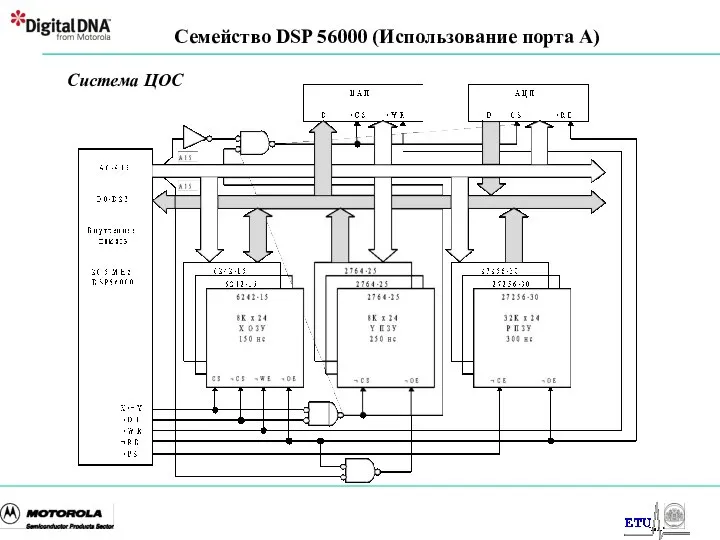

- 58. Семейство DSP 56000 (Использование порта А) Система ЦОС

- 59. . ХАРАКТЕРИСТИКИ DSP56300 Производительность - 100 MIPS на сегодняшний день, следующие ядра используют новые HiP-процессы Совместимость

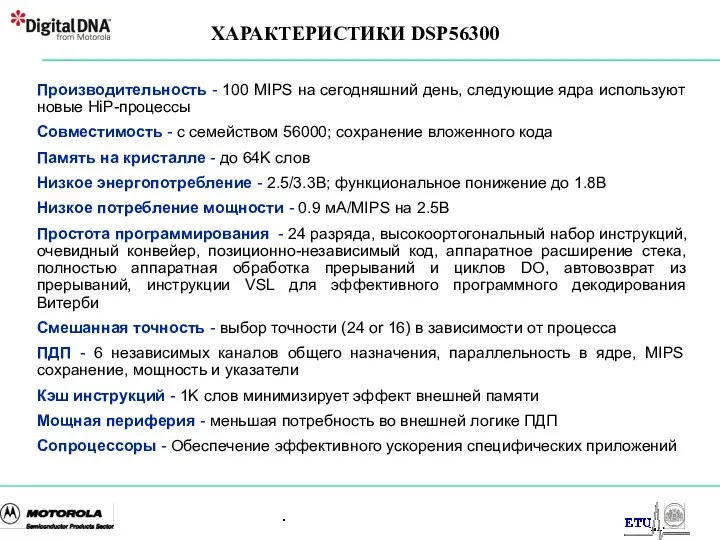

- 60. . ОСОБЕННОСТИ DSP56300 Выполнение текущей инструкции DSP (например, умножение с аккумулированием) за два внутренних цикла (2X-механизм)

- 61. . Архитектура DSP56300 Совместимость кода с архитектурой DSP56000 пути перехода для пользователей DSP56000 Процессорное ядро арифметико-логическое

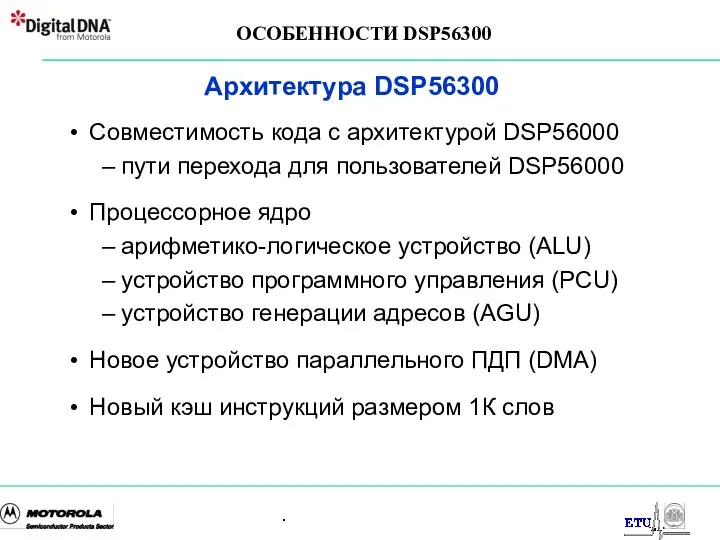

- 62. одна инструкция МАС за один цикл полностью конвейеризованный 24 x 24 параллельный умножитель-аккумулятор 56-битное параллельное устройство

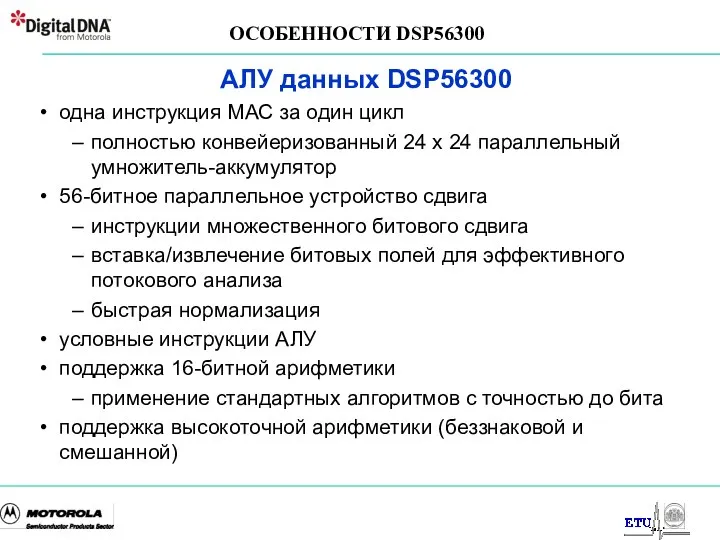

- 63. . Контроллер ПДП DSP56300 Скорость передачи - 24 бита/2 цикла, 120Mбайт @ 80MГц Параллельное выполнение операций

- 64. . Оптимизация для низкого энергопотребления Большая функциональность (например, ПДП, устройство сдвига и т. д.) средств снижает

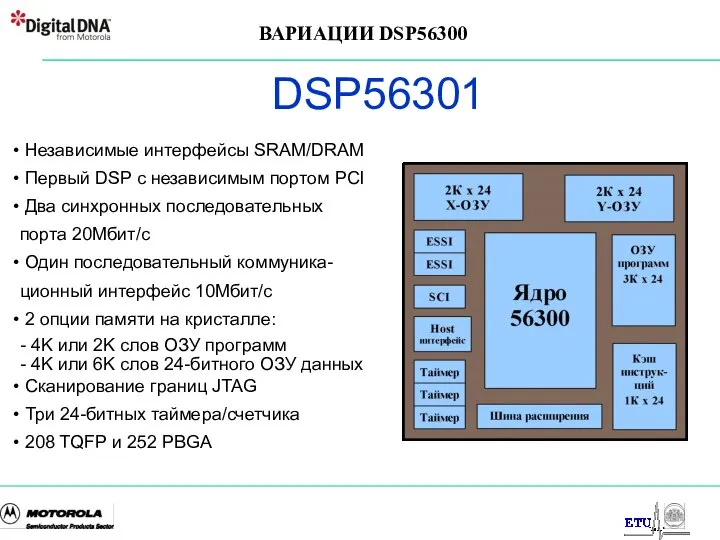

- 65. ВАРИАЦИИ DSP56300 DSP56301 Независимые интерфейсы SRAM/DRAM Первый DSP с независимым портом PCI Два синхронных последовательных порта

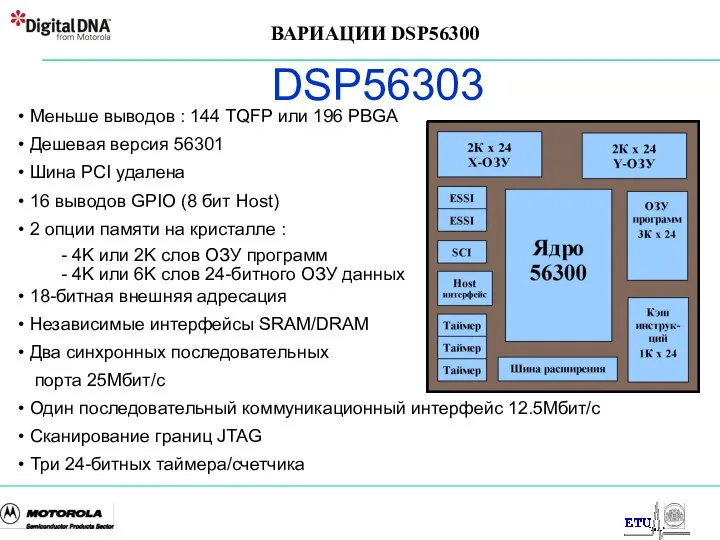

- 66. DSP56303 Меньше выводов : 144 TQFP или 196 PBGA Дешевая версия 56301 Шина PCI удалена 16

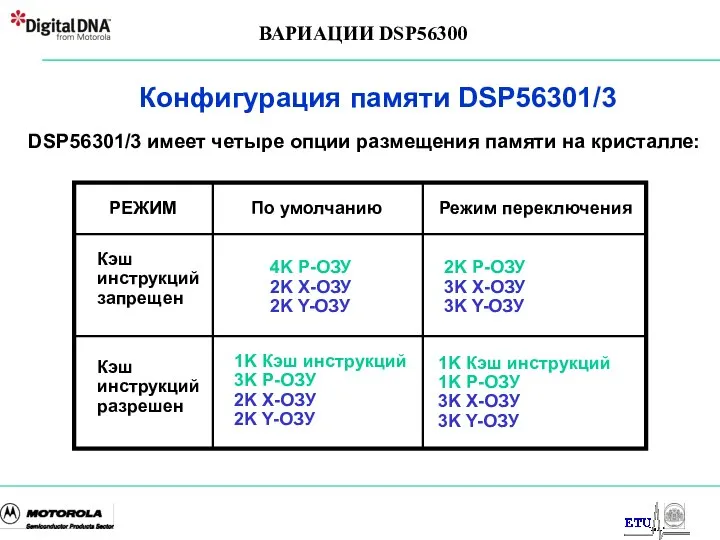

- 67. DSP56301/3 имеет четыре опции размещения памяти на кристалле: Конфигурация памяти DSP56301/3 ВАРИАЦИИ DSP56300

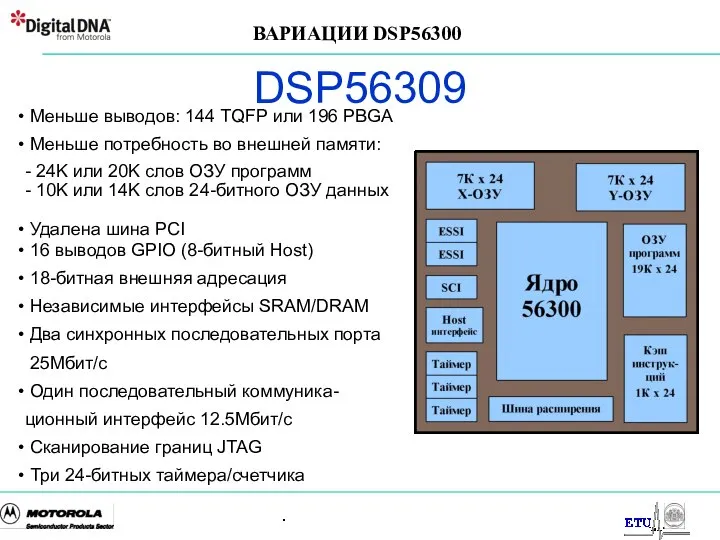

- 68. . DSP56309 Меньше выводов: 144 TQFP или 196 PBGA Меньше потребность во внешней памяти: - 24K

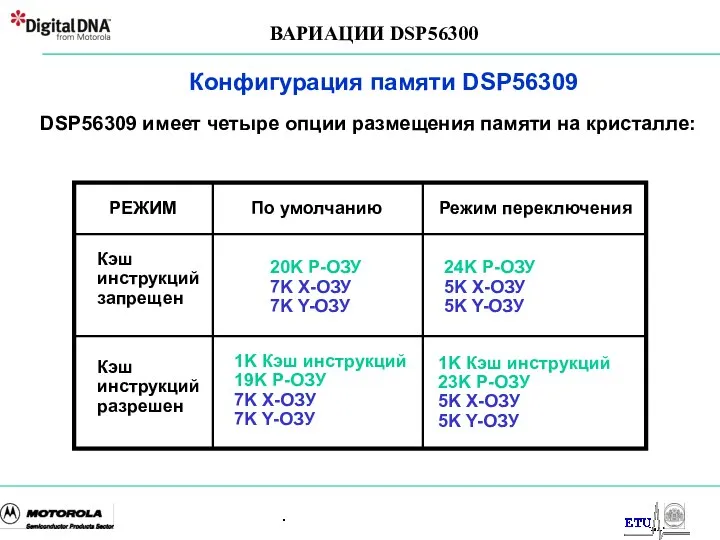

- 69. . DSP56309 имеет четыре опции размещения памяти на кристалле: Конфигурация памяти DSP56309 ВАРИАЦИИ DSP56300

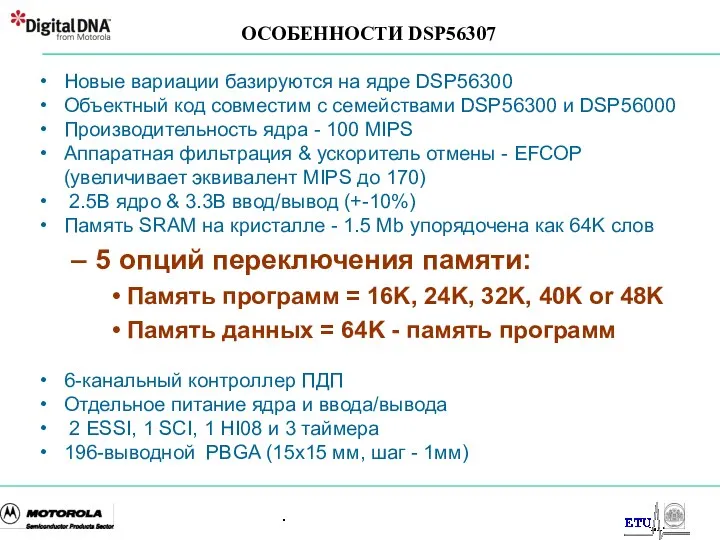

- 70. . Новые вариации базируются на ядре DSP56300 Объектный код совместим с семействами DSP56300 и DSP56000 Производительность

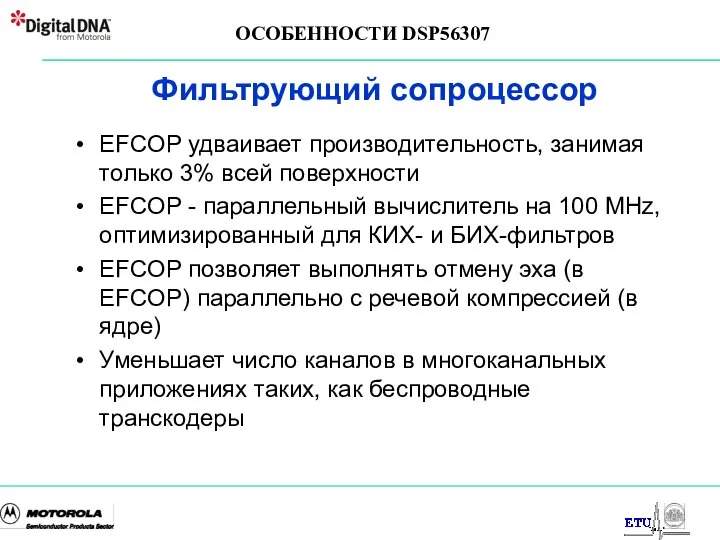

- 71. Фильтрующий сопроцессор EFCOP удваивает производительность, занимая только 3% всей поверхности EFCOP - параллельный вычислитель на 100

- 72. . Наборы ресурсов DSP Передающие беспроводные станции Многоканальные беспроводные локальные петли Мобильные сотовые центры переключений Контроллеры

- 73. Большой объем памяти на кристалле Высокая производительность без параллелизма Низкое потребление энергии (0.25 Вт) Нет состояний

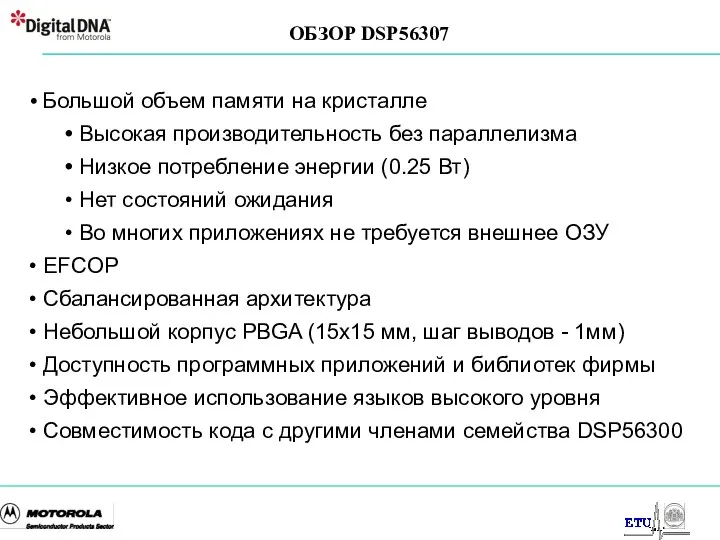

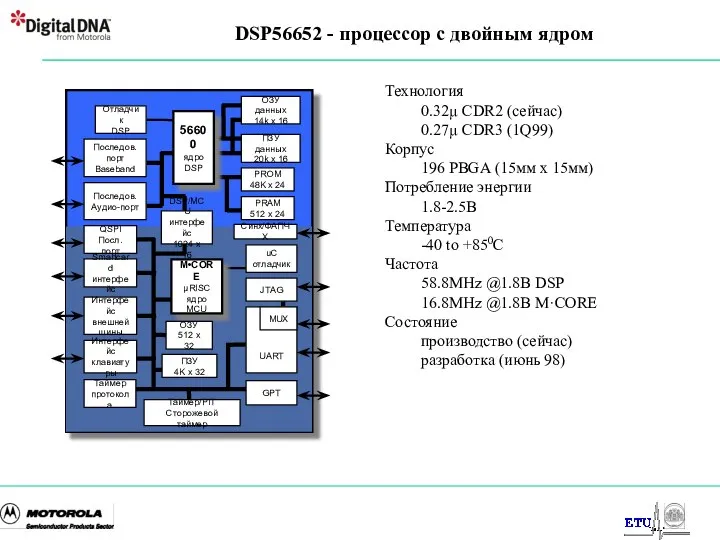

- 74. Технология 0.32µ CDR2 (сейчас) 0.27µ CDR3 (1Q99) Корпус 196 PBGA (15мм x 15мм) Потребление энергии 1.8-2.5В

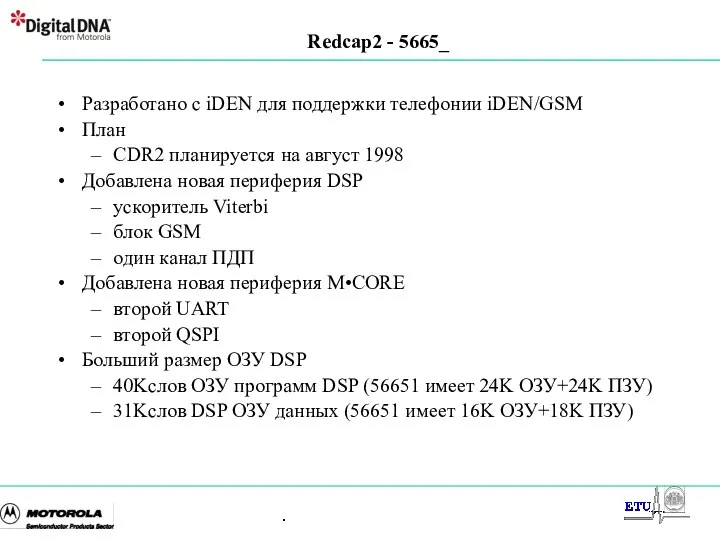

- 75. Redcap2 - 5665_ Разработано с iDEN для поддержки телефонии iDEN/GSM План CDR2 планируется на август 1998

- 77. Скачать презентацию

Викторина по творчеству и биографии Антона Павловича Чехова - презентация для начальной школы_

Викторина по творчеству и биографии Антона Павловича Чехова - презентация для начальной школы_ Человек и профессия

Человек и профессия Критерии успешности учителя, воспитателя

Критерии успешности учителя, воспитателя 21 нче февраль – Халыкара туган тел көне

21 нче февраль – Халыкара туган тел көне Функции по защите информации руководителя предприятия

Функции по защите информации руководителя предприятия Features that are available only in the Advanced version: 3D simulation

Features that are available only in the Advanced version: 3D simulation Презентация "Инвестиции муниципального образования" - скачать презентации по Экономике

Презентация "Инвестиции муниципального образования" - скачать презентации по Экономике Архитектура. Разновидности форм кровли. Учитель ИЗО,МОСШ№3, г. Белоярский, ХМАО Шаньшерова М.М.

Архитектура. Разновидности форм кровли. Учитель ИЗО,МОСШ№3, г. Белоярский, ХМАО Шаньшерова М.М. ПОДГОТОВКА К СЕРТИФИКАЦИОННОМУ АУДИТУ Евгения Соловей Сибирский сертификационный центр

ПОДГОТОВКА К СЕРТИФИКАЦИОННОМУ АУДИТУ Евгения Соловей Сибирский сертификационный центр  Неоинституциональная экономическая теория К.э.н., ст. препод. Бренделева Елена Алексеевна

Неоинституциональная экономическая теория К.э.н., ст. препод. Бренделева Елена Алексеевна  Региональные туристские организации

Региональные туристские организации Back-end. Протокол HTTP

Back-end. Протокол HTTP Чертежи фасадов зданий. Последовательность вычерчивания фасада здания. Наименование фасадов здания на чертеже

Чертежи фасадов зданий. Последовательность вычерчивания фасада здания. Наименование фасадов здания на чертеже Индуизм. Тилака или тилак. Теория и практика

Индуизм. Тилака или тилак. Теория и практика Развитие скоростно-силовых способностей юных волейболистов

Развитие скоростно-силовых способностей юных волейболистов Презентация Экологические права граждан и общественных объединений

Презентация Экологические права граждан и общественных объединений  Скрининг состояния организма за 5 минут с DePuls+

Скрининг состояния организма за 5 минут с DePuls+ Золотое сечение. Научно-практическая конфереция

Золотое сечение. Научно-практическая конфереция Работы победителей муниципального этапа областного конкурса детского и юношеского изобразительного искусства «Я рисую

Работы победителей муниципального этапа областного конкурса детского и юношеского изобразительного искусства «Я рисую Конфликты в школе

Конфликты в школе «Методы повышения учебной мотивации учащихся, развитие познавательной активности учащихся»

«Методы повышения учебной мотивации учащихся, развитие познавательной активности учащихся» Табакерка

Табакерка Хабар агенттіг

Хабар агенттіг телестудия LEONARUS

телестудия LEONARUS  Введение

Введение Поиск информации в сети интернет. Адресная строка

Поиск информации в сети интернет. Адресная строка Логические основы ЭВМ

Логические основы ЭВМ Распознаватели регулярных языков

Распознаватели регулярных языков