Содержание

- 2. Тема 1.1. Основные принципы построения систем ввода вывода и интерфейсов

- 3. Что такое система ввода-вывода и периферия? Система ввода-вывода-средства пере- дачи информации,объединяющих между собой основные устройства компьютера:

- 4. Роль и место систем ввода-вывода и интерфейсов в компьютере

- 6. ИНТЕРФЕЙС Средства и правила,обеспечивающие взаимосвязь устройств между собой,на- зываются интерфейсом. В интерфейсе стандартизируются: 1.Назначение и количество

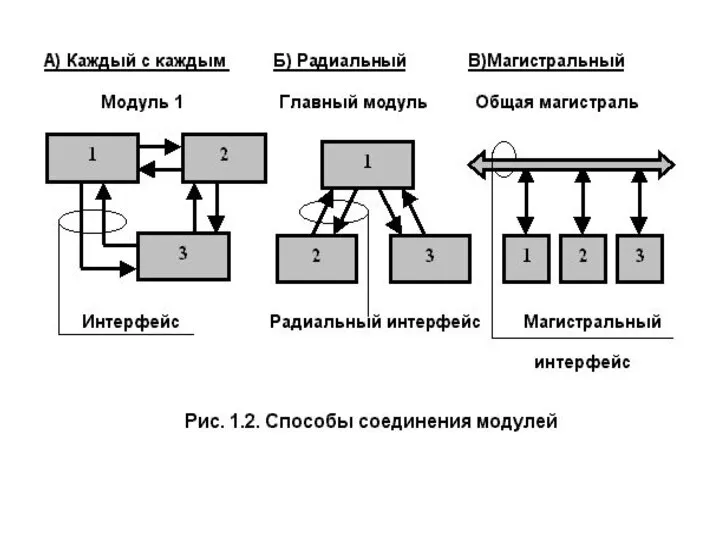

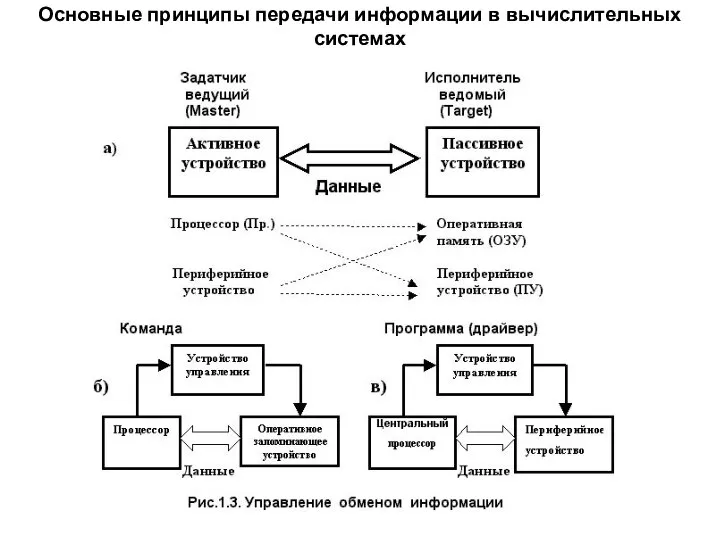

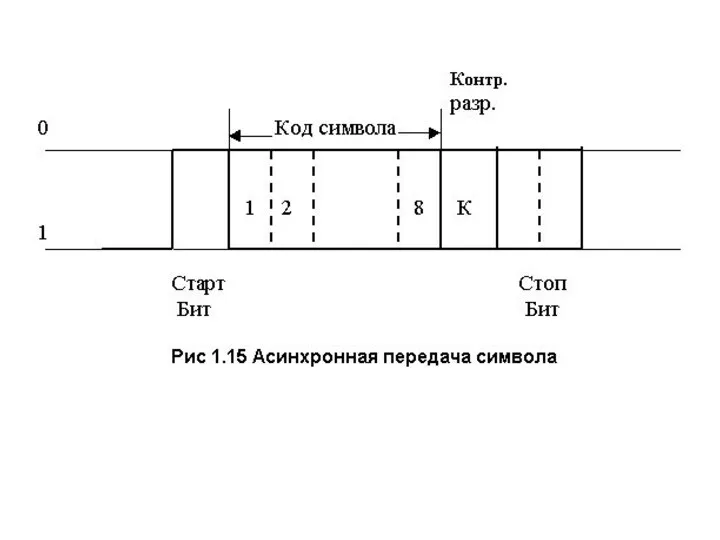

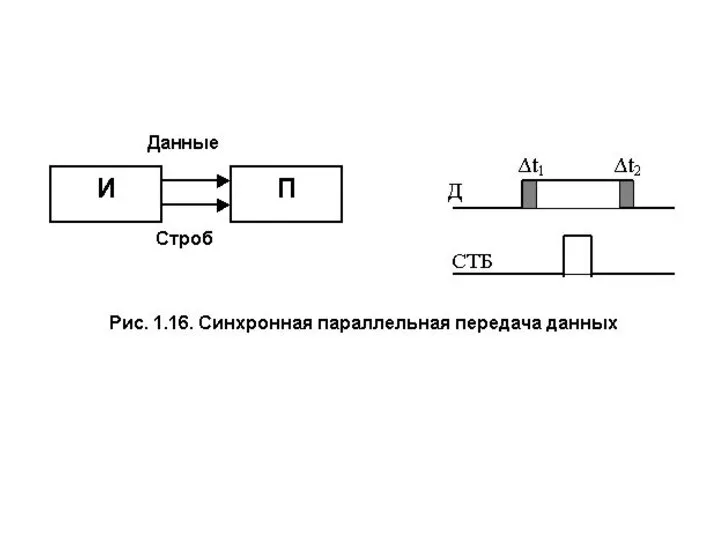

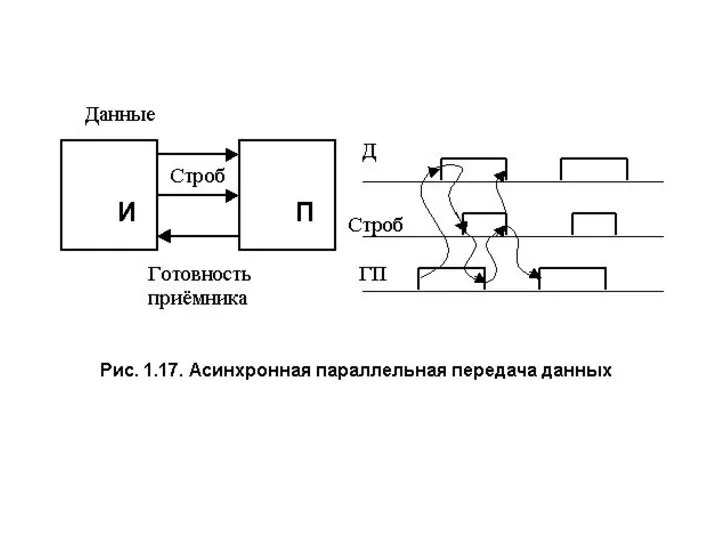

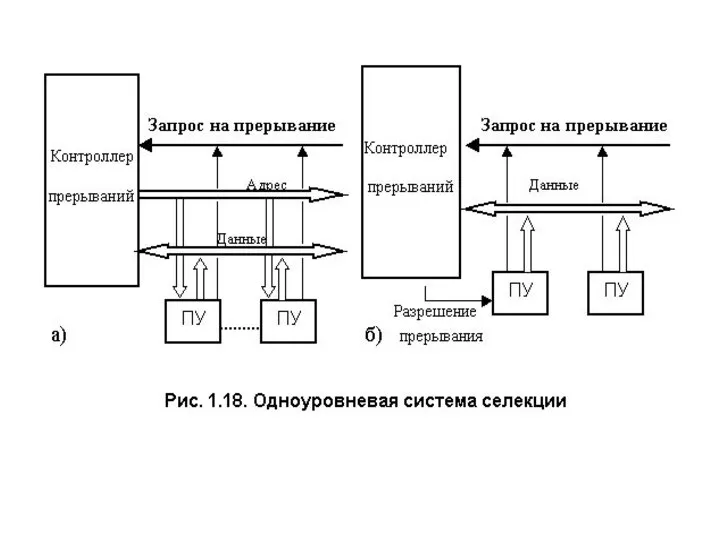

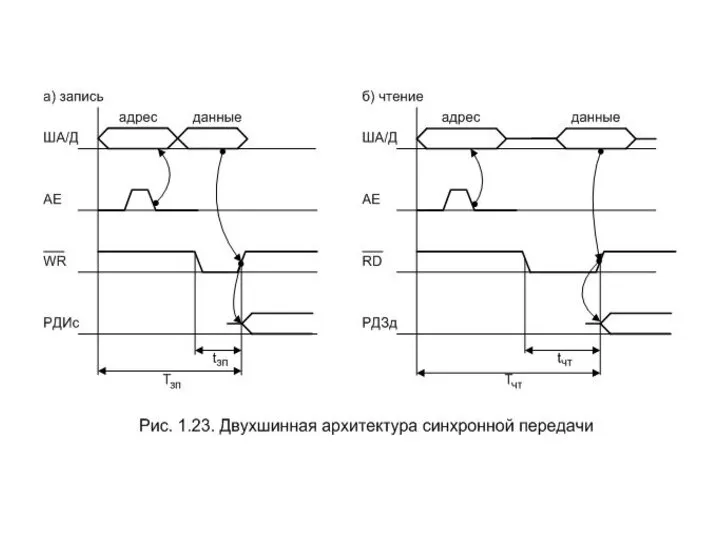

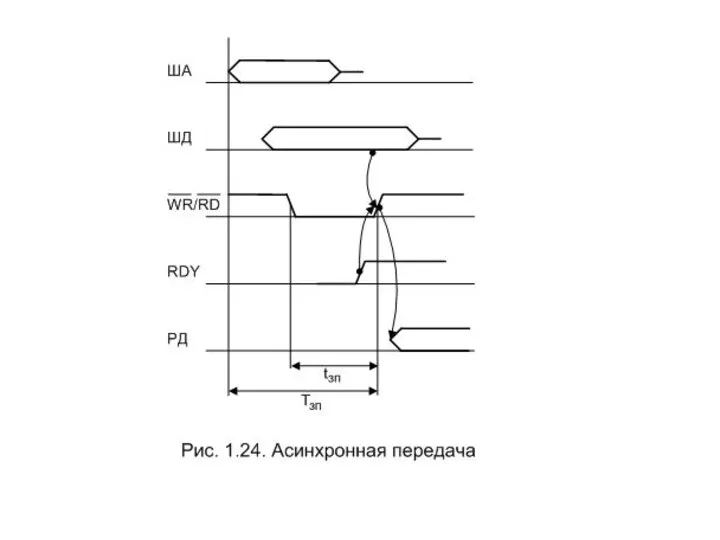

- 8. Основные принципы передачи информации в вычислительных системах

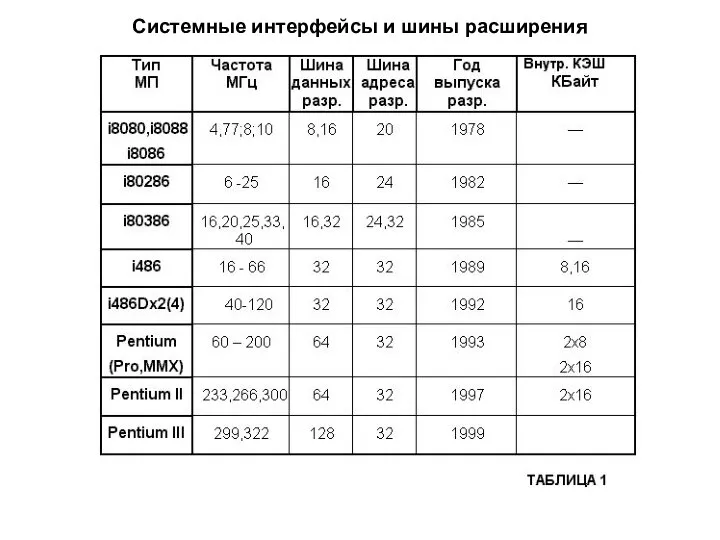

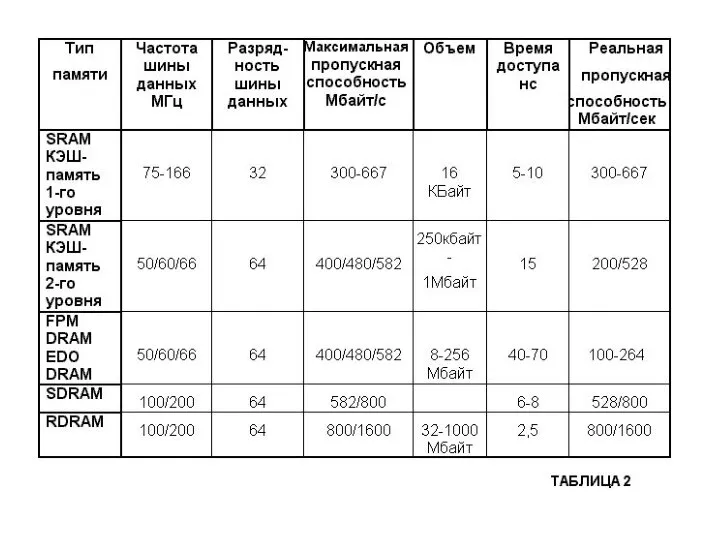

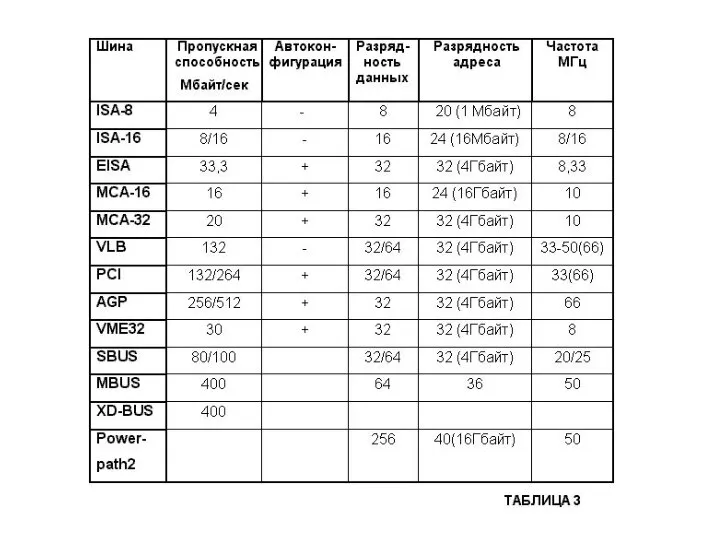

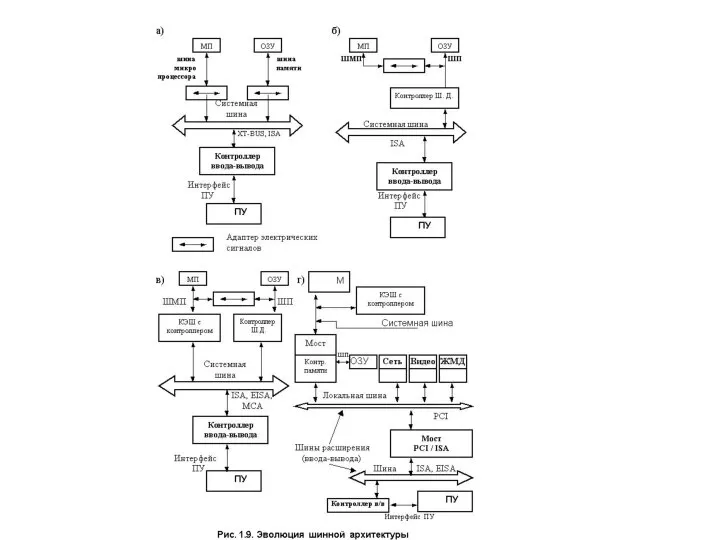

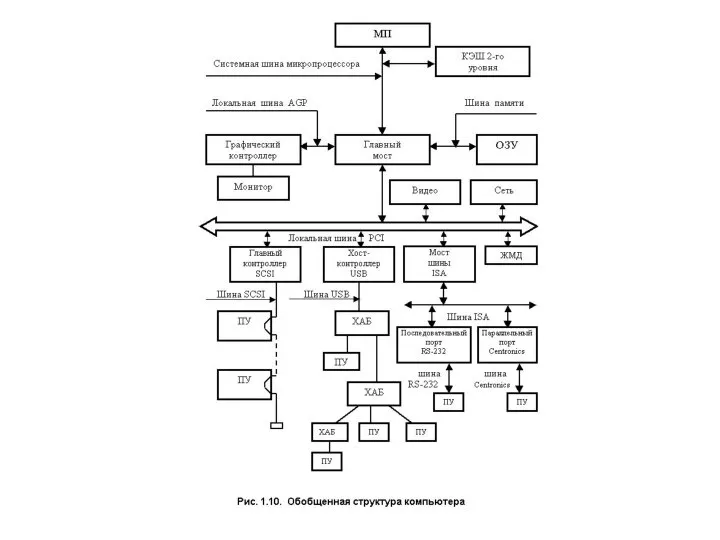

- 13. Системные интерфейсы и шины расширения

- 16. Интерфейсы периферийных устройств

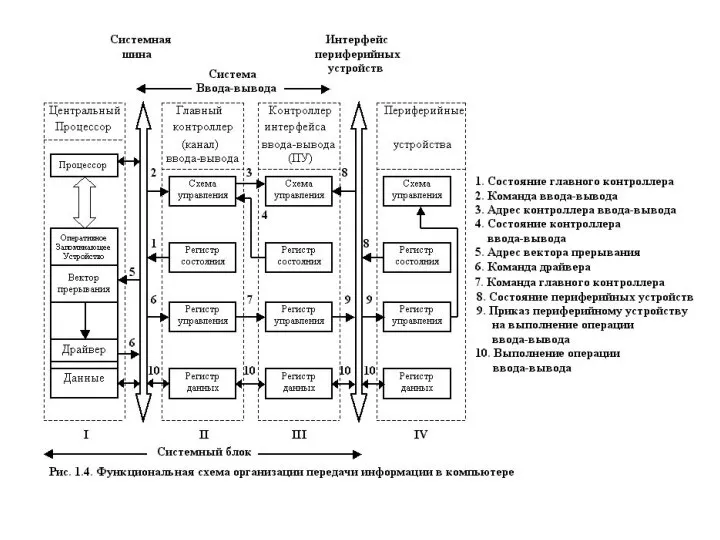

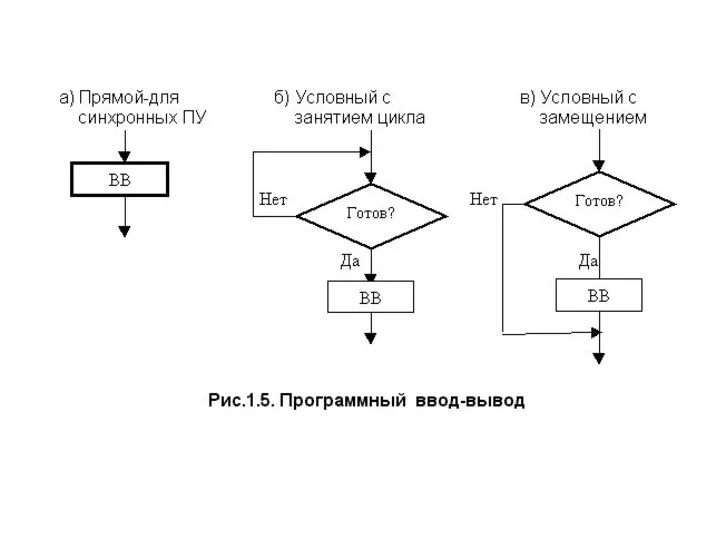

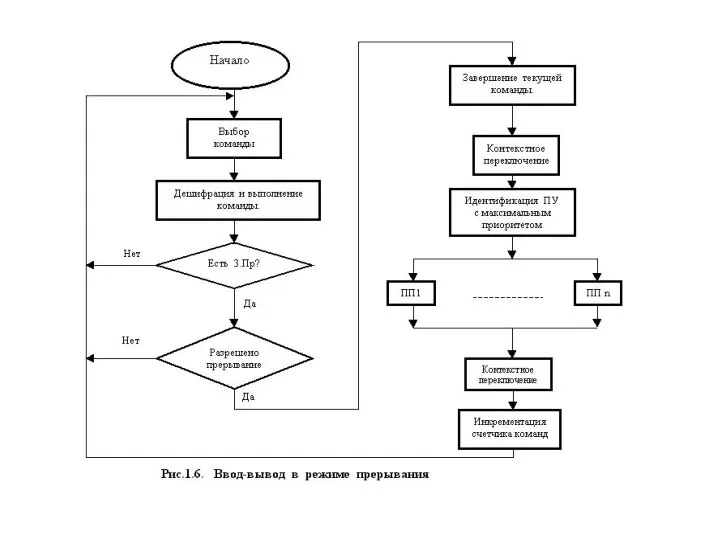

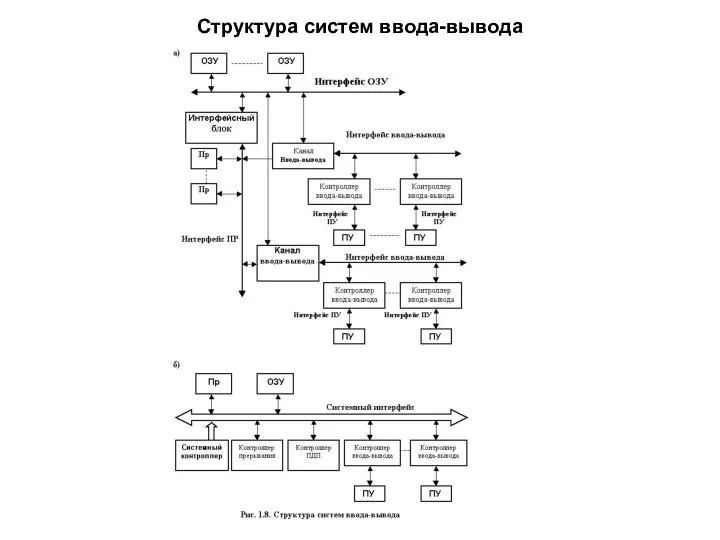

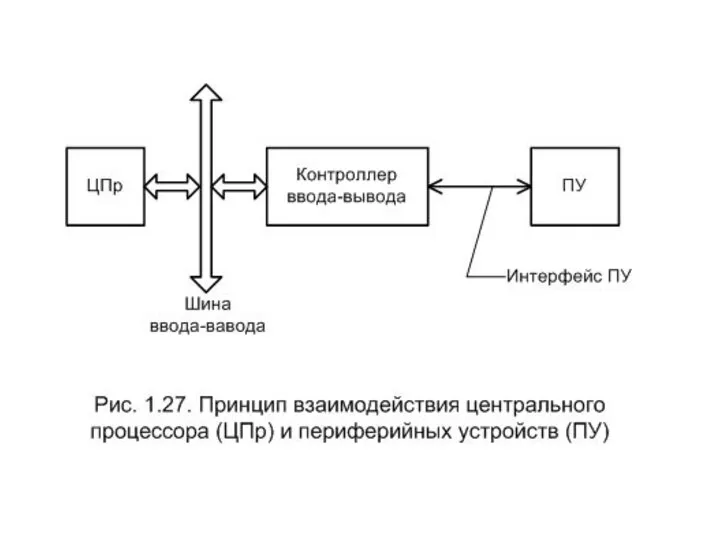

- 17. Структура систем ввода-вывода

- 22. Тема 1.2. Основные функции и принципы построения интерфейсов

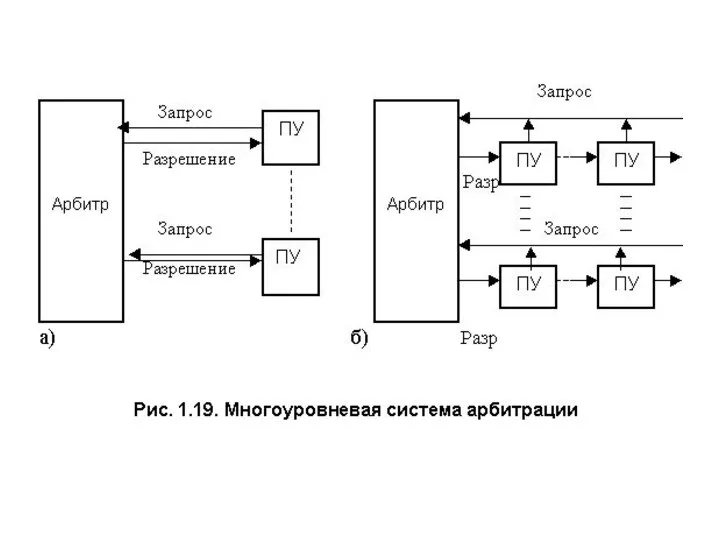

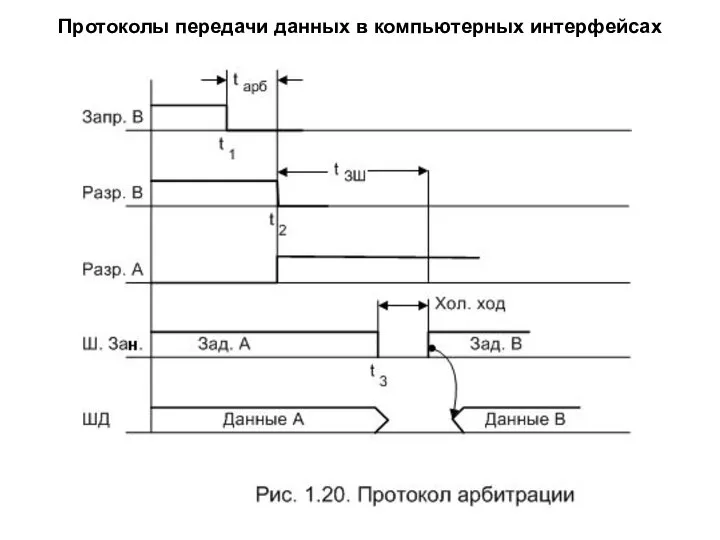

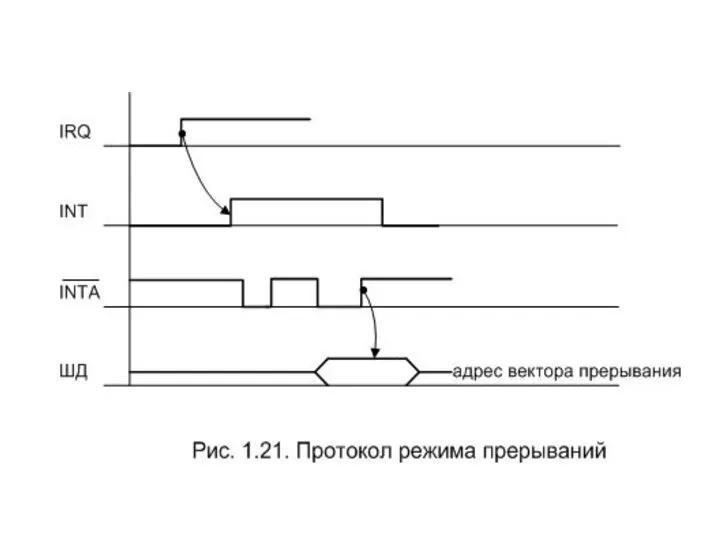

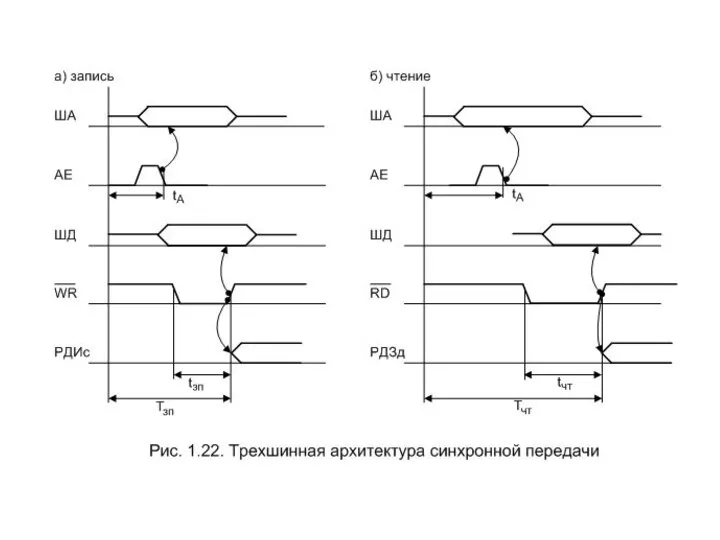

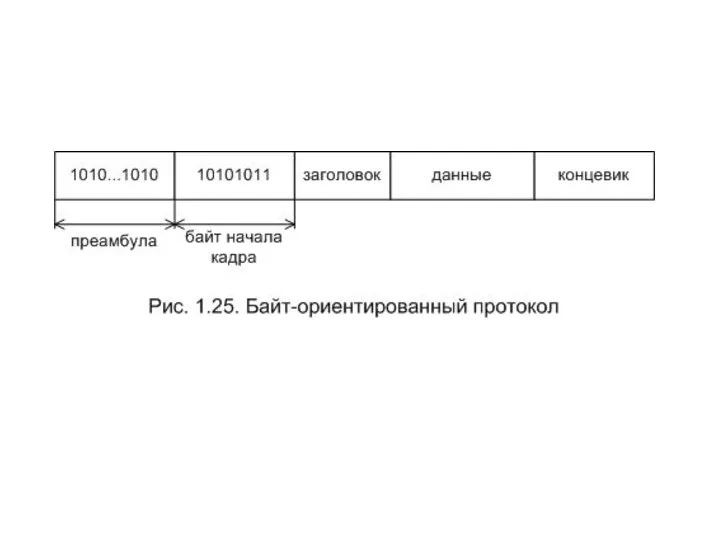

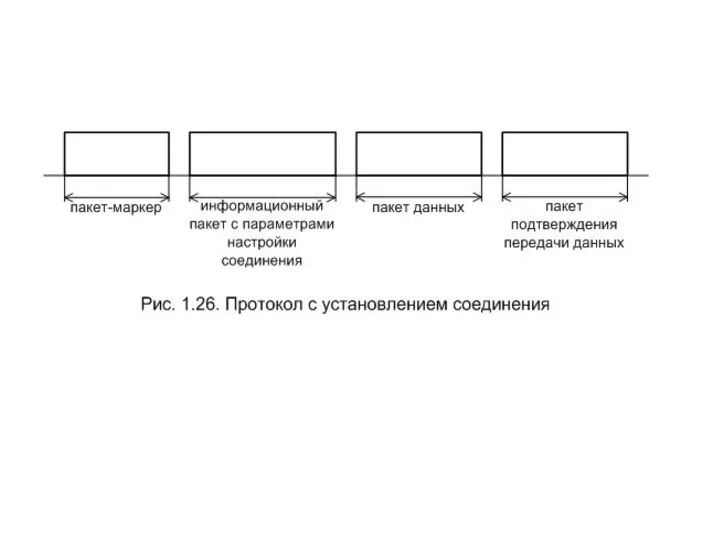

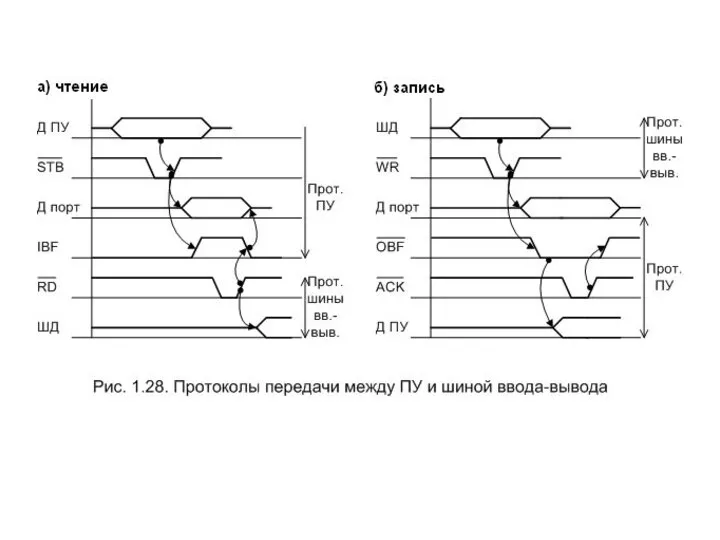

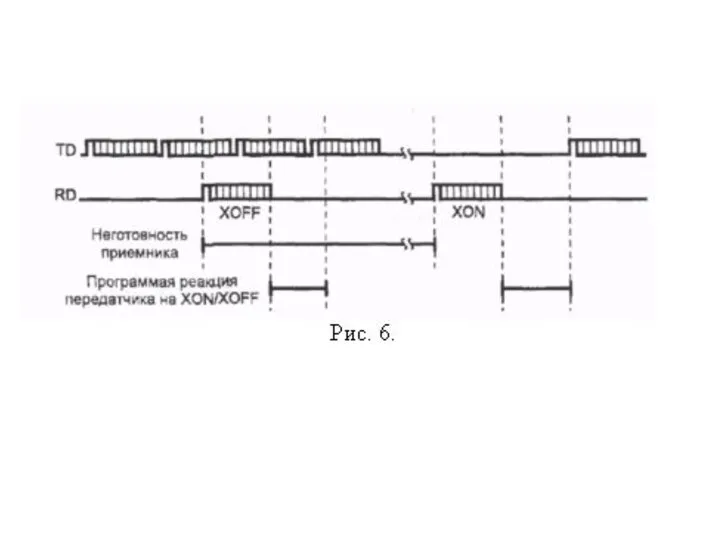

- 30. Протоколы передачи данных в компьютерных интерфейсах

- 39. Системные интерфейсы, шины расширения ТЕМА 1.3

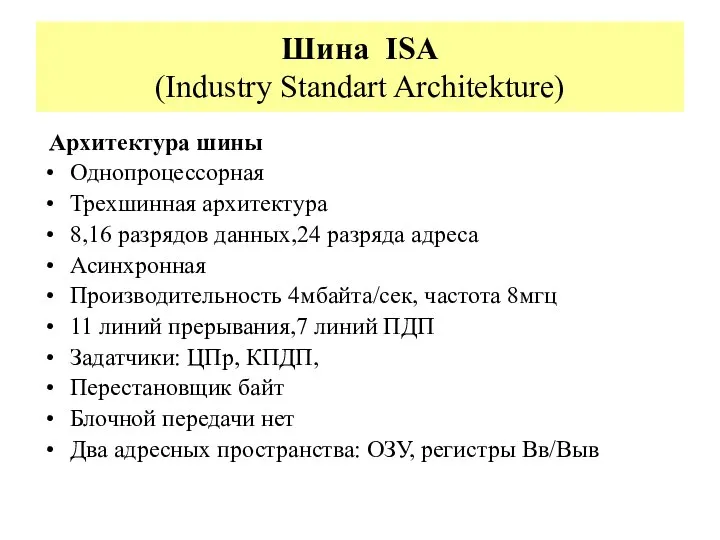

- 40. Шина ISA (Industry Standart Architekture) Архитектура шины Однопроцессорная Трехшинная архитектура 8,16 разрядов данных,24 разряда адреса Асинхронная

- 41. Типы циклов шины Ц Пр Плата расш. Контр. ПДП Контр рег. 16 р. 8 р. 16

- 42. Сигналы шины ISA Сигналы адреса и данных SA(System Adres)[19-0] - адрес с «защелкиванием» LA(Latchable Adres)[24-17] -

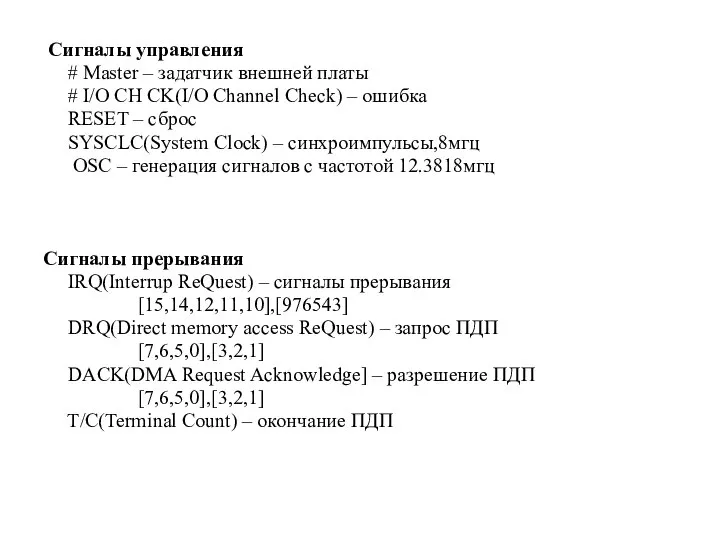

- 43. Сигналы управления # Master – задатчик внешней платы # I/O CH CK(I/O Channel Check) – ошибка

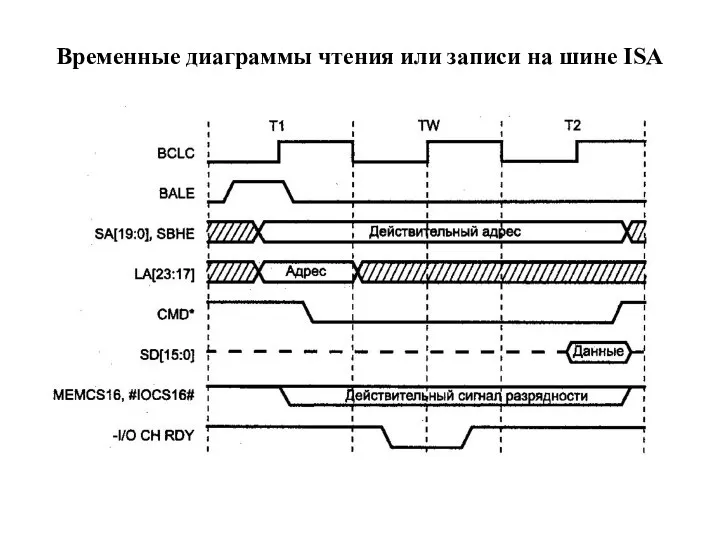

- 44. Временные диаграммы чтения или записи на шине ISA

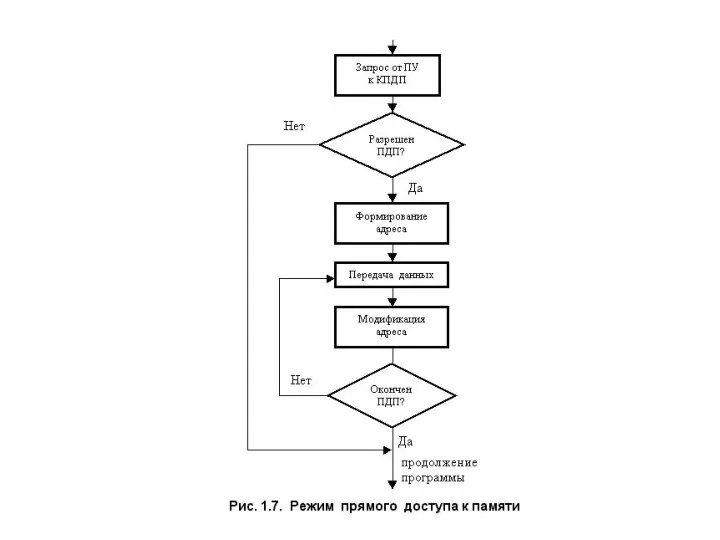

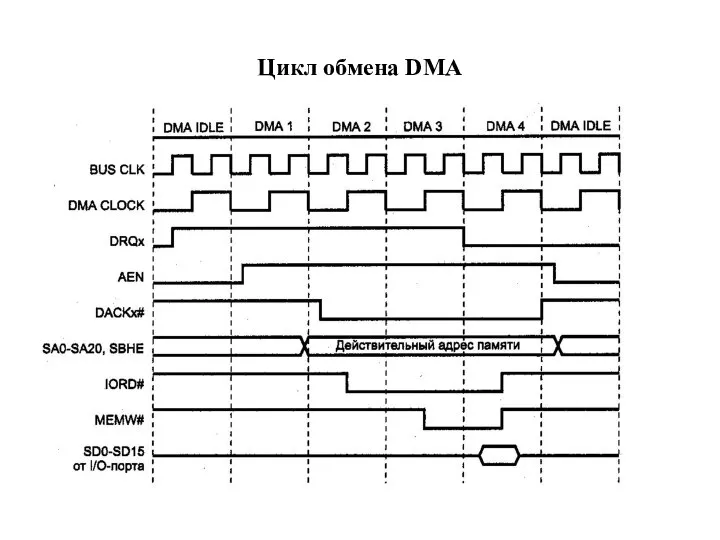

- 45. Цикл обмена DMA

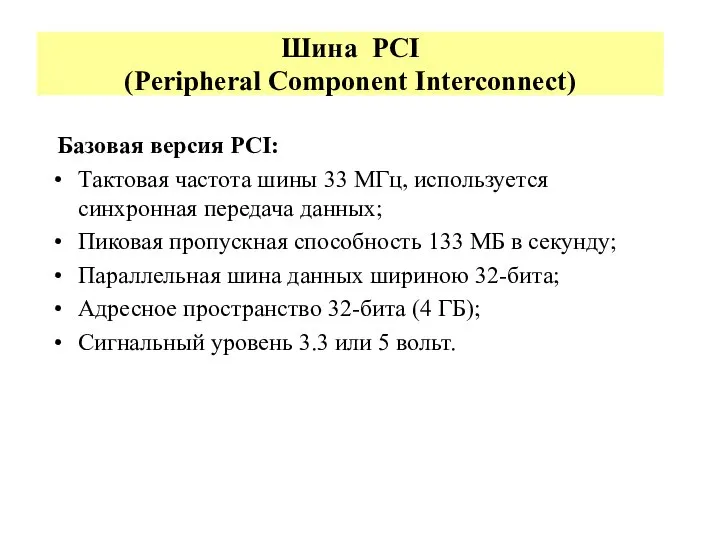

- 46. Шина PCI (Peripheral Component Interconnect) Базовая версия PCI: Тактовая частота шины 33 МГц, используется синхронная передача

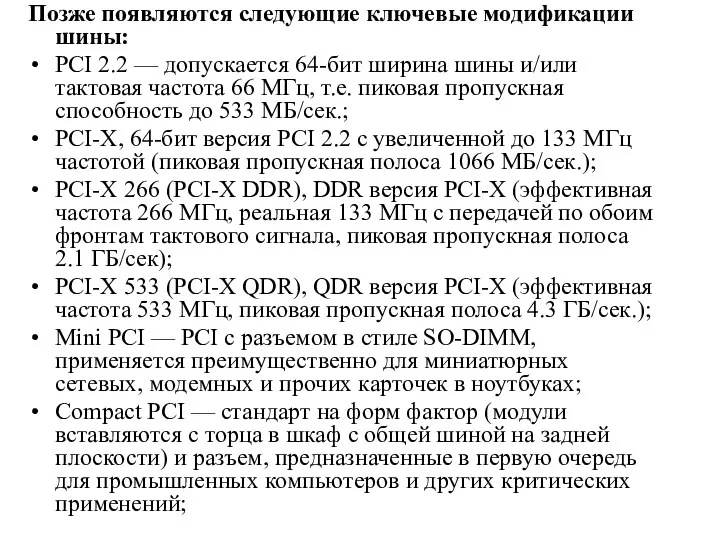

- 47. Позже появляются следующие ключевые модификации шины: PCI 2.2 — допускается 64-бит ширина шины и/или тактовая частота

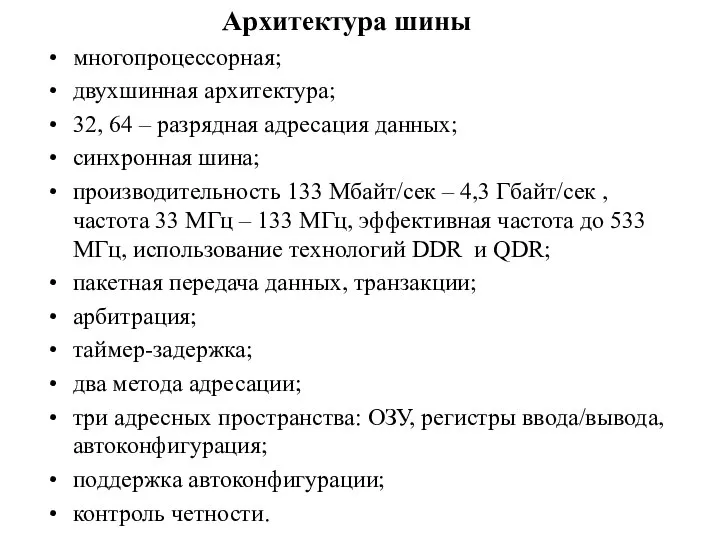

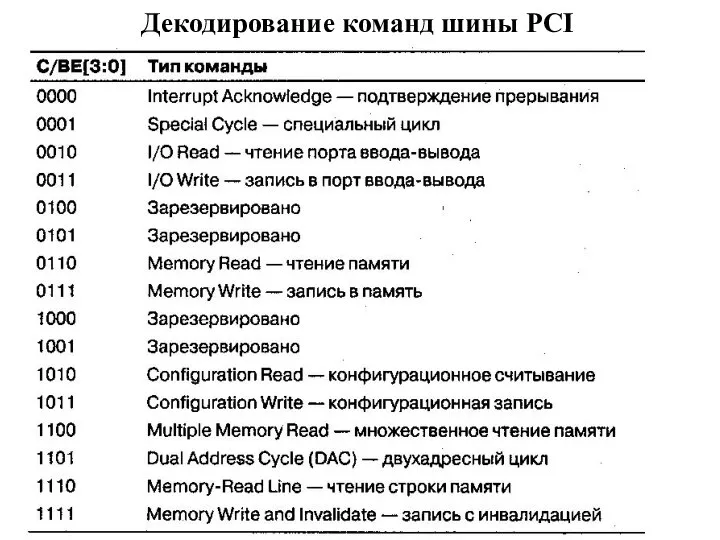

- 48. многопроцессорная; двухшинная архитектура; 32, 64 – разрядная адресация данных; синхронная шина; производительность 133 Мбайт/сек – 4,3

- 49. Пр Пр ОЗУ Контр. ОЗУ Авто конф. Арб. Исп. Зад. Мост П У PCI, ISA IDSEL

- 50. Базовые сигналы шины PCI AD[31-0] – адрес – данные; C/BE[3-0] – код команды, указатель байт; #FRAME

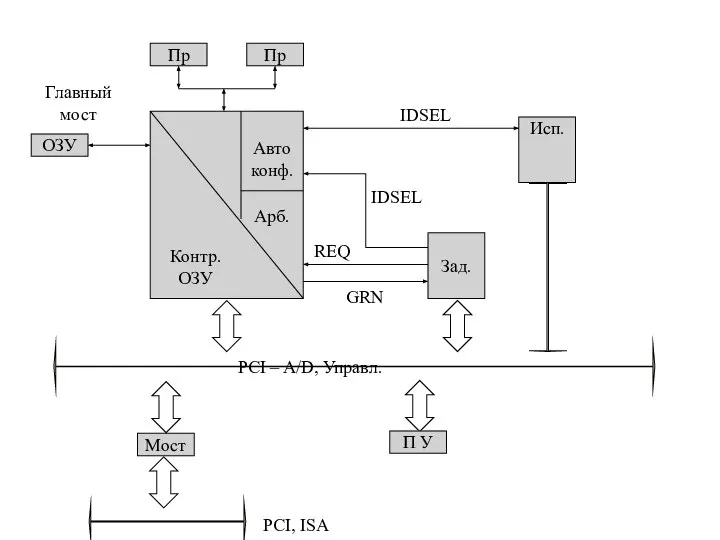

- 51. Декодирование команд шины PCI

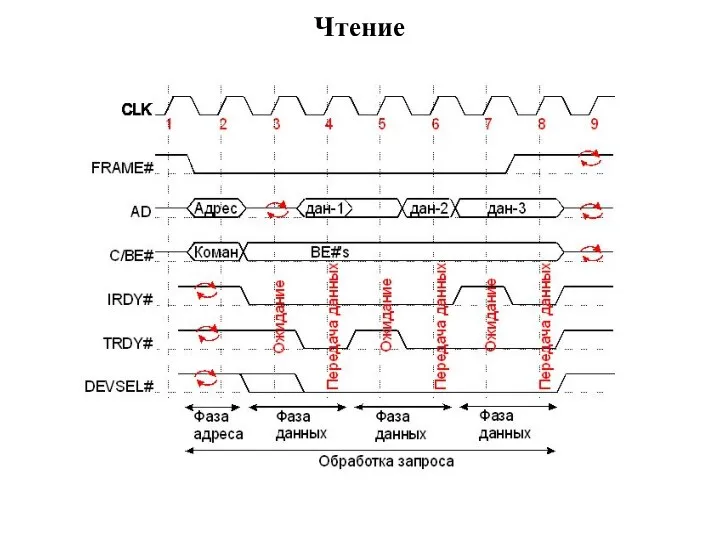

- 52. Чтение

- 53. Запись

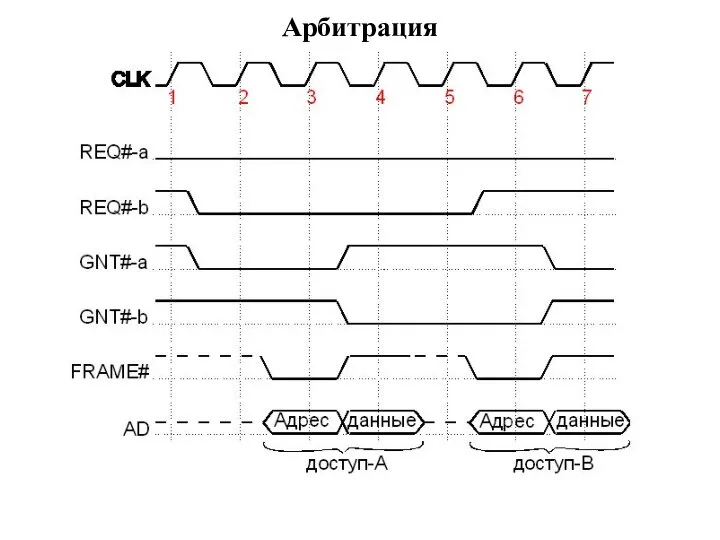

- 54. Арбитрация

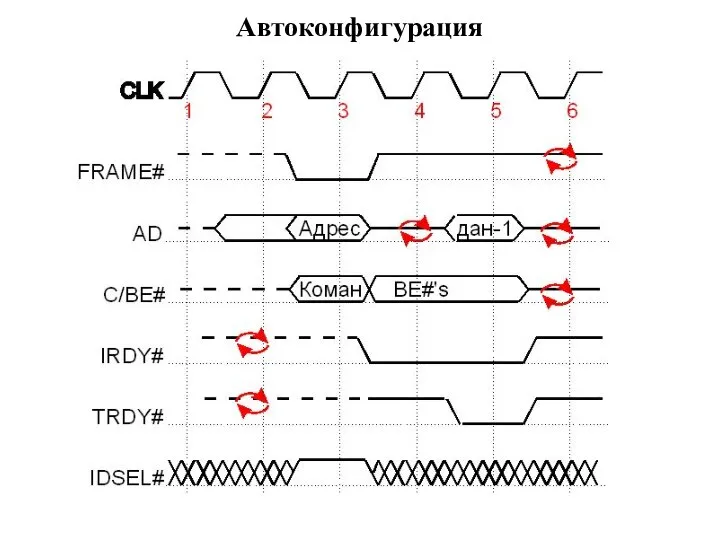

- 55. Автоконфигурация

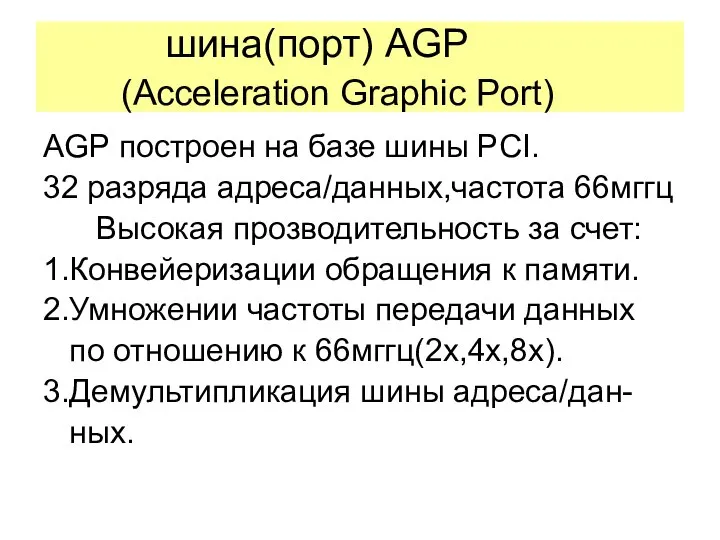

- 56. шина(порт) AGP (Acceleration Graphic Port) AGP построен на базе шины PCI. 32 разряда адреса/данных,частота 66мггц Высокая

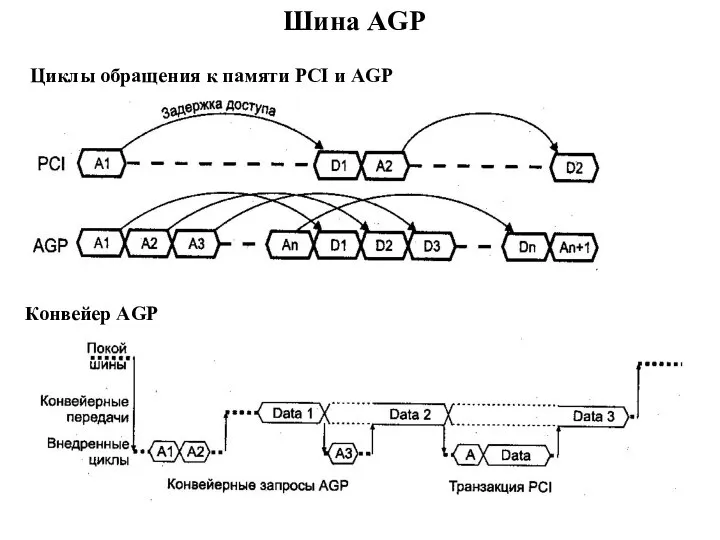

- 57. Шина AGP Циклы обращения к памяти PCI и AGP Конвейер AGP

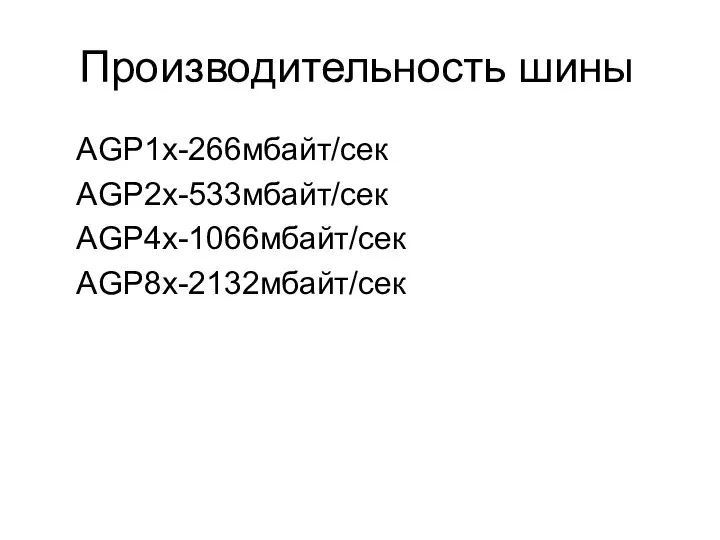

- 58. Производительность шины AGP1х-266мбайт/сек AGP2х-533мбайт/сек AGP4x-1066мбайт/сек AGP8x-2132мбайт/сек

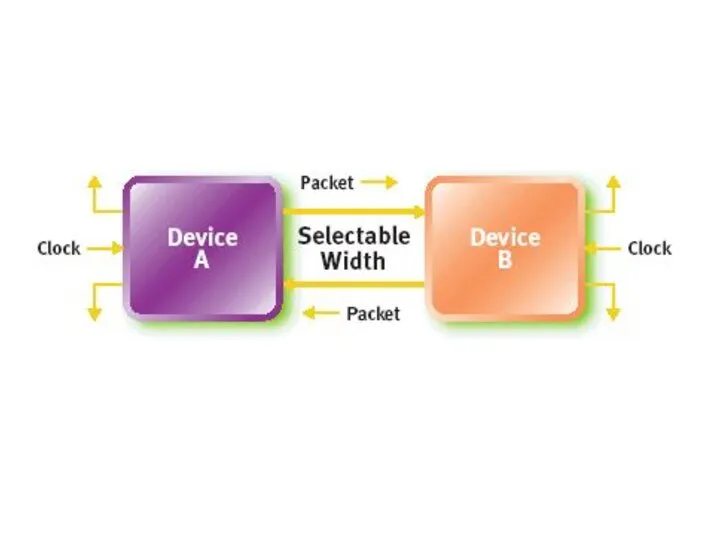

- 59. Шина PCI Express Последовательная системная шина общего назначения; Имя — PCI Express, на стадии проектирования была

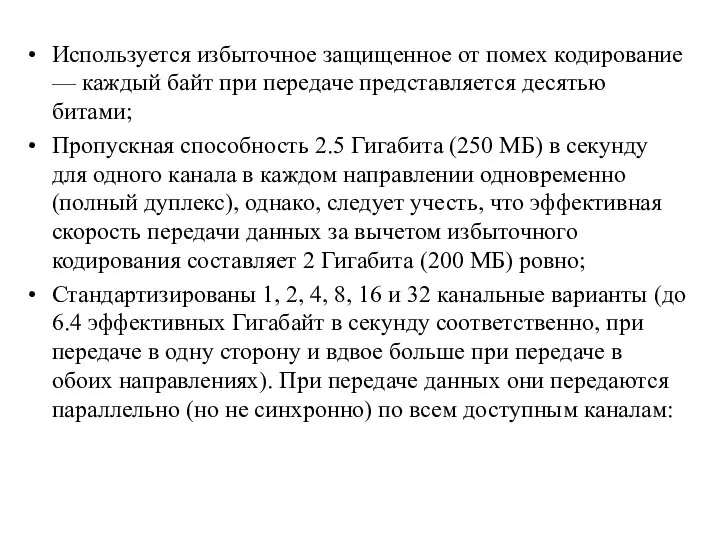

- 61. Используется избыточное защищенное от помех кодирование — каждый байт при передаче представляется десятью битами; Пропускная способность

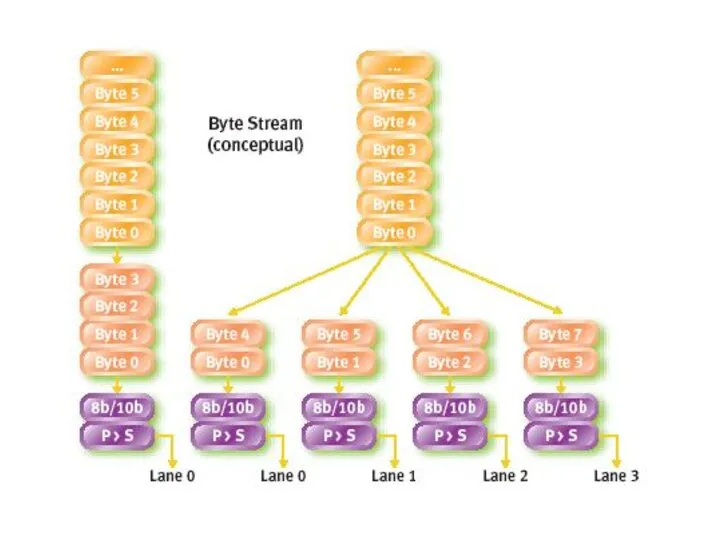

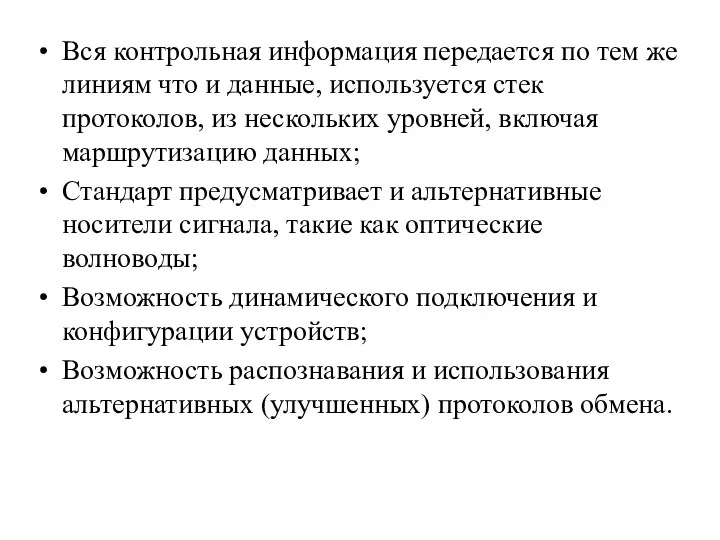

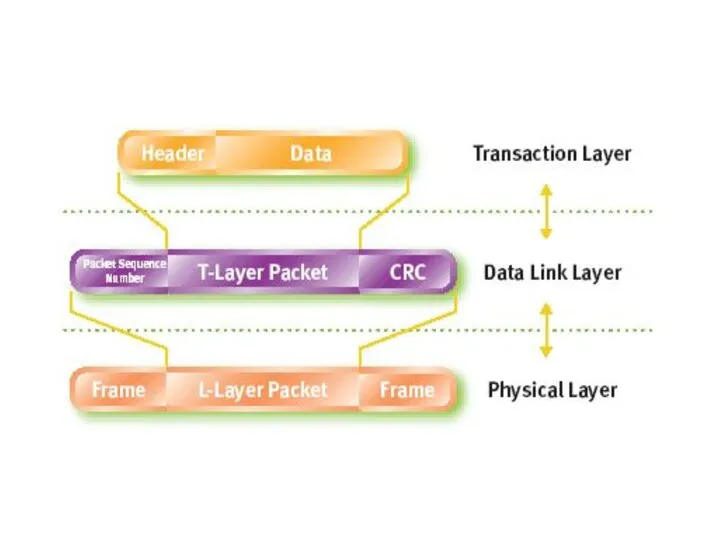

- 63. Вся контрольная информация передается по тем же линиям что и данные, используется стек протоколов, из нескольких

- 64. Деление на уровни

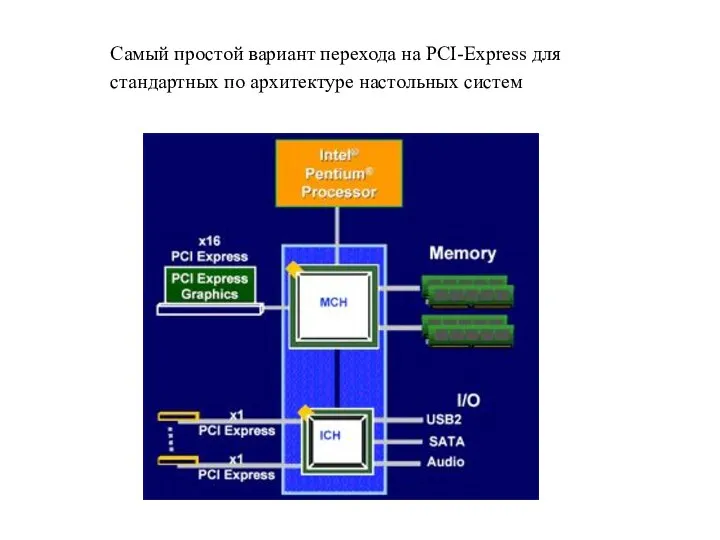

- 66. Самый простой вариант перехода на PCI-Express для стандартных по архитектуре настольных систем

- 67. Однако в будущем логично ожидать появление некоего разветвителя PCI Express. Тогда вполне оправданным станет и объединение

- 68. Более обобщенная (серверная) архитектура с одним мостом:

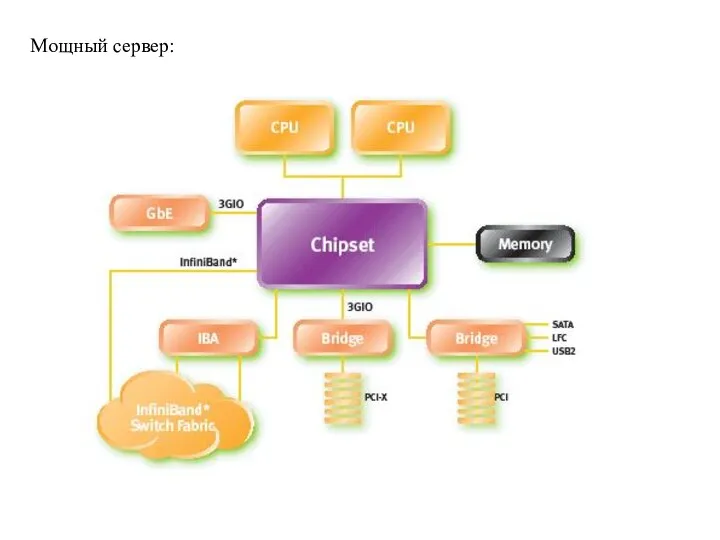

- 69. Мощный сервер:

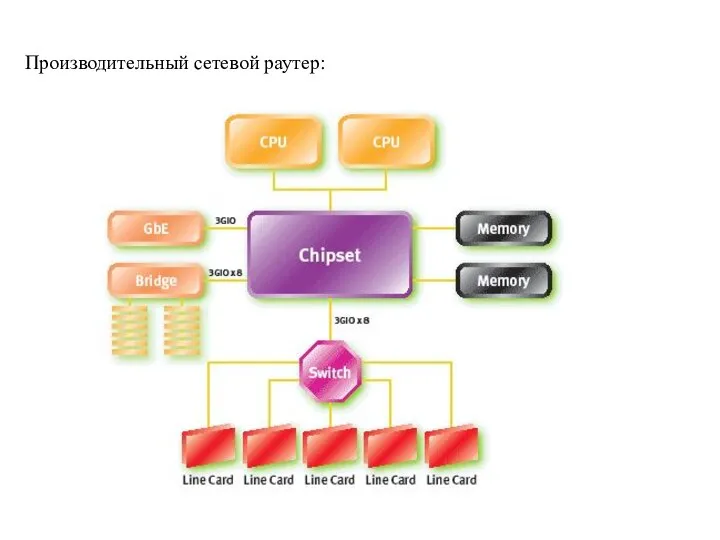

- 70. Производительный сетевой раутер:

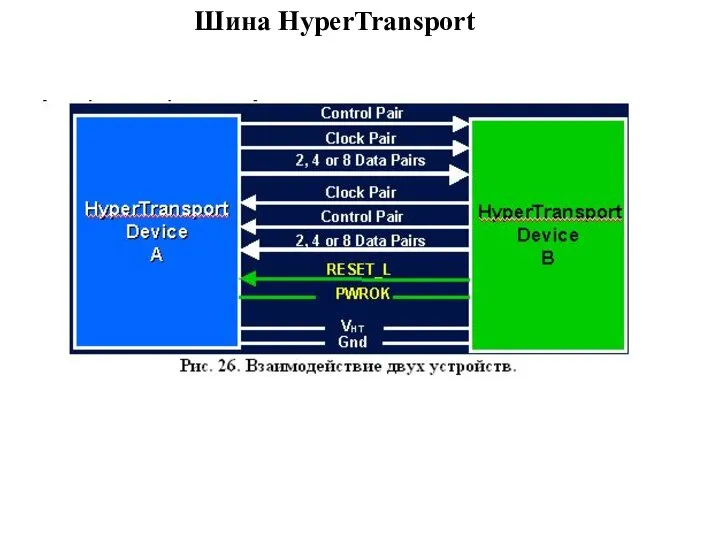

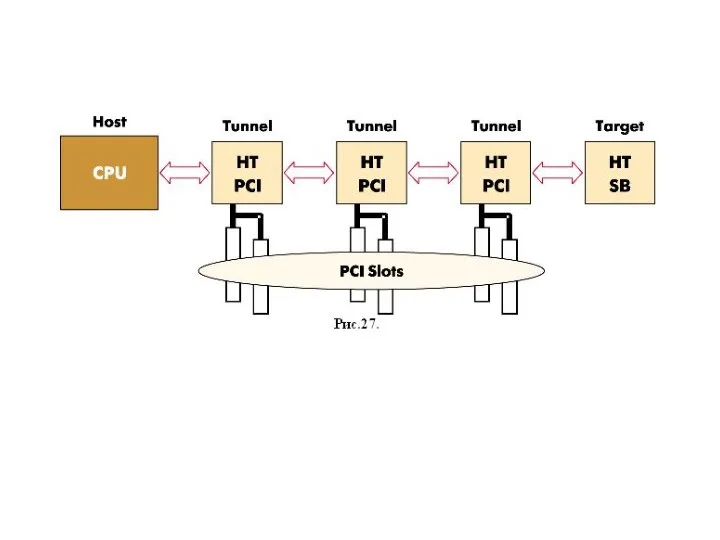

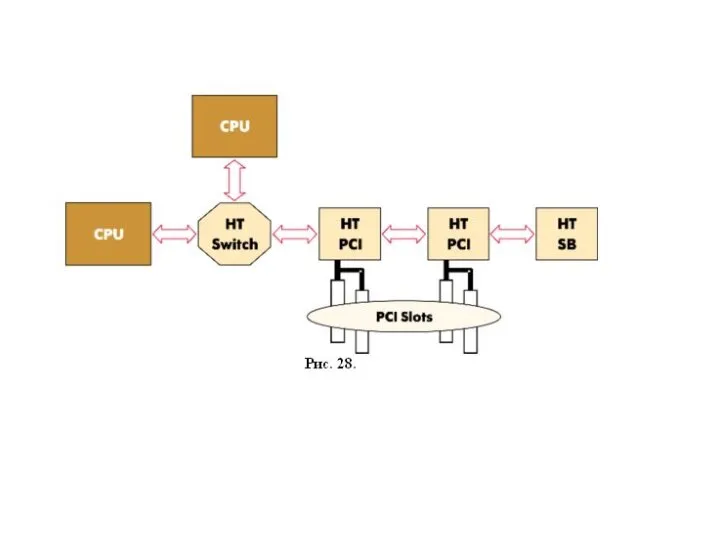

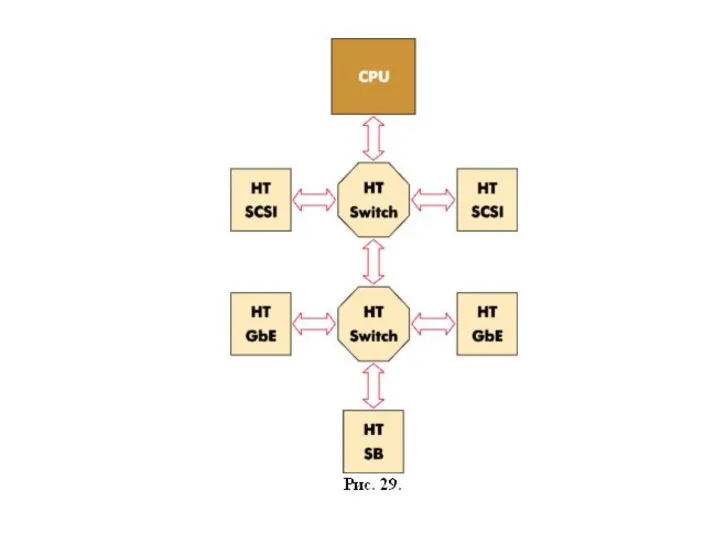

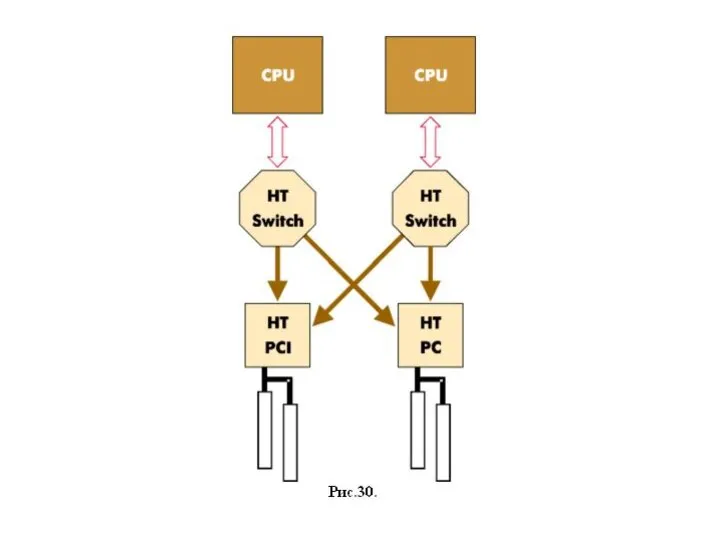

- 71. Шина HyperTransport

- 76. Тема 1.4. Интерфейсы периферийных устройств (Centronics, RS232, SCSI, USB)

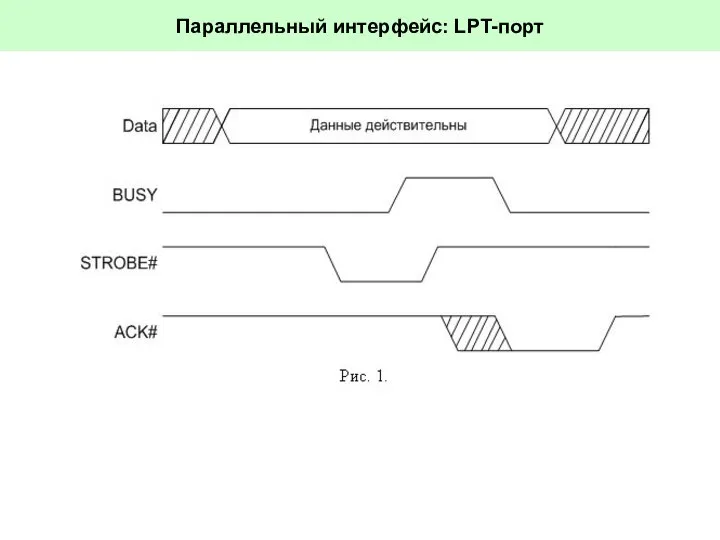

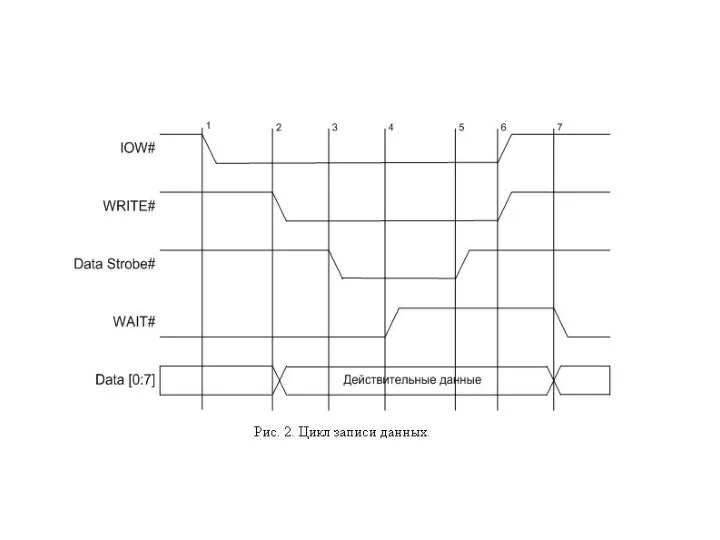

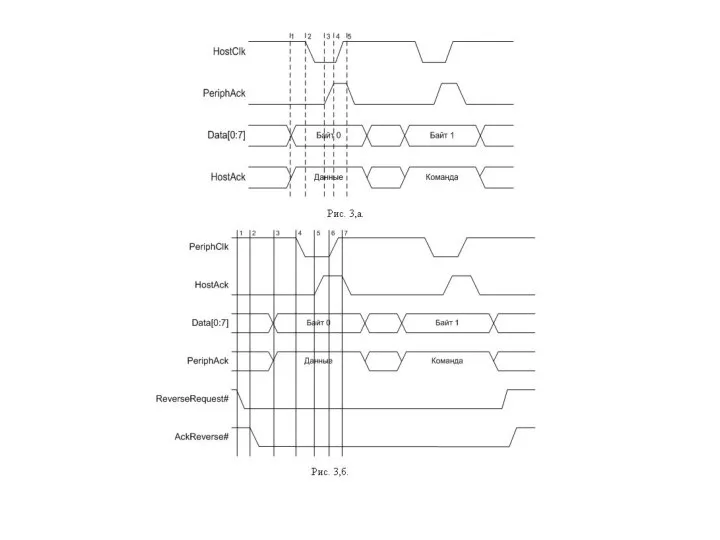

- 77. Параллельный интерфейс: LPT-порт

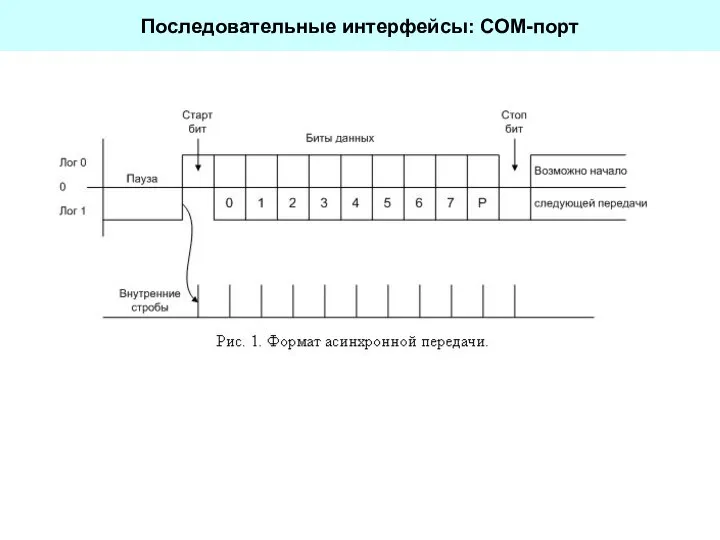

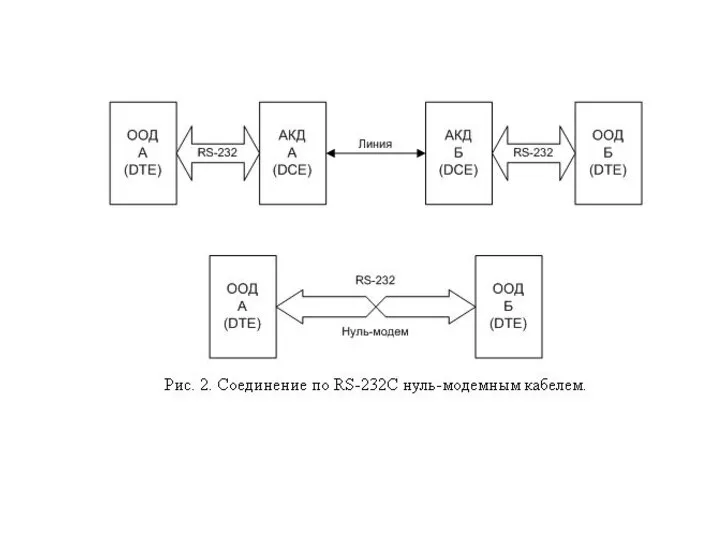

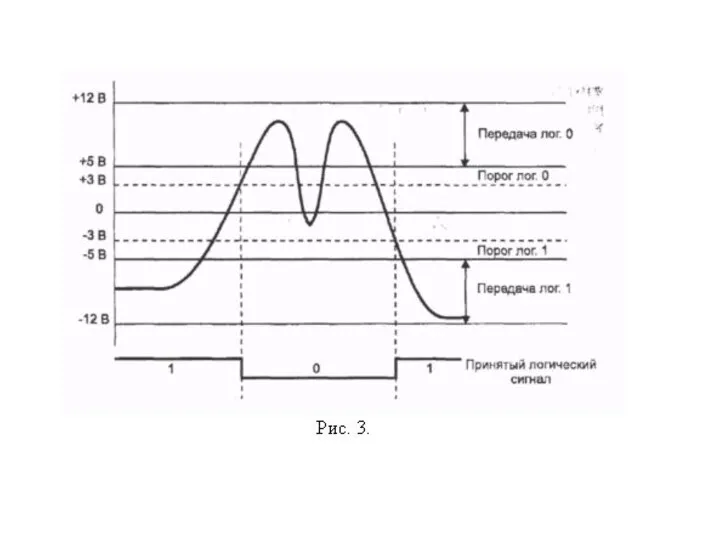

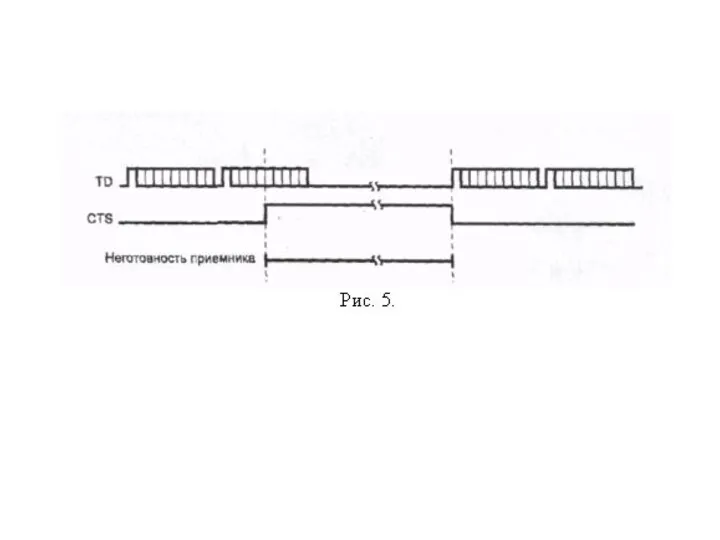

- 80. Последовательные интерфейсы: СОМ-порт

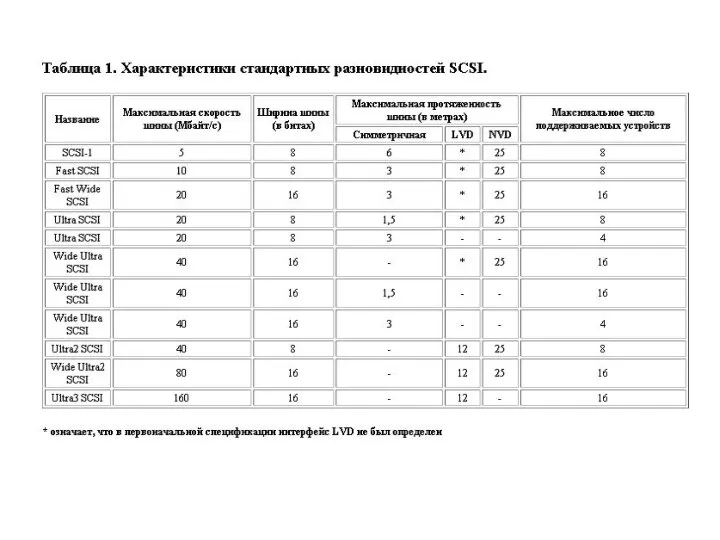

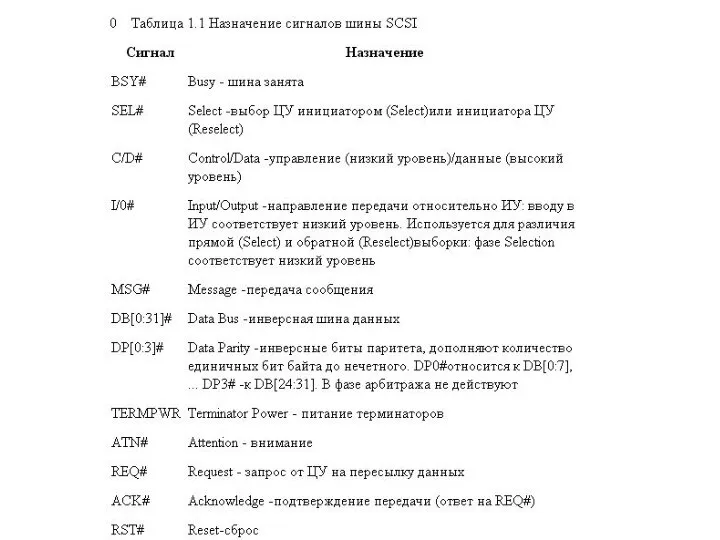

- 86. шина SCSI (Small Computer System Interface)

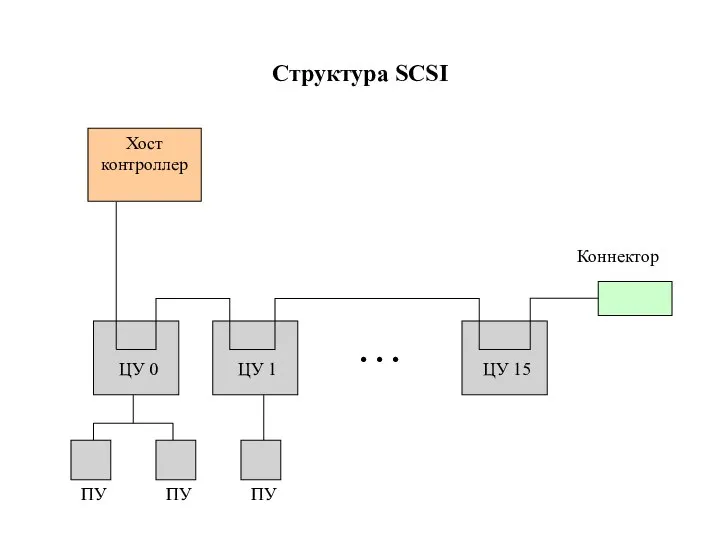

- 87. Структура SCSI Хост контроллер ЦУ 0 ЦУ 1 ЦУ 15 ПУ ПУ ПУ Коннектор …

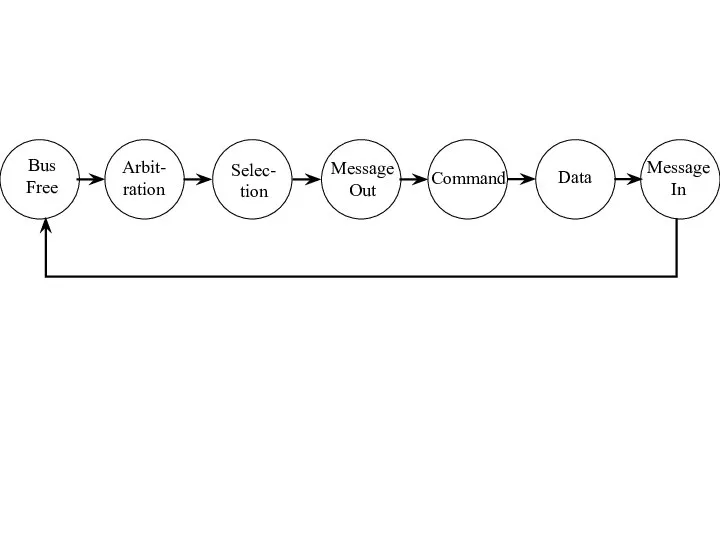

- 91. Bus Free Arbit-ration Selec-tion Message Out Command Data Message In

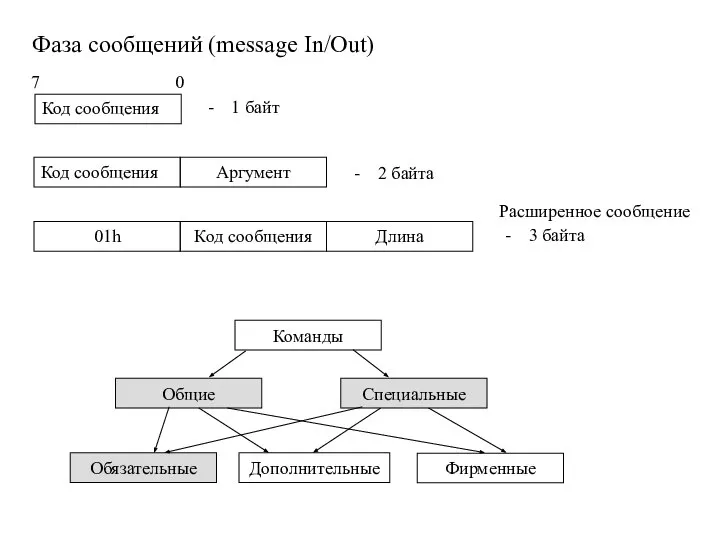

- 92. Фаза сообщений (message In/Out) Код сообщения - 1 байт 7 0 Код сообщения Аргумент - 2

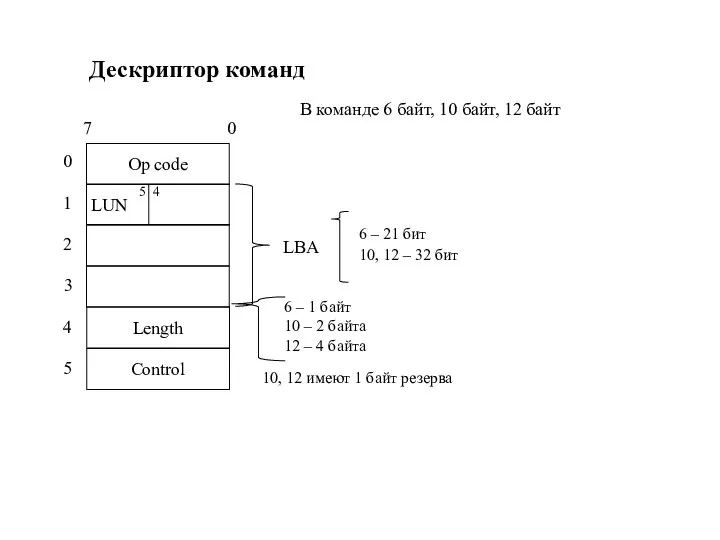

- 93. Дескриптор команд Op code 7 0 LUN Length Control 5 4 0 1 2 3 4

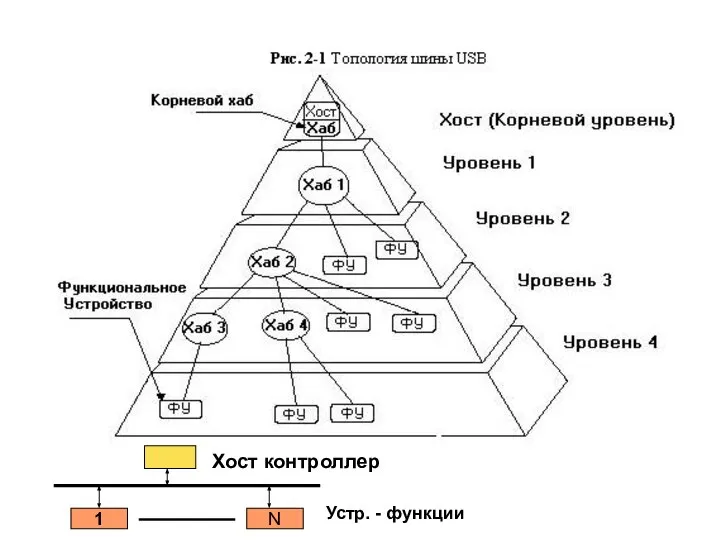

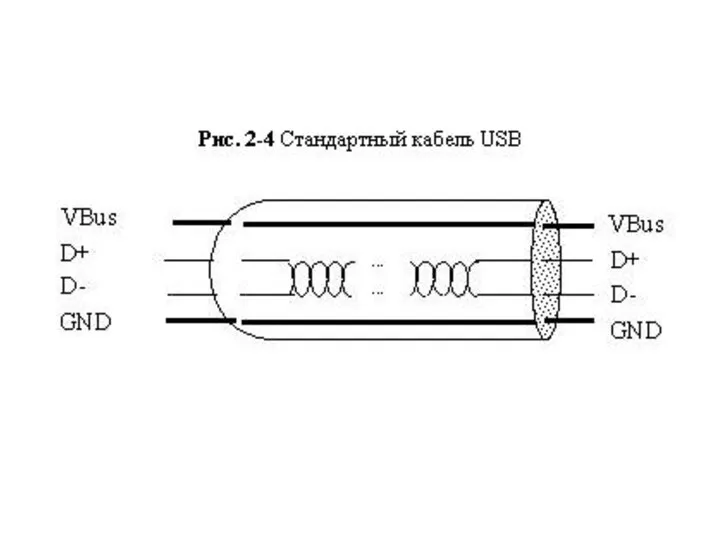

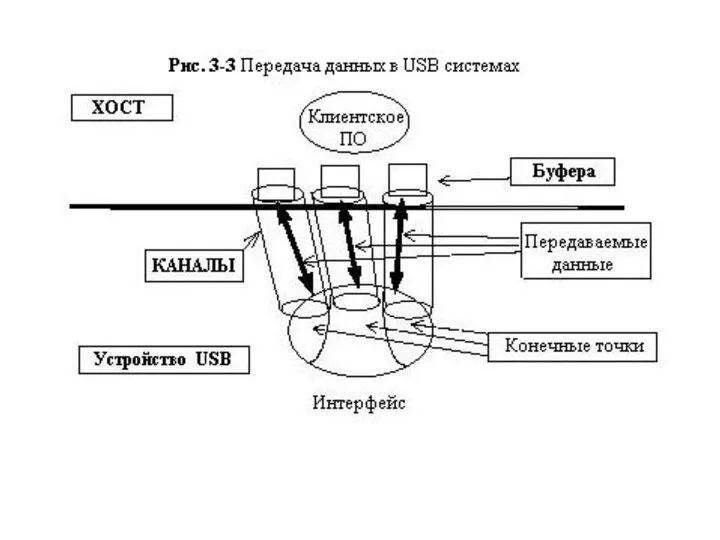

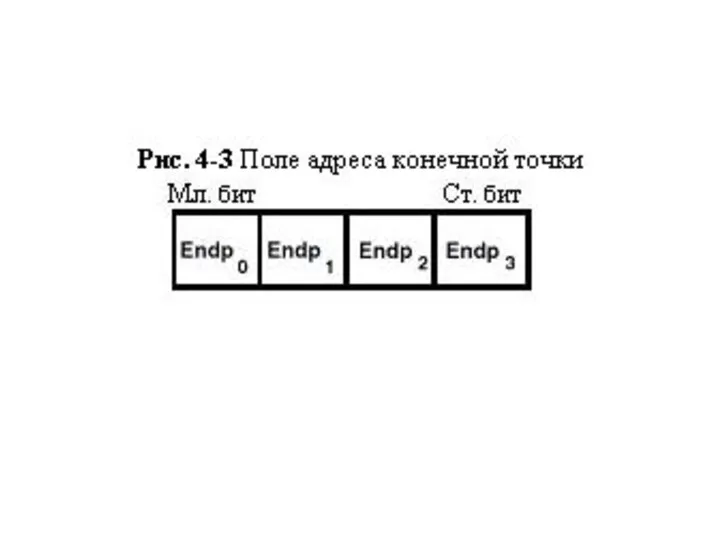

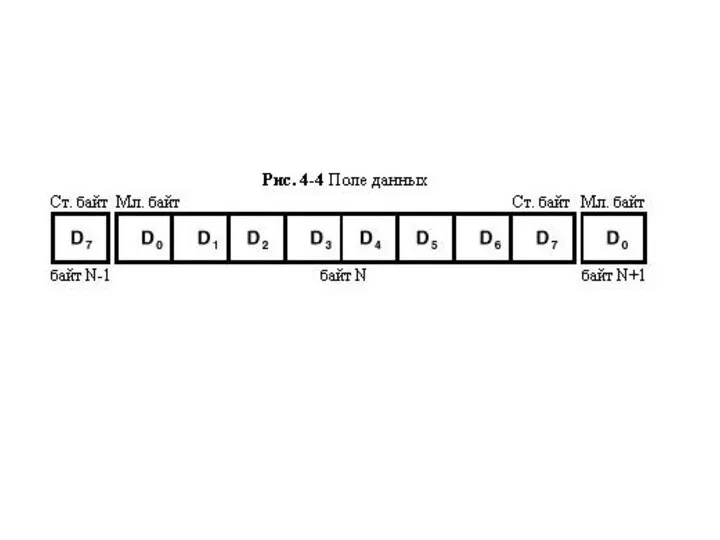

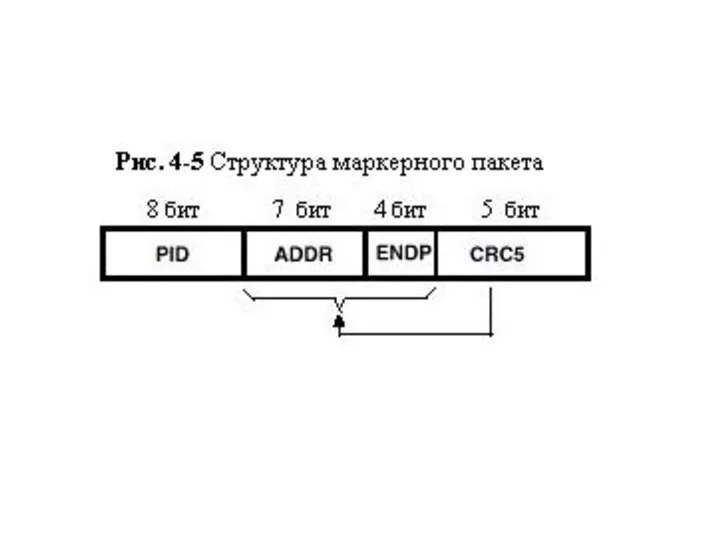

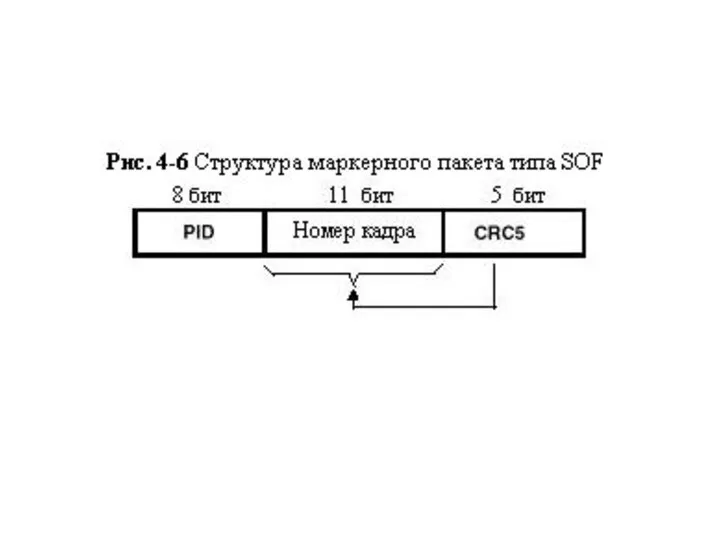

- 94. Шина USB (Universal Systems Interface)

- 95. 1 N Хост контроллер Устр. - функции

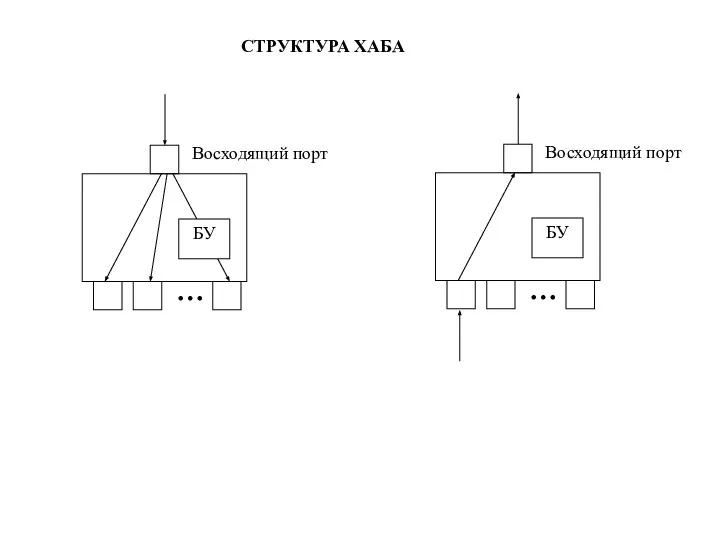

- 96. СТРУКТУРА ХАБА БУ Восходящий порт … БУ Восходящий порт …

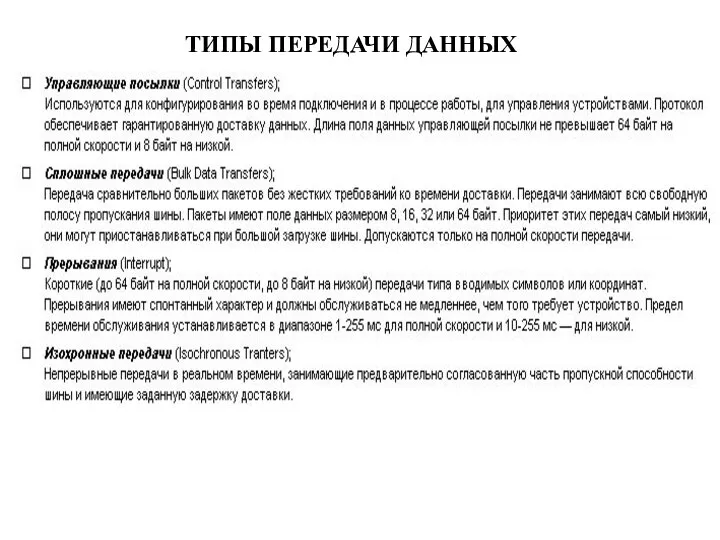

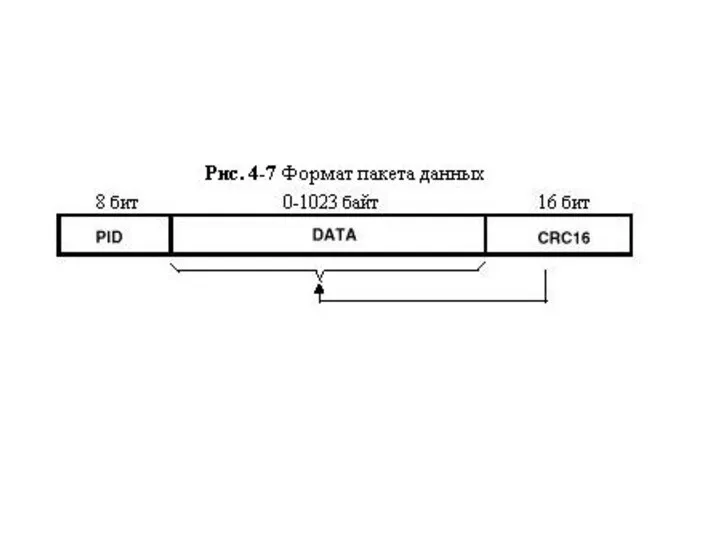

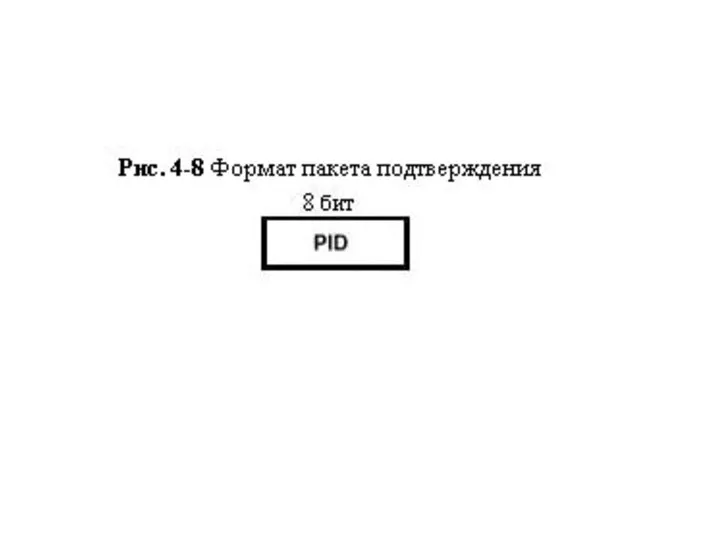

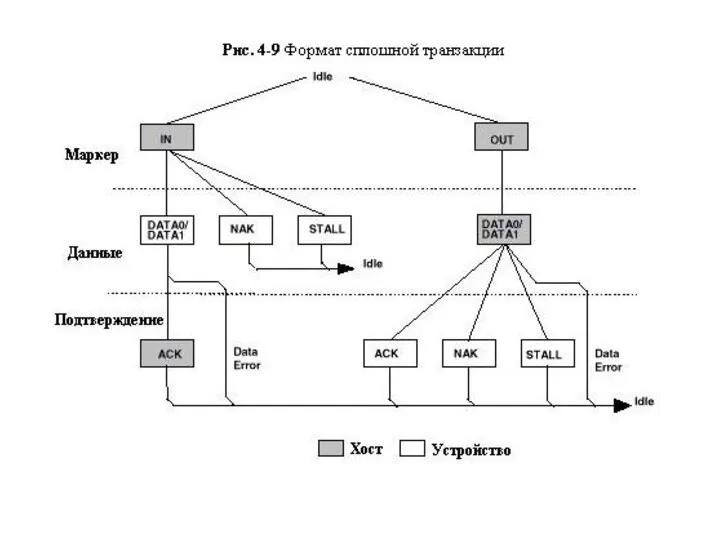

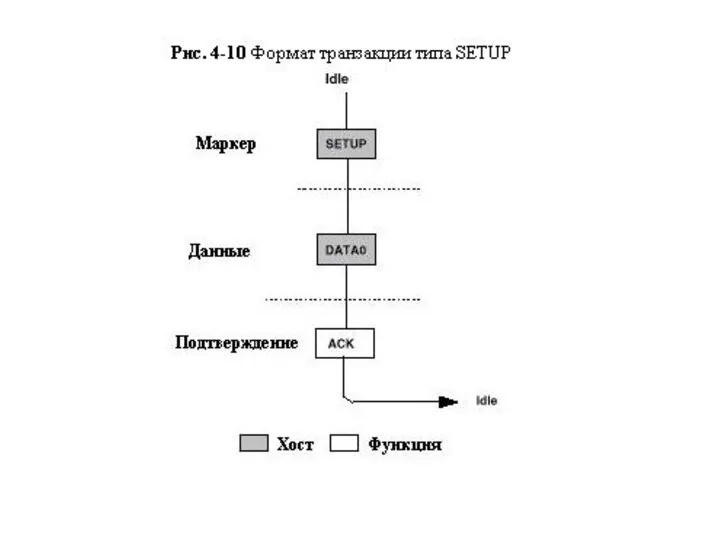

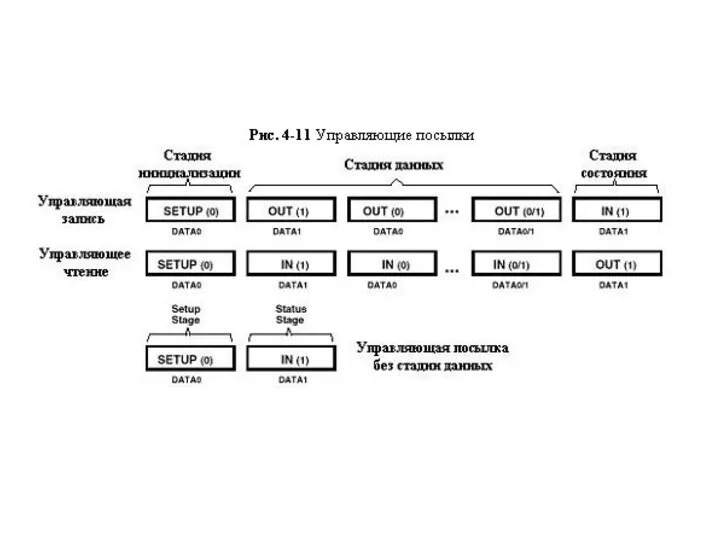

- 101. ТИПЫ ПЕРЕДАЧИ ДАННЫХ

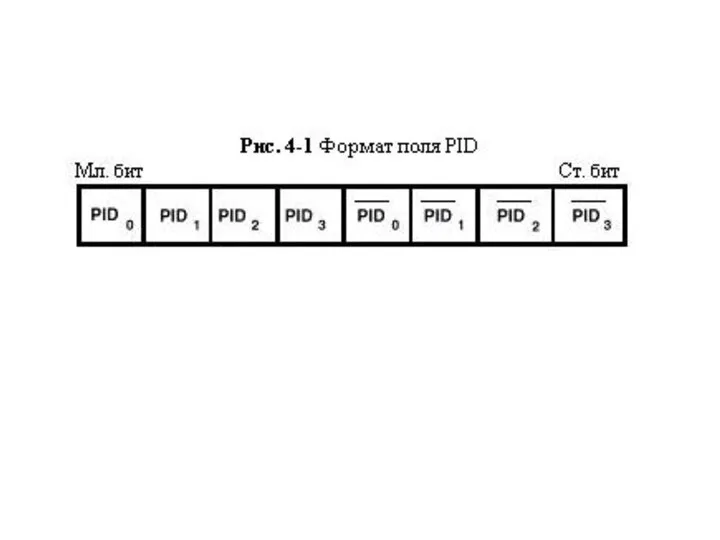

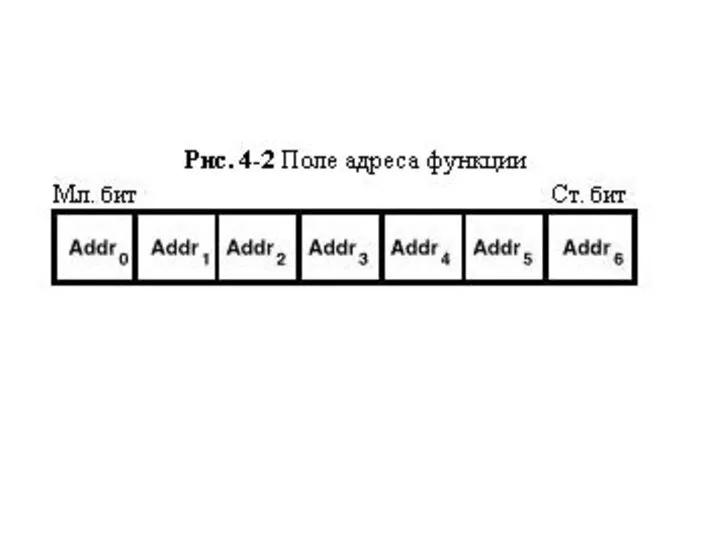

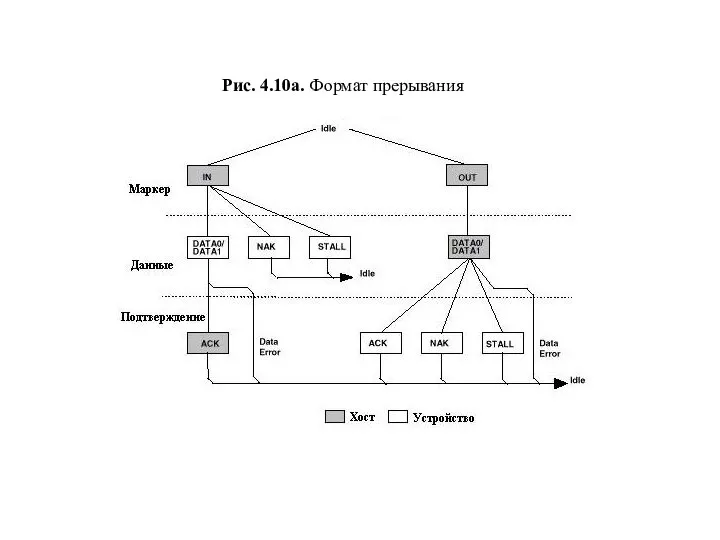

- 112. Рис. 4.10а. Формат прерывания

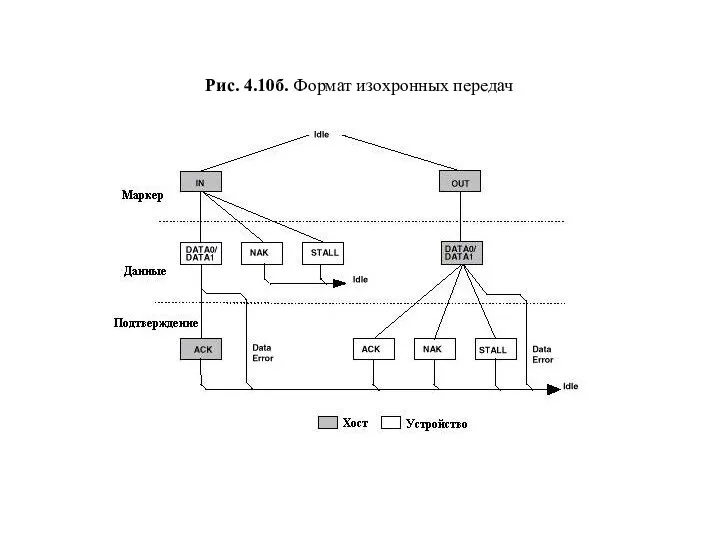

- 113. Рис. 4.10б. Формат изохронных передач

- 115. Тема 1.5. Аппаратные средства интерфейсов и систем ввода-вывода

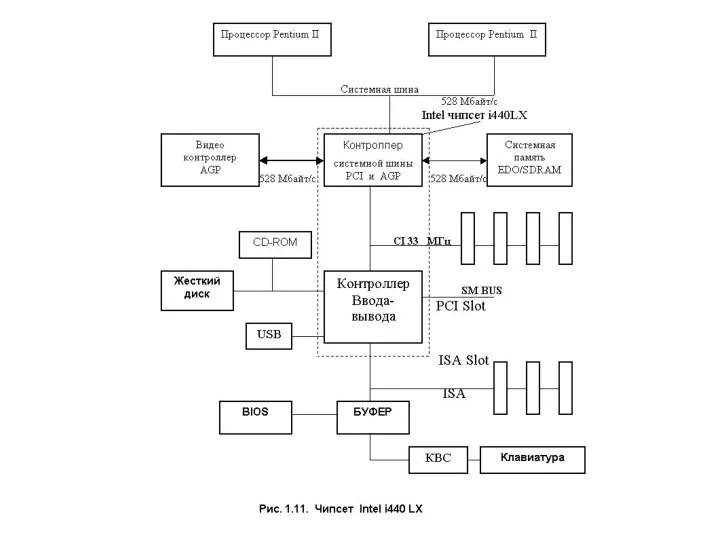

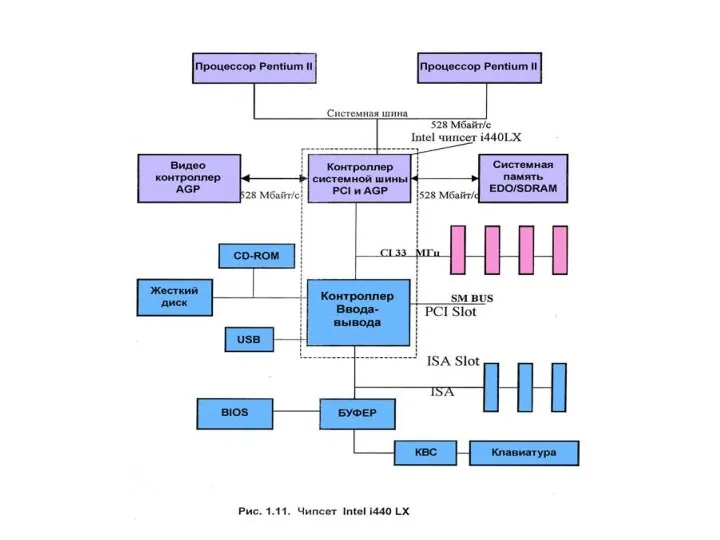

- 116. Чипсет(Chipset) Чипсет-набор микросхем,являющихся интер- Фейсом между составными частями компьюте- ра: ЦПр,ОЗУ,ПЗУ,порты ввода-вывода. Обычно это две микросхемы:

- 118. Свойства чипсет Intel 440BX: - возможность подключения двух проце- сcоров Pentium ll; - поддержка памяти EDORAM

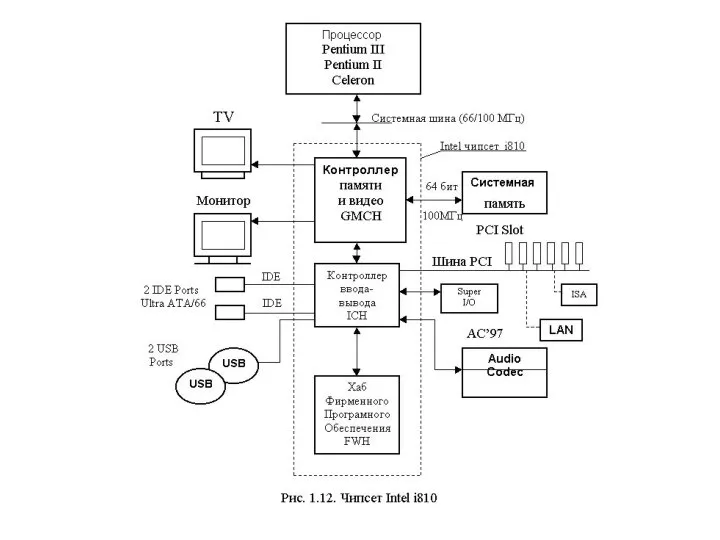

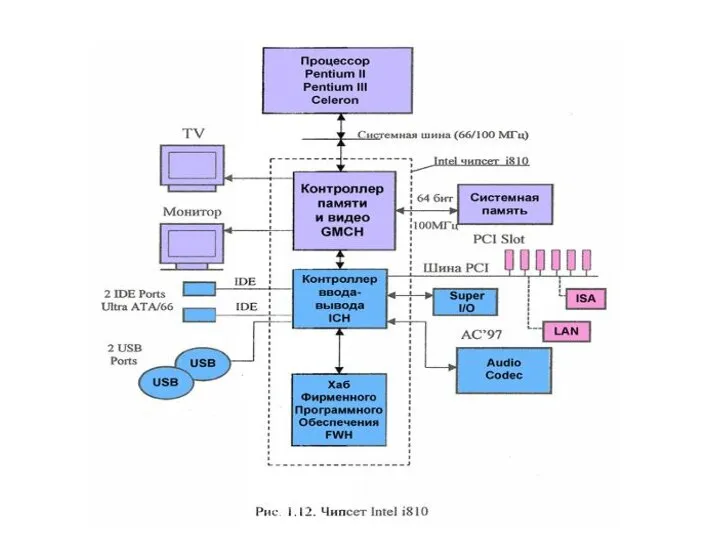

- 120. Характеристики чипсет i810: - поддержка однопрцессорной конфигу- рации; - системная шина 66 и 100МГц,64 разр.; -

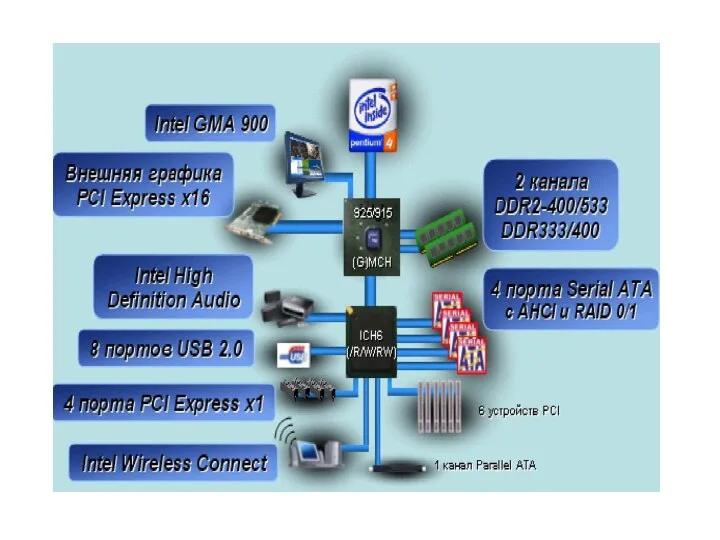

- 122. Характеристики чипсет-северный мост i925 - поддержка процессоров с частотой шины 533/800МГц; - двухканальный контроллер памяти DDR333/400

- 123. Характеристики чипсет южный мост ICH6 - 4порта PCI Express x1; - Matrix Storage-поддержка устройств Serial ATA

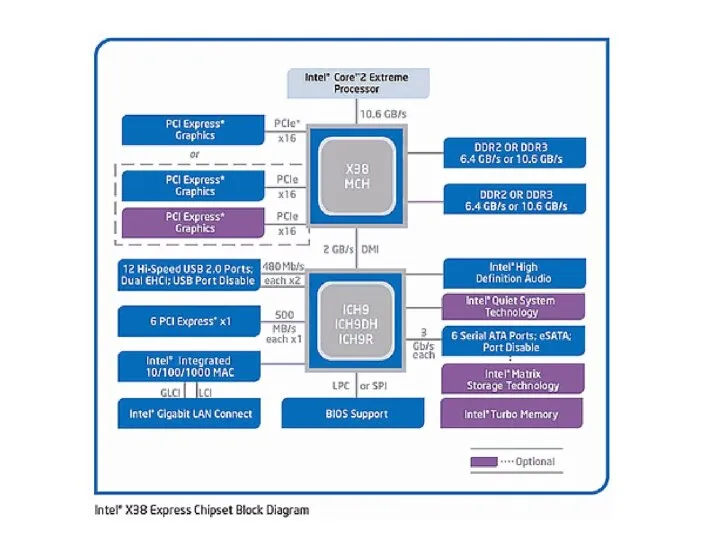

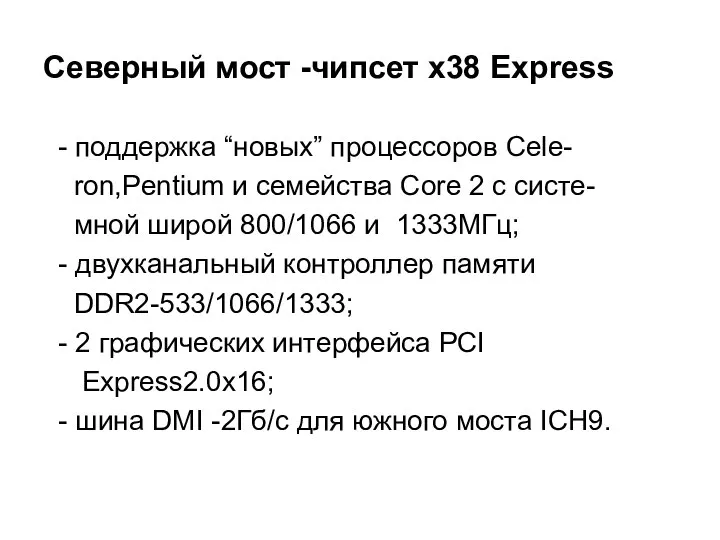

- 125. Северный мост -чипсет х38 Express - поддержка “новых” процессоров Cele- ron,Pentium и семейства Core 2 c

- 126. Чипсет Intel ICH9-южный мост - 6 портов PCI Express; - 4слота PCI; - 4 порта Serial

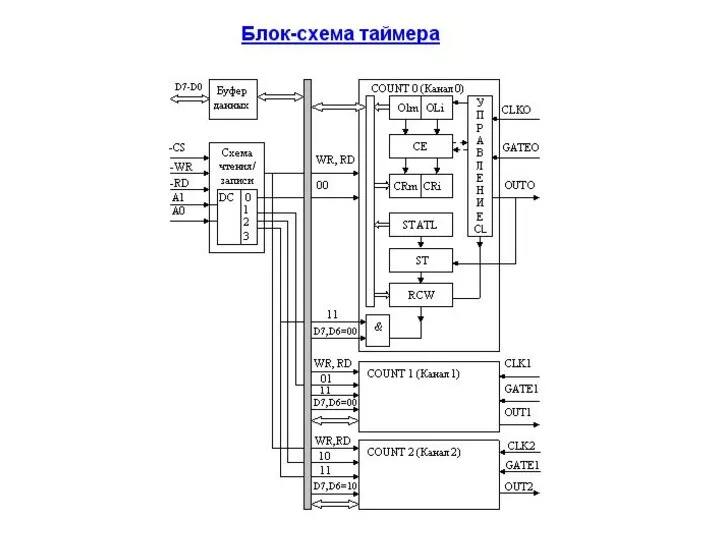

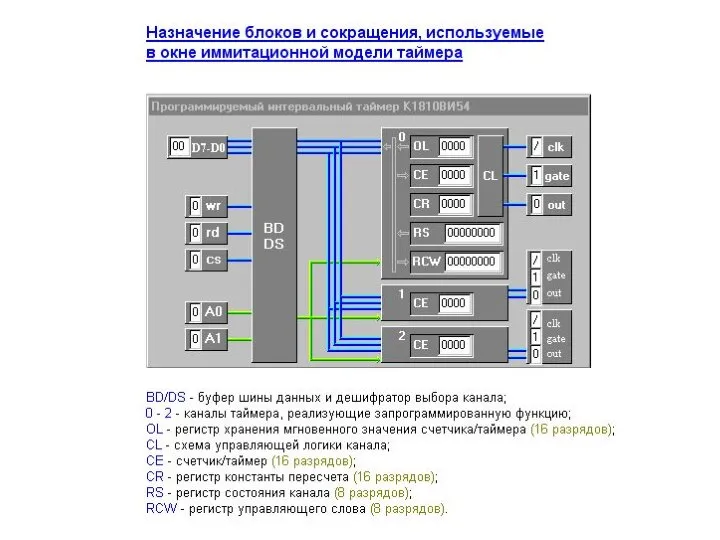

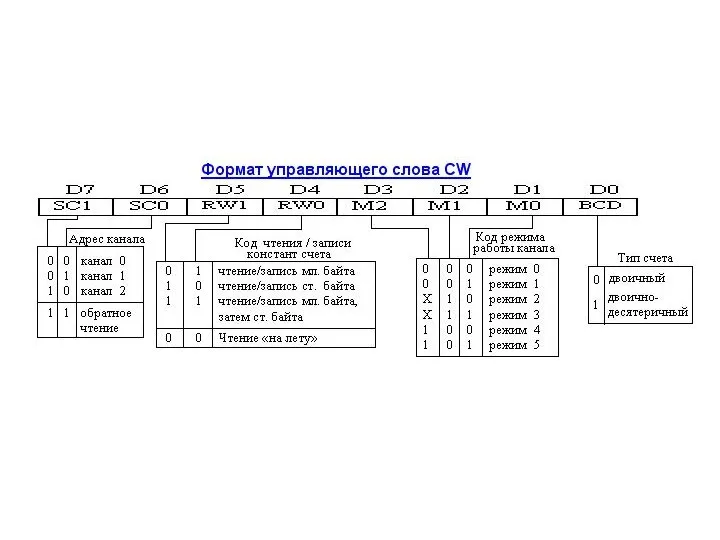

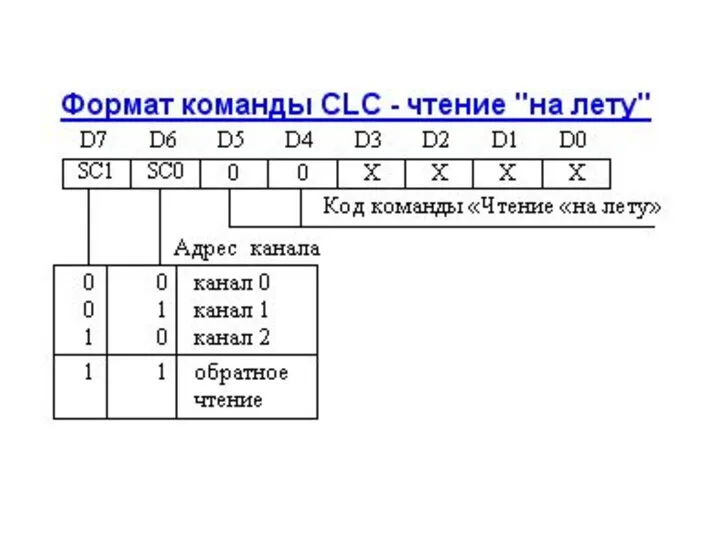

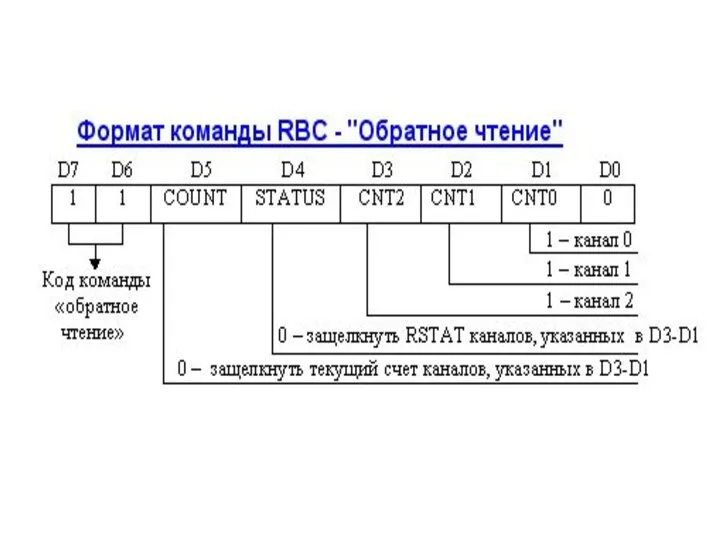

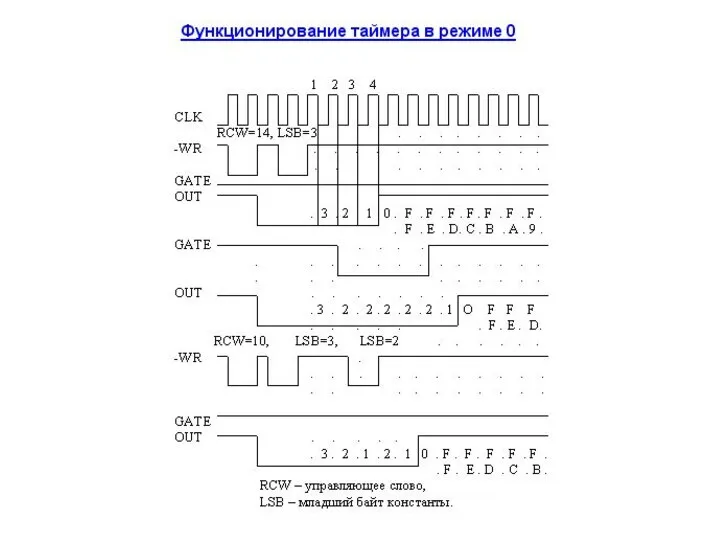

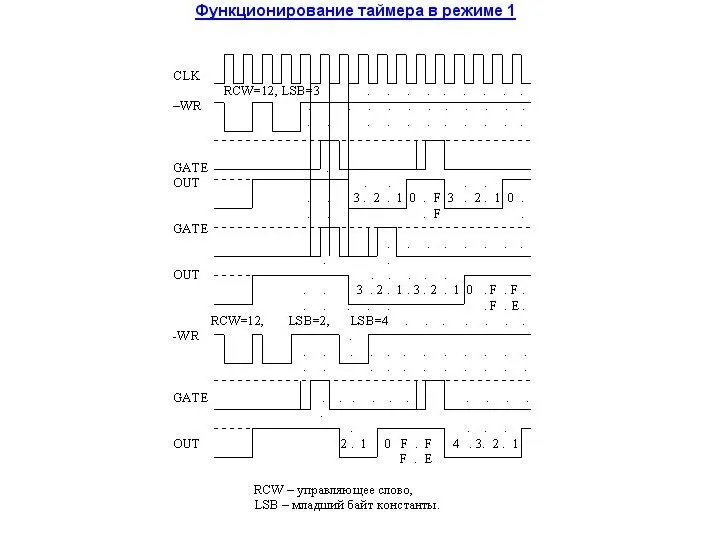

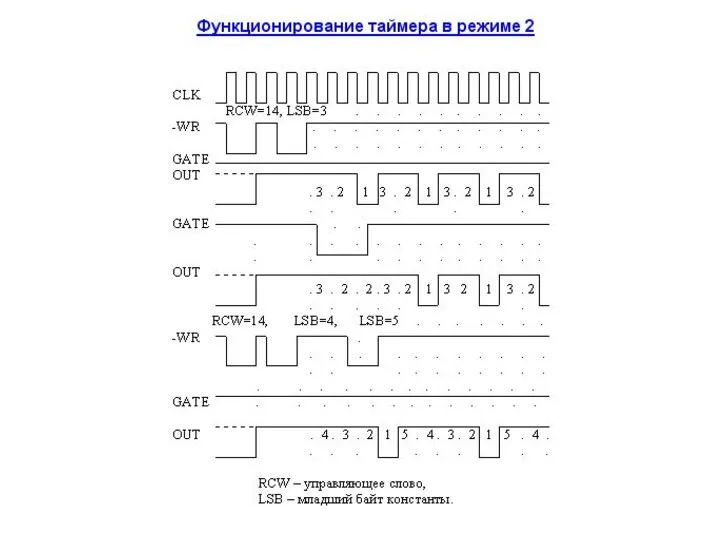

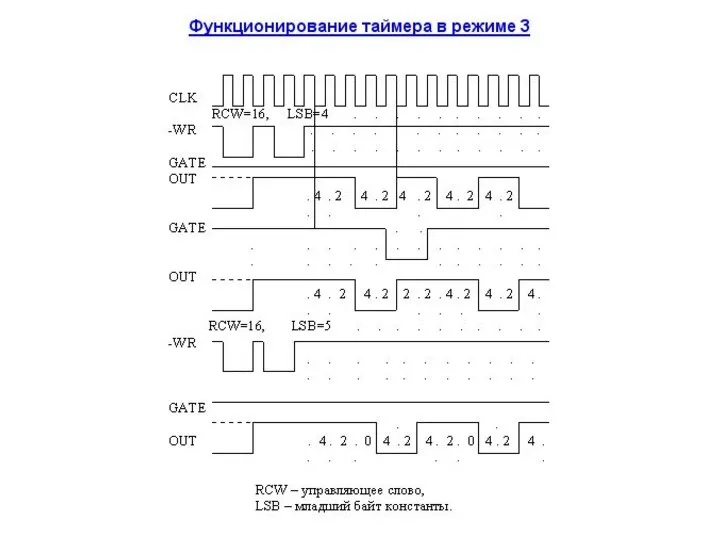

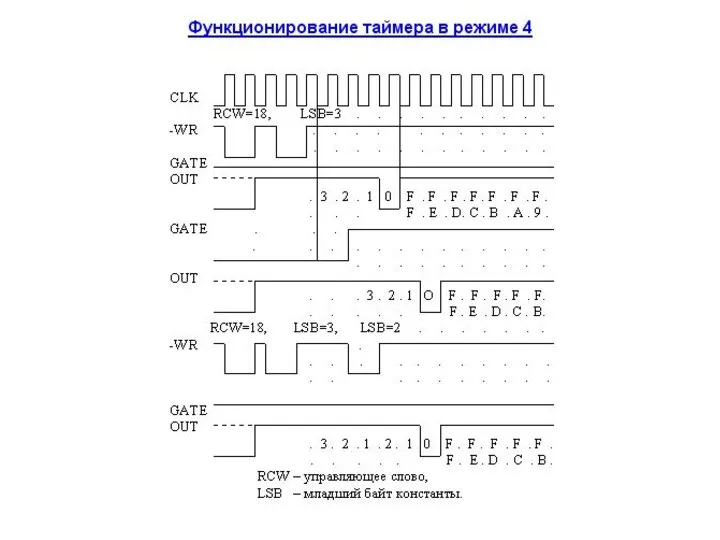

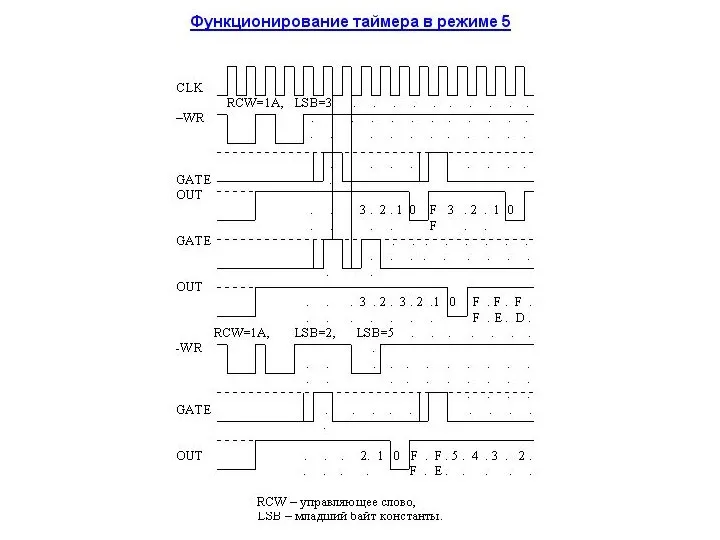

- 127. Таймер Програмно управляемое устройство предназначенное для задания вре- менных интервалов различного ви- да в системах ввода-вывода

- 141. Скачать презентацию

![Сигналы шины ISA Сигналы адреса и данных SA(System Adres)[19-0] - адрес](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1296964/slide-41.jpg)

![Базовые сигналы шины PCI AD[31-0] – адрес – данные; C/BE[3-0] –](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/1296964/slide-49.jpg)

Непрерывные коды

Непрерывные коды Урок по китайскому языку. (Урок 10)

Урок по китайскому языку. (Урок 10) Производительность

Производительность Детям о ПБП на ДЖ транспорте - презентация для начальной школы

Детям о ПБП на ДЖ транспорте - презентация для начальной школы Презентация на тему "Мониторинг как инструмент оценки качества образовательных результатов учащихся" - скачать презентации

Презентация на тему "Мониторинг как инструмент оценки качества образовательных результатов учащихся" - скачать презентации  Крымская война 1853—1856 Выполнила студентка Группы Ю-104 Чуева Яна

Крымская война 1853—1856 Выполнила студентка Группы Ю-104 Чуева Яна Szczeciński Park Naukowo-Technologiczny

Szczeciński Park Naukowo-Technologiczny Выборочный контроль ЛС отечественного и зарубежного производства, находящиеся в сфере обращения

Выборочный контроль ЛС отечественного и зарубежного производства, находящиеся в сфере обращения Михаи́л Васи́льевич Ломоно́сов

Михаи́л Васи́льевич Ломоно́сов Информационные ресурсы негуманитарных областей науки и практики

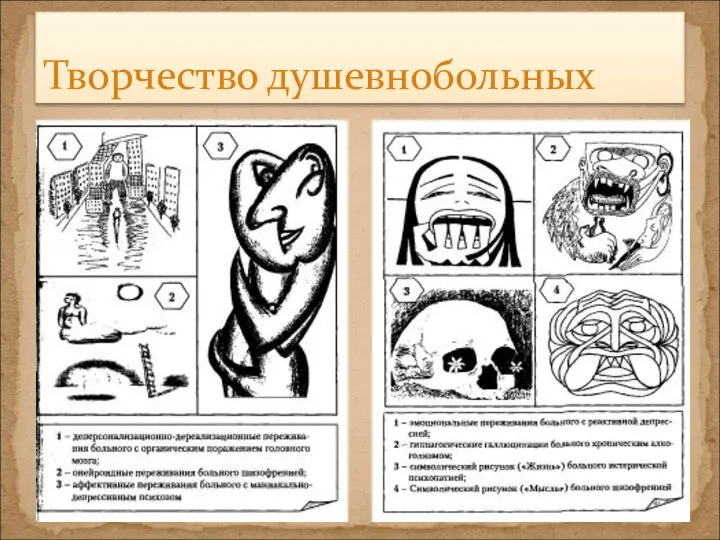

Информационные ресурсы негуманитарных областей науки и практики Творчество душевнобольных

Творчество душевнобольных Клуб супер математиков - презентация по Алгебре

Клуб супер математиков - презентация по Алгебре Традиционные праздники и социализация детей народов Поволжья

Традиционные праздники и социализация детей народов Поволжья Geometria.ru - cоциальная сеть о клубной и ночной жизни - презентация

Geometria.ru - cоциальная сеть о клубной и ночной жизни - презентация Правовое обеспечение мультимедийного контента

Правовое обеспечение мультимедийного контента «КРАСОТА РУССКОГО ЖЕНСКОГО КОСТЮМА» Апрель, 2009 г.

«КРАСОТА РУССКОГО ЖЕНСКОГО КОСТЮМА» Апрель, 2009 г. Е.И.Чарушин «Кабан» Составитель: Шаршукова В.А., учитель начальных классов МАОУСОШ № 8 г.Старая Русса Новгородской области

Е.И.Чарушин «Кабан» Составитель: Шаршукова В.А., учитель начальных классов МАОУСОШ № 8 г.Старая Русса Новгородской области Исторические этапы развития коммуникаций. Общинная коммуникационная система

Исторические этапы развития коммуникаций. Общинная коммуникационная система Важность физкультуры для молодёжи

Важность физкультуры для молодёжи Муниципальное образовательное учреждение средняя общеобразовательная школа №93 Барабинского района Новосибирской области

Муниципальное образовательное учреждение средняя общеобразовательная школа №93 Барабинского района Новосибирской области  Архитектура итальянского Возрождения Выполнила: Учитель музыки и МХК ГОУ СОШ № 249 СВАО г. Москвы

Архитектура итальянского Возрождения Выполнила: Учитель музыки и МХК ГОУ СОШ № 249 СВАО г. Москвы  Алгебра 8 класс.

Алгебра 8 класс.  Экономика электронного бизнеса и информационных систем

Экономика электронного бизнеса и информационных систем Построение диаграмм. Типы диаграмм – Точечная, поверхность

Построение диаграмм. Типы диаграмм – Точечная, поверхность Сервитутное право в Римском праве Выполнила Мамочкина Юля

Сервитутное право в Римском праве Выполнила Мамочкина Юля  Работа с реестром (Лекция № 5)

Работа с реестром (Лекция № 5) Система и источники административного права как отрасли права, науки и учебной дисциплины

Система и источники административного права как отрасли права, науки и учебной дисциплины Дифференциация в обучении – ключ к сохранению индивидуальности «Обучение должно быть вариативным и индивидуальным особенностям

Дифференциация в обучении – ключ к сохранению индивидуальности «Обучение должно быть вариативным и индивидуальным особенностям